# INSTRUCTOR'S MANUAL FOR

# Volume 2: Presentation Material

# **Behrooz Parhami**

Department of Electrical and Computer Engineering University of California Santa Barbara, CA 93106-9560, USA E-mail: <u>parhami@ece.ucsb.edu</u>

© Plenum Press, Winter 2002

|                          | Parts                                     | Half-Parts                                                                | Chapters                                                                                                                                                                                    |  |  |  |  |

|--------------------------|-------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                          | Part I:<br>Fundamental<br>Concepts        | Background and<br>Motivation<br>Complexity and<br>Models                  | <ol> <li>Introduction to Parallelism</li> <li>A Taste of Parallel Algorithms</li> <li>Parallel Algorithm Complexity</li> <li>Models of Parallel Processing</li> </ol>                       |  |  |  |  |

| iations                  | Part II:<br>Extreme<br>Models             | Abstract View of<br>Shared Memory<br>Circuit Model of<br>Parallel Systems | <ol> <li>5. PRAM and Basic Algorithms</li> <li>6. More Shared-Memory Algorithms</li> <li>7. Sorting and Selection Networks</li> <li>8. Other Circuit-Level Examples</li> </ol>              |  |  |  |  |

| Architectural Variations | Part III:<br>Mesh-Based<br>Architectures  | Data Movement<br>on 2D Arrays<br>Mesh Algorithms<br>and Variants          | <ol> <li>9. Sorting on a 2D Mesh or Torus</li> <li>10. Routing on a 2D Mesh or Torus</li> <li>11. Numerical 2D Mesh Algorithms</li> <li>12. Other Mesh-Related Architectures</li> </ol>     |  |  |  |  |

| Archite                  | Part IV:<br>Low-Diameter<br>Architectures | The Hypercube<br>Architecture<br>Hypercubic and<br>Other Networks         | <ul> <li>13. Hypercubes and Their Algorithms</li> <li>14. Sorting and Routing on Hypercubes</li> <li>15. Other Hypercubic Architectures</li> <li>16. A Sampler of Other Networks</li> </ul> |  |  |  |  |

|                          | Part V:<br>Some Broad<br>Topics           | Coordination and<br>Data Access<br>Robustness and<br>Ease of Use          | <ol> <li>17. Emulation and Scheduling</li> <li>18. Data Storage, Input, and Output</li> <li>19. Reliable Parallel Processing</li> <li>20. System and Software Issues</li> </ol>             |  |  |  |  |

|                          | Part VI:<br>Implementation<br>Aspects     | Control-Parallel<br>Systems<br>Data Parallelism<br>and Conclusion         | <ol> <li>Shared-Memory MIMD Machines</li> <li>Message-Passing MIMD Machines</li> <li>Data-Parallel SIMD Machines</li> <li>Past, Present, and Future</li> </ol>                              |  |  |  |  |

#### The structure of this book in parts, half-parts, and chapters

#### This instructor's manual is for

Introduction to Parallel Processing: Algorithms and Architectures, by Behrooz Parhami ISBN 0-306-45970-1, QA76.58.P3798 ©1999 Plenum Press, New York, http://www.plenum.com

For information and errata, see http://www.ece.ucsb.edu/Faculty/Parhami/text\_par\_proc.htm

All rights reserved for the author. No part of this instructor's manual may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without written permission. Contact the author at: ECE Dept., Univ. of California, Santa Barbara, CA 93106-9560, USA (<u>parhami@ece.ucsb.edu</u>)

## **Preface to the Instructor's Manual**

This instructor's manual consists of two volumes. Volume 1 presents solutions to selected problems and includes additional problems (many with solutions) that did not make the cut for inclusion in the text *Introduction to Parallel Processing: Algorithms and Architectures* (Plenum Press, 1999) or that were designed after the book went to print. Volume 2 contains enlarged versions of the figures and tables in the text as well as additional material, presented in a format that is suitable for use as transparency masters.

The winter 2002 edition Volume 1, which consists of the following parts, is available to qualified instructors through the publisher:

Volume 1 Part I Selected solutions and additional problems

Part II Question bank, assignments, and projects

The winter 2002 edition of Volume 2, which consists of the following parts, is available as a large file in postscript format through the book's Web page:

Volume 2 Parts I-VI Lecture slides and other presentation material

The book's Web page, given below, also contains an errata and a host of other material (please note the upper-case "F" and "P" and the underscore symbol after "text" and "par"):

http://www.ece.ucsb.edu/Faculty/Parhami/text\_par\_proc.htm

The author would appreciate the reporting of any error in the textbook or in this manual, suggestions for other tables, diagrams, or lecture topics, and sharing of teaching experiences. Please e-mail your comments to

parhami@ece.ucsb.edu

or send them by regular mail to the author's postal address:

Department of Electrical and Computer Engineering University of California Santa Barbara, CA 93106-9560, USA

Contributions will be acknowledged to the extent possible.

Behrooz Parhami Santa Barbara, Winter 2002 Introduction to Parallel Processing: Algorithms and Architectures

## Table of Contents, Vol. 2

|                      | Preface to the Instructor's Manual                                                                                                    | 3                        |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Part I               | Fundamental Concepts                                                                                                                  | 5                        |

| 1<br>2<br>3<br>4     | Introduction to Parallelism<br>A Taste of Parallel Algorithms<br>Parallel Algorithm Complexity<br>Models of Parallel Processing       | 6<br>29<br>45<br>57      |

| Part II              | Extreme Models                                                                                                                        | 71                       |

| 5<br>6<br>7<br>8     | PRAM and Basic Algorithms<br>More Shared-Memory Algorithms<br>Sorting and Selection Networks<br>Other Circuit-Level Examples          | 72<br>92<br>108<br>124   |

| Part III             | Mesh-Based Architectures                                                                                                              | 141                      |

| 9<br>10<br>11<br>12  | Sorting on a 2D Mesh or Torus<br>Routing on a 2-D Mesh or Torus<br>Numerical 2D Mesh Algorithms<br>Mesh-Related Architectures         | 142<br>158<br>171<br>195 |

| Part IV              | Low-Diameter Architectures                                                                                                            | 222                      |

| 13<br>14<br>15<br>16 | Hypercubes and Their Algorithms<br>Sorting and Routing on Hypercubes<br>Other Hypercubic Architectures<br>A Sampler of Other Networks | 223<br>243<br>265<br>283 |

| Part V               | Some Broad Topics                                                                                                                     | 313                      |

| 17<br>18<br>19<br>20 | Emulation and Scheduling<br>Data Storage, Input, and Output<br>Reliable Parallel Processing<br>System and Software Issues             | 314<br>332<br>342<br>359 |

| Part VI              | Implementation Aspects                                                                                                                | 380                      |

| 21<br>22<br>23       | Shared-Memory MIMD Machines<br>Message-Passing MIMD Machines<br>Data-Parallel SIMD Machines                                           | 381<br>392<br>404        |

24 Past, Present, and Future 417

# Part I Fundamental Concepts

#### Back to TOC

#### Part Goals

- Motivate us to study parallel processing

- Paint the big picture

- Provide background in the three Ts: Taxonomy – including basic terminology Tools – for evaluation or comparison Theory – easy and hard problems

Part Contents

- Chapter 1: Introduction to Parallelism

- Chapter 2: A Taste of Parallel Algorithms

- Chapter 3: Parallel Algorithm Complexity

- Chapter 4: Models of Parallel Processing

## **1** Introduction to Parallelism

#### Back to TOC

Chapter Goals

- Set the context in which the course material will be presented

- Review challenges that face the designers and users of parallel computers

- Introduce metrics for evaluating the effectiveness of parallel systems

Chapter Contents

- 1.1. Why Parallel Processing?

- 1.2. A Motivating Example

- 1.3. Parallel Processing Ups and Downs

- 1.4. Types of Parallelism: A Taxonomy

- 1.5. Roadblocks to Parallel Processing

- 1.6. Effectiveness of Parallel Processing

#### 1.1 Why Parallel Processing?

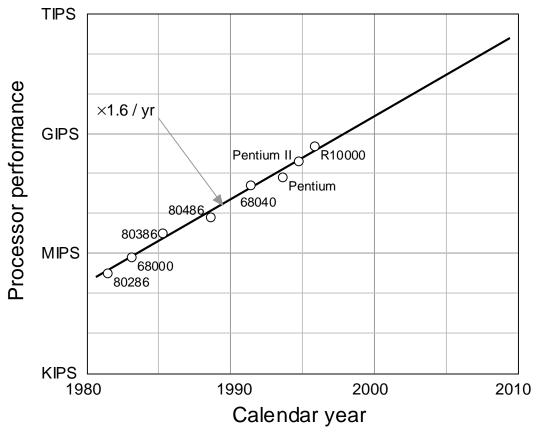

Fig. 1.1. The exponential growth of microprocessor performance, known as Moore's Law, shown over the past two decades.

Figures rounded/averaged from "2001 Technology Roadmap for Semiconductors" [Alla02]

| Calendar year $\rightarrow$ | 2001 | 2004 | 2007 | 2010 | 2013 | 2016 |

|-----------------------------|------|------|------|------|------|------|

| Halfpitch (nm)              | 140  | 90   | 65   | 45   | 32   | 22   |

| Clock freq. (GHz)           | 2    | 4    | 7    | 12   | 20   | 30   |

| Wiring levels               | 7    | 8    | 9    | 10   | 10   | 10   |

| Power supply (V)            | 1.1  | 1.0  | 0.8  | 0.7  | 0.6  | 0.5  |

| Max. power (W)              | 130  | 160  | 190  | 220  | 250  | 290  |

Factors contributing to the validity of Moore's law

Denser circuits Architectural improvements

Measures of processor performance

Instructions per second (MIPS, GIPS, TIPS, PIPS) Floating-point operations per second (MFLOPS, GFLOPS, TFLOPS, PFLOPS) Running time on benchmark suites Examples of benchmarks

Categories of supercomputers

Uniprocessor (vector processor) Multiprocessor Multicomputer Massively parallel processor (MPP)

There is a limit to the speed of a single processor (the speed-of-light argument)

Light travels 30 cm/ns;

signals on wires travel at a fraction of this speed ( $\cong c/E_r^{1/2}$ , where  $E_r \cong 2-4$  is the dielectric coeff.) If signals *must* travel 1 cm in an instruction cycle, cycle time cannot be shorter than 1/30 ns; thus, 30 GIPS is the best we can hope for

#### Motivations for concurrency

- Higher speed (solve problems faster)

Important when there are "hard" or "soft" deadlines;

e.g., 24-hour weather forecast

- 2. Higher throughput (solve more problems)Important when there are many similar tasks to perform;e.g., transaction processing

- Higher computational power (solve larger problems)

e.g., weather forecast for a week rather than 24 hours, or with a finer mesh for greater accuracy

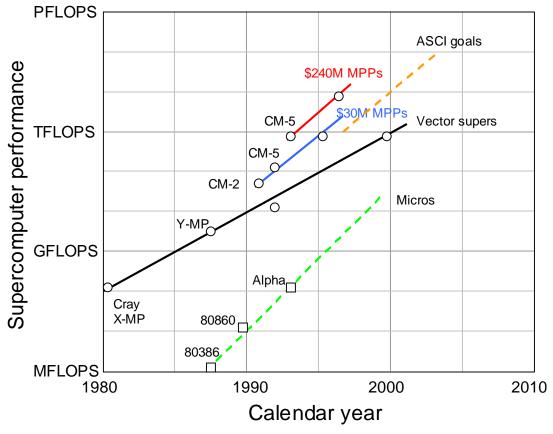

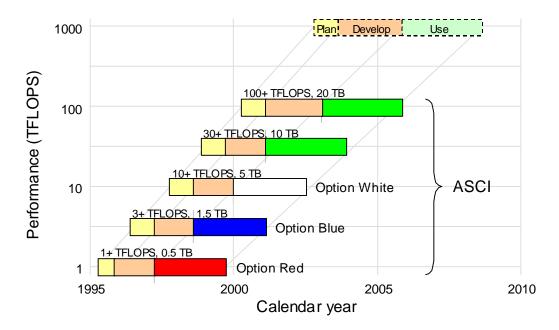

Fig. 1.2. The exponential growth in supercomputer performance over the past two decades (from [Bell92], with ASCI performance goals and microprocessor peak FLOPS superimposed as dotted lines).

## The need for TFLOPS

Modeling of heat transport to the South Pole in the southern oceans [Ocean model: 4096 E-W regions  $\times$  1024 N-S regions  $\times$  12 layers in depth]

30 000 000 000 FLOP per 10-min iteration  $\times$  300 000 iterations per six-year period =  $10^{16}$  FLOP

Fluid dynamics

1000  $\times$  1000  $\times$  1000 lattice  $\times$ 1000 FLOP per lattice point  $\times$  10 000 time steps = 10<sup>16</sup> FLOP

Monte Carlo simulation of nuclear reactor

100 000 000 particles to track (for  $\cong$ 1000 escapes) × 10 000 FLOP per particle tracked = 10<sup>15</sup> FLOP

Reasonable running time =

Fraction of hour to several hours  $(10^3 - 10^4 \text{ s})$

Computational power =

$10^{16}$  FLOP /  $10^{4}$ s or  $10^{15}$  FLOP /  $10^{3}$ s =  $10^{12}$  FLOPS

Why the current quest for PFLOPS?

Same problems, perhaps with finer grids or longer simulated times

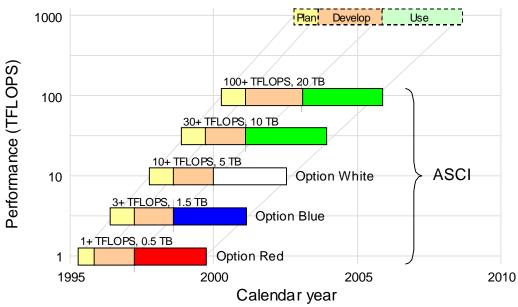

# ASCI: Advanced Strategic Computing Initiative, US Department of Energy

Fig. 24.1. Milestones in the Accelerated Strategic Computing Initiative (ASCI) program, sponsored by the US Department of Energy, with extrapolation up to the PFLOPS level.

## Status of Computing Power (circa 2000)

### **GFLOPS** on desktop

Apple Macintosh, with G4 processor

#### **TFLOPS** in supercomputer center

1152-processor IBM RS/6000 SP uses a switch-based interconnection network see *IEEE Concurrency*, Jan.-Mar. 2000, p. 9 Cray T3E, torus-connected

#### **PFLOPS on drawing board**

1M-processor IBM Blue Gene (2005?)

see IEEE Concurrency, Jan.-Mar. 2000, pp. 5-9 32 proc's/chip, 64 chips/board, 8 boards/tower, 64 towers Processor: 8 threads, on-chip memory, no data cache Chip: defect-tolerant, row/column rings in a  $6 \times 6$  array Board:  $8 \times 8$  chip grid organized as  $4 \times 4 \times 4$  cube Tower: Boards linked to 4 neighbors in adjacent towers System:  $32 \times 32 \times 32$  cube of chips, 1.5 MW (water-cooled)

#### **1.2 A Motivating Example**

#### Sieve of Eratosthenes ('er-a-'taas-tha-neez)

for finding all primes in [1, n]

| 2 3<br>m=2 | 4 5      | 6 | 7        | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 |

|------------|----------|---|----------|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 2 3<br>m=3 | 5        |   | 7        |   | 9 |    | 11 |    | 13 |    | 15 |    | 17 |    | 19 |    | 21 |    | 23 |    | 25 |    | 27 |    | 29 |    |

| 2 3        | 5<br>m=5 |   | 7        |   |   |    | 11 |    | 13 |    |    |    | 17 |    | 19 |    |    |    | 23 |    | 25 |    |    |    | 29 |    |

| 2 3        | 5        |   | 7<br>m=7 |   |   |    | 11 |    | 13 |    |    |    | 17 |    | 19 |    |    |    | 23 |    |    |    |    |    | 29 |    |

Fig. 1.3. The sieve of Eratosthenes yielding a list of 10 primes for n = 30. Marked elements have been distinguished by erasure from the list.

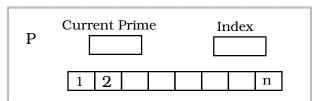

Fig. 1.4. Schematic representation of single-processor solution for the sieve of Eratosthenes.

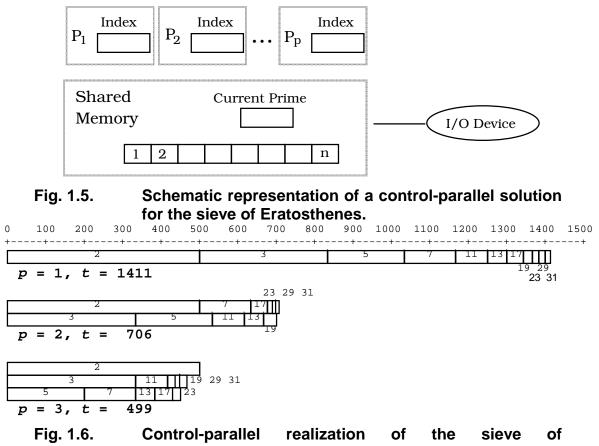

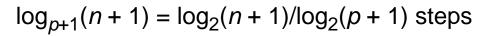

Eratosthenes with n = 1000 and  $1 \le p \le 3$ .

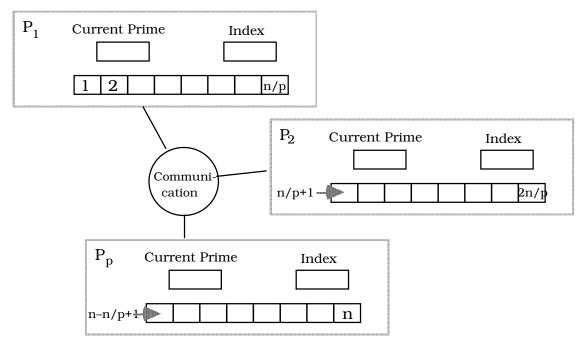

# P<sub>1</sub> finds each prime and broadcasts it to all other processors

Assume  $n/p \ge \sqrt{n}$  ( $p \le \sqrt{n}$ ), so that all primes whose multiples are to be marked reside in P<sub>1</sub>

Fig. 1.7. Data-parallel realization of the sieve of Eratosthenes.

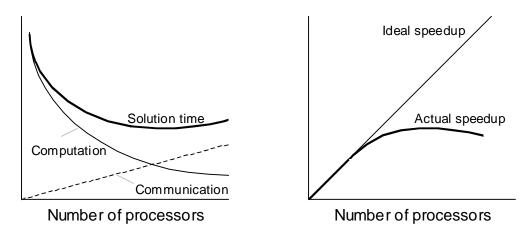

# Some reasons for sublinear speed-up Communication overhead

Fig. 1.8. Trade-off between communication time and computation time in the data-parallel realization of the sieve of Eratosthenes.

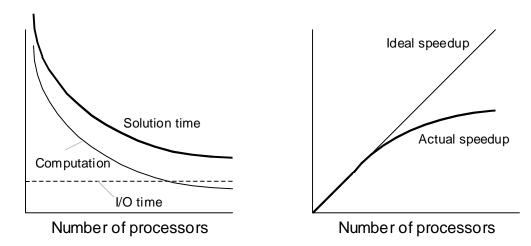

#### Input/output overhead

Fig. 1.9. Effect of a constant I/O time on the data-parallel realization of the sieve of Eratosthenes.

#### **1.3 Parallel Processing Ups and Downs**

Early 1900s: 1000s of "computers" (humans + calculators) to do 24-hour weather prediction in a few hours

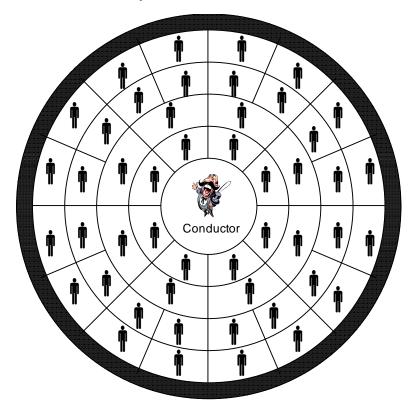

Fig. 1.10. Richardson's circular theater for weather forecasting calculations.

Parallel processing is used in virtually all computers

Compute-I/O overlap, pipelining (fetch/exec overlap), multitasking, VLIW, multiple function units

But ... in this course we use "parallel processing" in a stricter sense implying the availability of multiple CPUs

#### History of Parallel Processing

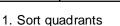

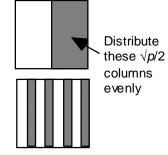

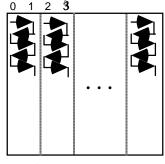

1960s: ILLIAC IV (U Illinois) – Four 8×8 mesh quadrants

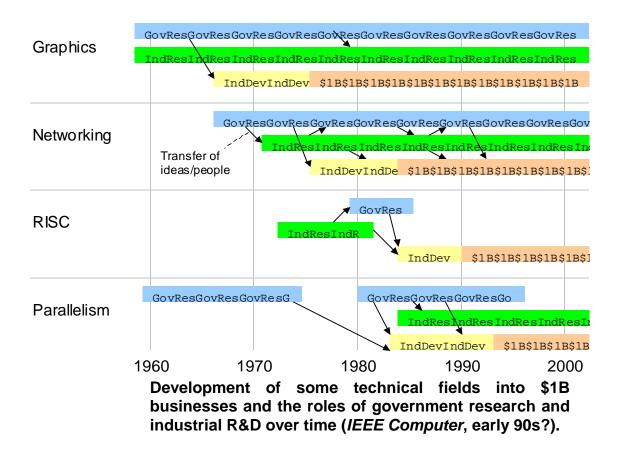

1980s: Commercial interest resurfaced; technology was driven by government contracts. Once funding dried up, many companies went bankrupt

2000s: Internet revolution – info providers, multimedia, data mining, etc. need extensive computational power

#### **1.4 Types of Parallelism: A Taxonomy**

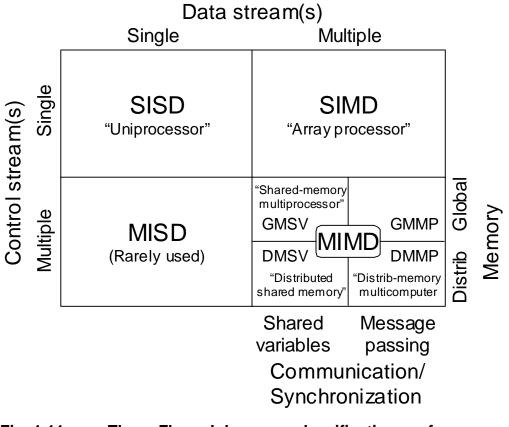

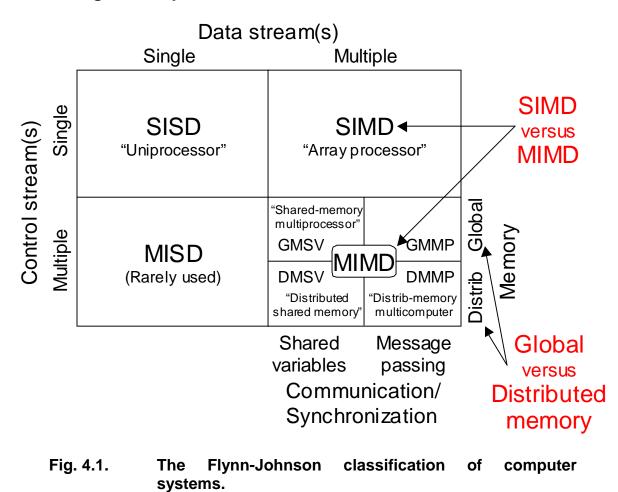

Fig. 1.11. The Flynn-Johnson classification of computer systems.

Why are computer architects so fascinated by four-letter acronyms and abbreviations?

| Systems:     | RISC, CISC, PRAM, NUMA, VLIW |

|--------------|------------------------------|

| Journals:    | JPDC, TPDS                   |

| Conferences: | ICPP, IPPS, SPDP, SPAA       |

My contribution:

- SINC: Scant/Simple Interaction Network Cell

- FINC: Full Interaction Network Cell

## 1.5 Roadblocks to Parallel Processing

a. Grosch's law (economy of scale applies, or computing power proportional to the square of cost)

Rebuttal: Not true any more. Even if it were, there is only one fastest computer; cannot get a faster one by spending more

b. Minsky's conjecture (speedup proportional to the logarithm of the number *p* of processors)

This is due to a statistical argument; you don't need a lot of people in a room to have some with identical birthdays (memory accesses will have conflicts)

Rebuttal: Just like the assumption of no conflict, and thus linear speedup, randomness is too pessimistic; perhaps *p*/log*p* is more realistic than either extreme

c. Tyranny of IC *technology* (since hardware becomes about 10 times faster every 5 years, by the time a parallel machine with 10-fold performance is built, uniprocessors will be just as fast)

Rebuttal: We might try to design parallel systems into which faster components can be incorporated as they become available. Also, we might aim for 100-fold or 1000-fold speedup, not just 10-fold Tyranny of vector supercomputers

(vector supercomputers are rapidly improving

in performance, offer a familiar programming model

and excellent vectorizing compilers;

why bother with parallel processors?)

Rebuttal: Many compute-intensive problems do not involve vector operations; besides, even vector machines nowadays use multiprocessing

e. Software inertia (Billions of dollars worth of existing software makes it hard to switch to parallel systems)

Rebuttal: Not all future applications have already been developed. Improved automatic tools can convert "dusty deck" programs into efficient parallel programs. Students are being trained to "think parallel" f. Amdahl's law

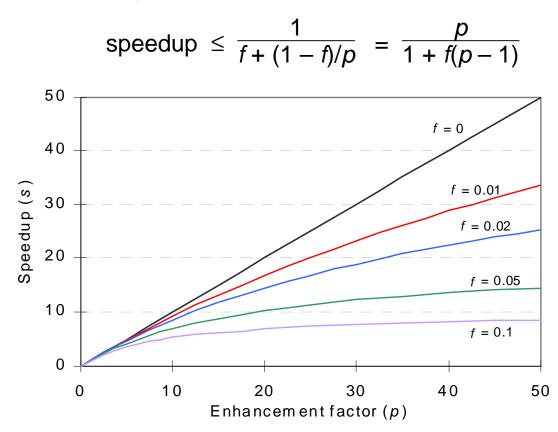

(a small fraction *f* of inherently sequential or unparallelizable computation severely limits the speed-up)

Fig. 1.12. Limit on speed-up according to Amdahl's law.

Rebuttal: Applications with very small *f* exist. Besides, sequential overhead need not be a fixed fraction

# **ABCs of Parallel Processing**

in one transparency\* (parhami@ece.ucsb.edu)

\* Originally appeared in *Computer Architecture News*, Vol. 27, No. 1, p. 2, March 1999.

f = unparallelizable fraction of a task (sequential overhead)  $T_x$  = running time of a task when executed on x processors

#### A Amdahl's Law (Speed-up Formula)

Bad news: Sequential overhead will kill you, since:

Speed-up =

$$\frac{T_1}{T_p} \leq \frac{1}{f + \frac{1-f}{p}} \leq \min(\frac{1}{f}, p)$$

Morale: For f = 0.1, e.g., the speed-up will be at best 10, no matter what the number of processors (peak OPS).

#### **B** Brent's Scheduling Theorem

Good news: Optimal scheduling is a very difficult problem, but even a naive scheduling algorithm can ensure:

$$\frac{T_{1}}{p} \leq T_{p} < \frac{T_{1}}{p} + T_{\infty} = \frac{T_{1}}{p} (1 + \frac{p}{T_{1}/T_{\infty}})$$

Result: For a reasonably parallel task (with small  $T_{\infty}$ ), or for a suitably small number of processors (say,  $p < T_1/T_{\infty}$ ), good speed-up and high utilization are attainable.

#### C Cost-Effectiveness Adage

Real news: The most cost-effective parallel solution to a given problem is often not the one with:

| Greatest speed-up (at what cos | ation can kill you)<br>st?)<br>ousy doing what?) |

|--------------------------------|--------------------------------------------------|

|--------------------------------|--------------------------------------------------|

Analogy: Mass transit (SIMD) might be more cost-effective than using private vehicles (MIMD) even if it is slower and leads to many empty seats on some trips.

## **1.6 Effectiveness of Parallel Processing**

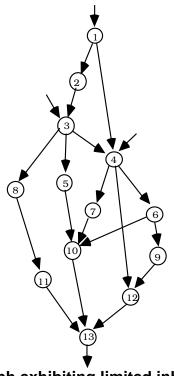

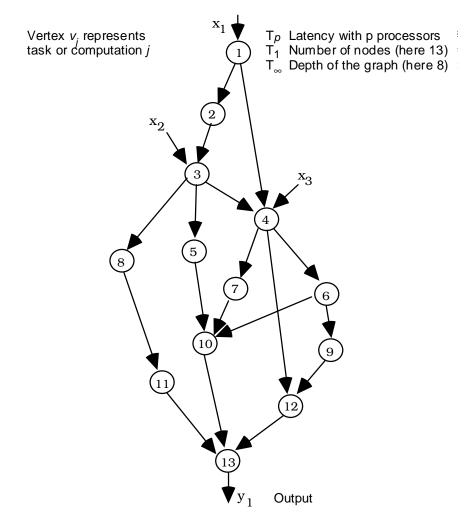

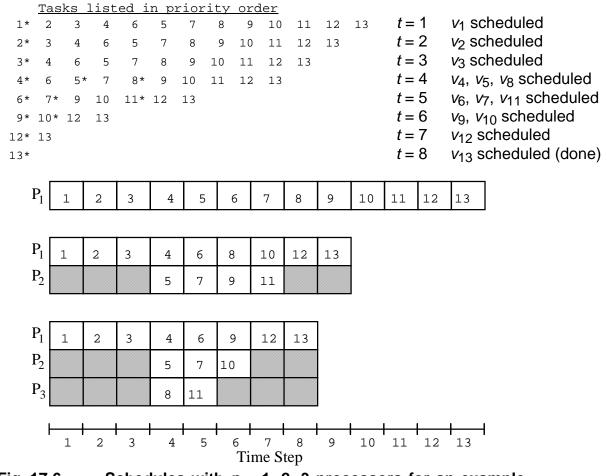

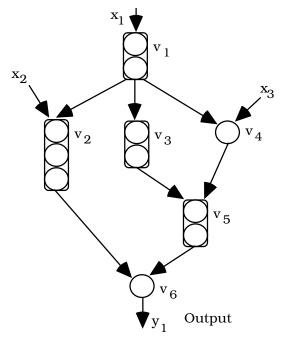

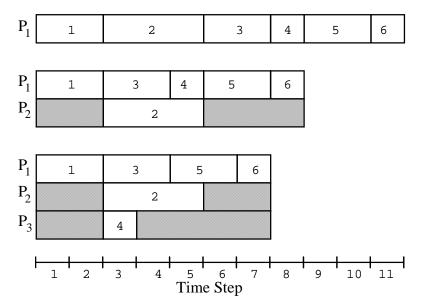

Fig. 1.13. Task graph exhibiting limited inherent parallelism.

Measures for comparing parallel architectures/algorithms:

| p             | Number of processors                                                                              |  |  |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| W(p)          | Total number of unit operations performed by<br><i>p</i> processors; computational work or energy |  |  |  |  |  |  |  |

| Т(р)          | Execution time with $p$ processors;<br>$T(1) = W(1)$ and $T(p) \le W(p)$                          |  |  |  |  |  |  |  |

| S(p)          | Speedup = $\frac{T(1)}{T(p)}$                                                                     |  |  |  |  |  |  |  |

| E(p)          | Efficiency = $\frac{T(1)}{pT(p)}$                                                                 |  |  |  |  |  |  |  |

| R(p)          | Redundancy = $\frac{W(p)}{W(1)}$                                                                  |  |  |  |  |  |  |  |

| U(p)          | Utilization = $\frac{W(p)}{pT(p)}$                                                                |  |  |  |  |  |  |  |

| Q( <i>p</i> ) | Quality = $\frac{T^3(1)}{pT^2(p)W(p)}$                                                            |  |  |  |  |  |  |  |

Relationships among the preceding measures:

$$1 \leq S(p) \leq p \qquad U(p) = R(p)E(p)$$

$$E(p) = \frac{S(p)}{p} \qquad Q(p) = E(p)\frac{S(p)}{R(p)}$$

$$\frac{1}{p} \leq E(p) \leq U(p) \leq 1 \qquad 1 \leq R(p) \leq \frac{1}{E(p)} \leq p$$

$$Q(p) \leq S(p) \leq p$$

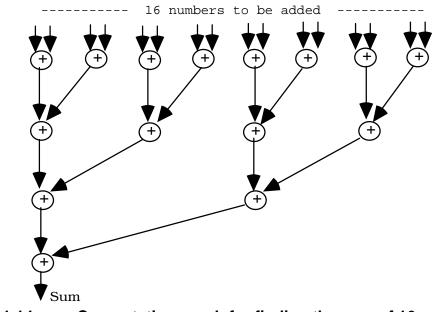

**Example:** Adding 16 numbers, assuming unit-time additions and ignoring all else, with p = 8

Fig. 1.14. Computation graph for finding the sum of 16 numbers.

Zero-time communication: W(8) = 15 T(8) = 4  $E(8) = 15 / (8 \times 4) = 47\%$ S(8) = 15 / 4 = 3.75 R(8) = 15/15 = 1 Q(8) = 1.76

Unit-time communication: W(8) = 22 T(8) = 7  $E(8) = 15 / (8 \times 7) = 27\%$ S(8) = 15 / 7 = 2.14 R(8) = 22 / 15 = 1.47 Q(8) = 0.39

## 2 A Taste of Parallel Algorithms

Back to TOC

Chapter Goals

- Consider five basic building-block parallel operations

- Implement them on four simple parallel architectures

- Learn about the nature of parallel computations, complexity analysis, and the algorithm/architecture interplay

Chapter Contents

- 2.1. Some Simple Computations

- 2.2. Some Simple Architectures

- 2.3. Algorithms for a Linear Array

- 2.4. Algorithms for a Binary Tree

- 2.5. Algorithms for a 2D Mesh

- 2.6. Algorithms with Shared Variables

#### 2.1 Some Simple Computations

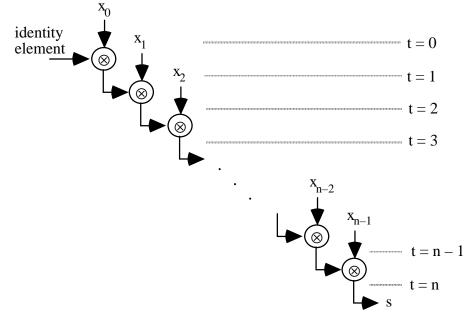

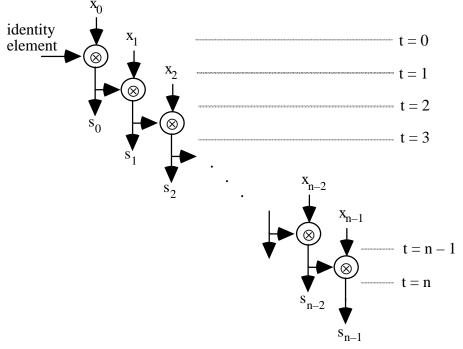

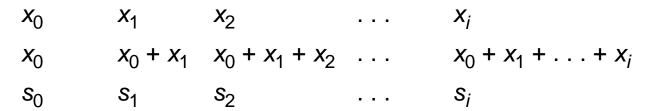

Fig. 2.1. Semigroup computation on a uniprocessor.

Semigroup computation viewed as a tree or fan-in computation.

Introduction to Parallel Processing: Algorithms and Architectures

Prefix computation on a uniprocessor.

3. Packet routing

one processor sending a packet of data to another

4. Broadcasting

one processor sending a packet of data to all others

5. Sorting

processors cooperating in rearranging their data into desired order

#### 2.2 Some Simple Architectures

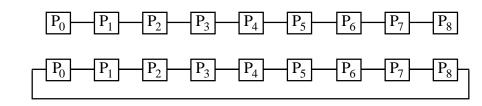

Fig. 2.2. A linear array of nine processors and its ring variant.

Diameter of linear array: D = p - 1

(Max) Node degree: d = 2

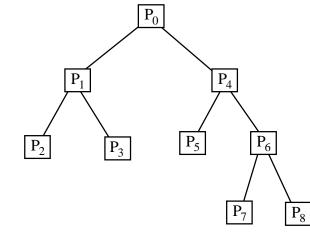

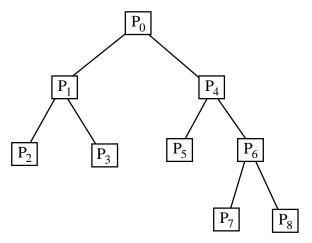

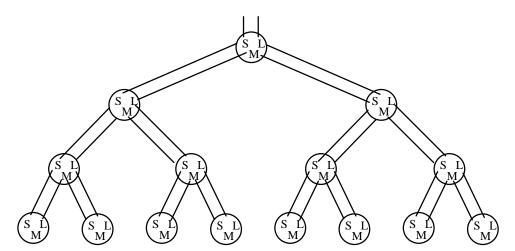

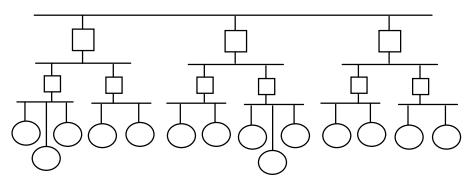

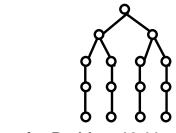

Fig. 2.3. A balanced (but incomplete) binary tree of nine processors.

Diameter of balanced binary tree:  $D = 2 \lfloor \log_2 p \rfloor$ ; or 1 less

(Max) Node degree: d = 3

We almost always deal with complete binary trees:

p one less than a power of 2,  $D = 2 \log_2(p+1) - 2$

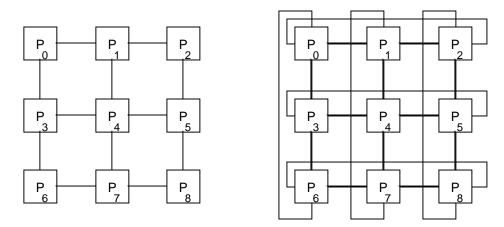

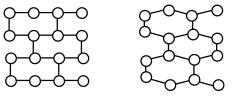

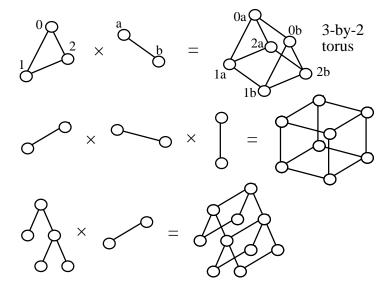

Fig. 2.4. 2D mesh of 9 processors and its torus variant.

Diameter of  $r \times (p/r)$  mesh: D = r + p/r - 2

(Max) Node degree: d = 4

Square meshes preferred; they minimize D (=  $2\sqrt{p}$  – 2)

Diameter of complete graph: D = 1

(Max) Node degree: d = p - 1

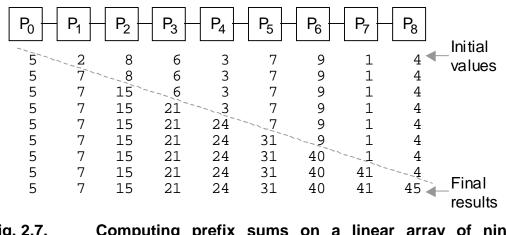

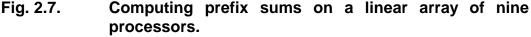

#### 2.3 Algorithms for a Linear Array

Diminished prefix computation: the *i*th result excludes the *i*th element (e.g., sum of the first i - 1 elements)

Fig. 2.8. Computing prefix sums on a linear array with two items per processor.

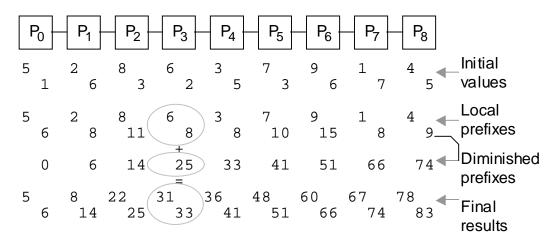

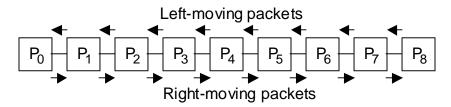

Packet routing or broadcasting:

#### right- and left-moving packets have no conflict

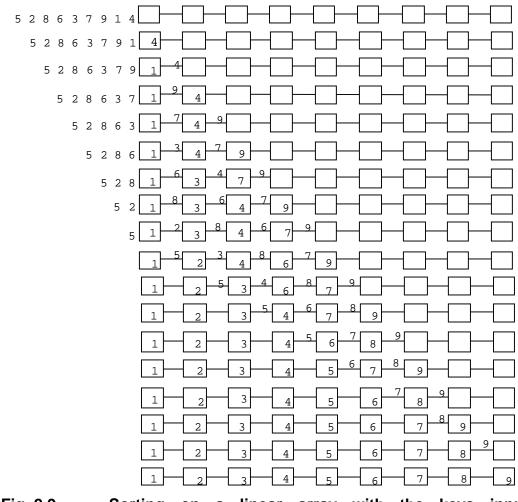

Fig. 2.9. Sorting on a linear array with the keys input sequentially from the left.

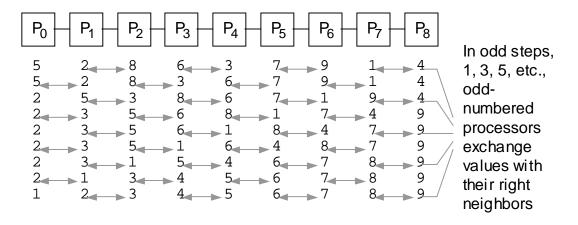

Fig. 2.10. Odd-even transposition sort on a linear array.

For odd-even transposition sort:

Speed-up =  $O(p \log p) / p = O(\log p)$ Efficiency =  $O((\log p) / p)$ Redundancy =  $O(p / (\log p))$ Utilization = 1/2

## 2.4 Algorithms for a Binary Tree

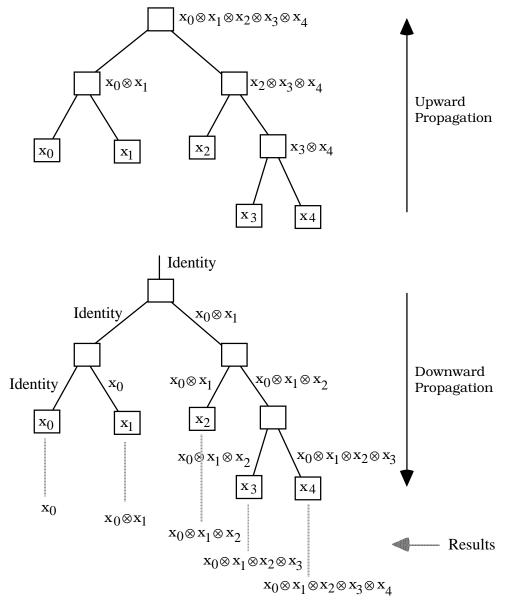

Fig. 2.11. Parallel prefix computation on a binary tree of processors.

#### Some applications of the parallel prefix computation

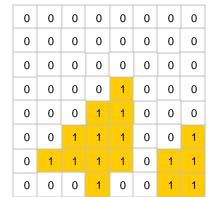

Finding the rank of each 1 in a list of 0s and 1s:

| Data:             | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

|-------------------|---|---|---|---|---|---|---|---|---|---|---|

| Prefix sums:      | 0 | 0 | 1 | 1 | 2 | 2 | 2 | 3 | 4 | 5 | 5 |

| Ranks of 1s:      |   |   | 1 |   | 2 |   |   | 3 | 4 | 5 |   |

| Priority circuit: |   |   |   |   |   |   |   |   |   |   |   |

| Data:             | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| Dim'd prefix ORs: | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| Complement:       | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| AND with data:    | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Carry computation in fast adders

Let "g", "p", and "a" denote the event that a particular digit position in the adder generates, propagates, or annihilates a carry. The input data for the carry circuit consists of a vector of three-valued elements such as:

Parallel prefix computation using the carry operator "¢"

$p \notin x = x$  x propagates over p, for all  $x \in \{g, p, a\}$

- $a \notin x = a$  x is annihilated or absorbed by a

- $g \notin x = g$  x is immaterial; a carry is generated

## Packet routing on a tree

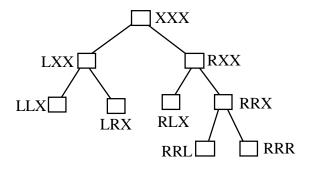

A balanced binary tree with preorder node indices.

```

\begin{array}{ll} \textit{maxl} (\textit{maxr}) = \textit{largest node number in left (right) subtree} \\ \textit{if} & \textit{dest} = \textit{self} \\ \textit{then remove the packet {done}} \\ \textit{else if dest < self or dest > maxr} \\ & \textit{then route upward} \\ & \textit{else if dest \leq maxl} \\ & \textit{then route leftward} \\ & \textit{else route rightward} \\ & \textit{endif} \\ \textit{endif} \\ \end{array}

```

# Other indexing schemes might lead to simpler routing algorithms

Broadcasting is done via the root node

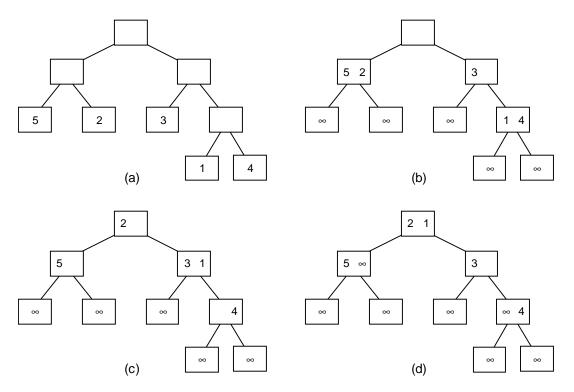

## Sorting: let the root "see" all data in nondescending order

Fig. 2.12. The first few steps of the sorting algorithm on a binary tree.

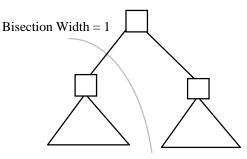

Fig. 2.13. The bisection width of a binary tree architecture.

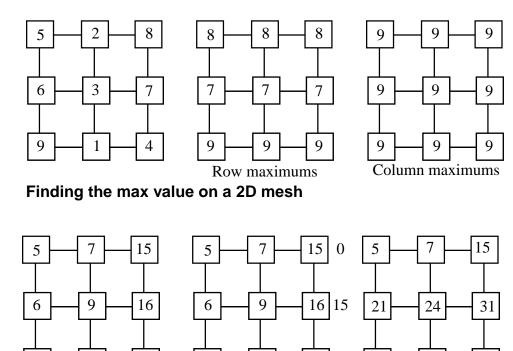

## 2.5 Algorithms for a 2D Mesh

910149101431Row prefix sumsDiminished prefix<br/>sums in last column

Computing prefix sums on a 2D mesh

Row-major order required if operator not commutative

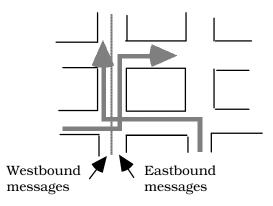

Routing and broadcasting done via row/column operations

40

41

Broadcast in rows

and combine

45

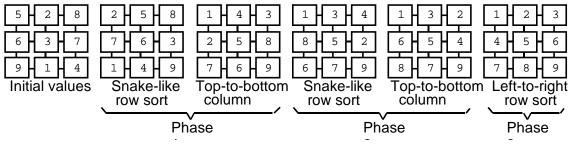

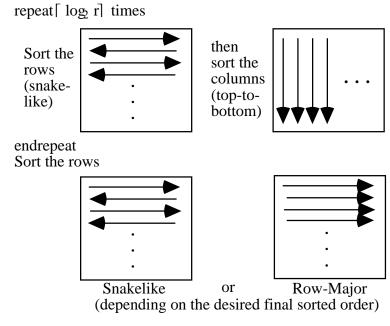

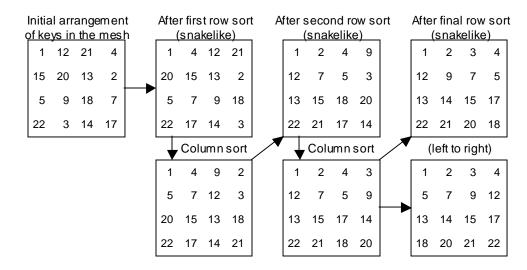

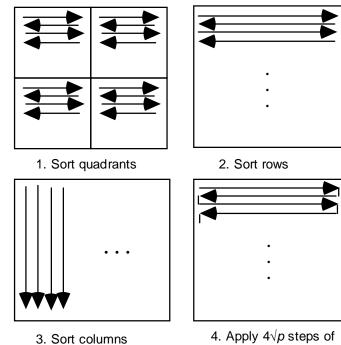

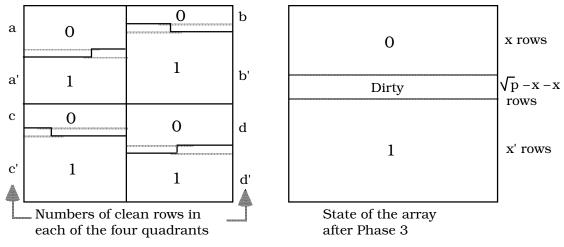

Fig. 2.14. The shearsort algorithm on a  $3 \times 3$  mesh.

## 2.6 Algorithms with Shared Variables

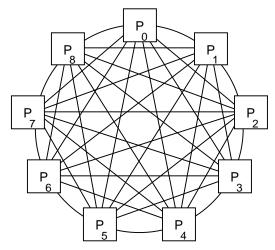

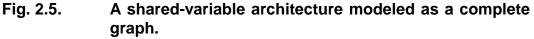

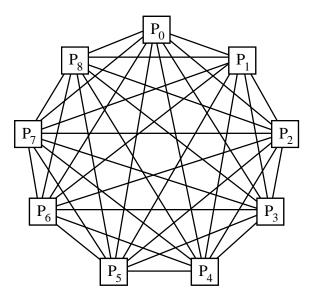

Fig. 2.5. A shared-variable architecture modeled as a complete graph.

Semigroup computation: each processor read all values in turn and combine

Parallel prefix: processor *i* read/combine values 0 to i - 1

Both of the above are quite inefficient, given the high cost

Routing/broadcasting: 1 step, with all-port communication

Sorting: rank each element by comparing it to all others, then permute according to ranks

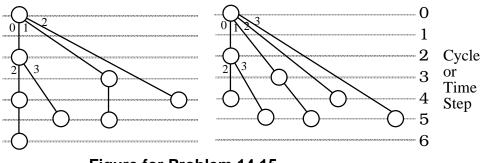

Figure for Problem 2.13.

## **3** Parallel Algorithm Complexity

Back to TOC

#### **Chapter Goals**

- Review algorithm complexity and various complexity classes

- Introduce the notions of time and time-cost optimality

- Derive tools for analyzing, comparing, and fine-tuning parallel algorithms

### **Chapter Contents**

- 3.1. Asymptotic Complexity

- 3.2. Algorithm Optimality and Efficiency

- 3.3. Complexity Classes

- 3.4. Parallelizable Tasks and the NC Class

- 3.5. Parallel Programming Paradigms

- 3.6. Solving Recurrences

### 3.1 Asymptotic Complexity

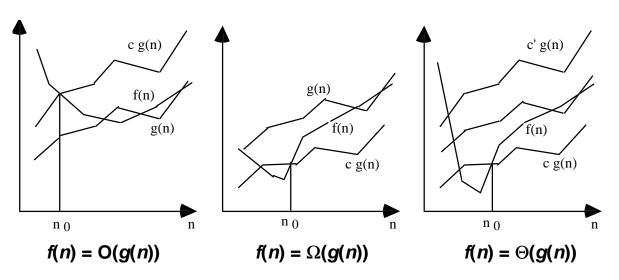

$$f(n) = O(g(n))$$

if  $\exists c, n_0$  such that  $\forall n > n_0, f(n) < c g(n)$

$f(n) = \Omega(g(n))$  if  $\exists c, n_0$  such that  $\forall n > n_0, f(n) > c g(n)$

$f(n) = \Theta(g(n))$  if  $\exists c, c', n_0$  such that

$\forall n > n_0, cg(n) < f(n) < c'g(n)$

Fig. 3.1. Graphical representation of the notions of asymptotic complexity.

- $f(n) = \mathrm{o}(g(n))$

- Growth rate strictly less than

- $f(n) = O(g(n)) \leq Growth rate no greater than$

- $f(n) = \Theta(g(n))$  = Growth rate the same as

<

- $f(n) = \Omega(g(n)) \ge Growth rate no less than$

- $f(n) = \omega(g(n))$  > Growth rate strictly greater than

## Table 3.1.Comparing the Growth Rates of Sublinear and<br/>Superlinear Functions (K = 1000, M = 1 000 000)

| Sublinear |            | Linear | near    |                  |

|-----------|------------|--------|---------|------------------|

| log²n     | $\sqrt{n}$ | n      | n log²n | n <sup>3/2</sup> |

| 9         | 3          | 10     | 90      | 30               |

| 36        | 10         | 100    | 3.6K    | 1K               |

| 81        | 31         | 1K     | 81K     | 31K              |

| 169       | 100        | 10K    | 1.7M    | 1M               |

| 256       | 316        | 100K   | 26M     | 32M              |

| 361       | 1K         | 1M     | 361M    | 1000M            |

## Table 3.2.Effect of Constants on the Growth Rates of Selected<br/>Functions Involving Constant Factors

| n    | $\frac{n}{4} \log^2 n$ | n log²n | 100√ <i>n</i> | <i>n</i> <sup>3/2</sup> |

|------|------------------------|---------|---------------|-------------------------|

|      |                        |         |               |                         |

| 10   | 22                     | 90      | 300           | 30                      |

| 100  | 900                    | 3.6K    | 1K            | 1K                      |

| 1K   | 20K                    | 81K     | 3.1K          | 31K                     |

| 10K  | 423K                   | 1.7N    | 1 10K         | 1M                      |

| 100K | 6M                     | 26M     | 32K           | 32M                     |

| 1M   | 90M                    | 361M    | 100K          | 1000M                   |

## Table 3.3.Effect of Constants on the Growth Rates of Selected<br/>Functions Using Larger Time Units and Round Figures

| n    | $\frac{n}{4}\log^2 n$ r | log <sup>2</sup> n 1 | $00\sqrt{n}$ | n <sup>3/2</sup> |

|------|-------------------------|----------------------|--------------|------------------|

|      | ·                       |                      |              |                  |

| 10   | 20 s                    | 2 min                | 5 min        | 30 s             |

| 100  | 15 min                  | 1 hr                 | 15 min       | 15 min           |

| 1K   | 6 hr                    | 1 day                | 1 hr         | 9 hr             |

| 10K  | 5 days                  | 20 days              | 3 hr         | 10 days          |

| 100K | 2 mo                    | 1 yr                 | 9 hr         | 1 yr             |

| 1M   | З yr                    | 11 yr                | 1 day        | 32 yr            |

## **3.2 Algorithm Optimality and Efficiency**

- *f*(*n*) Running time of fastest (possibly unknown) algorithm for solving a problem

- g(n) Running time of some algorithm  $A \Rightarrow f(n) = O(g(n))$

- h(n) Min time for solving the problem  $\Rightarrow f(n) = \Omega(h(n))$

$g(n) = h(n) \implies$  Algorithm A is time-optimal

Redundancy = Utilization = 1  $\Rightarrow$  A is cost-time optimal

Redundancy = Utilization =  $\Theta(1) \Rightarrow$  A is cost-time efficient

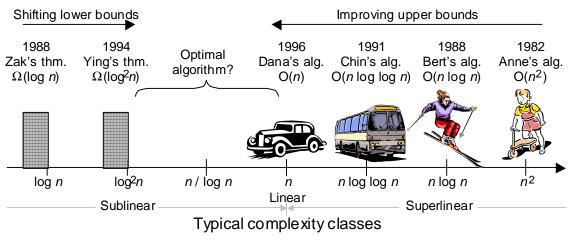

Fig. 3.2. Upper and lower bounds may tighten over time.

Introduction to Parallel Processing: Algorithms and Architectures

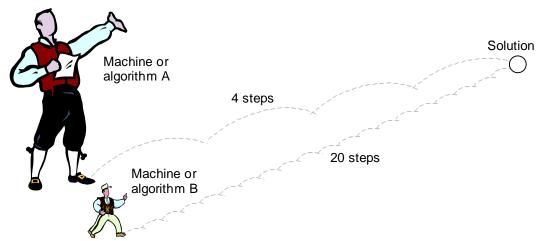

Fig. 3.3. Five times fewer steps does not necessarily mean five times faster.

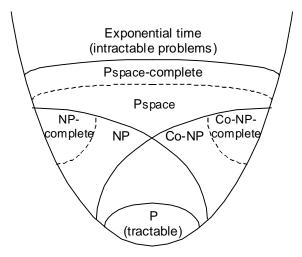

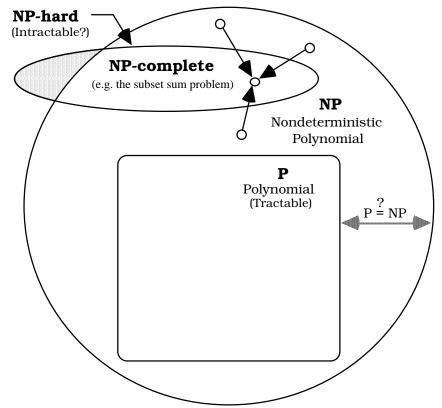

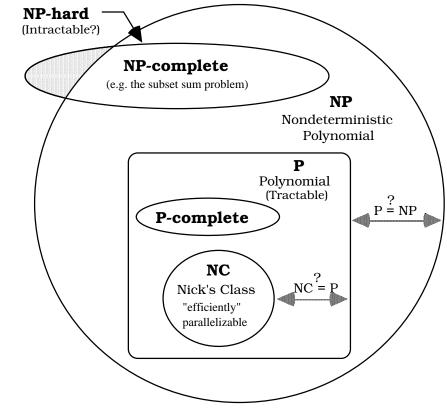

Alternate, more detailed, form of the "complexity classes" diagram for Section 3.3.

## 3.3 Complexity Classes

Conceptual view of the P, NP, NP-complete, and NP-hard classes.

Example NP(-complete) problem: the subset sum problem

Given a set of *n* integers and a target sum *s*, determine if a subset of the integers add up to *s*.

The subset sum problem looks deceptively simple, yet no one knows how to solve it other than by trying practically all of the  $2^n$  subsets of the given set.

Even if each trial takes only one picosecond  $(10^{-12} \text{ s})$ , the problem is virtually unsolvable for n = 100.

## 3.4 Parallelizable Tasks and the NC Class

Fig. 3.4. A conceptual view of complexity classes and their relationships.

NC (Nick's class, Niclaus Pippenger) Problems solvable in polylog time ( $T = O(\log^k n)$ ) using a polynomially bounded number of processors

Example P-complete problem: the circuit-value problem

For a logic circuit with known inputs, find its output The circuit-value problem is obviously in P, but no general algorithm exists for efficient parallel evaluation of a circuit's output.

## 3.5 Parallel Programming Paradigms

## **Divide and conquer**

Decompose problem of size *n* into smaller problems Solve the subproblems independently Combine subproblem results into final answer

| T( <i>n</i> ) | = | <i>T</i> <sub>d</sub> ( <i>n</i> ) | +   | $T_{s}$  | +      | $T_{\rm c}(n)$ |

|---------------|---|------------------------------------|-----|----------|--------|----------------|

|               | [ | Decompose                          | Sol | ve in pa | rallel | Combine        |

## Randomization

Often it is impossible or difficult to decompose a large problem into subproblems with equal solution times.

In these cases, one might use random decisions that lead to good results with very high probability.

Example: sorting with random sampling

Other forms of randomization: Random search, control randomization, symmetry breaking

## Approximation

Iterative numerical methods often use approximation to arrive at the solution(s).

Example: Solving linear systems using Jacobi relaxation.

Under proper conditions, the iterations converge to the correct solutions; more iterations  $\Rightarrow$  greater accuracy

## 3.6 Solving Recurrences

## Solution via unrolling

1.

$$f(n) = f(n-1) + n$$

{rewrite  $f(n-1)$  as  $f((n-1) - 1) + n - 1$ }

$= f(n-2) + n - 1 + n$

$= f(n-3) + n - 2 + n - 1 + n$

$= f(1) + 2 + 3 + \dots + n - 1 + n$

$= n(n + 1)/2 - 1$

$= \Theta(n^2)$

2.  $f(n) = f(n/2) + 1$  {Rewrite  $f(n/2)$  as  $f((n/2)/2 + 1$ }

$= f(n/4) + 1 + 1$

$= f(n/8) + 1 + 1 + 1$

$\dots$

$= f(n/n) + 1 + 1 + 1 + \dots + 1$

$\dots$

$= f(n/n) + 1 + 1 + 1 + \dots + 1$

$\dots$

$= \log_2 n$

$= \Theta(\log n)$

3.  $f(n) = 2f(n/2) + 1$

$= 4f(n/4) + 2 + 1$

$= 8f(n/8) + 4 + 2 + 1$

$\dots$

$= n f(n/n) + n/2 + \dots + 4 + 2 + 1$

$= n - 1$

$$= \Theta(n)$$

4.

$$f(n) = f(n/2) + n$$

$= f(n/4) + n/2 + n$

$= f(n/8) + n/4 + n/2 + n$

$\dots$

$= f(n/n) + 2 + 4 + \dots + n/4 + n/2 + n$

$= 2n - 2 = \Theta(n)$

5.  $f(n) = 2f(n/2) + n$

$= 4f(n/4) + n + n$

$= 8f(n/8) + n + n + n$

$\dots$

$= n f(n/n) + n + n + n + \dots + n$

$\dots$

$$= n \log_2 n = \Theta(n \log n)$$

Alternate solution for the recurrence f(n) = 2f(n/2) + n: Rewrite the recurrence as  $\frac{f(n)}{n} = \frac{f(n/2)}{n/2} + 1$

and denote f(n)/n by h(n) to convert the problem to Example 2

6.

$$f(n) = f(n/2) + \log_2 n$$

$$= f(n/4) + \log_2(n/2) + \log_2 n$$

$$= f(n/8) + \log_2(n/4) + \log_2(n/2) + \log_2 n$$

...

$$= f(n/n) + \log_2 2 + \log_2 4 + \dots + \log_2(n/2) + \log_2 n$$

$$= 1 + 2 + 3 + \dots + \log_2 n$$

$$= \log_2 n (\log_2 n + 1)/2 = \Theta(\log^2 n)$$

## Solution via guessing

Guess the solution and verify it by substitution

Substitution also useful to find the constant multiplicative factors and lower-order terms

Example: f(n) = f(n-1) + n; guess  $f(n) = \Theta(n^2)$ Write  $f(n) = an^2 + g(n)$ , where  $g(n) = o(n^2)$

Substituting in the recurrence equation, we get:

$$an^2 + g(n) = a(n-1)^2 + g(n-1) + n$$

This equation simplifies to:

g(n) = g(n-1) + (1-2a)n + a

Choose a = 1/2 to make  $g(n) = o(n^2)$  possible

$g(n) = g(n-1) + 1/2 = n/2 - 1 \quad \{g(1) = -1/2, g(2) = 0\}$

The solution to the original recurrence then becomes

$f(n) = n^2/2 + g(n) = n^2/2 + n/2 - 1$

## Solution via a basic theorem

Theorem 3.1 (basic theorem for recurrences): Given f(n) = a f(n/b) + h(n); *a*, *b* constant, *h* an arbitrary function the asymptotic solution to the recurrence is

$$\begin{split} f(n) &= \Theta(n^{\log_b a}) & \text{if } h(n) = O(n^{\log_b a - \varepsilon}) \text{ for some } \varepsilon > 0 \\ f(n) &= \Theta(n^{\log_b a} \log n) & \text{if } h(n) = \Theta(n^{\log_b a}) \\ f(n) &= \Theta(h(n)) & \text{if } h(n) = \Omega(n^{\log_b a + \varepsilon}) \text{ for some } \varepsilon > 0 \end{split}$$

## 4 Models of Parallel Processing

Back to TOC

#### Chapter Goals

- Elaborate on the taxonomy of parallel processing from Chapter 1

- Introduce abstract models of shared and distributed memory

- Understand the differences between abstract models and real hardware

#### **Chapter Contents**

- 4.1. Development of Early Models

- 4.2. SIMD versus MIMD Architectures

- 4.3. Global versus Distributed Memory

- 4.4. The PRAM Shared-Memory Model

- 4.5. Distributed-Memory or Graph Models

- 4.6. Circuit Model & Physical Realizations

#### **Development of Early Models** 4.1

Thousands of processors were found in some computers as early as the 1960s

These architectures were variously referred to as

associative memories associative processors logic-in-memory machines

More recent names are

processor-in-memory and intelligent RAM

| Tab    | ole 4.1. | Entering the Se<br>Processing | econd Half-Century of | Associative      |

|--------|----------|-------------------------------|-----------------------|------------------|

| Decade | Events a | and Advances                  | Technology            | Performance      |

| 1940s  | Formula  | tion of need & conce          | pt Relays             |                  |

| 1950s  | Emerge   | nce of cell technologi        | ies Magnetic, Cryoger | nic Mega-bit-OPS |

| 1960s  | Introduc | tion of basic architec        | tures Transistors     |                  |

| 1970s  | Comme    | rcialization & applicat       | tions ICs             | Giga-bit-OPS     |

| 1980s  | Focus o  | n system/software is:         | sues VLSI             | Tera-bit-OPS     |

| 1990s  | Scalable | e & flexible architectu       | res ULSI, WSI         | Peta-bit-OPS?    |

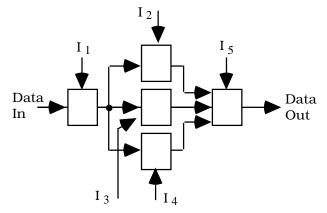

## Revisiting the Flynn-Johnson classification

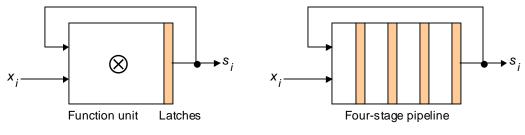

## MISD can be viewed as a flexible (programmable) pipeline

Fig. 4.2. Multiple instruction streams operating on a single data stream (MISD).

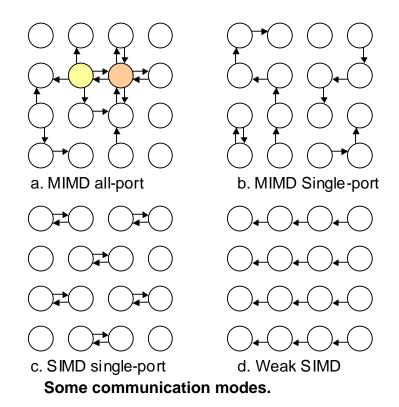

## 4.2 SIMD versus MIMD Architectures

Most early parallel machines were of SIMD type

Synchronous SIMD

To run data-dependent conditionals (if-then-else), first processors satisfying the condition are enabled, next the remainder are enabled for the "else" part

Critics of SIMD view the above as being wasteful

But: are buses less efficient than private cars, or is PC hardware wasted when you answer the phone?

Asynchronous SIMD = SPMD

Custom- versus commodity-chip SIMD

Most recent parallel machines are MIMD-type

MPP: massively or moderately parallel processor?

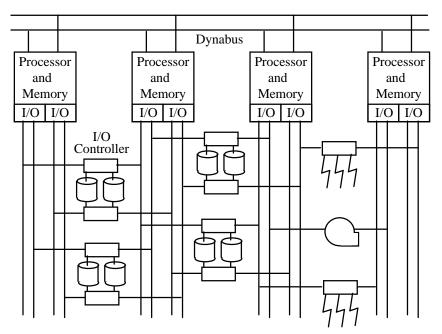

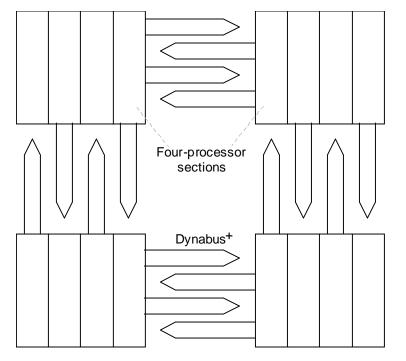

Tight versus loose coupling of processors

Tightly coupled: multiprocessors Loosely coupled: multicomputers Network or cluster of workstations (NOW, COW)

Hybrid: loosely coupled clusters, each tightly coupled

Message passing versus virtual shared memory

Shared memory is easier to program Message passing is more efficient

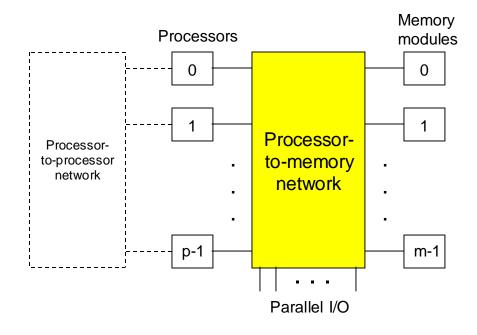

## 4.3 Global versus Distributed Memory

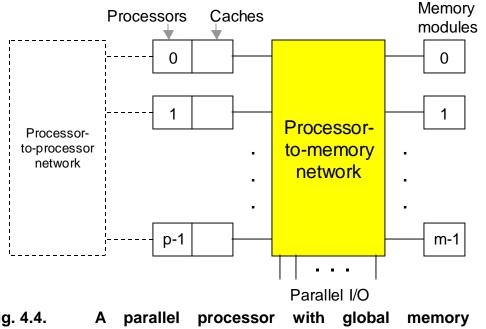

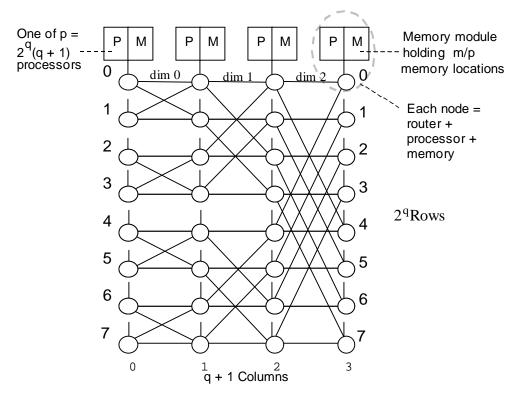

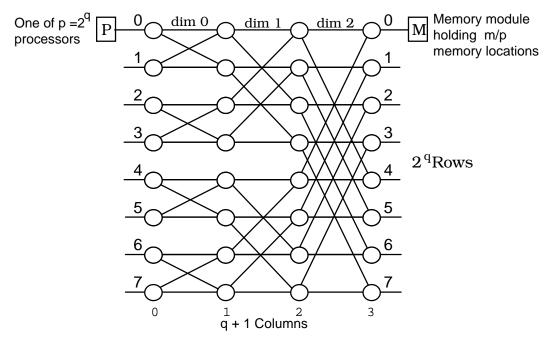

Fig. 4.3. A parallel processor with global memory.

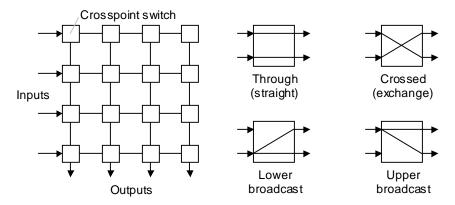

Example processor-to-memory/processor networks:

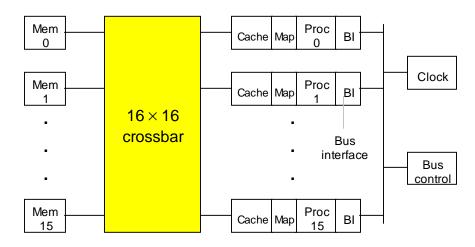

- 1. Crossbar;  $p \times m$  array of switches or crosspoints; cost too high for massively parallel systems

- 2. Single/multiple bus (complete or partial connectivity)

- Multistage interconnection network (MIN); cheaper than crossbar, more bandwidth than bus

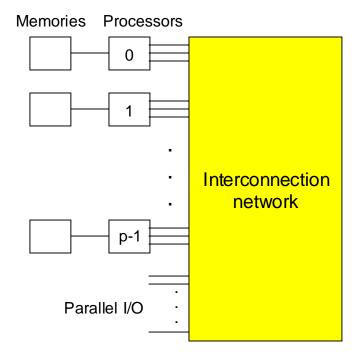

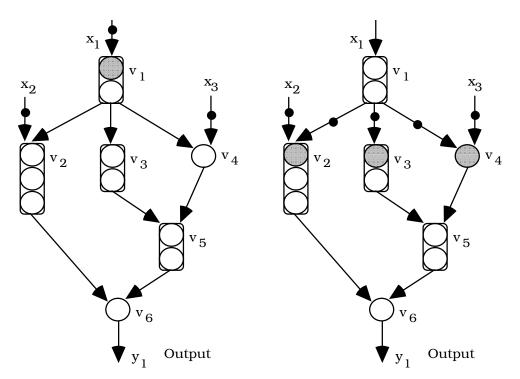

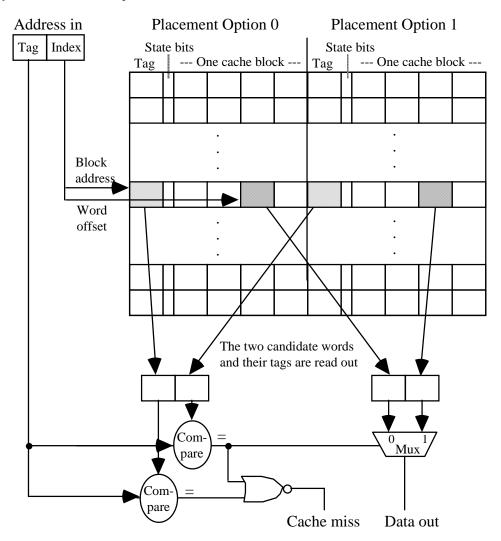

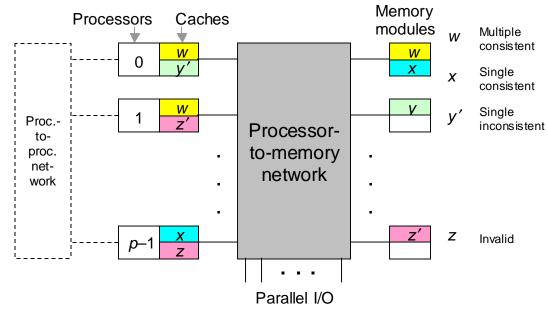

Fig. 4.4. A parallel processor with global memory and processor caches.

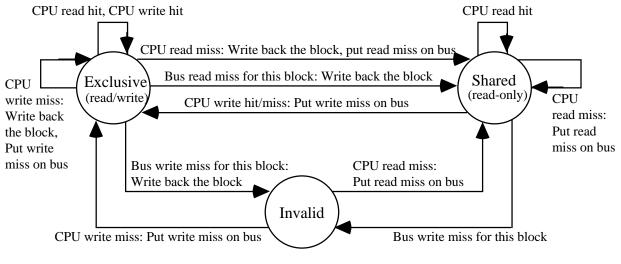

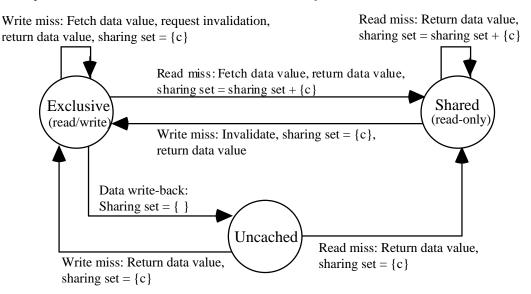

Solving the cache coherence problem

- 1. Do not cache any shared data

- Do not cache "writeable" shared data or allow only one cache copy

- 3. Use a cache coherence protocol (Chapter 18)

Fig. 4.5. A parallel processor with distributed memory.

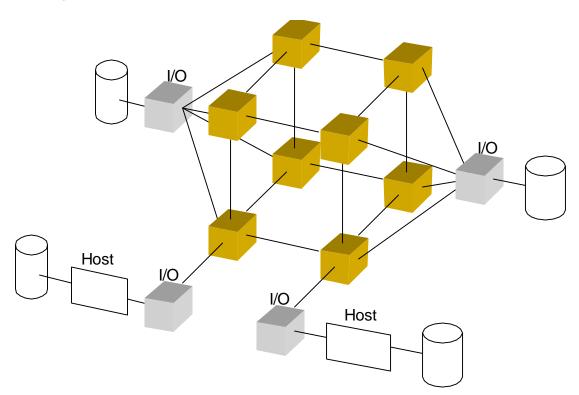

Examples networks for distributed memory machines

- 1. Crossbar; cost too high for massively parallel system

- 2. Single/multiple bus (complete or partial connectivity)

- 3. Multistage interconnection network (MIN)

- 4. Various direct networks (Section 4.5)

Terminology

- UMA Uniform memory access

- NUMA Nonuniform memory access

- COMA Cache-only memory architecture (aka all-cache)

## 4.4 The PRAM Shared-Memory Model

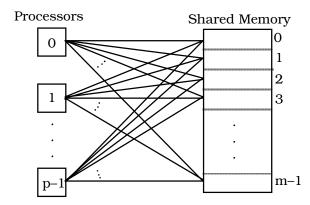

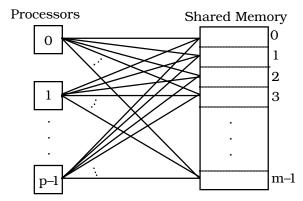

Fig. 4.6. Conceptual view of a parallel random-access machine (PRAM).

PRAM cycle

- 1. Processors access memory (usually different locations)

- 2. Processors perform a computation step

- 3. Processors store their results in memory

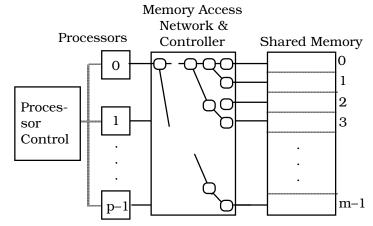

Fig. 4.7. PRAM with some hardware details shown.

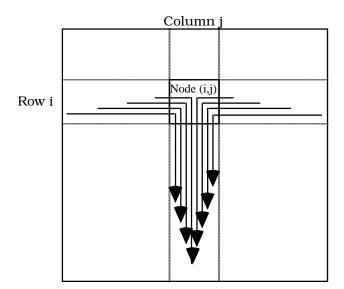

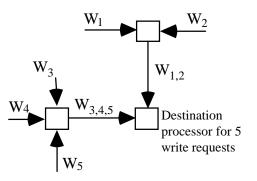

In practice, memory is divided into modules and simultaneous accesses to same module are disallowed

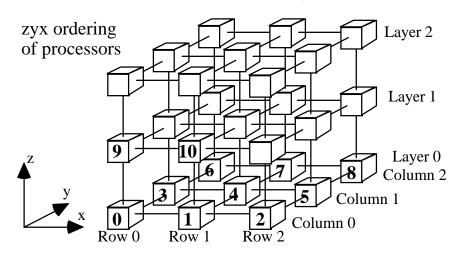

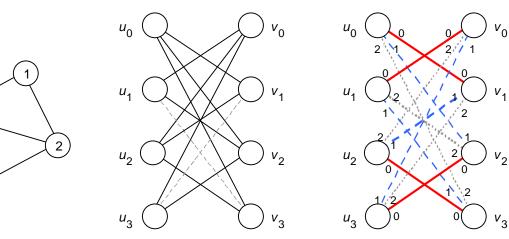

## 4.5 Distributed-Memory or Graph Models

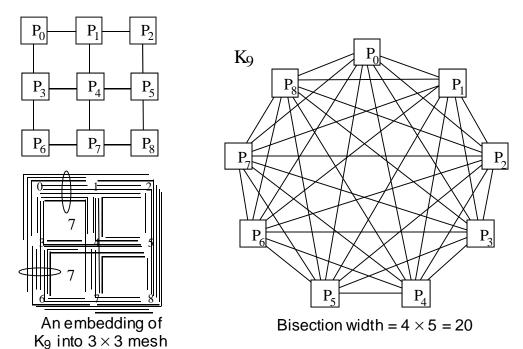

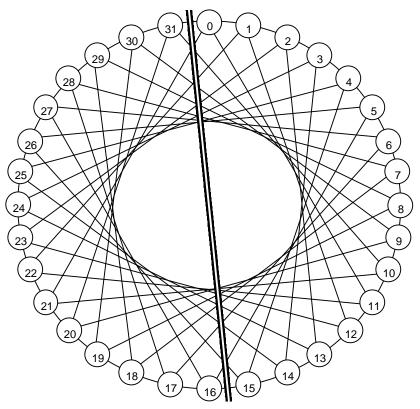

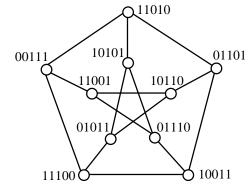

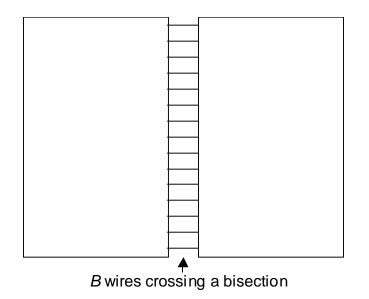

Parameters of interest for direct interconnection networks Diameter Bisection (band)width Node degree

Symmetry properties simplify algorithm development: Node or vertex symmetry Link or edge symmetry

| Network name(s)                  | Number<br>of nodes                    | Network<br>diameter  | Bisection width         | Node<br>degree | Local<br>links?  |

|----------------------------------|---------------------------------------|----------------------|-------------------------|----------------|------------------|

| 1D mesh (linear array)           | k                                     | <i>k</i> – 1         | 1                       | 2              | Yes              |

| 1D torus (ring, loop)            | k                                     | k/2                  | 2                       | 2              | Yes              |

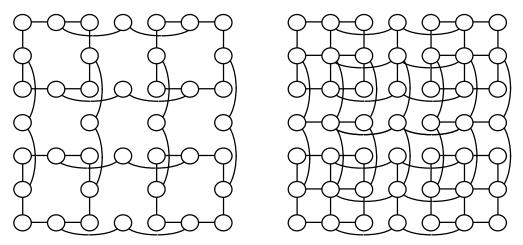

| 2D Mesh                          | k²                                    | 2k – 2               | k                       | 4              | Yes              |

| 2D torus ( <i>k</i> -ary 2-cube) | k²                                    | k                    | 2 <i>k</i>              | 4              | Yes <sup>1</sup> |

| 3D mesh                          | k <sup>3</sup>                        | 3 <i>k</i> – 3       | <b>k</b> <sup>2</sup>   | 6              | Yes              |

| 3D torus ( <i>k</i> -ary 3-cube) | k <sup>3</sup>                        | 3 <i>k</i> /2        | 2 <i>k</i> <sup>2</sup> | 6              | Yes <sup>1</sup> |

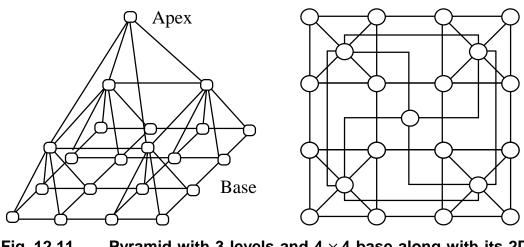

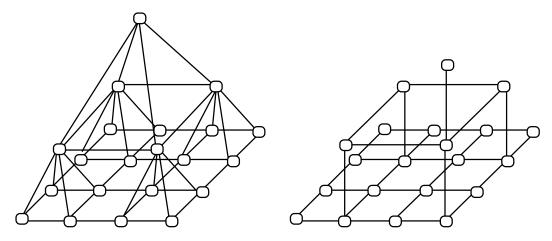

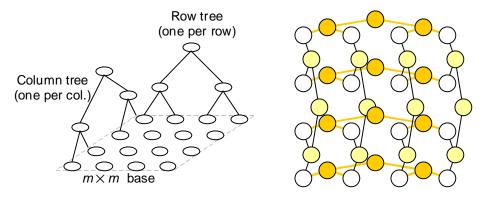

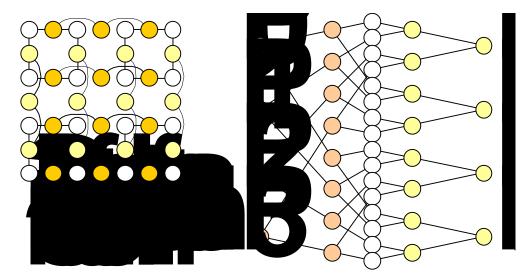

| Pyramid                          | (4 <i>k</i> <sup>2</sup> – 1)/3       | 2 log <sub>2</sub> k | 2 <i>k</i>              | 9              | No               |

| Binary tree                      | 2/-1                                  | 21-2                 | 1                       | 3              | No               |

| 4-ary hypertree                  | 2 <sup>/</sup> (2 <sup>/+1</sup> - 1) | 21                   | 2 <sup>/+1</sup>        | 6              | No               |

| Butterfly                        | $2^{\prime}(l+1)$                     | 21                   | 2′                      | 4              | No               |

| Hypercube                        | 21                                    | 1                    | 2 <sup>1–1</sup>        | 1              | No               |

| Cube-connected cycles            | 2//                                   | 21                   | 2 <sup>⊢</sup> 1        | 3              | No               |

| Shuffle-exchange                 | 21                                    | 2/-1                 | ≥ 2⊢1/I                 | 4 unidir.      | No               |

| De Bruijn                        | 2′                                    | 1                    | 2'/I                    | 4 unidir.      | No               |

## Table 4.2.Topological Parameters of Selected Interconnection<br/>Networks

<sup>1</sup> With folded layout.

Introduction to Parallel Processing: Algorithms and Architectures

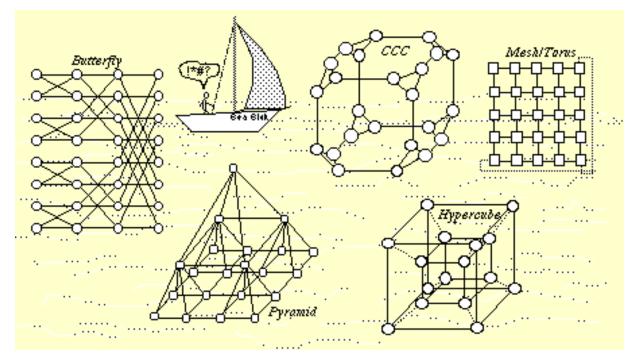

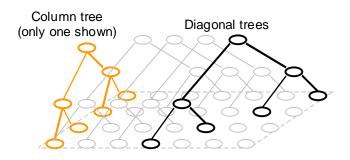

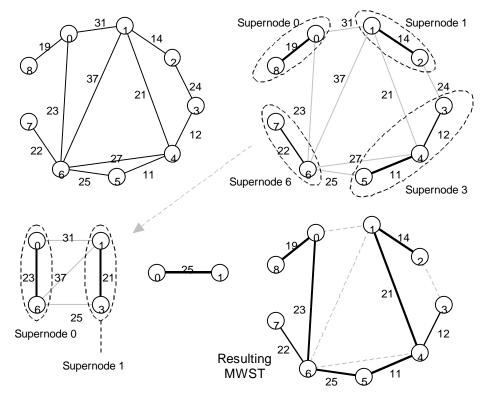

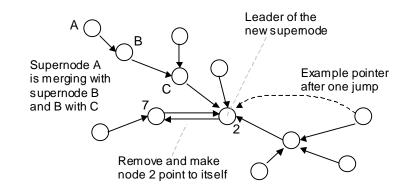

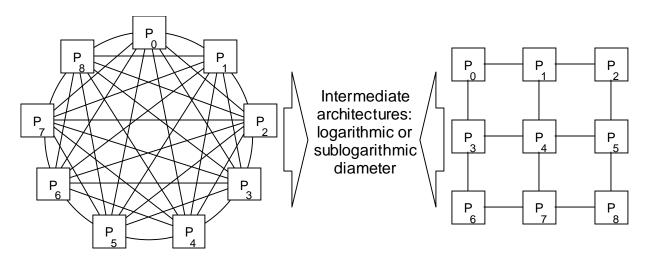

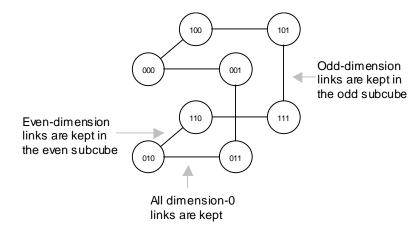

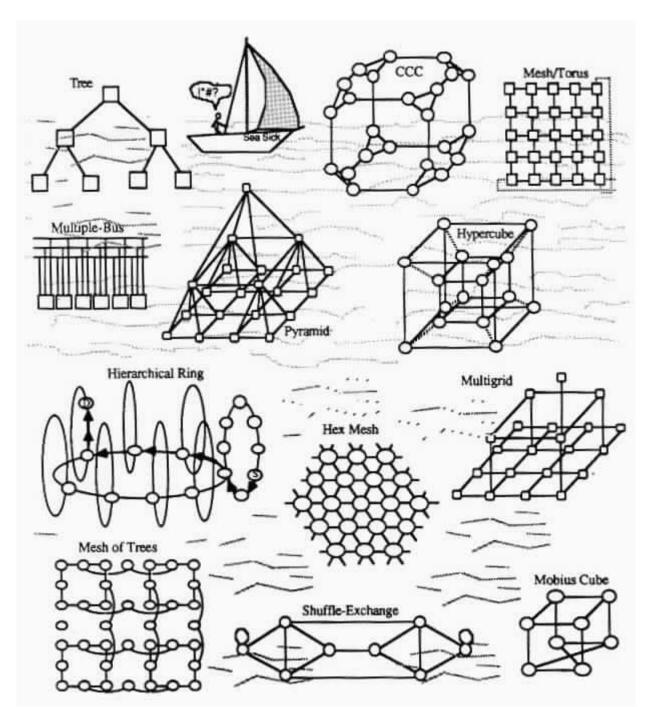

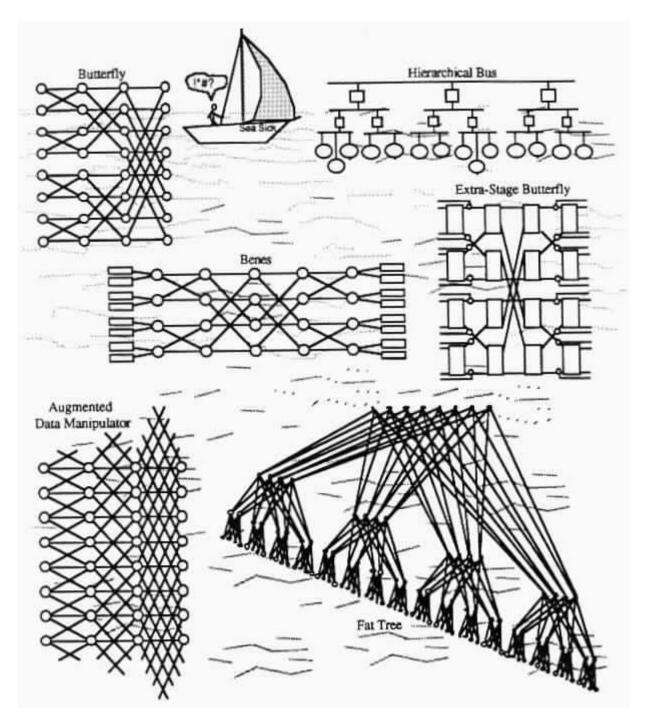

Fig. 4.8. The sea of interconnection networks.

Bus-based architectures are dominant in small-scale parallel systems.

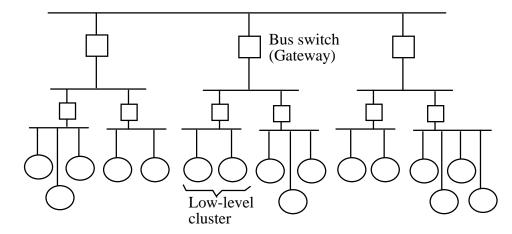

Fig. 4.9. Example of a hierarchical interconnection architecture.

Because each interconnection network requires its own algorithms, various abstract (architecture-independent) models have been suggested for such networks

## The LogP model

Characterizes an architecture with just four parameters:

- *L Latency* upper bound when a small message is sent from an arbitrary source to an arbitrary destination

- *o overhead*, defined as the length of time a processor is dedicated to transmission or reception of a message, thus being unable to do any other computation

- *g gap*, defined as the minimum time that must elapse between consecutive message transmissions or receptions by a single processor (1/*g* is the available per-processor communication bandwidth)

- *P Processor* multiplicity (*p* in our notation)

If LogP is in fact an accurate model for capturing the effects of communication in parallel processors, then details of interconnection network do not matter

## **The BSP model** (bulk-synchronous parallel)

Hides the communication latency altogether through a specific parallel programming style, thus making the network topology irrelevant

Synchronization of processors occurs once every L time steps, where L is a periodicity parameter

Computation consists of a sequence of supersteps

In a given superstep, each processor performs a task consisting of local computation steps, message transmissions, and message receptions

Data received in messages will not be used in the current superstep but rather beginning with the next superstep

After each period of *L* time units, a global check is made to see if the current superstep has been completed

If so, then the processors move on to executing the next superstep

Else, the next period of length *L* is allocated to the unfinished super-step

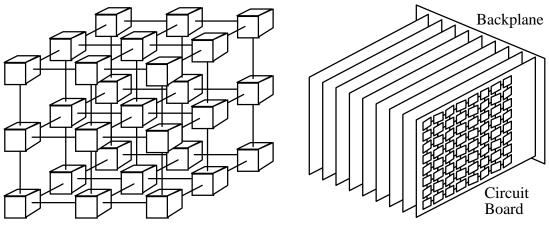

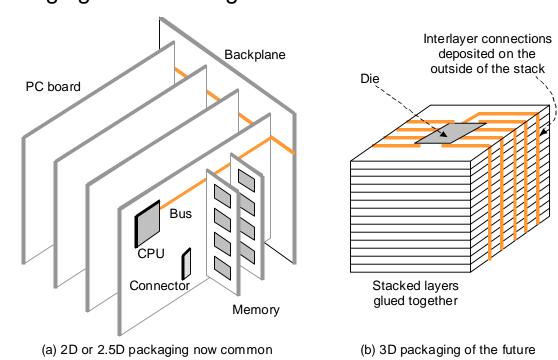

## 4.6 Circuit Model and Physical Realizations

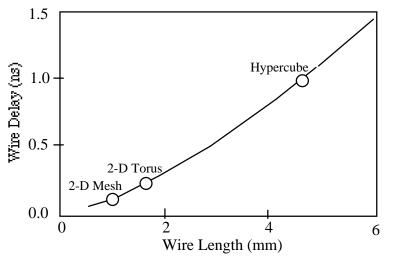

Fig. 4.10. Intrachip wire delay as a function of wire length.

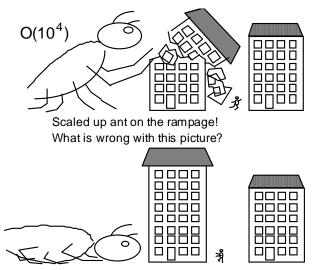

Scaled up ant collapses under own weight.

Fig. 4.11. Pitfalls of scaling up.

## Part II Extreme Models

## Back to TOC

## Part Goals

- Study two extreme parallel machine models

- Abstract PRAM shared-memory model ignores implementation issues altogether

- Concrete circuit model accommodates details like circuit depth and layout area

- Prepare for everything else that falls in between the two extremes

Part Contents

- Chapter 5: PRAM and Basic Algorithms

- Chapter 6: More Shared-Memory Algorithms

- Chapter 7: Sorting and Selection Networks

- Chapter 8: Other Circuit-Level Examples

## 5 **PRAM and Basic Algorithms**

### Back to TOC

#### **Chapter Goals**

- Define PRAM and its various submodels

- Show PRAM to be a natural extension of the sequential computer (RAM)

- Develop five important parallel algorithms that can serve as building blocks (more algorithms in the next chapter)

## **Chapter Contents**

- 5.1. PRAM Submodels and Assumptions

- 5.2. Data Broadcasting

- 5.3. Semigroup or Fan-in Computation

- 5.4. Parallel Prefix Computation

- 5.5. Ranking the Elements of a Linked List

- 5.6. Matrix Multiplication

#### 5.1 **PRAM Submodels and Assumptions**

Conceptual view of a parallel random-access machine Fig. 4.6. (PRAM).

Processor *i* can do the following in 3 phases of one cycle:

- Fetch an operand from address  $s_i$  in shared memory 1.

- 2. Perform computations on data held in local registers

- 3. Store a value into address  $d_i$  in shared memory

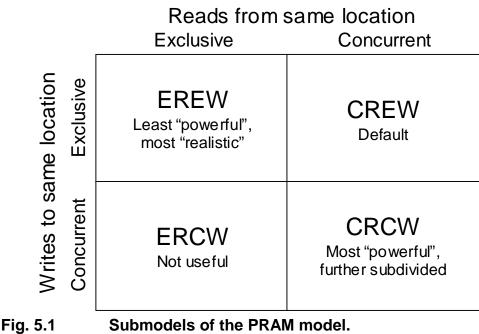

**CRCW PRAM** is classified according to how concurrent writes are handled. These submodels are all different from each other and from EREW and CREW.

- Undefined: In case of multiple writes, the value written is undefined (CRCW-U)

- Detecting: A code representing "detected collision" is written (CRCW-D)

- Common: Multiple writes allowed only if all store the same value (CRCW-C); this is sometimes called the consistent-write submodel

- Random: The value written is randomly chosen from those offered (CRCW-R)

- Priority: The processor with the lowest index succeeds in writing (CRCW-P)

- Max/Min: The largest/smallest of the multiple values is written (CRCW-M)

Reduction: The arithmetic sum (CRCW-S), logical AND (CRCW-A), logical XOR (CRCW-X), or another combination of the multiple values is written.

Ordering the submodels by computational power:

EREW < CREW < CRCW-D < CRCW-C < CRCW-R < CRCW-P **Theorem 5.1:** A *p*-processor CRCW-P (priority) PRAM can be simulated (emulated) by a *p*-processor EREW PRAM with a slowdown factor of  $\Theta(\log p)$ .

Intuitive justification for concurrent read emulation:

Write the *p* desired addresses in a list Sort the list of addresses in ascending order Remove all duplicate addresses Access data from desired addresses Replicate data via parallel prefix computation

Each of these steps requires constant or O(log *p*) time

### Some elementary PRAM computations

Initializing an *n*-vector (base address = B) to all 0s:

for j = 0 to  $\lceil n/p \rceil - 1$  processor *i* do if jp + i < n then M[B + jp + i] := 0endfor

Adding two *n*-vectors and storing the results in a third (base addresses B', B'', B)

Convolution of two *n*-vectors:  $W_k = \sum_{i+j=k} U_i \times V_j$ (base addresses  $B_W$ ,  $B_U$ ,  $B_V$ )

### 5.2 Data Broadcasting

Broadcasting is built-in for the CREW and CRCW models

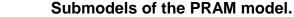

EREW broadcasting: make p copies of the data in a broadcast vector B

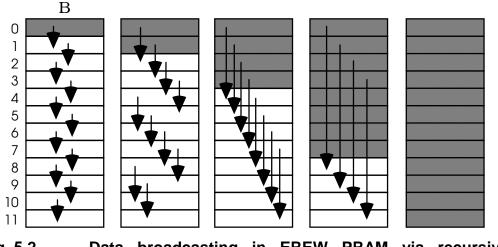

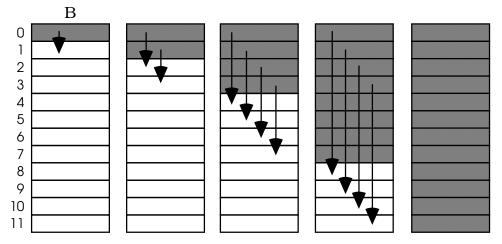

Fig. 5.2. Data broadcasting in EREW PRAM via recursive doubling.

Fig. 5.3. EREW PRAM data broadcasting without redundant copying.

EREW PRAM algorithm for broadcasting by Processor *i* Processor *i* write the data value into B[0] s := 1while s < p Processor *j*,  $0 \le j < \min(s, p - s)$ , do Copy B[j] into B[j + s] s := 2sendwhile Processor *j*,  $0 \le j < p$ , read the data value in B[j]

<u>EREW PRAM algorithm for all-to-all broadcasting</u> Processor *j*,  $0 \le j < p$ , write own data value into *B*[*j*] for *k* = 1 to *p* – 1 Processor *j*,  $0 \le j < p$ , do Read the data value in *B*[(*j* + *k*) mod *p*] endfor

Both of the preceding algorithms are time-optimal (shared memory is the only communication mechanism and each processor can read but one value per cycle) In the following naive sorting algorithm, processor j determines the rank R[j] of its data element S[j] by examining all the other data elements; it then writes S[j] in element R[j] of the output (sorted) vector

Naive EREW PRAM sorting algorithm (using all-to-all broadcasting) Processor j,  $0 \le j < p$ , write 0 into R[j]for k = 1 to p - 1 Processor j,  $0 \le j < p$ , do  $l := (j + k) \mod p$ if S[l] < S[j] or S[l] = S[j] and l < jthen R[j] := R[j] + 1endif endfor Processor j,  $0 \le j < p$ , write S[j] into S[R[j]]

This O(p)-time algorithm is far from being optimal

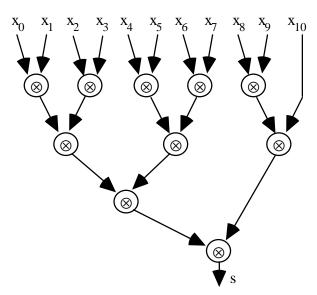

### 5.3 Semigroup or Fan-in Computation

This computation is trivial for a CRCW PRAM of the reduction variety if the reduction operator happens to be  $\otimes$

Fig. 5.4. Semigroup computation in EREW PRAM.

EREW PRAM semigroup computation algorithm Processor j,  $0 \le j < p$ , copy X[j] into S[j] s := 1while s < p Processor j,  $0 \le j , do$  $<math>S[j + s] := S[j] \otimes S[j + s]$  s := 2sendwhile Broadcast S[p - 1] to all processors

Time-optimal algorithm (CRCW can do better: prob. 5.16)

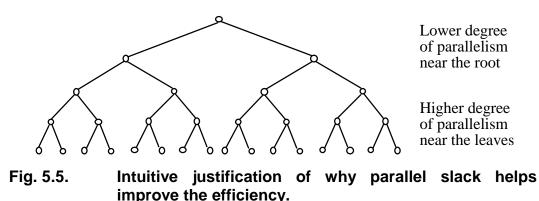

Speed-up =  $p/\log_2 p$ Efficiency = Speed-up/p =  $1/\log_2 p$ Utilization =  $\frac{W(p)}{pT(p)} \cong \frac{(p-1)+(p-2)+(p-4)+\dots+(p-p/2)}{p\log_2 p} \cong 1 - 1/\log_2 p$  Semigroup computation with each processor holding n/p data elements:

Each processor combine its sublist n/p steps Do semigroup computation on results  $\log_2 p$  steps

Speedup(n, p) =

$$\frac{n}{n/p + 2\log_2 p} = \frac{p}{1 + (2p\log_2 p)/n}$$

Efficiency(n, p) = Speedup/p =  $\frac{1}{1 + (2p\log_2 p)/n}$

For  $p = \Theta(n)$ , the speedup of  $\Theta(n/\log n)$  is sublinear The efficiency in this case is  $\Theta(n/\log n)/\Theta(n) = \Theta(1/\log n)$

Limit the number of processors to  $p = O(n/\log n)$ :

Speedup(*n*, *p*) =  $n/O(\log n) = \Omega(n/\log n) = \Omega(p)$ Efficiency(*n*, *p*) =  $\Theta(1)$

Using fewer processors than tasks = parallel slack

### Inner product of two *n*-vectors, storing the result in *s* Base addresses *B'* and *B''*, auxiliary vector of length *p* with base address *B* for j = 0 to $\lceil n/p \rceil - 1$ processor *i* do if jp + i < n then load M[B' + jp + i]multiply by M[B'' + jp + i]add to M[B + i]endif find sum or the *p*-vector, store the result in *s* endfor

$T(n, p) = O(n/p + \log p)$

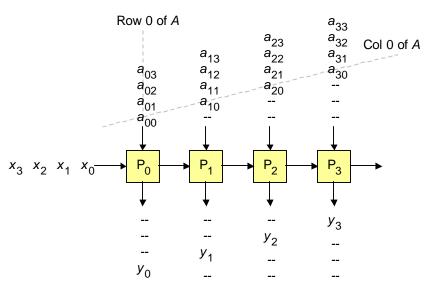

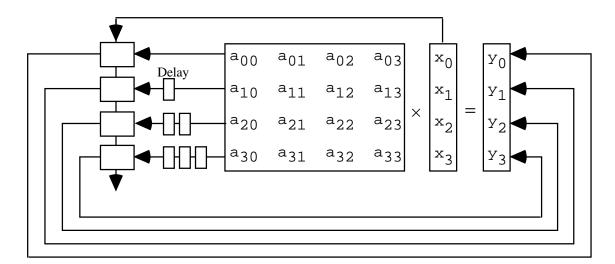

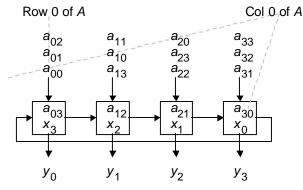

Matrix-by-vector multiplication  $U := M \times V$

$U_i$  is the inner product of row *i* of *M* and *V*

$T(n, p) = O(n^2/p + n \log p))$

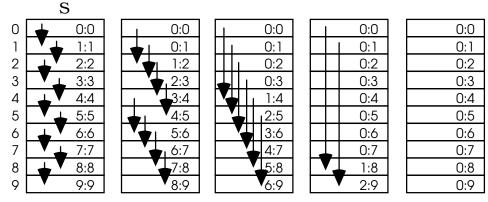

### 5.4 Parallel Prefix Computation

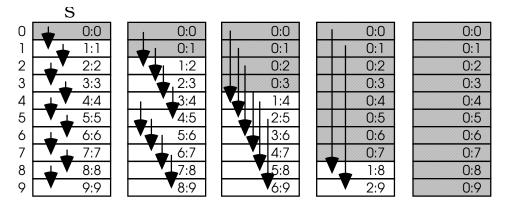

Fig. 5.6. Parallel prefix computation in EREW PRAM via recursive doubling.

### Two other solutions, based on divide and conquer

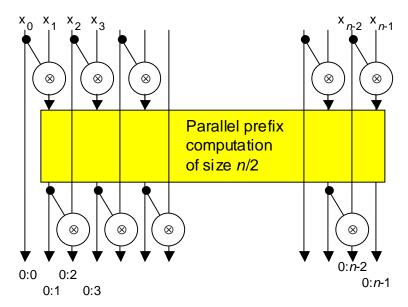

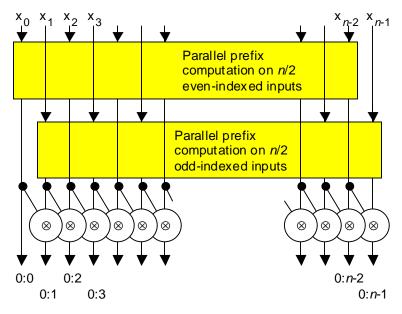

Fig. 5.7 Parallel prefix computation using a divide-and-conquer scheme.

Assume n = p $T(p) = T(p/2) + 2 = 2 \log_2 p$

Fig. 5.8. Another divide-and-conquer scheme for parallel prefix computation.

Assume n = p $T(p) = T(p/2) + 1 = \log_{10}$

$T(p) = T(p/2) + 1 = \log_2 p$  Requires commutativity

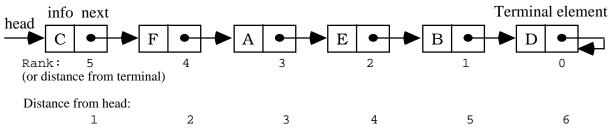

### 5.5 Ranking the Elements of a Linked List

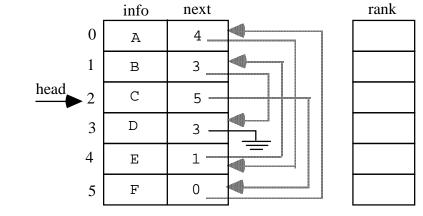

Fig. 5.9. Example linked list and the ranks of its elements.

Fig. 5.10. PRAM data structures representing a linked list and the ranking results.

List-ranking appears to be hopelessly sequential

However, we can in fact use a recursive doubling scheme to determine the rank of each element in optimal time

There exist other problems that seem unparallizable

This is why intuition can be misleading when it comes to determining which computation is or is not efficiently parallelizable (i.e., it is or is not in NC)

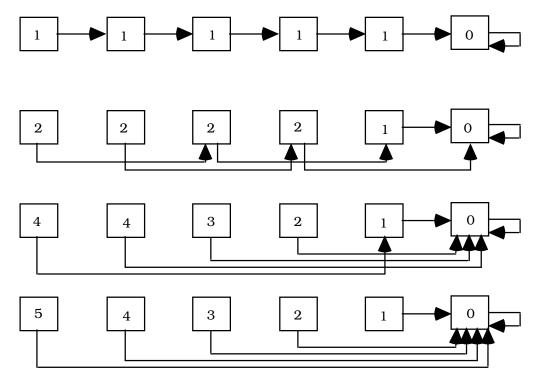

Fig. 5.11. Element ranks initially and after each of the three iterations.

PRAM list ranking algorithm (via pointer jumping) Processor j,  $0 \le j < p$ , do {initialize the partial ranks} if next[j] = jthen rank[j] := 0else rank[j] := 1endif while  $rank[next[head]] \ne 0$  Processor j,  $0 \le j < p$ , do rank[j] := rank[j] + rank[next[j]] next[j] := next[next[j]]endwhile

Which PRAM submodel is implicit in this algorithm?

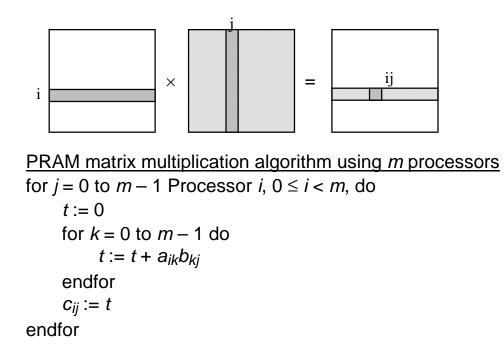

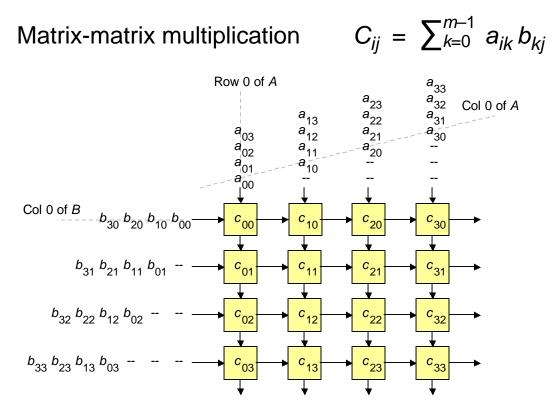

### 5.6 Matrix Multiplication

For

$$m \times m$$

matrices,  $C = A \times B$  means:  $c_{ij} = \sum_{k=0}^{m-1} a_{ik} b_{kj}$

Sequential matrix multiplication algorithm for i = 0 to m - 1 do for j = 0 to m - 1 do t := 0for k = 0 to m - 1 do  $t := t + a_{ik}b_{kj}$ endfor  $c_{ij} := t$ endfor endfor  $i = 1 + a_{ik}b_{kj} = 1$   $i = 1 + a_{ik}b_{kj} = 1$  $i = 1 + a_{ik}b_{kj} = 1$

Fig. 5.12. PRAM matrix multiplication;  $p = m^2$  processors.

PRAM matrix multiplication algorithm using  $m^2$  processors Processor (*i*, *j*),  $0 \le i, j < m$ , do begin t := 0for k = 0 to m - 1 do  $t := t + a_{ik}b_{kj}$ endfor  $c_{ij} := t$

end

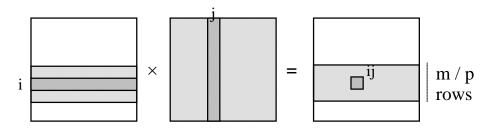

Both of the preceding algorithms are efficient and provide linear speedup

Using fewer than m processors: each processor computes m/p rows of C

This solution inefficient for NUMA parallel architectures Each element of B is fetched m/p times

For each such access, only two arith ops are performed

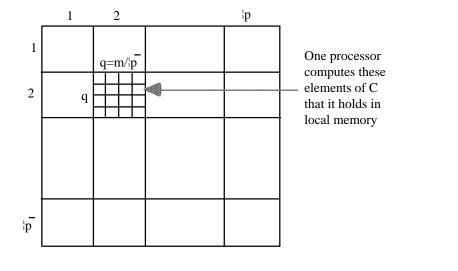

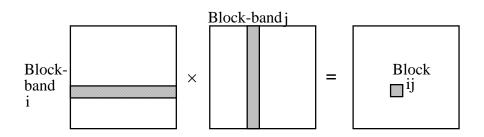

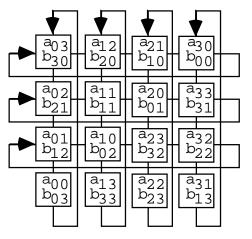

### Block matrix multiplication

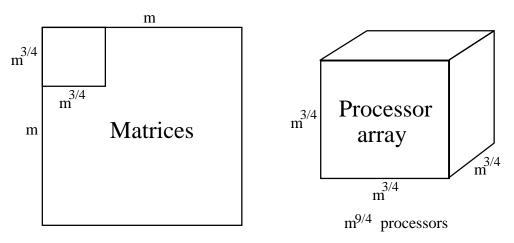

Fig. 5.13. Partitioning the matrices for block matrix multiplication.

Each multiply-add computation on  $q \times q$  blocks needs

$2q^2 = 2m^2/p$  memory accesses to read the blocks

$2q^3$  arithmetic operations

So, *q* arithmetic operations are done per memory access

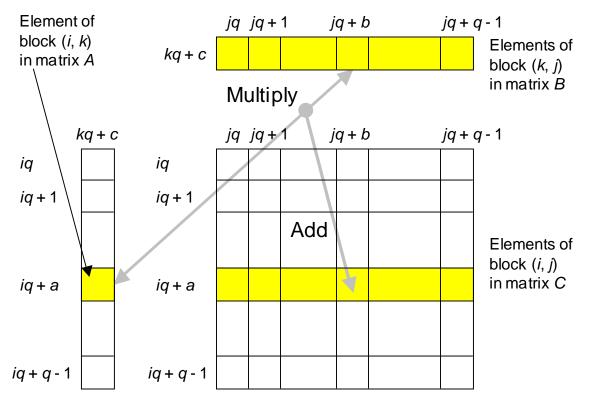

We assume that processor (i, j) has local memory to hold

Block (*i*, *j*) of the result matrix  $C(q^2 \text{ elements})$

One block-row of B; say row kq + c of block (k, j) of B

(Elements of *A* can be brought in one at a time)

For example, as element in row iq + a of column kq + c in block (*i*, *k*) of *A* is brought in, it is multiplied in turn by the locally stored *q* elements of *B*, and the results added to the appropriate *q* elements of *C*  Introduction to Parallel Processing: Algorithms and Architectures

Fig. 5.14. How Processor (*i*, *j*) operates on an element of *A* and one block-row of *B* to update one block-row of *C*.

On the Cm<sup>\*</sup> NUMA-type shared-memory multiprocessor, this block algorithm exhibited good, but sublinear, speedup

p = 16, speed-up = 5 in multiplying  $24 \times 24$  matrices;

improved to 9 (11) for  $36 \times 36$  ( $48 \times 48$ ) matrices

The improved locality of block matrix multiplication can also improve the running time on a uniprocessor, or distributed shared-memory multiprocessor with caches

Reason: higher cache hit rates.

# 6 More Shared-Memory Algorithms

Back to TOC

### Chapter Goals

- Develop PRAM algorithms for more complex problems (background on corresponding sequential algorithms also presented)

- Discuss some practical implementation issues such as data distribution

### **Chapter Contents**

- 6.1. Sequential Rank-Based Selection

- 6.2. A Parallel Selection Algorithm

- 6.3. A Selection-Based Sorting Algorithm

- 6.4. Alternative Sorting Algorithms

- 6.5. Convex Hull of a 2D Point Set

- 6.6. Some Implementation Aspects

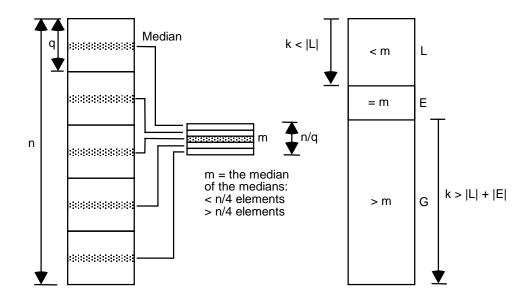

### 6.1 Sequential Rank-Based Selection

Selection: Find the (a) *k*th smallest among *n* elements Naive solution through sorting, O(*n* log *n*) time Linear-time sequential algorithm can be developed

Sequential rank-based selection algorithm select(S, k)

if |S| < q {q is a small constant} then sort S and return the kth smallest element of S else divide S into |S|/q subsequences of size q Sort each subsequence and find its median Let the |S|/q medians form the sequence T endif

2.

$$m = select(T, |T|/2)$$

{find the median m of the |S|/q medians}

- 3. Create 3 subsequences

- *L*: Elements of S that are < m

- *E*: Elements of *S* that are = m

- G: Elements of S that are > m

4. if  $|L| \ge k$ then return *select*(*L*, *k*) else if  $|L| + |E| \ge k$ then return *m* else return *select*(*G*, k - |L| - |E|) endif

Analysis:

$$T(n) = T(n/q) + T(3n/4) + cn$$

Let  $q = 5$ ; we guess the solution to be  $T(n) = dn$

$dn = dn / 5 + 3dn / 4 + cn \implies d = 20c$

## Examples for sequential selection

from an input list of size n = 25 using q = 5

|                | ←              | n/q subli    | ists of $q$ elements                                 |

|----------------|----------------|--------------|------------------------------------------------------|

| ${\mathcal S}$ | 645671         | 5382         | 1 0 3 4 5 6 2 1 7 1 4 5 4 9 5                        |

| T<br>m         | 6              | 3            | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

|                | 1 2 1 0 2 1 1  | 33           | 6 4 5 6 7 5 8 4 5 6 7 4 5 4 9 5                      |

|                | <br>L          | <br>E        | G                                                    |

|                | <i>L</i>   = 7 | <i>E</i>  =2 | <i>G</i>   = 16                                      |

To find the 5th smallest element in S, select the 5th smallest element in L

| S      | 1_2 | 2 1 0 2 1 | 1      |           |

|--------|-----|-----------|--------|-----------|

| T<br>m |     | 1         | 1<br>1 |           |

|        | 0   | 1 1 1 1   | 2 2    |           |

|        | -   |           |        |           |

|        | L   | E         | G      | Answer: 1 |

The 9th smallest element of S is 3

The 13th smallest element of S is found by selecting the 4th smallest element in G

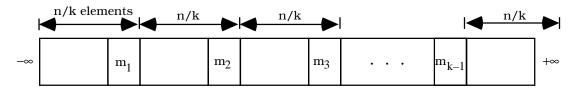

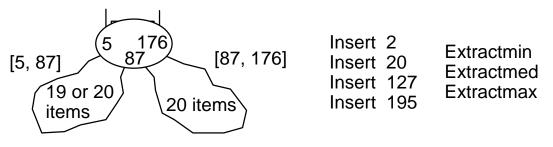

### 6.2 A Parallel Selection Algorithm

Parallel rank-based selection algorithm PRAMselect(S, k, p)

- 1. if |S| < 4then sort S and return the kth smallest element of S elsebroadcast |S| to all p processors divide S into p subsequences  $S^{(j)}$  of size |S|/pProcessor *j*,  $0 \le j < p$ , compute  $T_j := select(S_{ij}, |S_{ij}|/2)$ endif 2. m = PRAMselect(T, |T|/2, p) {median of the medians} Broadcast *m* to all processors and create 3 subsequences 3. *L*: Elements of S that are < m *E*: Elements of S that are = mG: Elements of S that are > m4. if  $|L| \ge k$ then return *PRAMselect*(L, k, p) else if  $|L| + |E| \ge k$

- then return *m* else return *PRAMselect*(*G*, k - |L| - |E|, *p*) endif

**Analysis:** Let  $p = n^{1-x}$ , with x > 0 a known constant

e.g.,

$$x = 1/2 \implies p = \sqrt{n}$$

$T(n, p) = T(n^{1-x}, p) + T(3n/4, p) + cn^{x} = O(n^{x})$

Speed-up $(n, p) = \Theta(n)/O(n^{x}) = \Omega(n^{1-x}) = \Omega(p)$

Efficiency =  $\Omega(1)$

What if x = 0, i.e., we use p = n processors for an *n*-input selection problem?

### 6.3 A Selection-Based Sorting Algorithm

Fig. 6.1. Partitioning of the sorted list for selection-based sorting.

Parallel selection-based sort PRAMselectionsort(S, p)

- 1. if |S| < k then return *quicksort*(*S*)

- 2. for *i* = 1 to *k* − 1 do *m<sub>j</sub>* := *PRAMselect*(*S*, *i*|*S*|/*k*, *p*) {for notational convenience, let *m*<sub>0</sub> := -∞; *m<sub>k</sub>* := +∞} endfor

3. for *i* = 0 to *k* = 1 do

- 3. for i = 0 to k 1 do make the sublist  $T^{(i)}$  from elements of S in  $(m_i, m_{i+1})$ endfor

- 4. for i = 1 to k/2 do in parallel PRAMselectionsort(T(i), 2p/k)  $\{p/(k/2) \text{ processors used for each}$ of the k/2 subproblems} endfor

- 5. for i = k/2 + 1 to k do in parallel  $PRAMselectionsort(T^{(i)}, 2p/k)$ endfor

**Analysis:**  $p = n^{1-x}$ , with x > 0 a known constant,  $k = 2^{1/x}$   $T(n, p) = 2T(n/k, 2p/k) + cn^x = O(n^x \log n)$ Why can't all k subproblems be solved in step 4 at once? Speedup $(n, p) = \Omega(n \log n) / O(n^x \log n) = \Omega(n^{1-x}) = \Omega(p)$ Efficiency = Speedup /  $p = \Omega(1)$ Work $(n, p) = pT(n, p) = \Theta(n^{1-x}) O(n^x \log n) = O(n \log n)$ Our asymptotic analysis is valid for x > 0 but not for x = 0; i.e., *PRAMselectionsort* does not allow us to sort p keys in optimal O(log p) time

#### **Example:**

S: 6456715382103456217045495 Threshold values:

$m_{0} = -\infty$   $m_{1} = PRAMselect(S, 6, 5) = 2$   $m_{1} = PRAMselect(S, 13, 5) = 4$   $m_{2} = PRAMselect(S, 13, 5) = 4$   $m_{3} = PRAMselect(S, 19, 5) = 6$   $m_{4} = +\infty$   $T: - - - 2 \begin{vmatrix} - - - - 4 \end{vmatrix} - - - - 6 \begin{vmatrix} - - - - - 4 \end{vmatrix}$   $T: - - - 2 \begin{vmatrix} - - - - 4 \end{vmatrix} - - - - 6 \begin{vmatrix} - - - - - 4 \end{vmatrix}$   $T: - - - 5 \begin{vmatrix} - - - - 4 \end{vmatrix}$

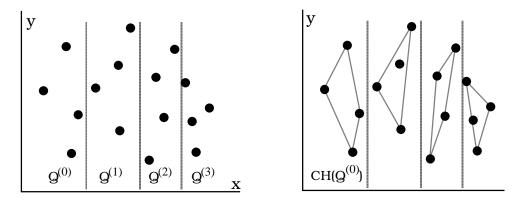

### 6.4 Alternative Sorting Algorithms

Sorting via random sampling

Given a large list S of inputs, a random sample of the elements can be used to find *k* comparison thresholds

In fact, it is easier if we pick k = p, so that each of the resulting subproblems is handled by a single processor.

Assume  $p \ll \sqrt{n}$ :

Parallel randomized sort *PRAMrandomsort*(*S*, *p*)

- 1. Processor *j*,  $0 \le j < p$ , pick  $|S|/p^2$  random samples of its |S|/p elements and store them in its corresponding section of a list *T* of length |S|/p

- 2. Processor 0 sort the list *T* {the comparison threshold  $m_i$  is the  $(i |S| / p^2)$ th element of *T*}

- 3. Processor *j*,  $0 \le j < p$ , store its elements falling in  $(m_i, m_{i+1})$  into  $T^{(i)}$

- 4. Processor *j*,  $0 \le j < p$ , sort the sublist  $T^{(j)}$

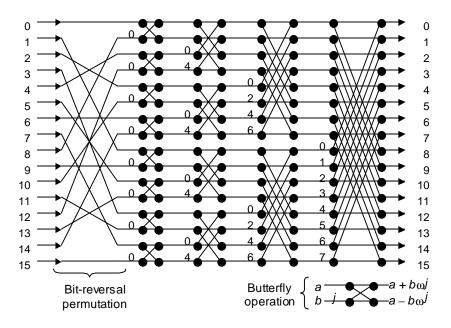

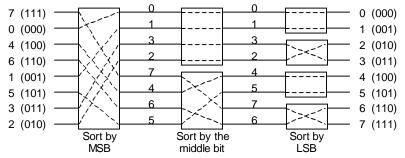

### Parallel radixsort

In binary version of *radixsort*, we examine every bit of the *k*-bit keys in turn, starting from the LSB

In Step *i*, bit *i* is examined,  $0 \le i < k$

Records are stably sorted by the value of the *i*th key bit

Example (keys are followed by their binary representations in parentheses):

| Input<br>list | Sort by<br>LSB | Sort by middle bit | Sort by<br>MSB |

|---------------|----------------|--------------------|----------------|

| 5 (101)       | 4 (100)        | 4 (100)            | 1 (001)        |

| 7 (111)       | 2 (010)        | 5 (101)            | 2 (010)        |

| 3 (011)       | <u>2 (010)</u> | <u>1 (001)</u>     | 2 (010)        |

| 1 (001)       | 5 (101)        | 2 (010)            | <u>3 (011)</u> |

| 4 (100)       | 7 (111)        | 2 (010)            | 4 (100)        |

| 2 (010)       | 3 (011)        | 7 (111)            | 5 (101)        |

| 7 (111)       | 1 (001)        | 3 (011)            | 7 (111)        |

| 2 (010)       | 7 (111)        | 7 (111)            | 7 (111)        |

### Performing the required data movements

| Input<br>list |   | Diminished prefix sums | Bit 0 | Prefix sums<br>plus 2 | Shifted<br>list |

|---------------|---|------------------------|-------|-----------------------|-----------------|

| 5 (101)       | 0 | _                      | 1     | 1 + 2 = 3             | 4 (100)         |

| 7 (111)       | 0 | _                      | 1     | 2 + 2 = 4             | 2 (010)         |

| 3 (011)       | 0 | _                      | 1     | 3 + 2 = 5             | <u>2 (010)</u>  |

| 1 (001)       | 0 | _                      | 1     | 4 + 2 = 6             | 5 (101)         |

| 4 (100)       | 1 | 0                      | 0     | _                     | 7 (111)         |

| 2 (010)       | 1 | 1                      | 0     | —                     | 3 (011)         |

| 7 (111)       | 0 | _                      | 1     | 5 + 2 = 7             | 1 (001)         |

| 2 (010)       | 1 | 2                      | 0     | _                     | 7 (111)         |

The running time consists mainly of the time to perform 2k parallel prefix computations: O(log *p*) for *k* constant

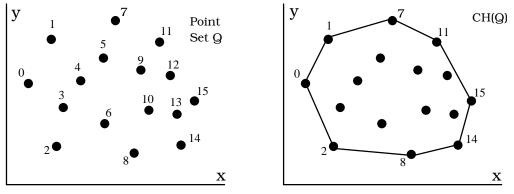

### 6.5 Convex Hull of a 2D Point Set

Fig. 6.2. Defining the convex hull problem.

Best sequential algorithm for p points:  $\Omega(p \log p)$  steps

Fig. 6.3. Illustrating the properties of the convex hull.

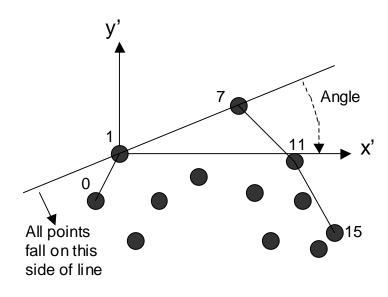

### Parallel convex hull algorithm PRAMconvexhull(S, p)

- 1. Sort point set by *x* coordinates

- 2. Divide sorted list into  $\sqrt{p}$  subsets  $Q^{(i)}$  of size  $\sqrt{p}$ ,  $0 \le i < \sqrt{p}$

- 3. Find convex hull of each subset  $Q^{(i)}$  using  $\sqrt{p}$  processors

- 4. Merge  $\sqrt{p}$  convex hulls CH( $Q^{(i)}$ ) into overall hull CH(Q)

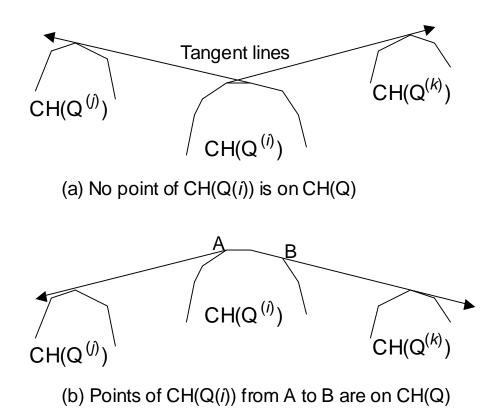

Fig. 6.4. Multiway divide and conquer for the convex hull problem.

Fig. 6.5. Finding points in a partial hull that belong to the combined hull.

Analysis:

$$T(p, p) = T(p^{1/2}, p^{1/2}) + c \log p \cong 2c \log p$$

The initial sorting time is also  $O(\log p)$

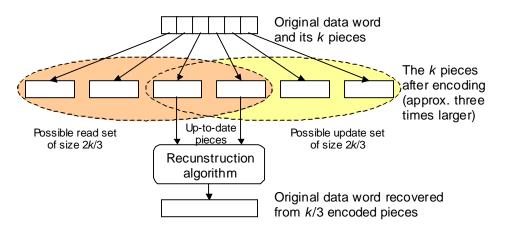

### 6.6 Some Implementation Aspects

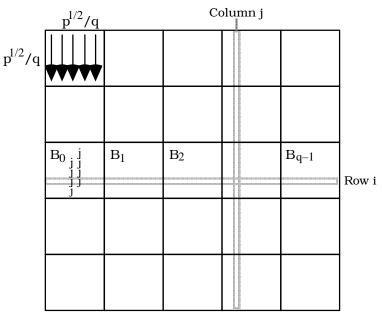

EREW-PRAM: Any *p* locations accessible by *p* processors Realistic: *p* locations must be in different memory modules

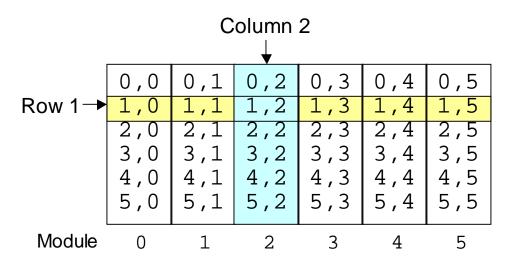

Fig. 6.6. Matrix storage in column-major order to allow concurrent accesses to rows.

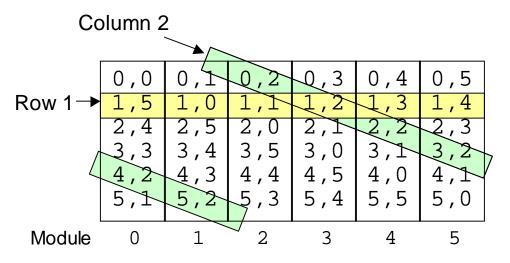

Fig. 6.7. Skewed matrix storage for conflict-free accesses to rows and columns.

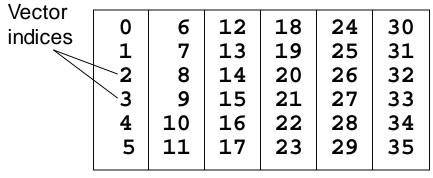

$A_{ii}$  is viewed as vector element i + jm

Fig. 6.8. A  $6 \times 6$  matrix viewed, in column-major order, as a 36element vector.

The vector in Fig. 6.8 may be accessed in some or all of the following ways

| Column:       | <i>k</i> , <i>k</i> +1, <i>k</i> +2, <i>k</i> +3, <i>k</i> +4, <i>k</i> +5                       | Stride = $1$         |

|---------------|--------------------------------------------------------------------------------------------------|----------------------|

| Row:          | k, k+m, k+2m, k+3m, k+4m, k+5m                                                                   | Stride = $m$         |

| Diagonal:     | k, k+ <i>m</i> +1, k+2( <i>m</i> +1), k+3( <i>m</i> +1),<br>k+4( <i>m</i> +1), k+5( <i>m</i> +1) | Stride = <i>m</i> +1 |

| Antidiagonal: | k, k+ <i>m</i> –1, k+2( <i>m</i> –1), k+3( <i>m</i> –1),<br>k+4( <i>m</i> –1), k+5( <i>m</i> –1) | Stride = <i>m</i> –1 |

*Linear skewing scheme:*

stores the *k*th vector element in bank  $a + kb \mod B$

The address within the bank is irrelevant to conflict-free parallel access

In fact, the constant *a* above is also irrelevant and can be safely ignored

So we can limit our attention to linear skewing schemes that assign  $V_k$  to memory module  $M_{kb \mod B}$

With a linear skewing scheme, the vector elements k, k+s, k+2s,  $\cdots$ , k+(B-1)s will be assigned to different memory modules iff sb is relatively prime with respect to the number B of memory banks.

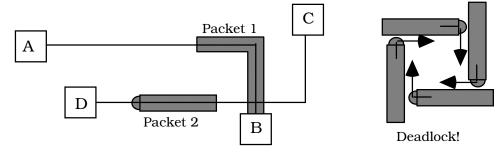

To allow access from each processor to every memory bank, we need a permutation network

Even with a full permutation network (complex, expensive), full PRAM functionality is not realized

Practical processor-to-memory network cannot realize all permutations (they are *blocking*)

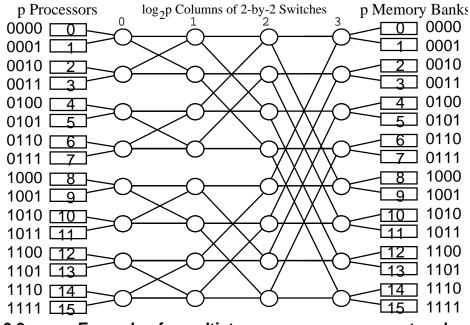

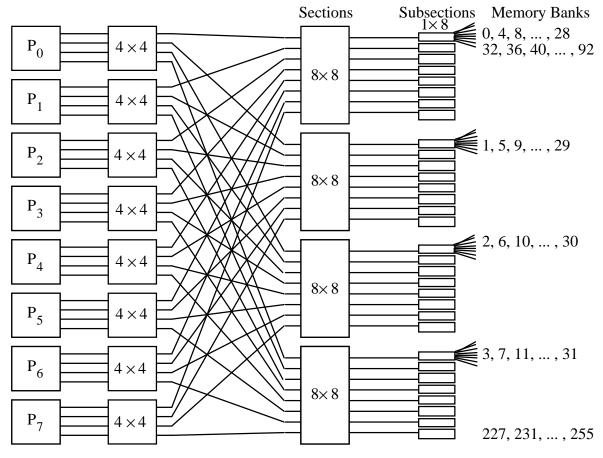

Fig. 6.9. Example of a multistage memory access network.

# 7 Sorting and Selection Networks

Back to TOC

### **Chapter Goals**

- Become familiar with the circuit-level models of parallel processing

- Architecture ⇒ algorithm (studied so far)

Problem ⇒ develop a suitable architecture (three more application-specific examples to come in Chapter 8)

- Introduce useful design tools and study trade-off issues via a familiar problem

#### **Chapter Contents**

- 7.1. What Is a Sorting Network?

- 7.2. Figures of Merit for Sorting Networks

- 7.3. Design of Sorting Networks

- 7.4. Batcher Sorting Networks

- 7.5. Other Classes of Sorting Networks

- 7.6. Selection Networks

### 7.1 What Is a Sorting Network?

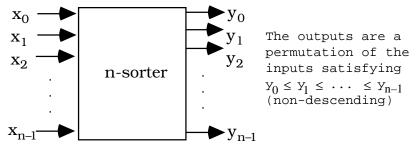

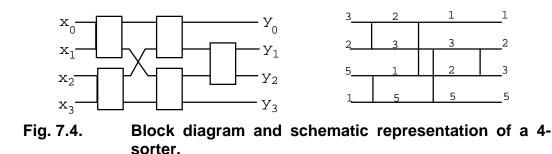

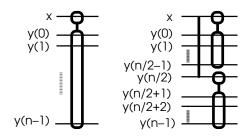

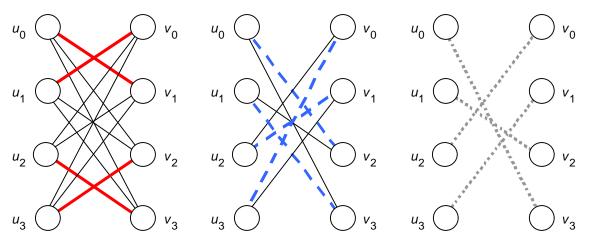

Fig. 7.1. An *n*-input sorting network or an *n*-sorter.

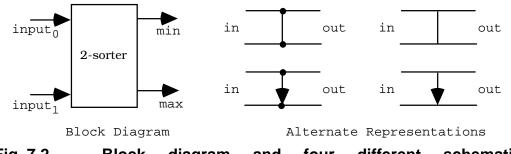

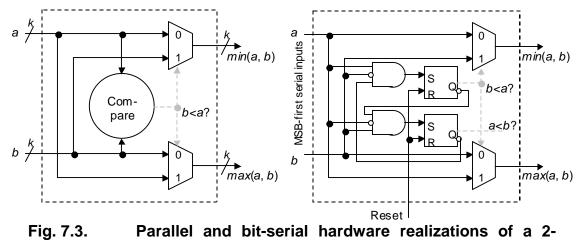

Fig. 7.2. Block diagram and four different schematic representations for a 2-sorter.

sorter.

Introduction to Parallel Processing: Algorithms and Architectures

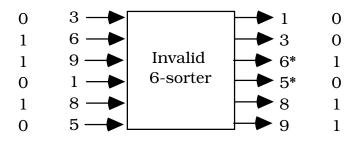

How to verify that the circuit of Fig. 7.4 is a valid 4-sorter?

The answer is easy in this case

After the first two circuit levels, the top line carries the smallest and the bottom line the largest of the four values

The final 2-sorter orders the middle two values

More generally, we need to verify the correctness of an *n*sorter through formal proofs or by time-consuming exhaustive testing. Neither approach is attractive.

*The zero-one principle:* A comparison-based sorter is valid iff it correctly sorts all 0/1 sequences.

### 7.2 Figures of Merit for Sorting Networks

- a. Cost: number of 2-sorters used in the design

- b. Delay: number of 2-sorters on the critical path

- c.  $Cost \times Delay$

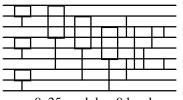

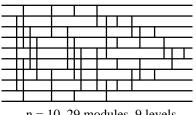

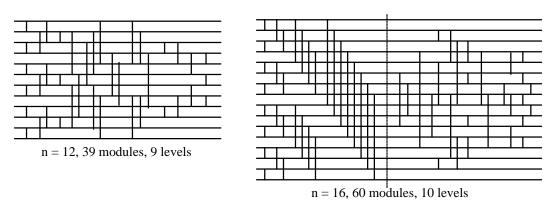

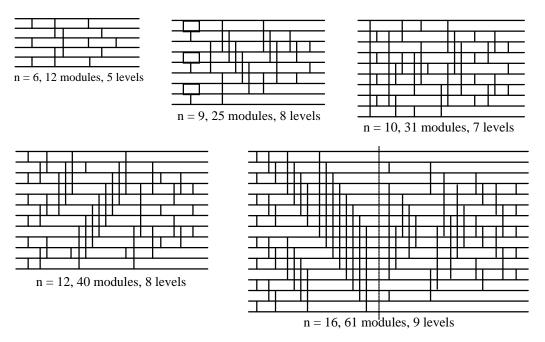

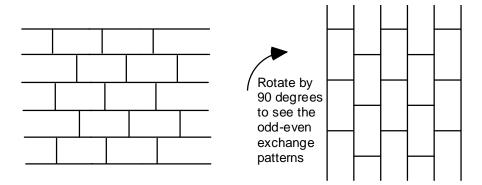

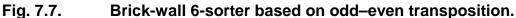

n = 9, 25 modules, 9 levels

n = 10, 29 modules, 9 levels

Fig. 7.5. Some low-cost sorting networks.

Fig. 7.6. Some fast sorting networks.

#### 7.3 Design of Sorting Networks

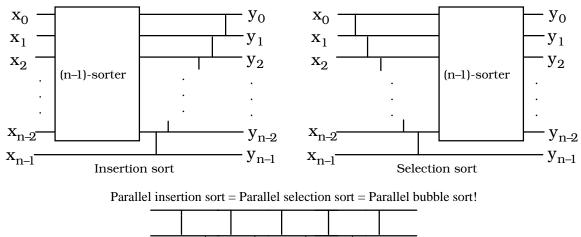

$C(n) = C(n-1) + n - 1 = (n-1) + (n-2) + \dots + 2 + 1 = n(n-1)/2$   $D(n) = D(n-1) + 2 = 2 + 2 + \dots + 2 + 1 = 2(n-2) + 1 = 2n - 3$ Cost × Delay =  $n(n-1)(2n-3)/2 = \Theta(n^3)$

Fig. 7.8. Sorting network based on insertion sort or selection sort.

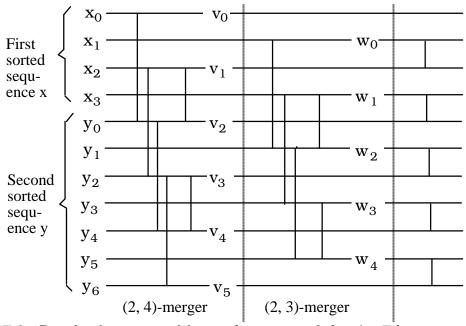

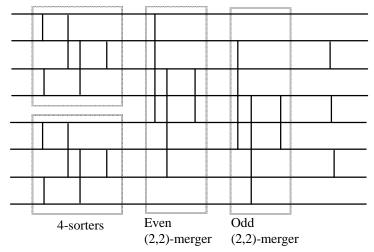

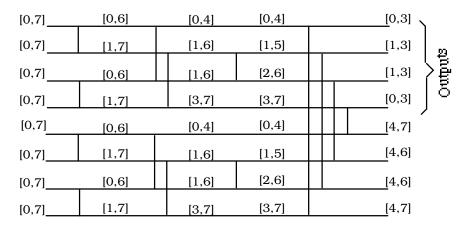

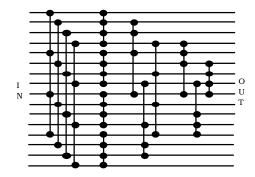

### 7.4 Batcher Sorting Networks

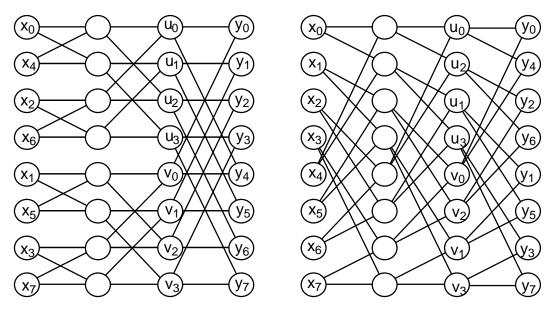

Fig. 7.9. Batcher's even–odd merging network for 4 + 7 inputs.

$x_0 \le x_1 \le \cdots \le x_{m-1}$  (k 0s)  $y_0 \le y_1 \le \cdots \le y_{m'-1}$  (k' 0s)

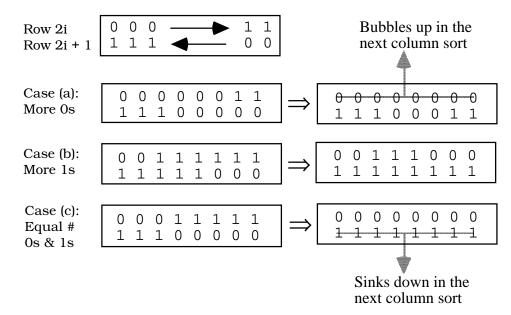

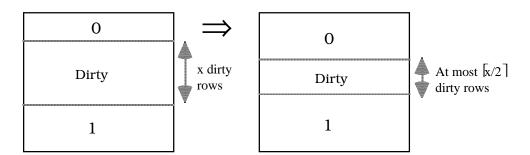

Merge  $x_0, x_2, \dots$  and  $y_0, y_2, \dots$  to get  $v_0, v_1, \dots k_{even} = \lceil k/2 \rceil + \lceil k/2 \rceil$  os Merge  $x_1, x_3, \dots$  and  $y_1, y_3, \dots$  to get  $w_0, w_1, \dots k_{odd} = \lfloor k/2 \rfloor + \lfloor k/2 \rfloor$  os Compare-exchange the pairs of elements  $w_0: v_1, w_1: v_2, w_2: v_3, \dots$ Case a:  $k_{even} = k_{odd}$  The sequence  $v_0 w_0 v_1 w_1 v_2 w_2 \dots$  already sorted Case b:  $k_{even} = k_{odd} + 1$  The sequence  $v_0 w_0 v_1 w_1 v_2 w_2 \dots$  already sorted Case c:  $k_{even} = k_{odd} + 2$

Batcher's (m, m) even-odd merger, when m is a power of 2, is characterized by the following recurrences:

$$C(m) = 2C(m/2) + m - 1$$

= (m-1) + 2(m/2-1) + 4(m/4-1) + ...

= m log<sub>2</sub>m + 1

$$D(m) = D(m/2) + 1$$

$= \log_2 m + 1$

$Cost \times Delay = \Theta(m \log^2 m)$

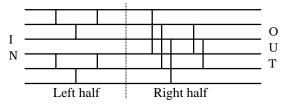

Fig. 7.10. The recursive structure of Batcher's even–odd merge sorting network.

Fig. 7.11. Batcher's even-odd merge sorting network for eight inputs.

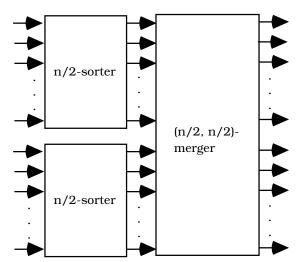

Batcher sorting networks based on the even-odd merge technique are characterized by the following recurrences:

$$C(n) = 2C(n/2) + (n/2)(\log_2(n/2)) + 1$$

$$\cong n(\log_2 n)^{2/2}$$

$$D(n) = D(n/2) + \log_2(n/2) + 1$$

$$= D(n/2) + \log_2 n$$

$$= \log_2 n (\log_2 n + 1)/2$$

Cost × Delay =  $\Theta(n \log^4 n)$

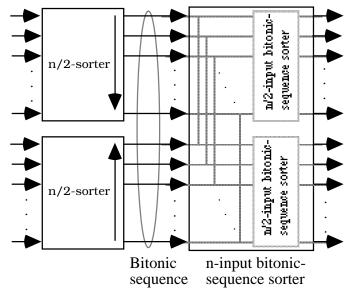

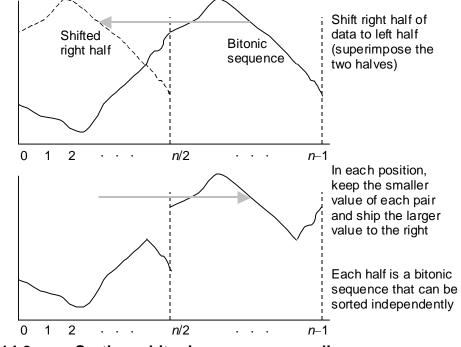

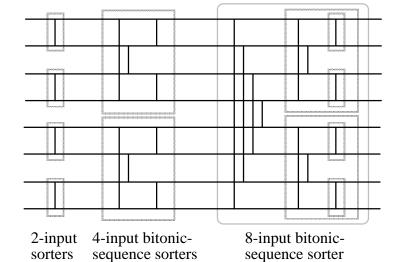

#### **Bitonic sorters**

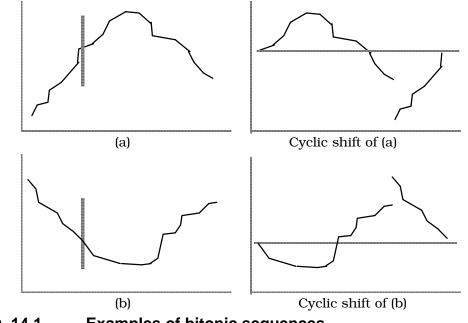

Bitonic sequence: "rises then falls", "falls then rises", or is obtained from the first two categories through cyclic shifts or rotations. Examples include:

- 1 3 3 4 6 6 6 2 2 1 0 0 Rises, then falls

- 8 7 7 6 6 6 5 4 6 8 8 9 Falls, then rises

8 9 8 7 7 6 6 6 5 4 6 8 The previous sequence, right-rotated by 2

Fig. 7.12. The recursive structure of Batcher's bitonic sorting network.

Introduction to Parallel Processing: Algorithms and Architectures

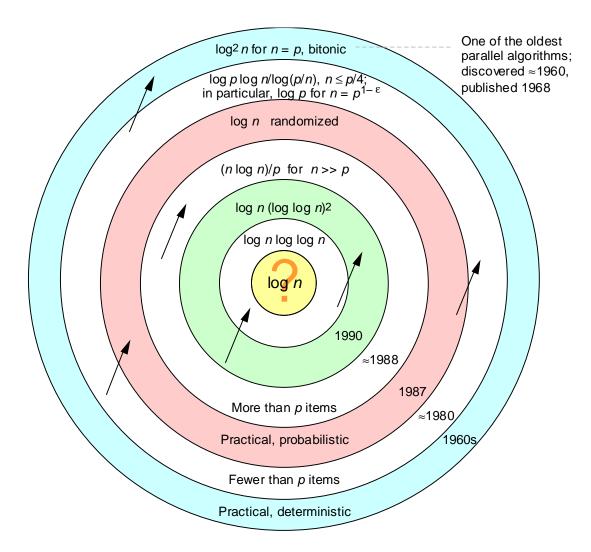

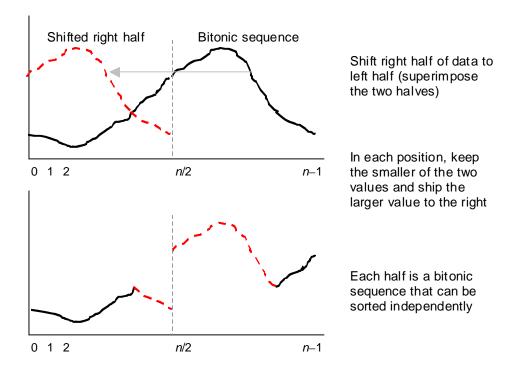

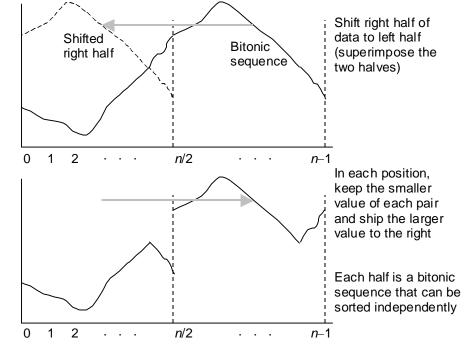

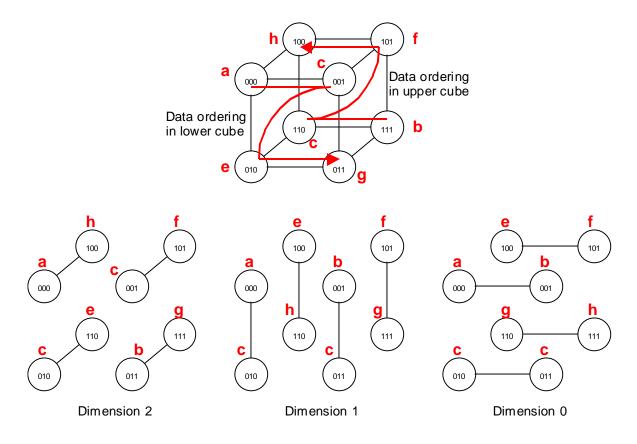

Fig. 14.2. Sorting a bitonic sequence on a linear array.

Fig. 7.13. Batcher's bitonic sorting network for eight inputs.

### 7.5 Other Classes of Sorting Networks

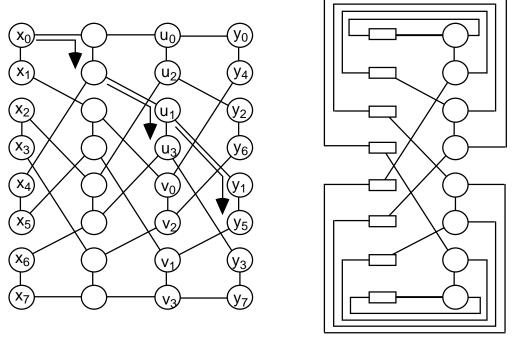

Periodic balanced sorting networks

Fig. 7.14. Periodic balanced sorting network for eight inputs.

Desirable properties:

- a. Regular and modular (easier VLSI layout).

- b. Slower, but more economical, implementations are possible by reusing the blocks

- c. Using an extra block provides tolerance to some faults (missed exchanges)

- d. Using 2 extra blocks provides tolerance to any single fault (a missed or incorrect exchange)

- e. Multiple passes through a faulty network can lead to correct sorting (graceful degradation)

- f. Single-block design can be made fault-tolerant by adding an extra stage to the block

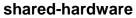

### Shearsort-based sorting networks

Offer some of the same advantages enumerated for periodic balanced sorting networks

Fig. 7.15. Design of an 8-sorter based on shearsort on 2×4 mesh.

Fig. 7.16. Design of an 8-sorter based on shearsort on  $4 \times 2$  mesh.

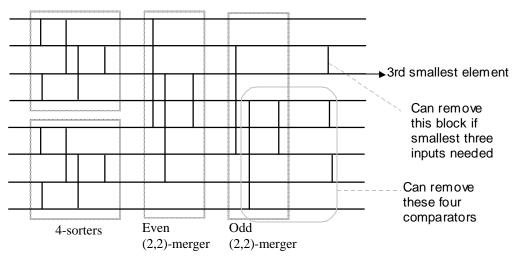

### 7.6 Selection Networks

Any sorting network can be used as a selection network, but a selection network (yielding the *k*th smallest or largest input value) is in general simpler and faster

One way to get a selection network is by pruning a sorting network

Deriving an (8, 3)-selector from Batcher's even-odd merge 8-sorter.

Direct design is likely to lead to more efficient networks, but unfortunately we know even less about selection networks than we do about sorting networks. One can define three selection problems:

- I. Select the *k* smallest values; present in sorted order

- II. Select *k*th smallest value

- III. Select the k smallest values; present in any order

Circuit and time complexity: (I) hardest, (III) easiest

Fig. 7.17. A type III (8, 4)-selector.

Classifier: a selection network that can divide a set of n values into n/2 largest and n/2 smallest values

The selection network of Fig. 7.17 is an 8-input classifier

Generalizing from Fig. 7.17, an *n*-input classifier can be built from two (n/2)-sorters followed by n/2 comparators

An *n*-classifier and two *n*/2-sorters can form an *n*-sorter. For such a sorting network:

$$T(n) = 2T(n/2) + 1 = n - 1$$

$$C(n) = 4C(n/2) + n/2 = n(n - 1)/2$$

Figure for Problem 7.7.

Figure for Problem 7.9.

Figure for Problem 7.11.

# 8 Other Circuit-Level Examples

#### Back to TOC

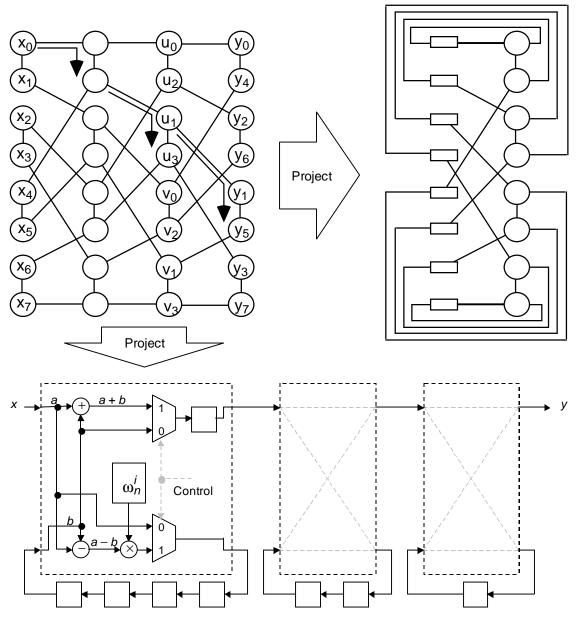

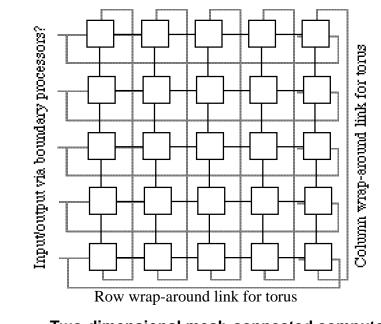

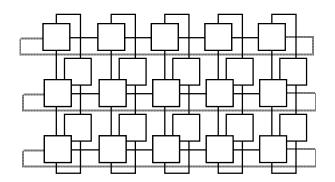

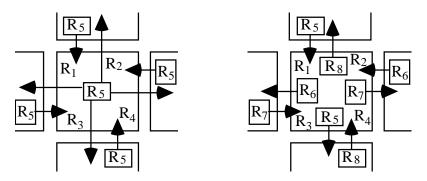

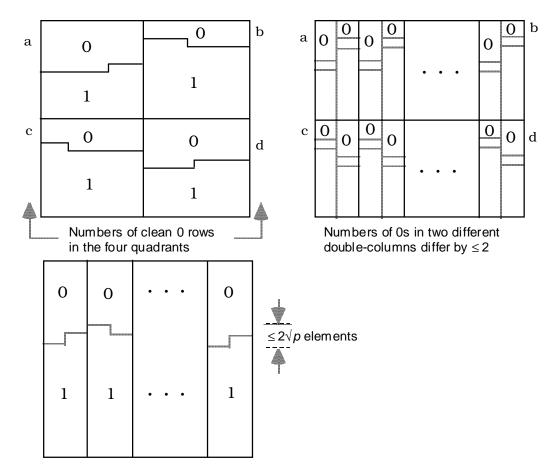

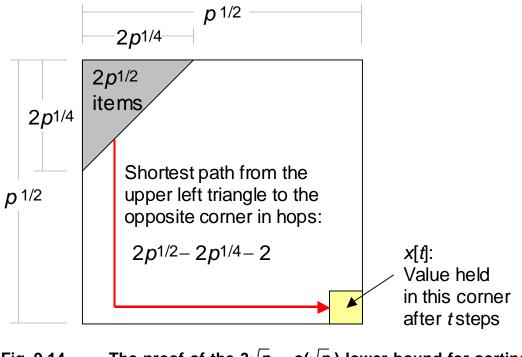

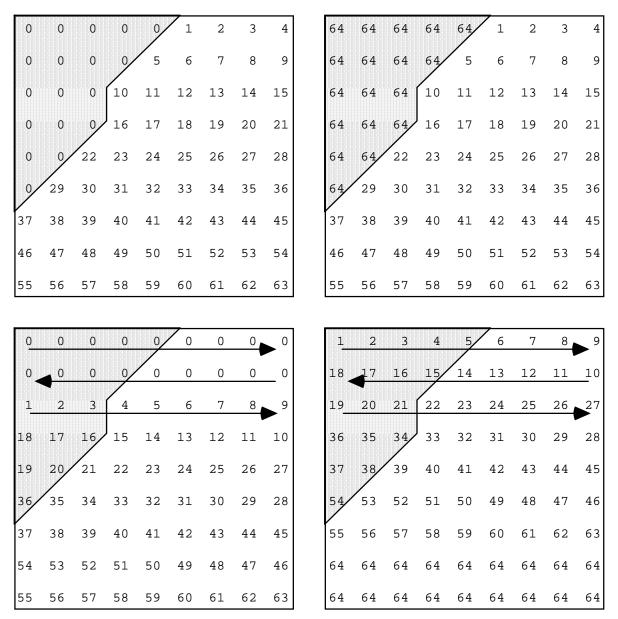

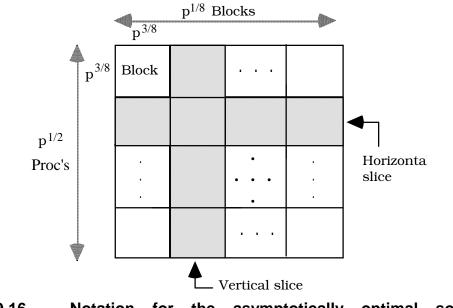

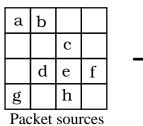

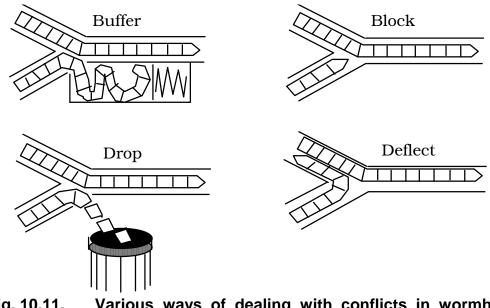

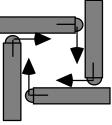

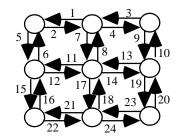

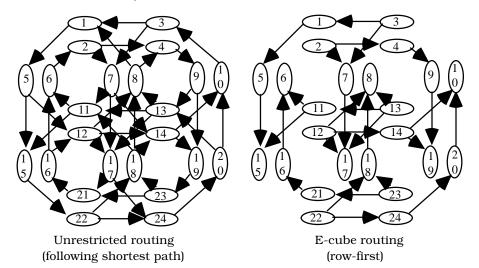

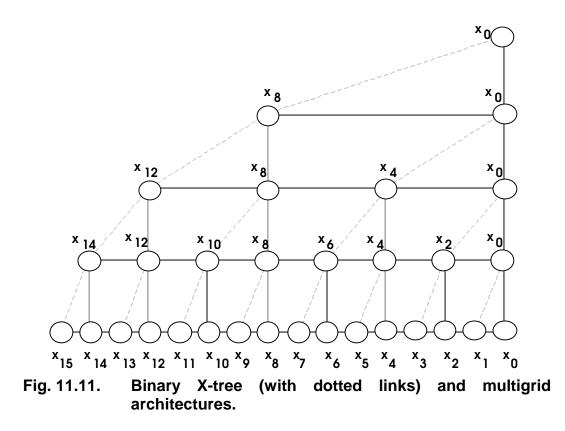

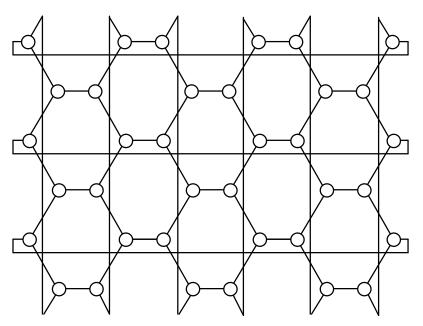

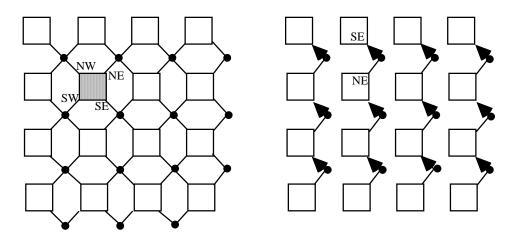

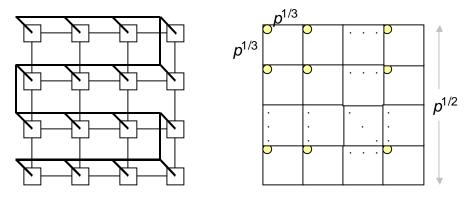

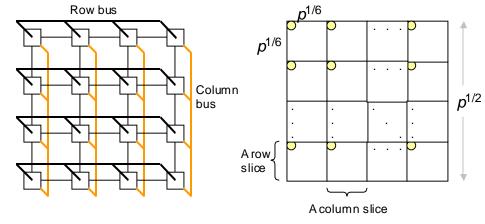

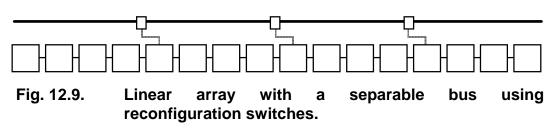

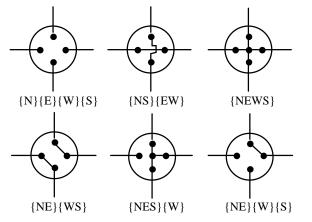

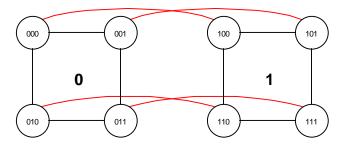

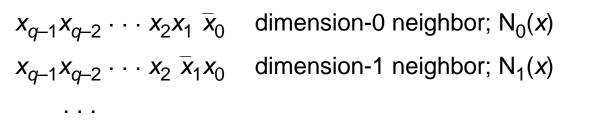

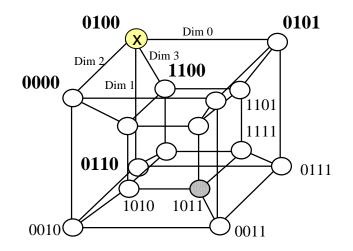

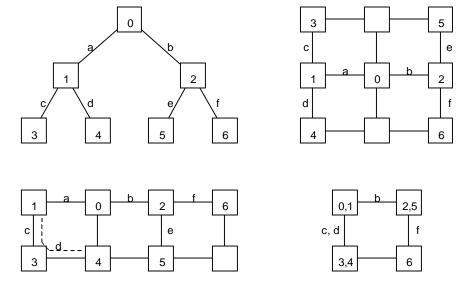

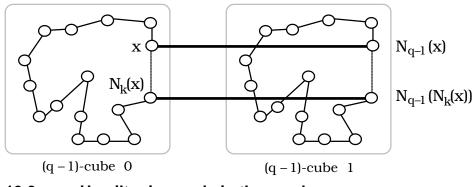

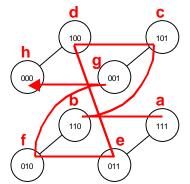

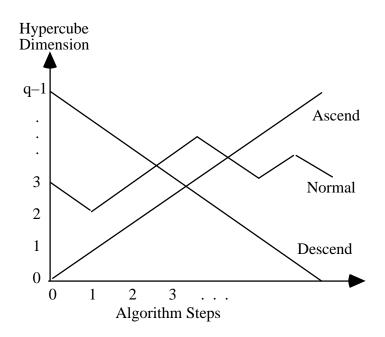

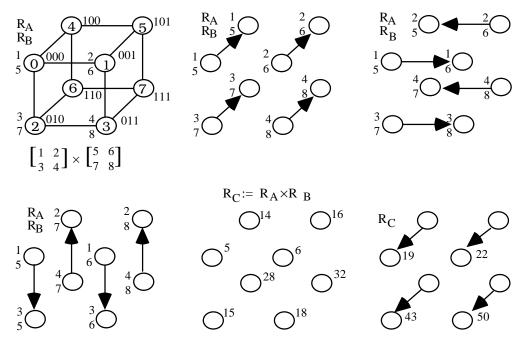

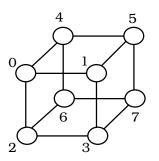

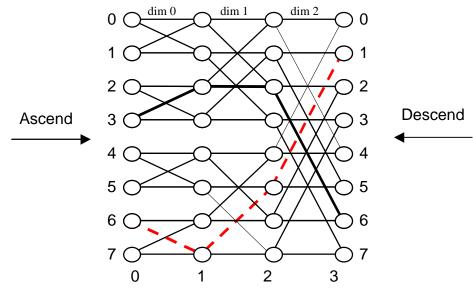

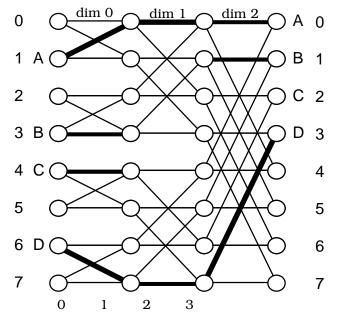

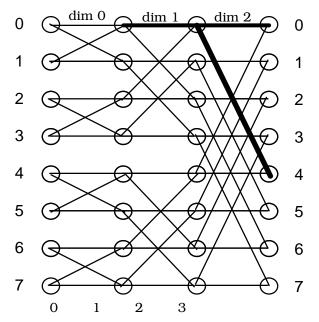

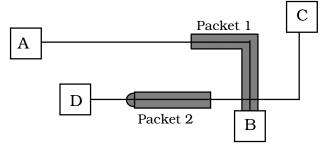

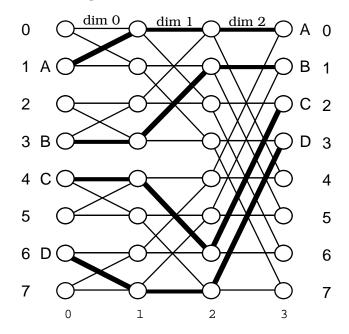

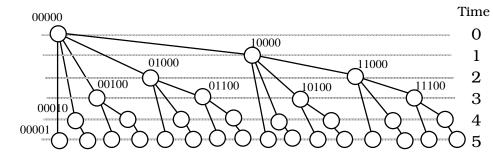

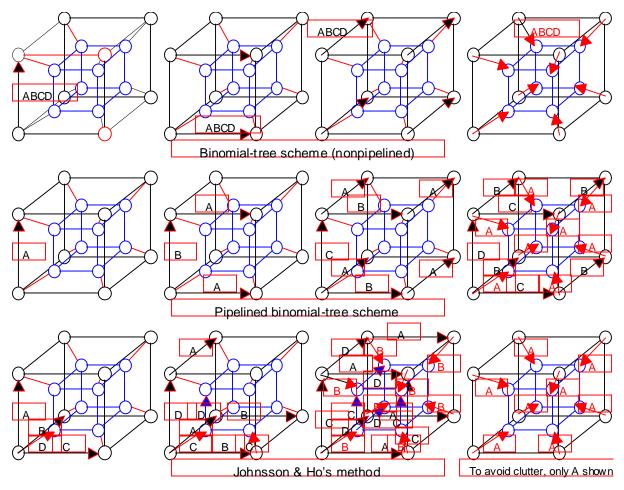

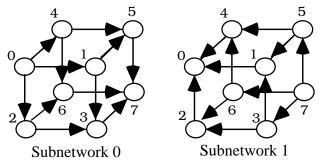

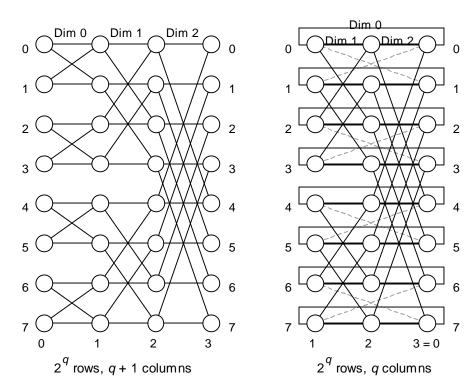

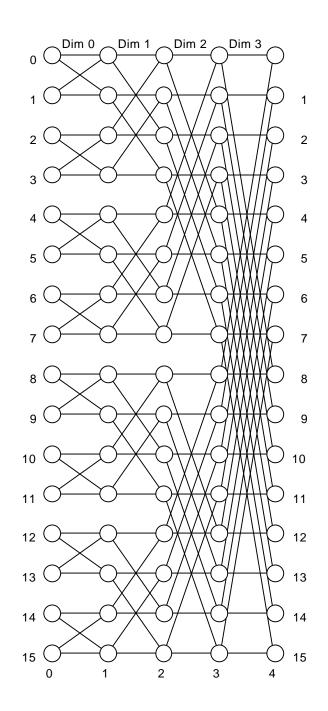

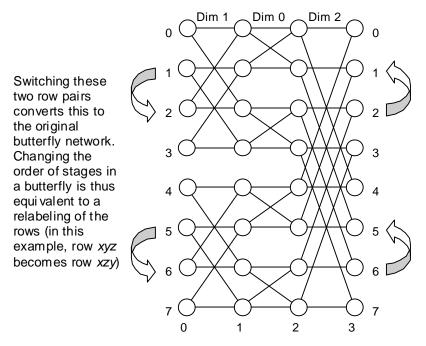

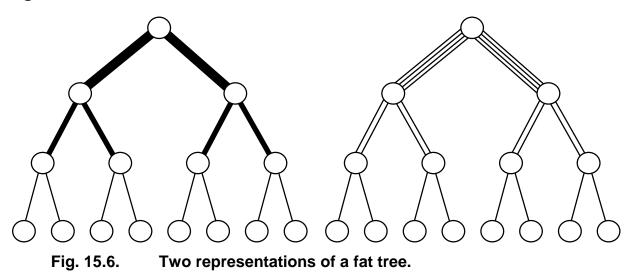

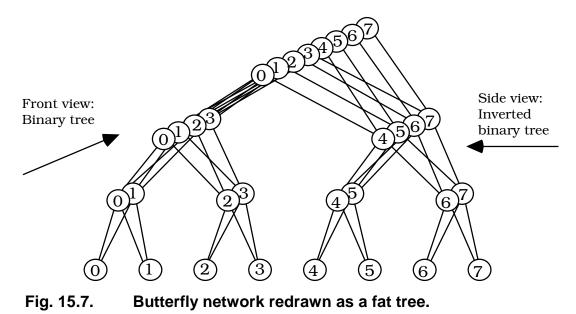

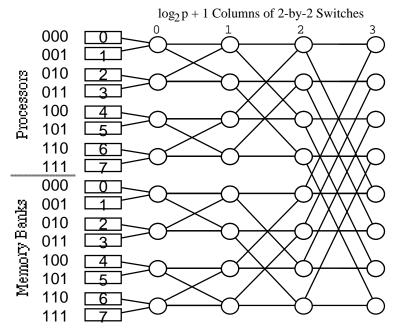

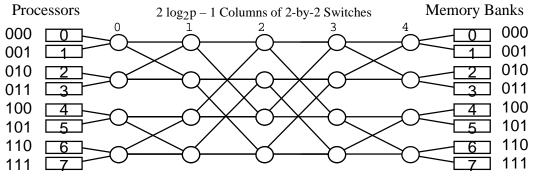

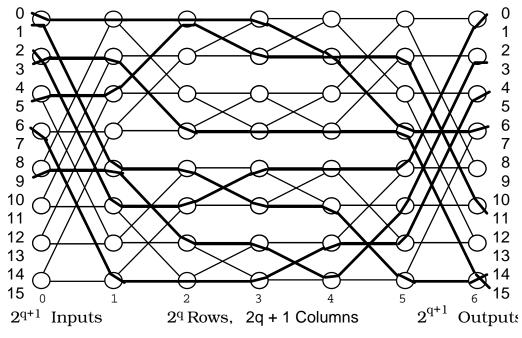

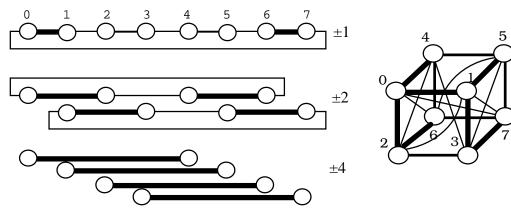

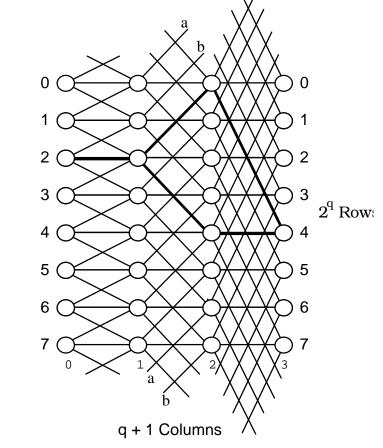

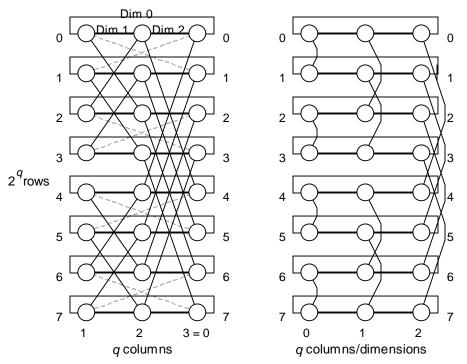

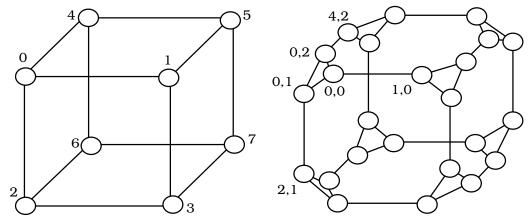

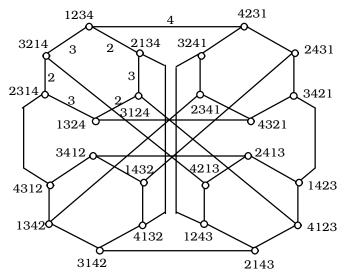

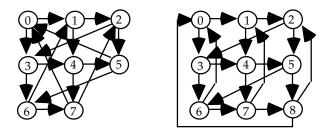

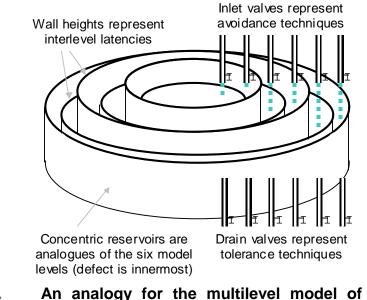

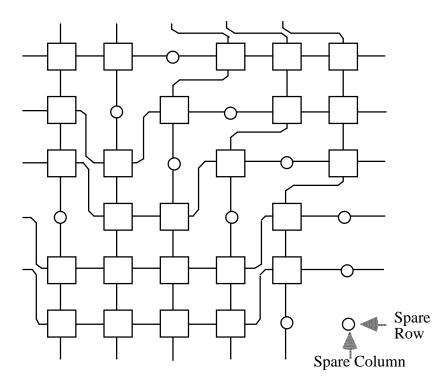

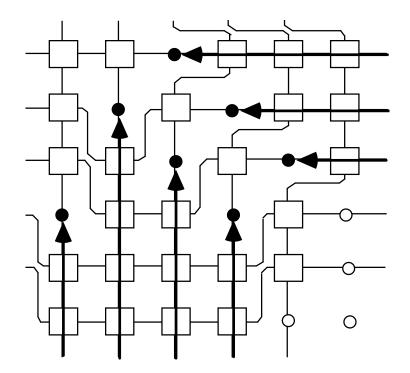

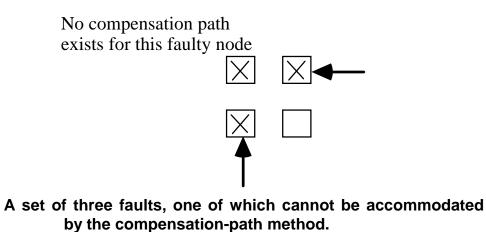

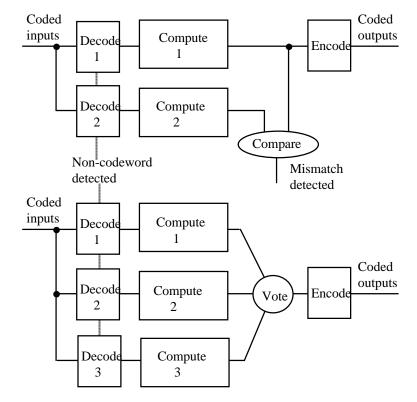

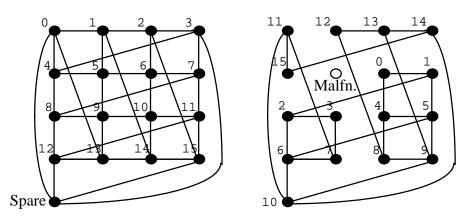

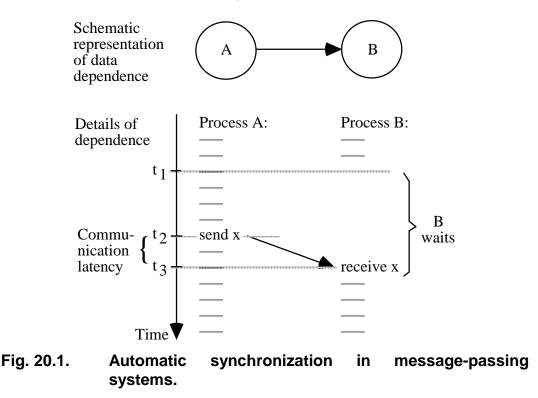

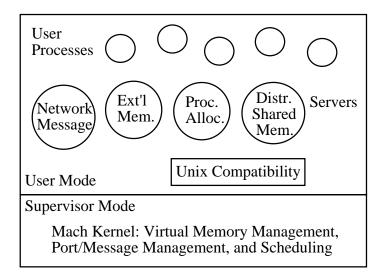

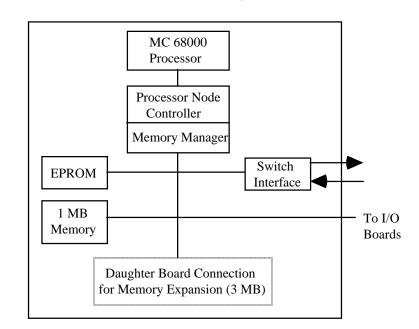

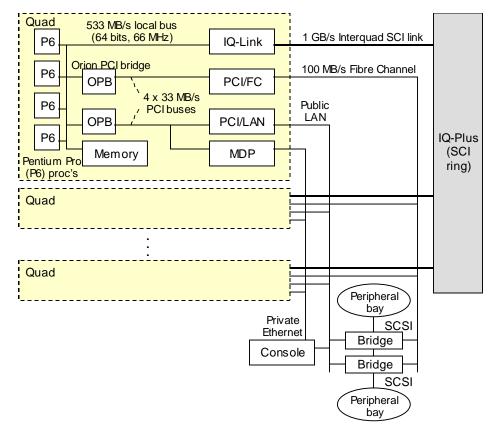

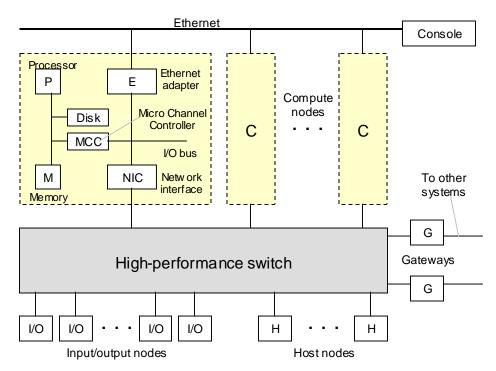

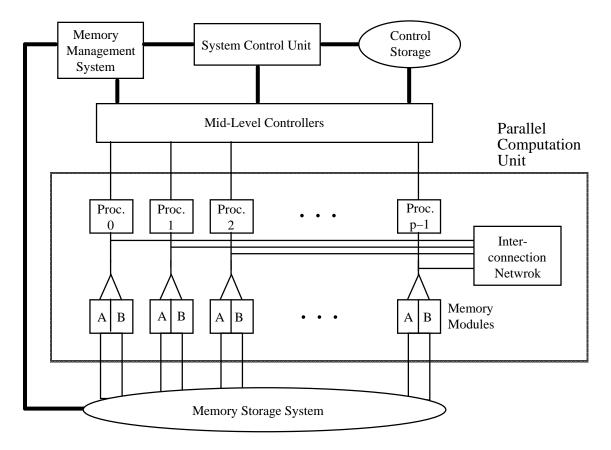

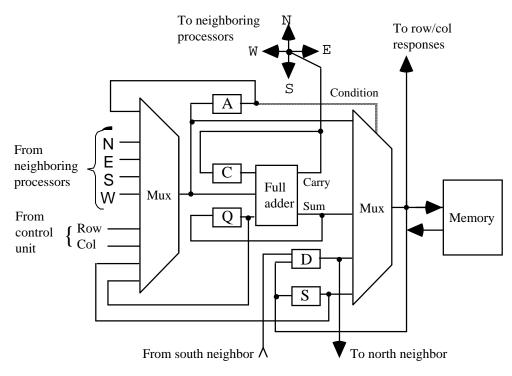

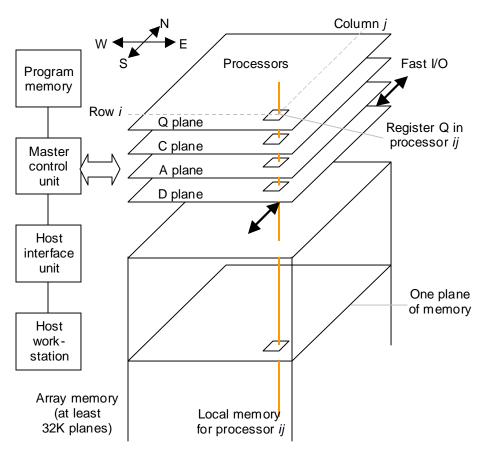

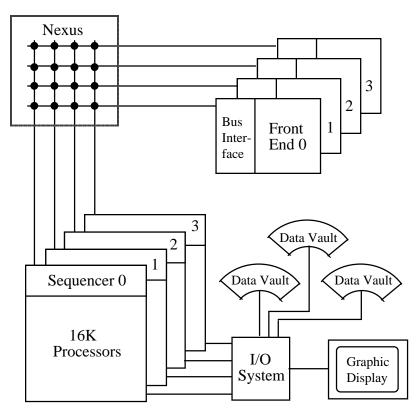

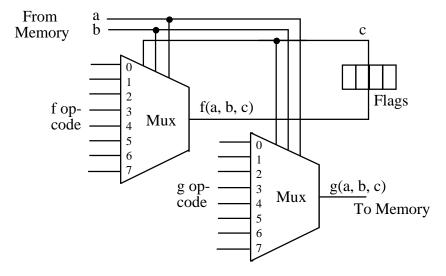

#### Chapter Goals