# Evolution of Chip-Scale Heterodyne Optical Phase-Locked Loops Toward Watt Level Power Consumption

Arda Simsek , *Student Member, IEEE*, Shamsul Arafin , *Senior Member, IEEE*, Seong-Kyun Kim , Gordon B. Morrison, Leif A. Johansson, *Member, IEEE*, Milan L. Mashanovitch, *Senior Member, IEEE*, Larry A. Coldren, *Life Fellow, IEEE, Fellow, OSA*, and Mark J. W. Rodwell, *Fellow, IEEE*

(Top-Scored Paper)

Abstract—We design and experimentally demonstrate two chipscale and agile heterodyne optical phase-locked loops (OPLLs) based on two types of InP-based photonic-integrated coherent receiver circuits. The system performance of the first-generation OPLL was improved in terms of offset-locking range, and power consumption with the use of a power efficient and compact photonic-integrated circuit (PIC). The second-generation PIC consists of a 60-nm widely tunable Y-branch laser as a local oscillator with a 2  $\times$  2 multimode interference (MMI) coupler and a pair of balanced photodetectors. This PIC consumes only 184-mW power in full operation, which is a factor of 3 less compared to the first-generation PIC. In addition, the sensitivity of these OPLLs was experimentally measured to be as low as 20  $\mu$ w. A possible solution to increase the sensitivity of these OPLLs is also suggested.

Index Terms—Heterodyne, integrated optics, optical phase-locked loop, photonic integrated circuits.

# I. INTRODUCTION

PTICAL phase-locked loops (OPLLs) have been of great interest for the last couple of decades due to the promising applications in the areas of communications, sensing and frequency control [1], [2]. These applications include short to medium range coherent optical communications [3], laser linewidth narrowing [4]–[6], terahertz signal generation [6], [7] and optical frequency synthesis [8]–[11]. With the improvements in the photonic integration, OPLLs became more attractive since they can offer small loop delay, which allows having OPLLs with loop bandwidths as large as 1.1 GHz [3]. However, these prior OPLLs consume almost 3 Watts of electrical power

Manuscript received July 1, 2017; revised August 23, 2017 and September 16, 2017; accepted September 25, 2017. Date of publication October 1, 2017; date of current version February 24, 2018. This work was supported in part by the DARPA-MTO under the DODOS Project and in part by the National Science Foundation under Grant 1402935. (Corresponding author: Arda Simsek.)

- A. Simsek, S. Arafin, L. A. Coldren, and M. J. W. Rodwell are with the Department of Electrical and Computer Engineering, University of California Santa Barbara, Santa Barbara, CA 93106 USA (e-mail: ardasimsek@ece.ucsb.edu; sarafin@ece.ucsb.edu; coldren@ece.ucsb.edu; rodwell@ece.ucsb.edu).

- S.-K. Kim is with Teledyne Scientific and Imaging Company, Thousand Oaks, CA 91360 USA (e-mail: skkim910@gmail.com).

- G. B. Morrison, L. A. Johansson, and M. L. Mashanovitch are with Freedom Photonics, LLC, Santa Barbara, CA 93117 USA (e-mail: gordon@freedomphotonics.com; leif@ece.ucsb.edu; mashan@ece.ucsb.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JLT.2017.2758744

[3]. This high-power consumption makes the use of OPLLs in practical applications questionable.

Therefore, realizing a low-power consumption OPLL is important to take advantage of recent advances in photonic integration. A chip-scale, compact, low power consumption OPLL can push the technology in the aforementioned application areas further forward. With the proper design of compact photonic integrated circuits (PICs), power consumption in such PICs, therefore OPLLs, can be lowered [12]. In this work, two chip-scale, highly-integrated OPLLs are designed and experimentally demonstrated using two different InP-based photonic integrated coherent receiver circuits.

After successfully achieving OPLLs with a reasonable offset locking range and low-power consumption, a detailed sensitivity analysis and some relevant experiments were performed. A minimum input optical power to demonstrate the phase-locking using our OPLLs was measured as 20  $\mu \rm w$  both theoretically and experimentally. A novel solution is proposed that can be implemented in such OPLLs in order to lock input power levels as low as nanowatts.

This paper is organized as follows. This paper begins with a short summary of OPLL system design together with the PIC design. We then present the experimental results for the first, and second generation OPLL. After this, the power budget for both OPLLs is given. Finally, the sensitivity analysis and a proposed solution for high sensitivity OPLL is provided.

# II. OPTICAL PHASE-LOCKED LOOP SYSTEM DESIGN

# A. PIC Design

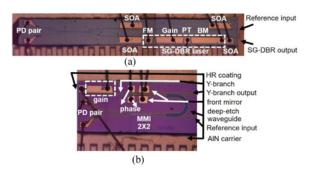

Since two different types of PICs are used in this study for demonstrating heterodyne OPLLs, we have named them as gen-1 and gen-2 PICs for clarity. All active/passive components in these PICs are monolithically integrated on an InGaAsP/InP material platform. Details of the fabrication of such PICs can be found in [13], [14]. Microscope images of both PICs are shown in Fig. 1(a) and (b).

Out of two PICs, gen-1 PIC (see Fig. 1(a)) consists of 40 nm widely-tunable sampled-grating distributed-Bragg-

U.S. Government work not protected by U.S. copyright.

Fig. 1. (a) Microscope image of the gen-1 InP based PIC. (b) Microscope image of low power consumption gen-2 InP based PIC. (BM: back mirror, FM: front mirror, PD: photodiode, PT: phase tuner, SG-DBR: sampled-grating distributed-Bragg-reflector, and SOA: semiconductor optical amplifier.)

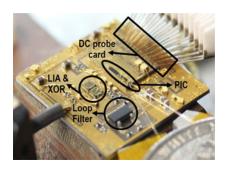

Fig. 2. OPLL system under measurement setup integrated on an AlN carrier including gen-1 PIC and control electronics.

reflector (SG-DBR) laser,  $2 \times 2$  multimode interference (MMI) coupler, a balanced photodetector pair and a couple of semiconductor optical amplifiers (SOAs) on reference and local-oscillator (LO) optical paths. Reference optical signal was coupled into this PIC using the upper arm and amplified by two SOAs. SG-DBR laser output propagated in the lower arm. These two optical signals were combined in a  $2 \times 2$  MMI coupler and mixed in a balanced photodetector pair to produce the beat note for the electronics part. The SG-DBR laser also has a second output from its backside for monitoring purposes.

Gen-2 PIC (see Fig. 1(b)) was designed for low power consumption. This PIC incorporates a widely tunable, compact Y-branch laser, formed between a high-reflectivity coated back cleaved mirror and a pair of Vernier tuned sampled-grating front mirrors, as well as a 2 × 2 MMI coupler and a balanced photodetector pair. The optical output from one of the front mirrors was connected to the MMI coupler, while the other output from another front mirror was used externally for monitoring the OPLL operation. The Y-branch laser has a compact cavity with short gain and mirror sections, requiring low current and therefore low drive power. It is tuned via Vernier effect and has been designed for high efficiency at 30 °C. The measured tuning range exceeds 60 nm with >50 dB side-mode suppression ratio [15].

# B. Feedback Electronics Design and OPLL Assembly

Both OPLLs use SiGe (Silicon Germanium) based commercial-off-the-shelf (COTS) electronic ICs and loop filters built from discrete components as the control electronics. Fig. 2 shows an exemplary OPLL system assembled by mounting gen-1 PIC and electronic components on a patterned AlN carrier.

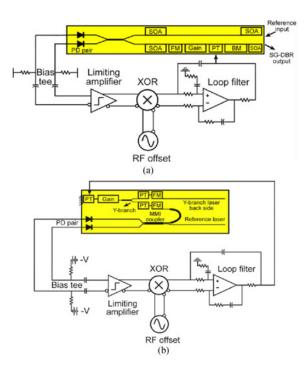

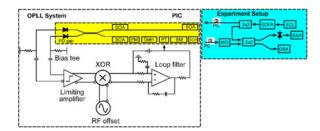

Fig. 3. (a) Circuit diagram of the first generation OPLL including gen-1 PIC in yellow and the control electronics. (b) Circuit diagram of the second generation OPLL including gen-2 PIC in yellow, and the control electronics. (BM: back mirror, FM: front mirror, PD: photodiode, PT: phase tuner, SG-DBR: sampled-grating distributed-Bragg-reflector, SOA: semiconductor optical amplifier.)

In this study, both OPLLs are designed to be heterodyne-type, which takes input offset frequency from external RF synthesizer and locks LO laser to the reference oscillator at this offset frequency. The second order loop filter with fast feedforward path was used in feedback electronics in order to get a high loop bandwidth. The circuit schematics of both OPLL systems can be seen in Fig. 3(a) and (b).

A limiting amplifier with 30 dB differential gain and 17 GHz 3-dB bandwidth, and a digital XOR gate functioning as a phase detector [16], together with an op-amp-based loop filter were used in the feedback electronics. The on-chip LO laser of the PIC was mixed via the external reference laser through the 2 × 2 MMI coupler and the PD pair to produce the beat note. This beat note then feeds the electronic ICs. First, it is amplified to logic levels through limiting amplifier and then mixed via external RF frequency synthesizer in order to produce an error signal. This error signal goes through the loop filter and feeds back to the phase-tuning section (PT) of on-chip LO laser. With sufficient feedback gain, this error signal becomes zero and LO laser is locked to external reference laser at a given RF offset frequency.

Open loop transfer function of an OPLL can be written as a product of gain, and the time constants of the loop [17]. Therefore, open loop transfer function of both OPLLs in this work can be expressed as follows:

$$T(s) = K_{\text{PD}} K_{\text{CCO}} \frac{1}{\left(\tau_{\text{laser}} s + 1\right)} e^{-\tau_{\text{d}} s}$$

$$\times \left(\frac{\tau_2 s + 1}{\tau_1 s} \frac{1/R_{out}}{\tau_{\text{op}} s + 1} e^{-\tau_{\text{dop}} s} + \frac{C_{\text{FF}}}{2}\right)$$

where  $K_{\rm PD}$  is the phase detection gain,  $K_{\rm CCO}$  is the laser tuning sensitivity,  $\tau_{\rm laser}$  is the laser tuning frequency responsivity,

Fig. 4. Experimental setup for the first generation OPLL system. (ECL: external cavity laser, ESA: electrical spectrum analyzer, OSA: optical spectrum analyzer, PC: polarization controller, ISO: isolator.)

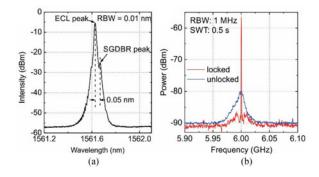

Fig. 5. (a) OSA spectrum when SGDBR is offset locked to the reference laser at 6 GHz offset, which corresponds 0.05 nm separation in optical domain. (b) Corresponding ESA spectrum when SGDBR is offset locked to the reference laser at 6 GHz offset, blue is before locking and red is after locking.

$\tau_1$  is the loop filter pole,  $\tau_2$  is the loop filter zero,  $\tau_{\rm OP}$  is the op-amp parasitic pole,  $R_{\rm out}$  is the voltage to current conversion resistance at the output,  $C_{\rm FF}$  is the feed-forward capacitor and  $\tau_{\rm dop}$  is the op-amp delay, and  $\tau_{\rm d}$  is the total loop delay. Here  $K_{\rm PD}$  is a constant value (2 \*  $V_{\rm logic}/\pi$ ) due to the limiting amplifier, which makes the system loop bandwidth insensitive to the optical power level variations. This loop was designed to have a safe phase margin of around 50–60° at unity gain crossover frequency for both OPLLs in order to realize a robust and stable system.

# III. FIRST GENERATION OPLL EXPERIMENTAL RESULTS

The experimental setup, as shown in Fig. 4, was used in order to demonstrate the offset locking with the OPLL using the gen-1 PIC. The reference external cavity laser (ECL) was coupled into the PIC using lensed fiber from the back side of the PIC. It was then combined with the tunable on-chip SG-DBR laser output in the MMI coupler and mixed to form the desired beat note in the PDs. Light from the SG-DBR laser was coupled out from the lower arm for monitoring purposes. The superimposed optical spectra of the reference laser together with on chip SG-DBR laser were measured by an optical spectrum analyzer (OSA). At the same time, the resulting RF beat-note was measured by an electrical spectrum analyzer (ESA) through a high speed photodiode.

This experiment shows offset-phase locking between the on chip SG-DBR laser and the external cavity laser (ECL) as the reference. ECL used in this study has the optical linewidth of 100 kHz. Fig. 5(a) demonstrates the optical spectrum when the reference laser and the on chip SG-DBR are offset locked at

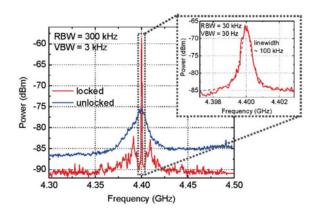

Fig. 6. ESA spectrum when SG-DBR is offset locked to the reference laser at 4.4 GHz offset. In this case, ECL and SG-DBR are decorrelated using a long fiber. Therefore, relative linewidth of the beat note is equal to 100 kHz, which is the linewidth of the ECL (reference laser).

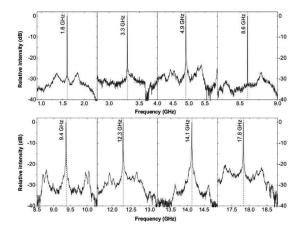

Fig. 7. Offset locking at multiple frequencies with the first generation OPLL at a RBW of 3 MHz.

6 GHz, which is determined by the RF frequency synthesizer. As can be seen in the figure, the separation between the two peaks are about 0.05 nm, which corresponds to 6 GHz frequency separation. In Fig. 5(b), the RF beat-note of the reference laser and the on chip SG-DBR laser is presented both in locked and unlocked cases. The relative linewidth of the locked beat note at 6 GHz is in the order of sub-Hz, which is limited by the resolution bandwidth of the ESA. It should be noted that the optical linewidth of our free-running on-chip laser is 10 MHz.

In order to measure the absolute linewidth of the locked beat note, the measurement was performed after adding 20 km of fiber between the upper and lower external  $2\times 2$  couplers to decorrelate the ECL from the SG-DBR. In this case, one would expect to get a linewidth of the RF beat note equal to the optical linewidth of the ECL. Fig. 6 demonstrates this result. On chip SG-DBR is offset locked at 4.4 GHz, but this time long fiber is added to decorrelate the ECL from the SG-DBR. In this case, the absolute linewidth of the locked beat tone was measured as  $100~\rm kHz$ , indicating the linewidth cloning of the SG-DBR to the ECL.

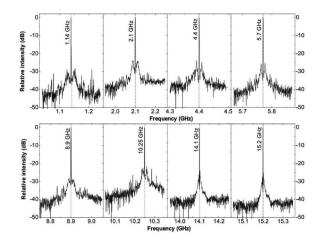

After proving the phase locking, the offset-locking range was demonstrated for different offset frequencies from 1.14 GHz up to 15.2 GHz as can be seen in Fig. 7. The higher the offset

Fig. 8. (a) OSA spectrum when on chip Y-branch laser is offset locked to the reference laser at 8.6 GHz offset, which corresponds 0.07 nm separation in optical domain. (b) Corresponding ESA spectrum when Y-branch laser is offset locked to the reference laser at 8.6 GHz offset.

locking range, the easier it became for the OPLL to track the reference signal over a broad range of frequencies [18], [19].

# IV. SECOND GENERATION OPLL EXPERIMENTAL RESULTS

Similar to the first generation OPLL, the experimental setup shown in Fig. 4 was used to demonstrate phase locking for the second generation OPLL. In this case, gen-1 PIC was replaced with the gen-2 PIC.

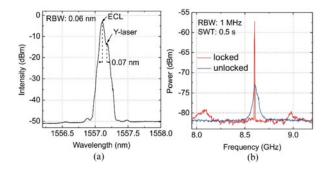

This experiment demonstrates phase locking between the onchip Y-branch laser and the reference laser. Fig. 8(a) shows the optical spectrum when the reference laser and the on chip Y-branch laser are offset locked at 8.6 GHz, which is determined by the RF frequency synthesizer. As can be seen in the figure, the separation between the two peaks are about 0.07 nm, which corresponds to 8.6 GHz frequency separation. In Fig. 8(b), the RF beat-note between the reference laser and the on chip Y-branch laser is displayed both before the locking and after the locking. The relative linewidth of the locked beat note at 8.6 GHz is in the order of sub-Hz, which is limited by the resolution bandwidth of the ESA. The beat note has a relative linewidth in the order of a MHz before the locking, which is the unlocked Y-branch laser's linewidth [12].

With similar arguments presented for the first generation OPLL, one can add a long enough fiber at the output between the upper and lower external  $2 \times 2$  couplers to decorrelate the ECL from the Y-branch laser and measure the actual linewidth of the beat note, which is equal to the linewidth of the ECL  $\sim 100 \ \text{kHz}$ .

As the next experiment, several offset frequencies from 1 GHz to 20 GHz were applied from the RF frequency synthesizer, and the same phase locking experiment was performed. Fig. 9 presents offset locking at several offset frequencies ranging from 1.6 GHz to 17.8 GHz.

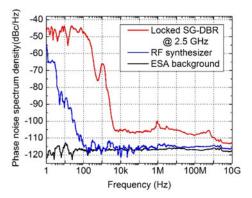

In addition to the phase locking experiments, the residual phase noise spectral density of the OPLL system was measured when on chip local oscillator is offset locked to the reference laser. Since the loop parameters and order were not changed from the OPLL with gen-1 PIC to the gen-2 based OPLL, we only provide phase noise spectrum of the former one. Fig. 10 shows phase noise spectrum when on chip SG-DBR laser is offset locked to reference ECL at 2.5 GHz. This figure also demonstrates the ESA background and RF synthesizer phase

Fig. 9. Offset locking at multiple frequencies with the second generation OPLL at a RBW of 3 MHz.

Fig. 10. Single-sideband residual phase noise of the heterodyne OPLL at 2.5 GHz offset locking. Phase noise results of the RF synthesizer at 2.5 GHz, and background is also shown here.

noise spectrum at 2.5 GHz. The phase noise variance is calculated to be 0.067 rad<sup>2</sup> from 1 kHz to 10 GHz offset interval. This corresponds to 14.8° standard deviation from the locking point. This OPLL achieves –100 dBc/Hz phase noise at an offset of 5 kHz. These results are comparable with the state of the art results in [20], [21].

For our OPLL system, the time domain equivalent of the phase error variance is equal to the timing jitter in the frequency range from 1 kHz to 10 GHz [22], which can be calculated as:

$$\text{Jitter} = \frac{\sqrt{0.067}}{2\pi \times 2.5 \times 10^9} = 16.48 \, \text{ps}$$

This study is a proof-of-principle demonstration of optical phase locking to a reference laser with low power consumption. This system can be integrated with a better reference sources such as microresonator based optical frequency combs to synthesize arbitrary pure optical frequencies [10], [15]. Also, such narrow RF beat tones generated by beating on-chip laser with the comb lines can be used in a wide range of applications, including short to medium range optical communications, as well as broadband wireless communication in microwave photonic link technology.

TABLE I

POWER BUDGET FOR FIRST GENERATION PIC PROVIDING 10 MW OPTICAL

POWER AND OVERALL OPLL SYSTEM

|                   |                      |                           |            | _                |

|-------------------|----------------------|---------------------------|------------|------------------|

| Gen-1 PIC         | Section              | Current                   | Voltage    | Power            |

|                   |                      | (mA)                      | (V)        | (mW)             |

|                   | Gain(1)              | 73                        | 1.5        | 109.5            |

|                   | FM (1)               | 30                        | 1.5        | 45               |

|                   | PT (1)               | 7                         | 1.3        | 9.1              |

|                   | PD (2)               | 1                         | 2          | 4                |

|                   | BM (1)               | 120                       | 1.5        | 180              |

|                   | SOA (3)              | 70                        | 1.5        | 315              |

|                   |                      |                           |            |                  |

|                   | PIC-1 TOT            | AL                        |            | 662.6            |

| Electronic        | PIC-1 TOT            | 180                       | 3.3        | <b>662.6</b> 594 |

| Electronic<br>ICs |                      | 1                         | 3.3<br>3.3 |                  |

|                   | LIA                  | 180                       |            | 594              |

|                   | LIA<br>XOR           | 180<br>130<br>16          | 3.3        | 594<br>429       |

| ICs               | LIA<br>XOR<br>Op-amp | 180<br>130<br>16<br>TOTAL | 3.3        | 594<br>429<br>96 |

TABLE II

POWER BUDGET FOR SECOND GENERATION PIC PROVIDING 10 MW OPTICAL

POWER AND OVERALL OPLL SYSTEM

| Gen-2 PIC  | Section    | Current<br>(mA) | Voltage<br>(V) | Power<br>(mW) |

|------------|------------|-----------------|----------------|---------------|

|            | Gain(1)    | 73              | 1.5            | 109.5         |

|            | FM (2)     | 20              | 1.3            | 52            |

|            | PT (2)     | 7               | 1.3            | 18.2          |

|            | PD (2)     | 1               | 2              | 4             |

|            | 184        |                 |                |               |

| Electronic | LIA        | 180             | 3.3            | 594           |

| ICs        | XOR        | 130             | 3.3            | 429           |

|            | Op-amp     | 16              | 6              | 96            |

|            | 1119       |                 |                |               |

| Total Po   | 1.3<br>(W) |                 |                |               |

### V. POWER BUDGET OF BOTH OPLLS

As mentioned, one of the primary objectives for this work was to realize a compact, chip-scale OPLL with Watt-level power consumption. In order to do this, one can improve the control electronics, PIC or both. In this work we proposed a novel, compact, low power consumption PIC as a possible solution to realize a chip scale, a Watt level OPLL. Tables I and II provides the power consumption of gen-1 PIC, gen-2 PIC, control electronics and overall OPLL systems. (Numbers in the parentheses for each section in the PIC part tell how many of them are integrated in the PIC, BM: back mirror, FM: front mirror, LIA: limiting amplifier, PD: photodiode, PT: phase tuner, SOA: semiconductor optical amplifier)

As can be seen from these tables gen-1 PIC consumes 660 mW, whereas gen-2 PIC consumes only 184 mW. Together

with the control electronics, the OPLL with gen-2 PIC only consumes record-low 1.3 Watts of electrical power.

# VI. SENSITIVITY OF THE OPLL SYSTEM

For practical applications including coherent optical communications and optical frequency synthesis, OPLLs should be able to lock to input reference power levels in the order of  $\mu$ Ws or even 10s of nWs. In this section, sensitivity analysis of the OPLL is given and experimental sensitivity results are reported. In addition to these results, a novel high gain transimpedance amplifier (TIA) is presented and possible OPLL is proposed using this TIA, which can lock to input power levels as low as 25 pW.

Both OPLLs in this work employs SiGe based COTS limiting amplifier, which has 30 dB differential gain. InP-based PICs have on chip tunable lasers, which produces reasonable amount of optical power. This is mixed with the reference input power through 2  $\times$  2 MMI coupler and the PDs. The detected electrical signal is then fed into the limiting amplifier having a 50  $\Omega$  common mode logic interface. In this system, the minimum required input current level from the balanced PD pair can be found as follows, where  $V_{\rm INPUT,MIN}$  represents the minimum required voltage level just before the limiting amplifier and  $I_{\rm BEAT,MIN}$  represents the minimum required beat current produced by the photodiodes:

$$Gain_{LIA} = 30 \text{ dB} = 31.6$$

$V_{INPUT,MIN} = \frac{300 \text{ mV}}{31.6} = 9.5 \text{ mV}$

$I_{BEAT,MIN} = \frac{9.5 \text{ mV}}{50} = 0.19 \text{ mA}$

From the above equations, we found out that the minimum input current level for offset locking with the designed OPLLs is around 0.19 mA. Given the responsivity of the on-chip PDs is around 1 A/W, the minimum input beat power is around 0.19 mW. If we use this in the coherent detection equation, we can get the minimum required input power level from the reference laser as follows, where  $I_{\rm BEAT}$  represents the beat current produced by the PDs,  $I_{LO}$  is the current produced by LO laser and  $I_{\rm INPUT}$  is the current produced by the reference laser.

$$\begin{split} I_{\text{BEAT}} &= 2\sqrt{I_{LO}\,I_{\text{INPUT}}}\\ I_{\text{INPUT,MIN}} &= \frac{I_{\text{BEAT,MIN}}^2}{4I_{LO}}\\ I_{\text{INPUT,MIN}} &= 9~\mu\text{A} \end{split}$$

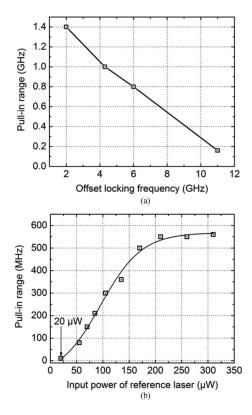

Therefore, the minimum input power required to offset lock this OPLL is theoretically about 9  $\mu$ W, which is close to the experimental results demonstrated in Fig. 11(b), in which the minimum input power level required to operate the OPLL system was found to be 20  $\mu$ W.

Fig. 11(a) and (b) demonstrates the pull-in range of the OPLL system with respect to offset locking frequency and input power levels respectively. Pull-in range varies from 1.4 GHz to 200 MHz depending on the offset frequency range. As expected, the pull-in range decreases with increasing offset frequencies, since the gain of the overall loop reduces. Similarly, decreasing input power levels reduces the pull-in range, and eventually at some point OPLL stops working with the certain input power levels. This minimum input power level was found to be  $20~\mu W$ , as can be seen in Fig. 11(b).

Fig. 11. (a) Pull-in range vs. offset locking frequency. (b) Pull in range vs. input power of the reference external cavity laser. Minimum input power required for locking was found 20  $\mu$ W experimentally.

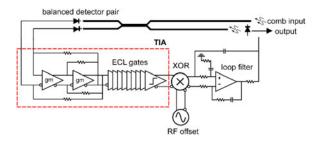

In order to improve the sensitivity of the OPLL further, an application specific transimpedance amplifier (TIA) with low noise, high gain and wide bandwidth using 130 nm SiGe HBT (Silicon Germanium Heterojunction Bipolar Transistor) process was designed. This chip was designed for 80 dB voltage gain and 120 dB-ohm transimpedance gain with 30 GHz 3-dB bandwidth. It has less than 10 pA/ $\sqrt{\rm Hz}$  input referred noise current density up to 20 GHz with respect to 50 fF photodiode capacitance according to the circuit level simulations. With this TIA minimum input power level of reference signal can be reduced to as low as 22.5 pW as follows, where each symbol is used the same way as explained previously:

$$\begin{split} Gain_{\rm TIA} &= 120~{\rm dB}\Omega = 1~{\rm M}\Omega \\ I_{\rm BEAT,MIN} &= \frac{300\,{\rm mV}}{10^6\,\Omega} = 0.3~\mu{\rm A} \\ I_{\rm BEAT} &= 2\sqrt{I_{LO}I_{\rm INPUT}} \\ I_{\rm INPUT,MIN} &= \frac{I_{\rm BEAT,MIN}^2}{4I_{LO}} \\ I_{\rm INPUT,MIN} &= 22.5~{\rm pA} \end{split}$$

Using this TIA, one can make a highly sensitive OPLL, which can be used in optical communications and optical frequency synthesis systems. Fig. 12 shows the proposed OPLL system using this novel TIA. The COTS SiGe limiting amplifier is replaced by this TIA in the proposed OPLL system. Please note that TIA gain was measured functionally to be 60 dB without DC restoration loop. With a proper DC restoration loop, one can get the simulated gain of 80 dB from the TIA. The study relating to the sensitive OPLL system with these high-performance TIAs is ongoing and will be reported in the future.

Fig. 12. Schematic of the sensitive OPLL with low noise, high gain transimpedance amplifier.

### VII. CONCLUSION

In this paper, two chip-scale OPLLs were designed and demonstrated. By designing a novel, low power consumption InP-based photonic integrated receiver circuit, overall power consumption of the first generation OPLL was significantly reduced. The second generation OPLL consumes only 1.35 Watts of electrical power, which is the lowest power consumption reported for an OPLL to the best of author's knowledge. Both OPLLs have 500 MHz loop bandwidth, with 0.067 rad² phase noise variance, integrating from 1 kHz to 10 GHz. Offset locking ranges are 15.2 GHz and 17.8 GHz respectively. Minimum input power level required from the reference side for phase locking was measured to be 20  $\mu$ W. Novel, application specific electrical IC was proposed for lowering the sensitivity of such OPLLs to as low as 25 pW.

### REFERENCES

- L. G. Kazovsky, "Balanced phase-locked loops for optical homodyne receivers: performance analysis, design considerations, and laser linewidth requirements," J. Lightw. Technol., vol. 4, no. 2, pp. 182–195, Feb. 1986.

- [2] V. Ferrero and S. Camatel, "Optical phase locking techniques: An overview and a novel method based on single side sub-carrier modulation," Opt. Exp., vol. 16, no. 2, pp. 818–828, Jan. 2008.

- [3] H. C. Park et al., "40 Gbit/s coherent optical receiver using a Costas loop," Opt. Exp., vol. 20, no. 26, pp. B197–B203, Dec. 2012.

- [4] S. Camatel and V. Ferrero, "Narrow linewidth CW laser phase noise characterization methods for coherent transmission system applications," *J. Lightw. Technol.*, vol. 26, no. 17, pp. 3048–3055, Sep. 2008.

- [5] S. Ristic, A. Bhardwaj, M. J. Rodwell, L. A. Coldren, and L. A. Johansson, "An optical phase-locked loop photonic integrated circuit," *J. Lightw. Technol.*, vol. 28, no. 4, pp. 526–538, Feb. 2010.

- [6] K. Balakier, M. J. Fice, L. Ponnampalan, A. J. Seeds, and C. C. Renaud, "Monolithically integrated optical phase lock loop for microwave photonics," *J. Lightw. Technol.*, vol. 32, no. 20, pp. 3893–3900, Oct. 2014.

- [7] R. J. Steed et al., "Hybrid integrated optical phase-lock loops for photonic terahertz sources," *IEEE J. Sel. Topics Quantum Electron.*, vol. 17, no. 1, pp. 210–217, Feb. 2011.

- [8] D. T. Spencer et al., "Towards an integrated-photonics optical-frequency synthesizer with <1 Hz residual frequency noise," in Proc. Opt. Fiber Commun. Conf., 2017, pp. 1–3.

- [9] C. C. Renaud, C. F. C. Silva, M. Dueser, P. Bayvel, and A. J. Seeds, "Exact, agile, optical frequency synthesis using an optical comb generator and optical injection phase lock loop," in *Proc. IEEE/LEOS Summer Top.* Meet. 2003, pp. WC1 3/67–WC1 3/68.

- Meet., 2003, pp. WC1.3/67–WC1.3/68.

[10] S. Arafin et al., "Towards chip-scale optical frequency synthesis based on optical heterodyne phase-locked loop," Opt. Exp., vol. 25, no. 2, pp. 681–695, Jan. 2017.

- [11] M. Lu, H. C. Park, E. Bloch, L. A. Johansson, M. J. Rodwell, and L. A. Coldren, "A highly-integrated optical frequency synthesizer based on phase-locked loops," in *Proc. Opt. Fiber Commun. Conf.*, 2014, pp. 1–3.

- [12] A. Simsek et al., "A chip-scale heterodyne optical phase-locked loop with low-power consumption," in Proc. Opt. Fiber Commun. Conf., 2017, pp. 1–3.

- [13] L. A. Coldren et al., "High performance InP-based photonic ICs—A tutorial," J. Lightw. Technol., vol. 29, no. 4, pp. 554–570, Feb. 2011.

- [14] M. Lu, "Integrated optical phase-locked loops," Ph.D. dissertation, Electr. Comput. Eng. Dept., Univ. California Santa Barbara, Santa Barbara, CA, USA, 2013.

- [15] S. Arafin et al., "Power-efficient Kerr frequency comb based tunable optical source," *IEEE Photon. J.*, vol. 9, no. 3, pp. 1–14, Jun. 2017.

- [16] [Online]. Available: http://www.adsantec.com/200-asnt5020-pqc.html; http://www.adsantec.com/83-asnt5040-kmc.html

- [17] F. G. Agis et al., "Ultrafast phase comparator for phase-locked loop-based optoelectronic clock recovery systems," J. Lightw. Technol., vol. 27, no. 13, pp. 2439–2448, Jul. 2009.

- [18] K. Balakier, L. Ponnampalam, M. J. Fice, C. C. Renaud, and A. J. Seeds, "Integrated semiconductor laser optical phase lock loops (invited paper)," *IEEE J. Sel. Topics Quantum Electron.*, vol. 24, no. 1, Jan. 2018, Art. no. 1500112.

- [19] M. Lu et al., "Highly integrated optical heterodyne phase-locked loop with phase/frequency detection," Opt. Exp., vol. 20, no. 9, pp. 9736–9741, Apr. 2012.

- [20] R. J. Steed et al., "Monolithically integrated heterodyne optical phase-lock loop with RF XOR phase detector," Opt. Exp., vol. 19, no. 21, pp. 20048– 20053, Oct. 2011.

- [21] M. Lu *et al.*, "An integrated 40 Gbit/s optical costas receiver," *J. Lightw. Technol.*, vol. 31, no. 13, pp. 2244–2253, Jul. 2013.

- [22] T. R. Clark, T. F. Carruthers, P. J. Matthews, and I. N. D. III, "Phase noise measurements of ultrastable 10-GHz harmonically modelocked fibre laser," *Electron. Lett.*, vol. 35, no. 9, pp. 720–721, Apr. 1999.

**Arda Simsek** received the B.S. degree in electrical engineering from Bilkent University, Ankara, Turkey, in 2014, and the M.S. degree in electrical and computer engineering in 2015 from the University of California Santa Barbara, Santa Barbara, CA, USA, where he is currently working toward the Ph.D. degree in electrical and computer engineering. His main research interests include RF and millimeter-wave-integrated circuits in silicon and III–V technologies for phased-array systems and optical phase-locked loops.

Shamsul Arafin (S'08–M'12–SM'17) received the B.Sc. degree in electrical and electronics engineering from Bangladesh University of Engineering and Technology, Dhaka, Bangladesh, in 2005, the M.Sc. degree in communication technology from Universitat Ulm, Ulm, Germany, in 2008, and the Ph.D. degree from the Walter Schottky Institut, Technische Universitat Munchen, Munich, Germany, in 2012. He was a Postdoctoral Research Scholar with the Device Research Laboratory, University of California Los Angeles, Los Angeles, CA, USA. He is currently an Assistant Project Scientist with the University of California Santa Barbara, Santa Barbara, CA. He has authored and coauthored more than 80 papers in leading technical journals and international conferences.

Seong-Kyun Kim received the B.S., M.S., and Ph.D. degrees from the College of Information and Communication Engineering, Sungkyunkwan University, Suwon, South Korea, in 2007, 2009, and 2013, respectively. He is currently a Postdoctoral Research Fellow in the Department of Electrical and Computer Engineering, University of California Santa Barbara, Santa Barbara, CA, USA. His current research interests include RF and millimeter-wave-integrated circuits for wireless communications and phased array.

Gordon B. Morrison received the B.A.Sc. degree (Hons.) in engineering physics from Simon Fraser University, Vancouver, BC, Canada, in 1997, and the Ph.D. degree in engineering physics from McMaster University, Hamilton, ON, Canada, in 2002. His doctoral work, under Prof. D. T. Cassidy, focused on modeling and characterization of gain-coupled DFB lasers. From 1998 to 2002, he spent more than a year with Nortel Networks, Toronto, ON, as a Graduate Student Researcher. From 2002 to 2003, he was a Postdoctoral Fellow with McMaster University, where he was involved in the development of a model for asymmetric-multiple-quantum-well gain and worked on process development for the quantum-well intermixing. In June 2003, he joined the Department of Electrical and Computer Engineering, University of California Santa Barbara, as a Visiting Assistant Research Engineer in Prof. L. Coldren's group, where he participated in the design, fabrication, and characterization of small footprint DBR EMLs using quantum-well-intermixing technology, and used photocurrent spectroscopy to characterize and optimize photonic integrated circuits. In

2005, he joined ASIP (formally III–V Photonics), Houten, The Netherlands, and in 2006, he joined Apogee Photonics (formerly ASIP/T-Networks), Allentown, PA, USA, where he worked on uncooled 1310 EML technology, 40G EA modulators, and monolithically integrated SOA/EA products. Apogee photonics was acquired by CyOptics, Inc., Breinigsville, PA, and subsequently was acquired by Avago technologies. At CyOptics/Avago, he continued work on EML development while additionally focusing on design, characterization, calibration, and qualification of liquid crystal external cavity tunable lasers for coherent applications. In 2014, he joined Freedom Photonics LLC, Santa Barbara, CA, USA, as the Director of Engineering. He is the author or coauthor of more than 30 peer-reviewed journal papers.

**Leif A. Johansson** (M'04) received the Ph.D. degree in engineering from University College London, London, U.K., in 2002. He has been a Research Scientist with the University of California at Santa Barbara, Santa Barbara, CA, USA, and is the founder of Freedom Photonics, Santa Barbara. His current research interests include design and characterization of integrated photonic devices for analog and digital applications and analog photonic systems and subsystems.

Milan L. Mashanovitch (M'99-SM'13) received the Dipl.Ing. degree in electrical engineering from the University of Belgrade, Belgrade, Serbia, in 1998, and the Ph.D. degree in electrical engineering from the University of California Santa Barbara, Santa Barbara, CA, USA, in 2004. He cofounded Freedom Photonics LLC, Santa Barbara, in 2005, and he has been in many technical roles related to product development and program management since. In addition to Freedom Photonics, he was with the University of California Santa Barbara, both as a Researcher on photonic-integrated circuits, and as an Adjunct Professor teaching graduate level classes on semiconductor lasers and photonic ICs. He has coauthored nearly 130 papers, many invited, on photonic-integrated circuits and various photonic devices. He is one of the authors of the second edition of the Diode Lasers and Photonic Integrated Circuits (Wiley, 2012). He has chaired, serves, or has served on technical committees for the IEEE Avionics, Fiber Optics and Photonics Conference, the IEEE Microwave Photonics Conference, the OSA's Integrated Photonics Research Conference, the International Semiconductor Laser Conference, and the Indium Phosphide and Related Materials Conference.

Larry A. Coldren (S'67-M'72-SM'77-F'82-LF'12) received the Ph.D. degree in electrical engineering from Stanford University, Stanford, CA, USA, in 1972. After 13 years in the research area with Bell Laboratories, he joined the University of California at Santa Barbara (UCSB), Santa Barbara, CA, in 1984. He is currently the Fred Kavli Professor of optoelectronics and sensors and holds appointments in the Department of Materials and the Department of Electrical and Computer Engineering. From 2009 to 2011, he was an acting Dean of the College of Engineering. In 1990, he cofounded Optical Concepts, later acquired as Gore Photonics, to develop novel vertical-cavity surface-emitting lasers (VCSEL) technology, and, in 1998, he cofounded Agility Communications, later acquired by JDSU (now Lumentum), to develop widely tunable integrated transmitters. At UCSB, he worked on multiple-section widely tunable lasers and efficient VCSELs. More recently, his group has developed high-performance InP-based photonic-integrated circuits and high-speed high-efficiency VCSELs. He has authored or coauthored more than a thousand journal and conference papers, eight book chapters, a widely used textbook, and 63 issued patents. He is a Fellow of the OSA, the IEE, and the National Academy of Inventors, as well as a Member of the National Academy of Engineering. He received the 2004 John Tyndall Award, the 2009 Aron Kressel Award, the 2014 David Sarnoff Award, the 2015 IPRM Award, and the 2017 Nick Holonyak, Jr., Award.

Mark J. W. Rodwell received the Ph.D. degree from Stanford University, Stanford, CA, USA, in 1988. He holds the Doluca Family Endowed Chair in the Electrical and Computer Engineering with the University of California Santa Barbara (UCSB), Santa Barbara, CA. He also manages the UCSB Nanofabrication Lab. His research group develops nanometer and terahertz transistors, and millimeter-wave and submillimeter-wave-integrated circuits. The work of his group and collaborators has been recognized by the 2010 IEEE Sarnoff Award, the 2012 IEEE Marconi Prize Paper Award, the 1997 IEEE Microwave Prize, the 1998 European Microwave Conference Microwave Prize, and the 2009 IEEE IPRM Conference Award.