# A 200 GHz InP HBT Direct-Conversion LO-Phase-Shifted Transmitter/Receiver with 15 dBm Output Power

Munkyo Seo<sup>#1</sup>, Ahmed S. H. Ahmed<sup>\$\*</sup>, Utku Soylu<sup>\*</sup>, Ali Farid<sup>\*</sup>, Yunsik Na<sup>#</sup>, Mark Rodwell<sup>\*</sup> <sup>#</sup>Department of Electrical and Computer Engineering, Sungkyunkwan University, South Korea <sup>§</sup>Marki Microwave Inc., USA

\*Department of Electrical and Computer Engineering, University of California, Santa Barbara, USA <sup>1</sup>mkseo@skku.edu

*Abstract*—Fully-integrated 200 GHz direct-conversion transmitter and receiver ICs in InP-HBT process are presented. The transmitter exhibits > 20 dB conversion gain for 190-217 GHz, with 16.5 dBm / 15.3 dBm saturated output power at 195 GHz / 200 GHz, consuming 1,250 mW. The receiver has >15dB conversion gain over 190-213 GHz, 825 mW dissipation, and 7.7-9.3 dB noise figure over 200-212 GHz. An LO phase shifter enables sets of these ICs to form phased-array transceivers.

*Keywords*—millimeter wave integrated circuits, THz integrated circuits, direct conversion, InP HBT.

# I. INTRODUCTION

The 100-300GHz spectrum has been drawing significant interest due to its potential for beyond-5G high-speed communication [1]. Recently, integrated transmitters and receivers in various technologies, operating at around 200 GHz or beyond, have been reported [2]-[13]. Challenges in wireless communication at such high frequencies include relatively high path loss and low active device gain. To secure link margin overcoming the path loss, the output power from a single transmitter must be increased. Multiple transmitters can form a phased array, further extending the communication range, with built-in beamforming capability. Low available transistor gain translates into a low power efficiency, e.g. ~1%, typical for 100-200 GHz transmitters. To extend the battery life without excessive heating, the transmitter efficiency must be increased. In this paper, we report the design and measured results of 200 GHz QPSK/QAM-compatible transmitter (Fig. 1) and receiver IC (Fig. 2) with high output power and integrated LO phase shifter, fabricated in Teledyne 250nm InP HBT Technology.

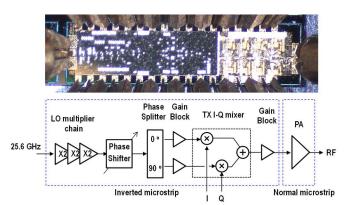

Fig. 1. A 200 GHz direct-conversion transmitter: chip photo (top) and block diagram (bottom). Chip size: 2.9×0.75mm<sup>2</sup>

## **II. TRANSMITTER DESIGN**

The 200 GHz transmitter consists of a LO multiplier (×8), phase shifter, phase splitter, I-Q mixer and power amplifier, as shown in Fig. 1. Two types of lines are used: inverted microstrip (IMSL) and normal microstrip lines (MSL). IMSLs are used for LO circuits, mixer and gain block, where the device density is relatively high. The top-metal (M4) provides a continuous ground plane regardless of device contacts at M1, eliminating performance degradation (reduced bandwidth and gain, cross-talk) from impedances due to ground plane holes. Uncertainty in layout EM modelling is thus reduced at the cost of extra line loss: 2.5 dB/mm and 1.1 dB/mm at 200 GHz, for IMSL and MSL, respectively. The PA and LNA are implemented in MSL for best PAE and lowest noise figure. Simulated loss of an IMSL-MSL transition is < 0.1dB.

## A. LO Multiplier (×8)

The 8:1 LO multiplier is implemented by cascading three stages of frequency-doublers in push-push configuration. In simulation, the minimum required power at the multiplier input is -15 dBm, and the output power remains > 0 dBm for 180-230 GHz, while consuming 250 mW.

# B. LO Phase shifter

A 200 GHz phase shifter is implemented in the LO path to enable multiple ICs to form LO-beamforming phased-arrays. The benefit of LO-beamforming, compared to the RFbeamforming counterpart, is that the system performance is

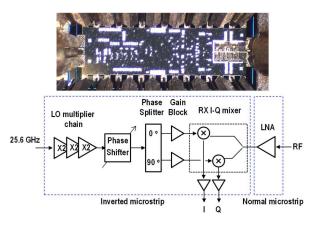

Fig. 2. A 200 GHz direct-conversion receiver: chip photo (top) and block diagram (bottom). Chip size:  $2.3 \times 0.85 \text{mm}^2$

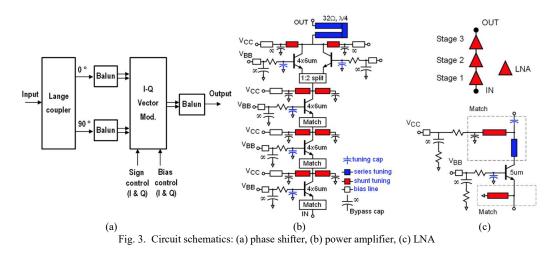

less sensitive to the bandwidth and linearity of the phase shifter, at the cost of multiple up-conversion mixers. The phase shifter is based on I-Q vector-modulator (Fig. 3 (a)), to avoid insertion loss and amplitude variations of passive phase shifters. A Lange coupler generates I and Q-path with 90° relative phase shift. The magnitude and polarity of each LO path is controlled by a double-balanced mixer, followed by a balun for a single-ended output. The designed phase shifter has -5 dB insertion loss at 200 GHz, consuming 160 mW. In simulation, the magnitude and phase error of the Lange coupler is < 0.3 dB and < 2°, respectively, with < 1.5 dB insertion loss, for 170-250 GHz.

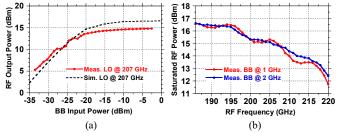

Fig. 5. TX measured results: (a) conversion gain vs. baseband frequency at a fixed LO, (b) conversion gain vs. LO frequency at a fixed baseband frequency.

Fig. 6. TX measured results: (a) RF output power vs. baseband input power at 1 GHz baseband frequency, (b) saturated RF power vs. RF frequency.

## C. TX I-Q mixer

The phase shifter output is split into I and Q-paths by another Lange coupler. The I-Q mixer consists of two doublebalanced mixers with a common inductor load. A 5-10 $\mu$ m wire will introduce 3-4° phase delay at 200 GHz, and such delays, especially if accumulated, tend to reduce the bandwidth. Layout asymmetries in I and Q-path will create amplitude and phase imbalance, degrading the error-vector magnitude (EVM) performance. Therefore, minimum design rules were used in the mixer layout, while minimizing I-Q asymmetry. Simulated I-Q imbalance is < 0.7 dB and < 3° up to 20 GHz baseband input, including layout parasities.

# D. Power Amplifier

The PA uses four capacitively linearized common-base (CB) stages, designed for high efficiency and compact layout (Fig. 3(b)). This design shows superior efficiency compared to common-emitter or grounded common-base at 1dB gain compression [14]. Two power cells (48-µm HBT periphery) are combined by a 2:1 combiner based on a single  $\lambda/4$  line [14]-[16]. Shunt inductors tune the transistor parasitics. One level driver scaling is used for a reasonable efficiency while reusing the same transistor footprint. The drivers have a separate bias which can be separately tuned for high efficiency. Simulated saturated power of the PA is 17 dBm at 200 GHz with > 20 dB gain, while dissipating 450 mW.

#### **III. RECEIVER DESIGN**

The 200 GHz receiver shares the same LO building blocks in the transmitter. The LNA is implemented in MSL to keep its noise figure low, while other circuits use IMSL.

#### A. LNA

The LNA uses common-base stages with the base capacitance adjusted so that the source impedance for minimum noise measure is equal to the stage input impedance, this allowing simultaneous input matching for reflection coefficient and for noise (Fig. 3(c)). The HBT junction area of each stage is scaled so that the source conductance for minimum noise measure is 20mS; this permits the input stage to be noise-

| Table I. | Comparison | of recently published >20 | 0 GHz integrated transmitters |

|----------|------------|---------------------------|-------------------------------|

|          |            |                           |                               |

| Ref. | Technology       | Integrated TX circuit blocks                    | Modulation    | Freq.<br>(GHz) | P <sub>sat</sub><br>(dBm) | P <sub>DC</sub><br>(mW) | Efficiency<br>(%) |

|------|------------------|-------------------------------------------------|---------------|----------------|---------------------------|-------------------------|-------------------|

| [2]  | 0.1µm GaAs mHEMT | IF-mixer, LO multiplier (×2), PA, antenna       | External mod. | 220            | -6                        | 110                     | 0.23              |

| [3]  | 50nm GaAs mHEMT  | IF-mixer, PA                                    | External mod. | 240            | 1                         | N/A                     | N/A               |

| [4]  | 32nm SOI CMOS    | LO VCO, OOK mod, PA, antenna                    | OOK           | 210            | 4.6                       | 240                     | 1.20              |

| [5]  | 65nm CMOS        | IQ-mixer, tripler                               | QPSK          | 240            | -0.5                      | 220                     | 0.41              |

| [6]  | 250nm InP-HBT    | IF-mixer, LO driver, LO oscillator              | External mod. | 298.1          | -2.3                      | 452                     | 0.13              |

| [7]  | 130nm SiGe       | IQ-mixer, LO multiplier (×16), PA               | 16-QAM/64-QAM | 240            | -4.4                      | 1,033                   | 0.04              |

| [8]  | 130nm SiGe       | Mixer, LO driver, antenna                       | BPSK          | 190            | -6                        | 32 <sup>1</sup>         | 0.78              |

| [9]  | 40nm CMOS        | IQ-mixer, LO multiplier (×3)                    | 16-QAM        | 265.68         | -1.6                      | 890                     | 0.08              |

| [10] | 130nm SiGe       | IQ-mixer, LO multiplier (×16), PA               | 16-QAM        | 220-255        | 5                         | 960                     | 0.33              |

| [11] | 130nm SiGe       | IQ-mixer, LO multiplier (×16), PA               | QPSK          | 225-255        | 7.5                       | 960 <sup>2</sup>        | 0.59              |

| [12] | 130nm SiGe       | IQ-mixer, LO multiplier (×8), PA                | 16-QAM        | 240            | 124                       | 1,237                   | 1.28              |

| [13] | 80nm InP-HEMT    | IF-mixer, LO driver, PA <sup>3</sup>            | External mod. | 290            | 12                        | 6,600                   | 0.24              |

| This | 250nm InP-HBT    | IQ-mixer, LO multiplier (×8), phase shifter, PA | QPSK / QAM    | 195            | 16.5                      | 1,250                   | 3.57              |

| work |                  |                                                 |               | 200            | 15.3                      | 1,250                   | 2.71              |

<sup>1</sup>P<sub>DC</sub> not including LO generator at 190 GHz <sup>2</sup>P<sub>DC</sub> for 1-channel I-Q TX+LO <sup>3</sup>Individually packaged, not integrated <sup>4</sup>Measured from PA breakout

matched to 500hms with a single inductive shunt element, avoiding the added attenuation, hence the added noise, of a series matching element. Center frequencies of the three stages are staggered to provide wider bandwidth.

## B. RXI-Q Mixer and 50-ohm Driver

The receiver I-Q mixer consists of two double-balanced cores, and minimum design rules were used in layout, similarly to the TX mixer. The mixer is followed by an emitter-degenerated differential pair to drive 50-ohm load.

#### IV. MEASURED RESULTS

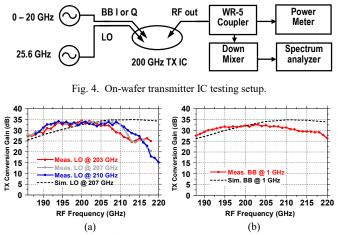

The fabricated transmitter IC was measured using on-wafer

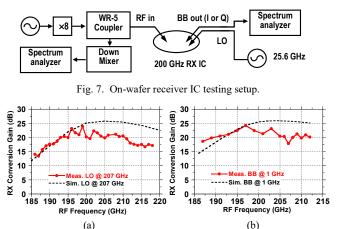

Fig. 8. RX measured results: (a) conversion gain vs. RF frequency at a fixed LO, (b) conversion gain vs. RF frequency at a fixed BB frequency.

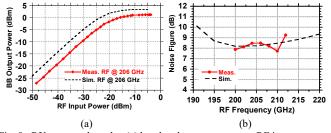

Fig. 9. RX measured results: (a) baseband output power vs. RF input power at  $f_{LO} = 207$  GHz and  $f_{RF} = 206$  GHz, (c) measured vs. simulated noise figure.

test setup in Fig. 4. A WR-5 directional coupler was used for simultaneous spectrum and power measurement. First, the baseband frequency  $f_{BB}$  was varied with fixed LO frequency  $f_{LO}$ . In Fig. 5(a), the peak measured conversion gain was 34 dB with ~20 GHz of 3-dB bandwidth (only I-channel was driven). Second,  $f_{LO}$  was swept with  $f_{BB} = 1$  GHz. The measured conversion gain was > 25 dB for 190-220 GHz in Fig. 5(b), implying the LO multiplier bandwidth is > 30 GHz. The measured saturated output power was 16.5 dBm and 15.3 dBm, at  $f_{RF} = 195$  GHz and 200 GHz, respectively, in Fig. 6. The transmitter IC consumes 1,250 mW.

The receiver was tested using on-wafer setup in Fig. 7. The peak measured conversion gain was 25 dB and remains > 15 dB for 190-213 GHz (Fig. 8). The measured input  $P_{1dB}$  of the receiver was -24 dBm in Fig. 9(a), with 825 mW dissipation. The receiver noise figure (Fig. 9(b)), measured with a VDI-WR5.1NS hot/cold noise source connected to the receiver input, was 7.7-9.3 dB over 200-212 GHz. The receiver output noise power spectral density was measured at 100MHz using a ~20dB low-noise post-amplifier and a spectrum analyser.

Testing of a breakout circuit shows that the 200 GHz phase shifter is fully functional. For all measurement, the reference plane was at the probe tip, with losses of 140-220 GHz GGB probes, coupler, waveguides, cables, etc, all de-embedded. Table I compares this work with prior publications. To the best of authors' knowledge, the presented transmitter exhibits the highest output power and efficiency, among all integrated up-converting transmitters beyond 200 GHz.

#### V. CONCLUSION

A 200 GHz transmitter and receiver IC were presented with record output power (15.3-16.5 dBm) and efficiency (2.71-3.57%) over 195-200 GHz. Further testing is under way, including modulated testing (e.g. QPSK or QAM).

#### ACKNOWLEDGMENT

This work was supported by ComSenTer, a JUMP program sponsored by the Semiconductor Research Corporation, by a gift from Samsung corporation and by the Samsung Electronics, under the Grant SRFC-TB1803-06.

#### REFERENCES

- [1] M. J. W. Rodwell et al., "100-340GHz Systems: Transistors and Applications," in *Proc. IEEE IEDM*, 2018, pp. 14.3.1-14.3.4

- [2] M. Abbasi et al., "Single-chip 220-GHz active heterodyne receive and transmitter MMICs with on-chip integrated antenna," IEEE Trans. Microwave Theory and Techniques, vol. 59, no. 2, Feb. 2011.

- [3] D. Lopez-Diaz et al., "A subharmonic chipset for gigabit communication around 240 GHz," 2012 IEEE/MTT-S International Microwave Symposium Digest, Montreal, QC, Canada, 2012, pp. 1-3.

- [4] Z. Wang, P. Chiang, P. Nazari, C. Wang, Z. Chen and P. Heydari, "A CMOS 210-GHz Fundamental Transceiver with OOK Modulation," in IEEE Journal of Solid-State Circuits, vol. 49, no. 3, pp. 564-580, March 2014.

- [5] S. Kang, S. V. Thyagarajan and A. M. Niknejad, "A 240 GHz Fully Integrated Wideband QPSK Transmitter in 65 nm CMOS," in IEEE Journal of Solid-State Circuits, vol. 50, no. 10, pp. 2256-2267, Oct. 2015.

- [6] S. Kim et al., "300 GHz Integrated Heterodyne Receiver and Transmitter with On-Chip Fundamental Local Oscillator and Mixers," in IEEE Transactions on Terahertz Science and Technology, vol. 5, no. 1, pp. 92-101, Jan. 2015.

- [7] N. Sarmah et al., "A Fully Integrated 240-GHz Direct-Conversion Quadrature Transmitter and Receiver Chipset in SiGe Technology," in IEEE Transactions on Microwave Theory and Techniques, vol. 64, no. 2, pp. 562-574, Feb. 2016.

- [8] D. Fritsche, P. Stärke, C. Carta and F. Ellinger, "A Low-Power SiGe BiCMOS 190-GHz Transceiver Chipset with Demonstrated Data Rates up to 50 Gbit/s Using On-Chip Antennas," in IEEE Transactions on Microwave Theory and Techniques, vol. 65, no. 9, pp. 3312-3323, Sept. 2017.

- [9] S. Lee et al., "An 80-Gb/s 300-GHz-Band Single-Chip CMOS Transceiver," in IEEE Journal of Solid-State Circuits, vol. 54, no. 12, pp. 3577-3588, Dec. 2019.

- [10] P. Rodríguez-Vázquez, J. Grzyb, B. Heinemann and U. R. Pfeiffer, "A 16-QAM 100-Gb/s 1-M Wireless Link with an EVM of 17% at 230 GHz in an SiGe Technology," in IEEE Microwave and Wireless Components Letters, vol. 29, no. 4, pp. 297-299, April 2019.

- [11] P. Rodriguez-Vazquez, J. Grzyb, B. Heinemann and U. R. Pfeiffer, "A QPSK 110-Gb/s Polarization-Diversity MIMO Wireless Link With a 220–255 GHz Tunable LO in a SiGe HBT Technology," in IEEE Transactions on Microwave Theory and Techniques, vol. 68, no. 9, pp. 3834-3851, Sept. 2020.

- [12] M. H. Eissa, N. Maletic, E. Grass, R. Kraemer, D. Kissinger and A. Malignaggi, "100 Gbps 0.8-m Wireless Link based on Fully Integrated 240 GHz IQ Transmitter and Receiver," 2020 IEEE/MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 2020, pp. 627-630.

- [13] H. Hamada et al., "300-GHz-Band 120-Gb/s Wireless Front-End Based on InP-HEMT PAs and Mixers," in IEEE Journal of Solid-State Circuits, vol. 55, no. 9, pp. 2316-2335, Sept. 2020.

- [14] A. S. H. Ahmed, M. Seo, A. A. Farid, M. Urteaga, J. F. Buckwalter and M. J. W. Rodwell, "A 140GHz power amplifier with 20.5dBm output power and 20.8% PAE in 250-nm InP HBT technology," 2020 IEEE/MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 2020, pp. 492-495.

- [15] A. S. H. Ahmed, U. Soylu, M. Seo, M. Urteaga, J. F. Buckwalter and M. J. W. Rodwell., " A 190-210GHz Power Amplifier with 17.7-18.5dBm Output Power and 6.9-8.5% PAE.," in press, *Proc.* IMS2021.

- [16] A. S. H. Ahmed, M. Seo, A. A. Farid, M. Urteaga, J. F. Buckwalter and M. J. W. Rodwell, "A 200mW D-band Power Amplifier with 17.8% PAE in 250-nm InP HBT Technology," 2020 15th European Microwave Integrated Circuits Conference (EuMIC), Utrecht, Netherlands, 2021, pp. 1-4.