### University of California Santa Barbara

# High-efficiency Millimeter-wave Power Amplifiers and Packaging Design

A dissertation submitted in partial satisfaction of the requirements for the degree

$\begin{array}{c} {\rm Doctor~of~Philosophy} \\ {\rm in} \\ {\rm Electrical~and~Computer~Engineering} \end{array}$

by

Ahmed Samir Hamed Sayed Ahmed

### Committee in charge:

Professor Mark Rodwell, Chair Professor James Buckwalter Professor Ali Niknejad, University of California, Berkeley Professor Loai Salem Dr. Miguel Urteaga, Teledyne Scientific and Imaging

December 2020

| _                | Professor James Buckwalter                             |

|------------------|--------------------------------------------------------|

| -<br><b>'</b> ro | fessor Ali Niknejad, University of California, Berkele |

| _                | Professor Loai Salem                                   |

| _<br>_           | Or Migual Urtanga Taladyma Sajantifia and Imaging      |

| L                | Or. Miguel Urteaga, Teledyne Scientific and Imaging    |

November 2020

High-efficiency Millimeter-wave Power Amplifiers and Packaging Design

Copyright © 2020

by

Ahmed Samir Hamed Sayed Ahmed

### Acknowledgements

I was extremely lucky to join a research group with tremendous talent. I express my deepest gratitude to my advisor Professor Mark Rodwell. It has been a privilege working with him during my Ph.D. Prof. Rodwell has a vision for the next communication generation which may shape the future industry. I learned lots of millimeter wave knowledge with access to the state-of-the-art technologies and equipment. Not only I learned lots of technical science, but also I learned to think critically of any new problem which reflected on my personal life as well. I would also like to thank my Ph.D. committee members, Professor James Buckwalter, Professor Ali Niknejad, Professor Loai Salem, and Dr. Miguel Urteaga for their valuable support during my research. We had lots of interaction and sharing ideas between our group and Prof. James Buckwalter's team in many joint projects. We also had a regular meetings, during ComSenter, between different research groups (UCB, UCSD,...etc) and I got a lot of fruitful feedback from Prof. Niknejad. I did a lot of work in Teledyne technologies and Dr. Miguel supported me with lots of practical consideration in mm-wave IC and packaging design.

I would like to thank previous and current group members for their tremendous support. Thanks to the previous members: postdoc. Seong-Kyun Kim, Rob Maurer, and Arda Simsek for their support. I was also lucky to work with the visiting professor Munkyo Seo in my last year in the Ph.D. Thanks to the current members: Ali Farid, and Utku Soylu for their great help in the technical discussion and lab measurement. I would also like to thank device group members Brian Markman, Hsin-Ying Tseng, and Yihao Fang for their valuable interactions.

Especial thanks to Kyocera team (Minami, David, Kevin, Paul, Yoshi, Hisanao, Yamaguchi, Chong) for the board fabrication and assembly. We were extremely lucky to work

with one of the top-tier companies in assembly and board fabrication. All the packaging efforts are based on their guide, review, fabrication, and assembly.

I am also grateful to be part of ComSenter where we had lots of collaboration between different research teams among the universities. Thanks to the UCB team (Prof. Ali Niknejad, Anita, James, Nima, and Lorenzo) for their valuable comments and suggestions during the regular meetings and reviews. Also, we collaborated with UCSD (Prof. Gabriel Rebeiz, Zhe, and Siwei). They helped us in building the Quartz antenna for the 210GHz array. We also had regular meetings with Buckwalter's group (Andrea, Kang, Jeff, Everett, Ahmed, Jonathan, Eythan, and Cam) and Madhow's team (Mohamed, and Maryam).

I want to thank Teledyne Scientific and Imaging for IC fabrication. Also, I would like to thank (Miguel, Zach, and Andrea) for valuable insights and design reviews. Thanks to Global Foundries for fabricating the ICs and the National Science Foundation (NSF) GigaNets program and Semiconductor Research Consortium (SRC) ComSenTer program for funding my research.

I was glad that our research attracted interest from Samsung Research America. They offered me an internship and we working closely in joint projects. I am grateful to work with Navneet, Hamid, Daquan, Shadi, and Gary Xu for their valuable support.

Finally, I want to thank my parents, brother and sister for their tremendous support.

## Curriculum Vitæ

### Ahmed Samir Hamed Sayed Ahmed

#### Education

| 2020 | Ph.D. in Electrical and Computer Engineering (Expected), Univer- |

|------|------------------------------------------------------------------|

|      | sity of California, Santa Barbara.                               |

| 2015 | M.Sc in Electronics and Electrical Communications Engineering,   |

|      | Cairo University, Cairo, Egypt.                                  |

| 2012 | B.S. in Electronics and Electrical Communications Engineering,   |

|      | Cairo University, Cairo, Egypt.                                  |

### **Professional Experience**

| 9/2015 -2020     | Research Assistant at the High-Frequency Electronics Group at Uni- |

|------------------|--------------------------------------------------------------------|

|                  | versity of California, Santa Barbara, USA.                         |

| 6/2019 -12/2019  | Summer Internship at Samsung Research America, Dallas, Texas, USA. |

| 6/2017 - 10/2017 | Summer Internship at Skyworks, Newbury Park, Ventura, USA.         |

| 9/2015 -2020     | Research and Teaching Assistant at Cairo University, Cairo, Egypt. |

### **Publications**

- 1. A. S. H. Ahmed, Munkyo Seo, A. A. Farid, M. Urteaga and M. J. W. Rodwell, "A 140GHz power amplifier with 20.5dBm output power and 20.8% PAE in 250-nm InP HBT technology," 2020 IEEE/MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 2020, pp. 492-495.

- A. S. H. Ahmed, Munkyo Seo, A. A. Farid, M. Urteaga and M. J. W. Rodwell, "A 200mW D-band Power Amplifier with 17.8% PAE in 250-nm InP HBT Technology," accepted to 2020 15th (EuMIC), Utrecht, 2020

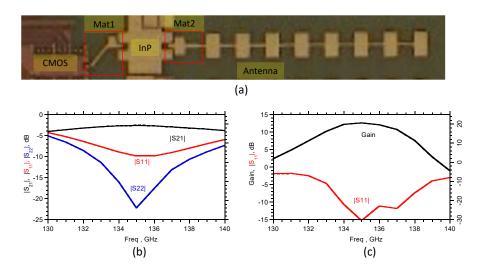

- 3. A. S. H. Ahmed, A. Simsek, A. A. Farid, A. D. Carter, M. Urteaga and M. J. W. Rodwell, "A W-Band transmitter channel with 16dBm output power and a receiver channel with 58.6mW DC power consumption using heterogeneously integrated InP HBT and Si CMOS technologies"," 2019 (IMS), Boston, MA, USA, 2019.

- 4. A. S. H. Ahmed, A. A. Farid, M. Urteaga and M. J. W. Rodwell, "204GHz Stacked-Power Amplifiers Designed by a Novel Two-Port Technique," 2018 13th European Microwave Integrated Circuits Conference (EuMIC), Madrid, 2018, pp. 29-32.

- A. S. H. Ahmed, A. Simsek, M. Urteaga and M. J. W. Rodwell, "8.6-13.6 mW Series-Connected Power Amplifiers Designed at 325 GHz Using 130 nm InP HBT Technology," 2018 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), San Diego, CA, 2018, pp. 164-167.

- 6. A. Simsek, Seong-Kyun Kim, Mohammed Abdelghany, A. S. H. Ahmed, A. A. Farid, Upamanyu Madhow, M. Urteaga and M. J. W. Rodwell, "A 146.7 GHz Transceiver with 5 GBaud Data Transmission using a Low-Cost Series-Fed Patch Antenna Array through Wirebonding Integration," 2020 IEEE Radio and Wireless Symposium (RWS), San Antonio, TX, USA, 2020.

- A. A. Farid, A. Simsek, A. S. H. Ahmed and M. J. W. Rodwell, "A Broadband Direct Conversion Transmitter/Receiver at D-band Using CMOS 22nm FDSOI," 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2019,

- 8. A. Simsek, Seong-Kyun Kim, A. S. H. Ahmed, Robert Maurer M. Urteaga and M. J. W. Rodwell, "A Dual-Conversion Front-End with a W-Band First Intermediate Frequency for 1-30 GHz Reconfigurable Transceivers," in 2019 IEEE Radio and Wireless Symposium (RWS), Florida, CA, USA, in press.

- 9. A. Simsek, A. S. H. Ahmed, A. A. Farid, U. Soylu and M. J. W. Rodwell, "A 140GHz Two-Channel CMOS Transmitter Using Low-Cost Packaging Technologies," 2020 IEEE Wireless Communications and Networking Conference Workshops (WCNCW), Seoul, Korea (South), 2020, pp. 1-3,

#### Abstract

High-efficiency Millimeter-wave Power Amplifiers and Packaging Design

by

### Ahmed Samir Hamed Sayed Ahmed

There is an increasing demand for high data rate communications. The available spectrum is nearly full, and industry considered 5G systems. In this research, we considered the next-generation systems (100-340GHz). Millimeter frequencies permit much larger spectrum and shorter wavelengths provides massive MIMO array and high image resolution. The thesis focuses on building the hardware and necessary components for such systems. There are lots of challenges in building the hardware; path loss and weather attenuation are high which demands high output power with high efficiency. Additionally, mm-wave packaging is very challenging. Here, we introduce a network theory to analyze the amplifiers degrees of freedom and design for maximum PAE. The proposed theory considers the stacking and parallel power combing approaches using network theory techniques. From the theory, we can design using arbitrarily complex transistor models, and lossy interconnect for maximum PAE. The theory establishes a design framework for high efficiency power amplifier design.

We demonstrate high efficiency mm-wave power amplifiers (140, 210, and 300GHz) with moderate output powers. The 140GHz amplifiers produce measured output power (20.5-23dBm) with record efficiency of 17.8-20.8%PAE. We are also presenting 17.7-18.5dBm output power over 190-210GHz frequency range with high efficiency of 6.9-8.5% PAE. We simulated 17dBm saturated power at 300GHz. The design key features are: 1) Low loss

combiner: we proposed transmission line network combiner which is more compact and less lossy compared to Wilkinson. 2) careful selection for the power cell. We have done a comparative study between different topologies and found that common base showed superior performance, compared to common emitter, at the frequency of interest and Teledyne technologies. 3) driver design: We optimized the driver size and topology to achieve high PAE.

The last part of the thesis is massive MIMO demonstration and mm-wave packaging. We started with a CMOS transmitter and receiver with advanced copper pillar. We also have bare InP power amplifiers. We present all the design procedures and challenges moving from the wafer level to the packaging and complete system. We demonstrate a single CMOS channel transmitter and receiver with eight element series fed patch antenna showing EIRP of 13dBm at 135 GHz. We also built a tile with eight elements transmitter or receiver which is currently in fabrication. High efficiency with 100mW InP amplifier is integrated with the CMOS transmitter to increase the system EIRP and cover long ranges

# Contents

| Cı | Curriculum Vitae |                                                   |      |  |

|----|------------------|---------------------------------------------------|------|--|

| Al | bstra            | $\operatorname{\mathbf{ct}}$                      | viii |  |

| Li | st of            | Figures                                           | xiv  |  |

| Li | st of            | Tables                                            | xxi  |  |

| 1  | Intr             | oduction                                          | 1    |  |

|    | 1.1              | Millimeter Wave for Next Communication Generation | 1    |  |

|    | 1.2              | Dissertation Contributions and Organization       | 2    |  |

|    | 1.3              | Permissions and Attributions                      | 5    |  |

| 2  | Mill             | limeter-Wave Power Amplifier Fundamentals         | 7    |  |

|    | 2.1              | Introduction                                      | 7    |  |

|    | 2.2              | Unit Cell Design                                  | 8    |  |

|    |                  | 2.2.1 Loadline Matching                           | 8    |  |

|    |                  | 2.2.2 LoadLine Matching Limitations               | 11   |  |

|    |                  | 2.2.3 Load-pull techniques                        | 12   |  |

|    | 2.3              | Driver Design                                     | 13   |  |

|    | 2.4              | Power Combining Techniques                        | 14   |  |

|    | 2.5              | Stability Analysis                                | 14   |  |

|    | 2.6              | Technology Selection Criteria                     | 16   |  |

| 3  | Net              | work Theory for High-Efficiency Amplifier Design  | 19   |  |

|    | 3.1              | Introduction                                      | 19   |  |

|    | 3.2              | Degrees of Freedom in Amplifiers                  | 21   |  |

|    | 3.3              | Key Factors for High-Efficiency Amplifiers        | 24   |  |

|    | 3.4              | Optimum Cell Selection                            | 25   |  |

|    | 3.5              | Stacked Power Amplifier                           | 29   |  |

|    |                  | 3.5.1 Stack Concept                               | 29   |  |

|    |                  | 3.5.2 Conventional Stack Design Procedures        | 31   |  |

|   |     | 3.5.3            | Limitations of the Existing Approach                                  | 32        |

|---|-----|------------------|-----------------------------------------------------------------------|-----------|

|   |     | 3.5.4            | Network Theory for Stacked Power Amplifier: Motivation                | 32        |

|   |     | 3.5.5            | Stack Design Procedure                                                | 33        |

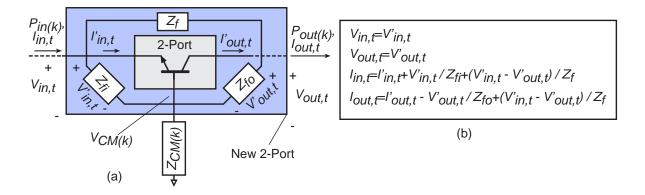

|   |     | 3.5.6            | 2-port Transistor Modeling                                            | 33        |

|   |     | 3.5.7            | V&I Distribution for Maximum PAE                                      | 34        |

|   |     | 3.5.8            | Generic Stack Cell Design                                             | 36        |

|   |     | 3.5.9            | Stacked Stages for Maximum PAE                                        | 40        |

|   |     |                  | Example: Three CB Stacked PA                                          |           |

|   |     | 3.5.11           | CE Stack Procedures                                                   | 48        |

|   |     | 3.5.12           | CE Stack Design Procedure                                             | 49        |

|   |     | 3.5.13           | Example: Three CE Stacked PA                                          | 50        |

|   |     | 3.5.14           | Example: Neutralization Impact                                        | 53        |

|   |     | 3.5.15           | General Form of the Equations                                         | 54        |

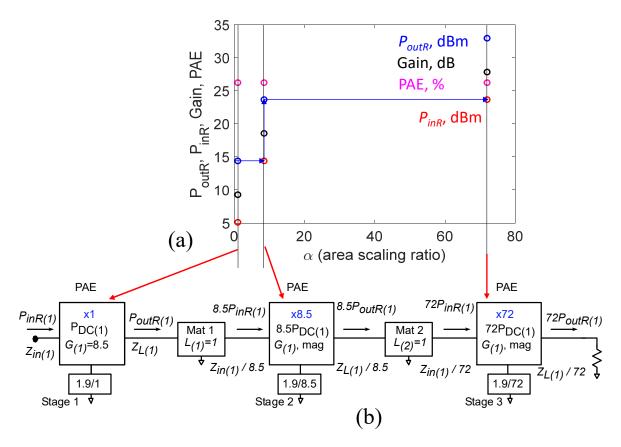

|   | 3.6 | Area F           | Progression Techniques (Parallel Combining Techniques)                | 57        |

|   |     | 3.6.1            | Motivation                                                            | 57        |

|   |     | 3.6.2            | Analysis of Amplifier Designed by Area Progression Technique          | 58        |

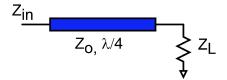

|   |     | 3.6.3            | Wilkinson Power Combiner                                              | 60        |

|   |     | 3.6.4            | Pros                                                                  | 62        |

|   |     | 3.6.5            | Cons                                                                  | 63        |

|   |     | 3.6.6            | Proposed General Transmission Line Combiner                           |           |

|   |     | 3.6.7            | Pros                                                                  | 65        |

|   |     | 3.6.8            | Limitations                                                           | 65        |

|   |     | 3.6.9            | Example for Area Progression Technique: Three-Stage Amplifier         |           |

|   |     | 3.6.10           | Area Progression Technique Efficiency                                 | 67        |

|   | 3.7 | Stacke           | d Amplifier with Area Progression                                     |           |

|   |     | 3.7.1            | Motivation                                                            |           |

|   | 3.8 | Design           | Guide for Amplifier Design                                            | 73        |

| 4 | Exp | erimer           | ntal Verifications for High-Efficiency Power Amplifiers ( ${\sim}140$ | GHz       |

|   | 210 | ,                | and 300GHz)                                                           | <b>76</b> |

|   | 4.1 |                  | $\operatorname{uction}$                                               |           |

|   | 4.2 | $250\mathrm{nm}$ | and 130nm InP HBT technology                                          | 78        |

|   | 4.3 | 140GH            | Iz Power Amplifier with $20.8\% PAE$ and $20.5 dBm$ Output Power      | 79        |

|   |     | 4.3.1            | Amplifier Design                                                      | 79        |

|   |     | 4.3.2            | Unit Cell design                                                      | 80        |

|   |     | 4.3.3            | Driver design                                                         | 83        |

|   |     | 4.3.4            | Combiner design                                                       |           |

|   |     | 4.3.5            | S-Parameters measurements                                             |           |

|   |     | 4.3.6            | Power Measurements                                                    | 87        |

|   |     | 4.3.7            | Summary                                                               |           |

|   | 4.4 | 131GH            | Iz Power Amplifier with $17.8\% PAE$ and $200 mW$ Output Power $$     | 91        |

|   |     | 4.4.1            | Power and Driver Cells Design                                         | 91        |

|   |              | 4.4.2 | Low Loss Transmission Line Combiner                                    |

|---|--------------|-------|------------------------------------------------------------------------|

|   |              | 4.4.3 | S-parameters Measurements                                              |

|   |              | 4.4.4 | Power Measurements                                                     |

|   |              | 4.4.5 | Summary                                                                |

|   | 4.5          | 204GF | Iz Stacked-Power Amplifiers                                            |

|   |              | 4.5.1 | Two Cell Amplifier Design                                              |

|   |              | 4.5.2 | Four-Cells Amplifier Design                                            |

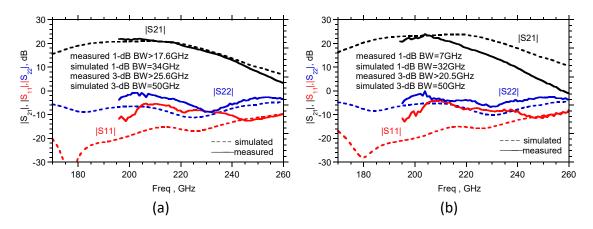

|   |              | 4.5.3 | S-Parameters Measurements                                              |

|   |              | 4.5.4 | Power Measurements                                                     |

|   | 4.6          | 325G  | Hz Stacked Power Amplifier with 8.6-13.6 mW Output Power $ \dots $ 106 |

|   |              | 4.6.1 | Single Cell Power Amplifier Design                                     |

|   |              | 4.6.2 | 2:1 Power Combined Design                                              |

|   |              | 4.6.3 | Measurement Results                                                    |

|   | 4.7          | Sumn  | nary and Conclusion                                                    |

| 5 | 210          | СПа т | ransmitter for MIMO Demonstration 113                                  |

| J | 5.1          |       | ation                                                                  |

|   | $5.1 \\ 5.2$ |       | Iz Transmitter with $\sim 2 \text{dBm}$ Output Power                   |

|   | 5.2          |       | Iz Transmitter with $\approx$ 2dBm Output Fower                        |

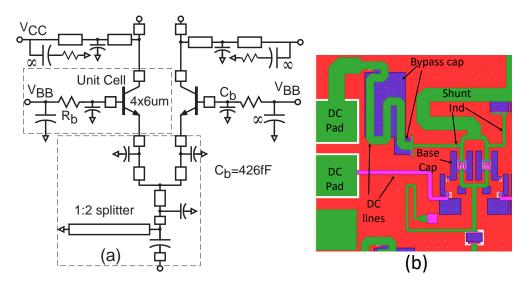

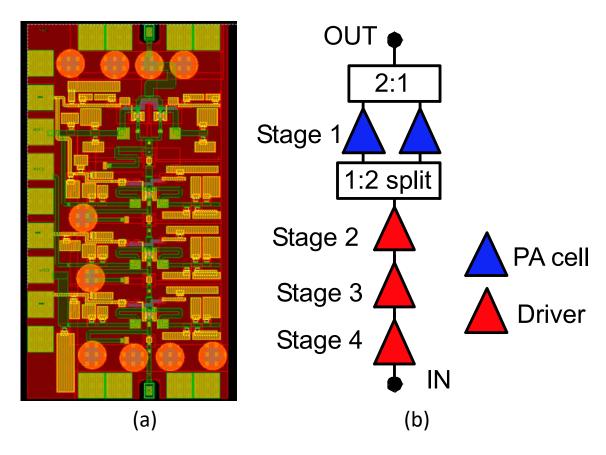

|   | 5.5          | 5.3.1 | 210GHz Amplifier Design with $\sim$ 18dBm output power and 8% PAE 116  |

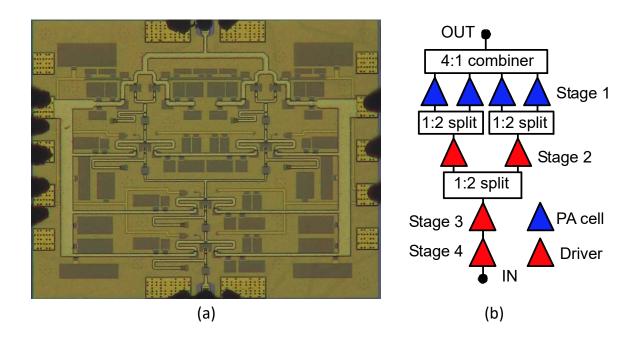

|   |              | 5.3.2 | Amplifier Design                                                       |

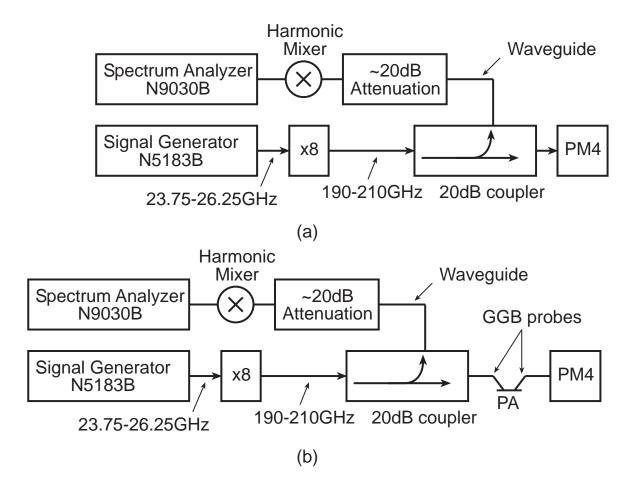

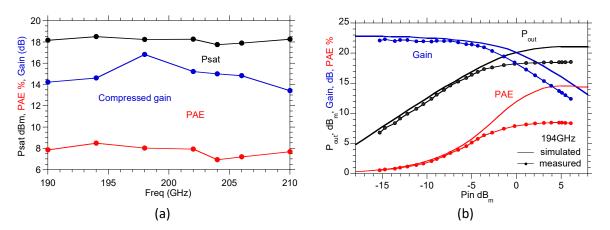

|   |              | 5.3.2 | Measurement Results                                                    |

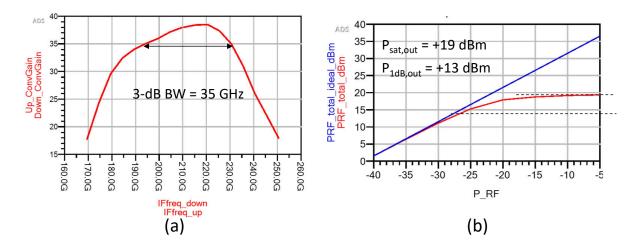

|   |              | 5.3.4 | Transmitter Simulation Results                                         |

|   | 5.4          |       | arison of the State-of-the-Art Amplifiers                              |

|   | 5.5          |       | ging Options for 210GHz Transmitter                                    |

|   | 5.6          | ,     | ransmitter with Quartz Antenna                                         |

|   |              | 5.6.1 | Two Cells Amplifier Design                                             |

|   |              | 5.6.2 | Amplifier Measurement Results                                          |

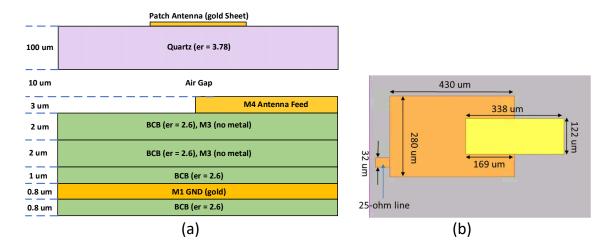

|   |              | 5.6.3 | Quartz Antenna Design                                                  |

|   |              | 5.6.4 | 2x2 Array Design                                                       |

|   |              |       |                                                                        |

| 6 |              |       | IIMO Demonstration and Millimeter-Wave packaging 130                   |

|   | 6.1          |       | uction                                                                 |

|   | 6.2          |       | n Level Requirement: Link Budget                                       |

|   | 6.3          |       | esign Overview                                                         |

|   | 0.4          | 6.3.1 | Challenges in tileable approach                                        |

|   | 6.4          |       | teter-Wave packaging                                                   |

|   | 6.5          |       | o Package Transition                                                   |

|   |              | 6.5.1 | Wirebond                                                               |

|   |              | 6.5.2 | C4 Flip Chip                                                           |

|   |              | 6.5.3 | Copper Pillars                                                         |

|   |              | 6.5.4 | Microstrip to Antenna Coupling                                         |

|    | 6.6   | LTCC    | vs PCB Approaches                                | 140 |

|----|-------|---------|--------------------------------------------------|-----|

|    | 6.7   | Interpo | oser Design                                      | 141 |

|    | 6.8   | Carrie  | r Board Design                                   | 142 |

|    | 6.9   | 135GH   | Iz CMOS Transmitter Tile                         | 142 |

|    |       | 6.9.1   | Copper Pillar Matching                           | 144 |

|    |       | 6.9.2   | Packaging Results for a Single CMOS Chip         | 144 |

|    |       | 6.9.3   | Antenna Design                                   | 146 |

|    |       | 6.9.4   | CMOS to Antenna Transition                       | 148 |

|    |       | 6.9.5   | Single Transmitter Element: Measurement Results  | 148 |

|    | 6.10  | 135GH   | Iz CMOS Receiver Tile                            | 151 |

|    | 6.11  | 135GH   | Iz CMOS transmitter with InP PA Transmitter Tile | 152 |

|    |       | 6.11.1  | Wirebond transition                              | 153 |

|    |       | 6.11.2  | Thermal Consideration                            | 154 |

|    |       | 6.11.3  | InP PA to Antenna and CMOS Transition            | 155 |

| 7  | Con   | clusion | ns and Future Work                               | 158 |

| Bi | bliog | raphy   |                                                  | 160 |

# List of Figures

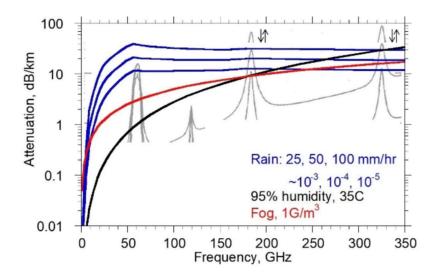

| 1.1        | Atmospheric loss [1]                                                                                                                                                                                                                                                                                | 2        |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

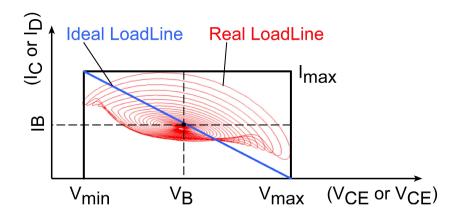

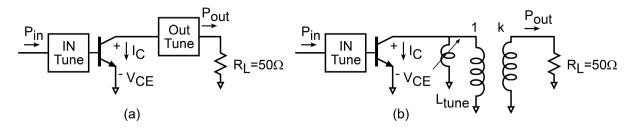

| 2.1<br>2.2 | Ideal and Real Loadline for class A operation plotted on the SOA (a) Transistor with output and input tuning. (b) Transistor with output                                                                                                                                                            | 9        |

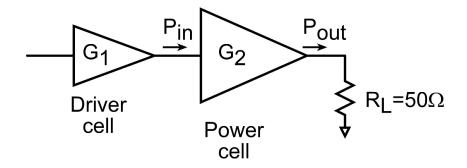

| 2.3        | tuning using an inductor and transformer                                                                                                                                                                                                                                                            | 10<br>13 |

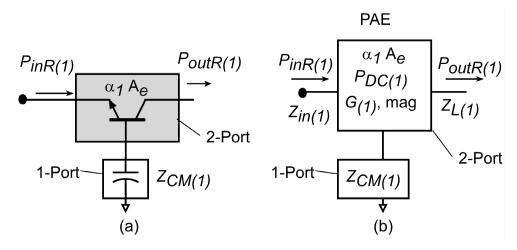

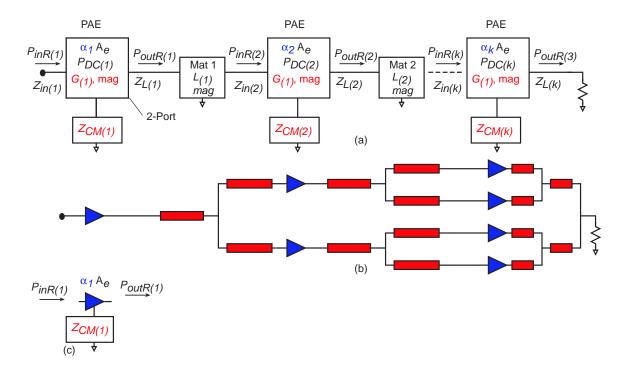

| 3.1        | Unit Cell: a) Showing the circuit details. b) Omitting the circuit details using network theory                                                                                                                                                                                                     | 21       |

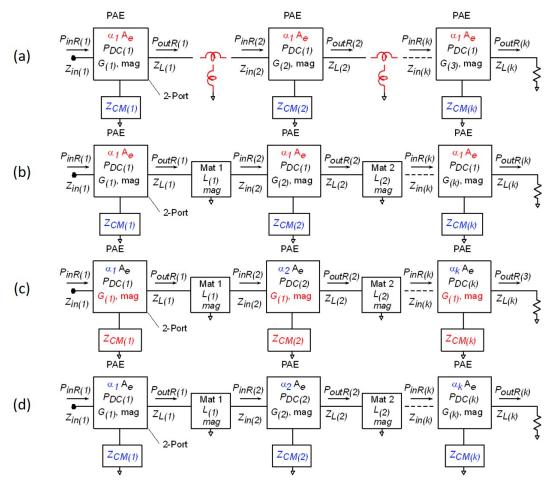

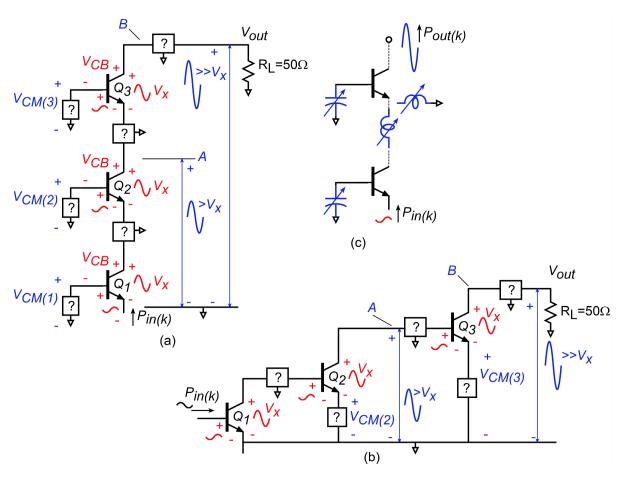

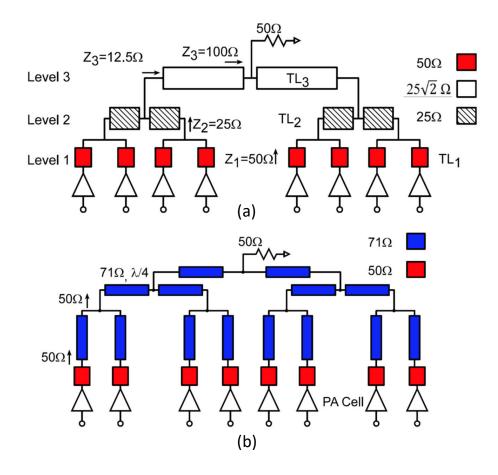

| 3.2        | Amplifier's degrees of freedom: a) Conventional stacked amplifiers with single element matching. b) Stacked power amplifiers with full impedance matching. c) Amplifier design with area progression technique under constant normalized base impedance. d) Amplifier design with area progression. | 22       |

| 3.3        | sion and impedance scaling techniques                                                                                                                                                                                                                                                               | 22       |

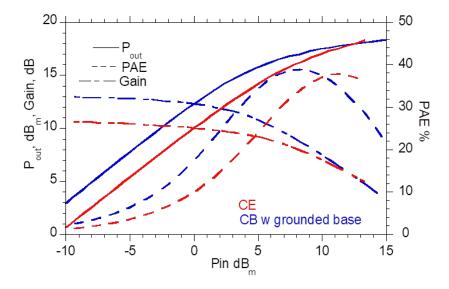

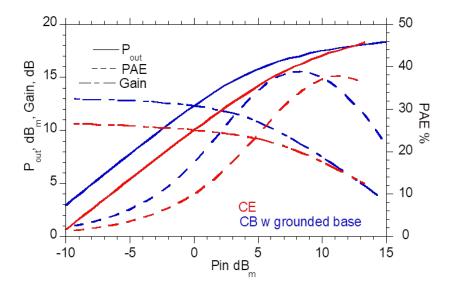

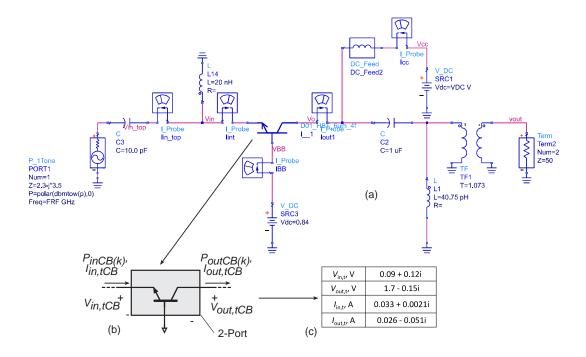

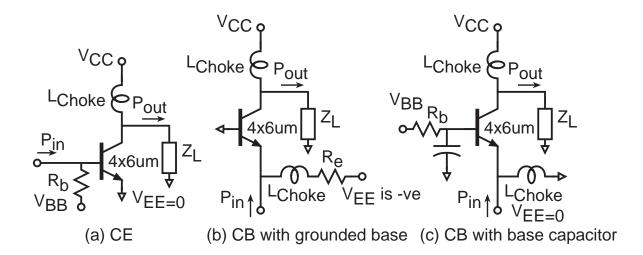

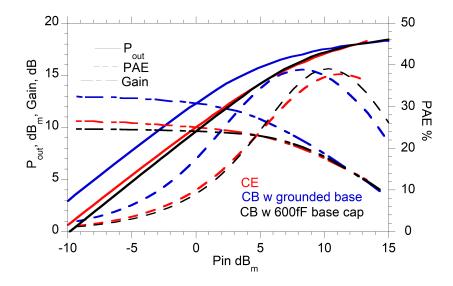

| ა.ა        | power) for CE and grounded CB at 140GHz in 250nm InP HBT technology.                                                                                                                                                                                                                                | 27       |

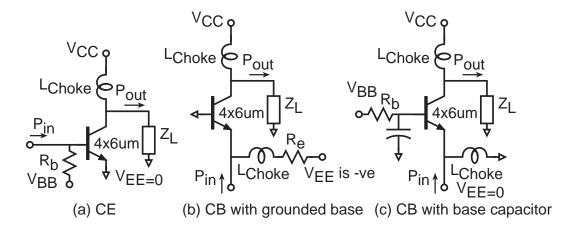

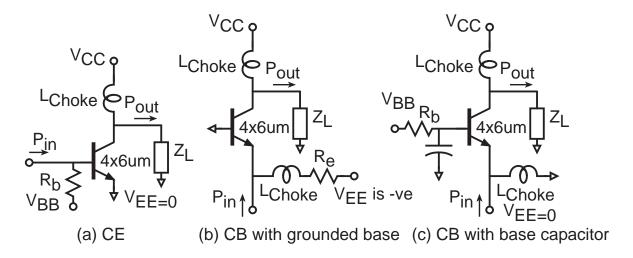

| 3.4        | Schematic diagram of: (a) CE (b) CB with grounded base. (c) CB with                                                                                                                                                                                                                                 |          |

|            | 600fF base capacitor.                                                                                                                                                                                                                                                                               | 28       |

| 3.5        | Conceptual drawing for three stacked with full impedance tuning PA; a) CB and b) CE topologies. c) Conventional stack representation for CB                                                                                                                                                         |          |

|            | stack with limited tuning elements                                                                                                                                                                                                                                                                  | 30       |

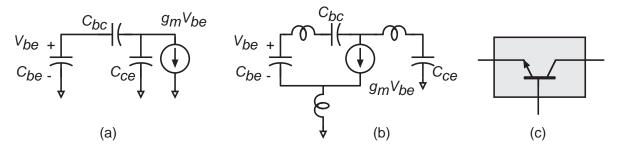

| 3.6        | Equivalent transistor model in different representations a) Using simplified                                                                                                                                                                                                                        |          |

|            | model. b) Including more parasitics. c) Using 2-port network                                                                                                                                                                                                                                        | 34       |

| 3.7        | Large signal characteristic (output power, gain, and PAE versus input                                                                                                                                                                                                                               | 25       |

| 3.8        | power) for CE and grounded CB at 140GHz in 250nm InP HBT technology. Schematic diagram of: (a) CE (b) CB with grounded base; (c) CB with                                                                                                                                                            | 35       |

| 0.0        | 600fF base capacitor                                                                                                                                                                                                                                                                                | 36       |

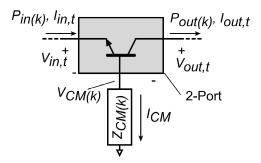

| 3.9        | Generic CB stack cell showing the complex input, output powers, voltage                                                                                                                                                                                                                             |          |

|            | and current distribution                                                                                                                                                                                                                                                                            | 37       |

| 3.10       | Generic CB stack cell showing the complex input, output powers, voltage                                                                                                                                                                                                                             | 0.0      |

|            | and current distribution                                                                                                                                                                                                                                                                            | 38       |

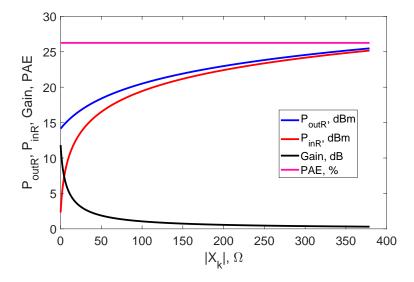

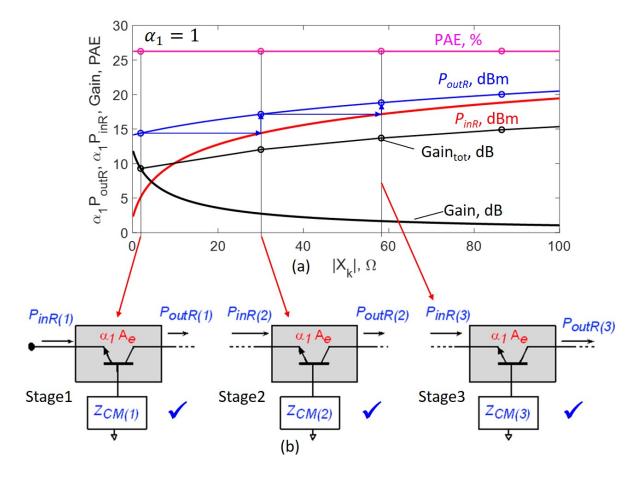

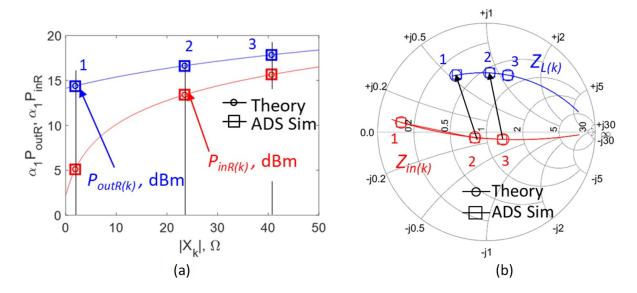

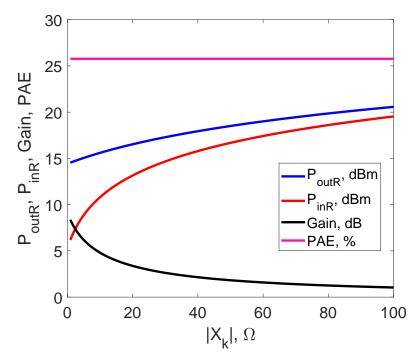

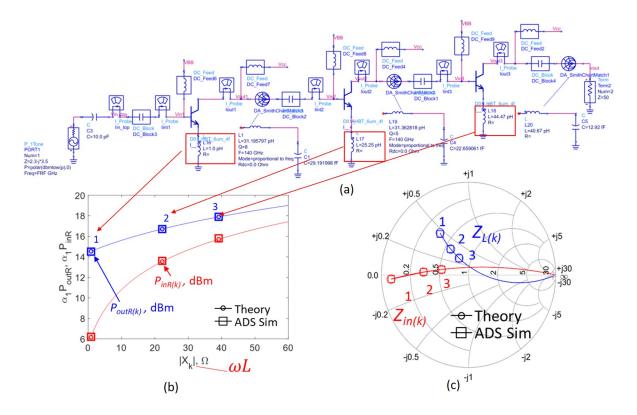

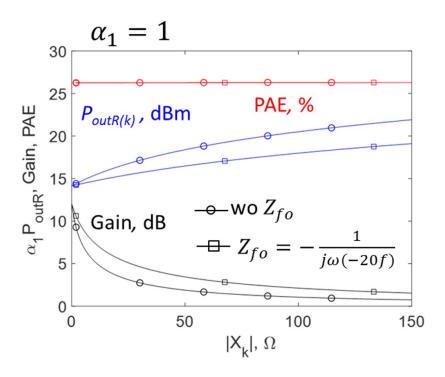

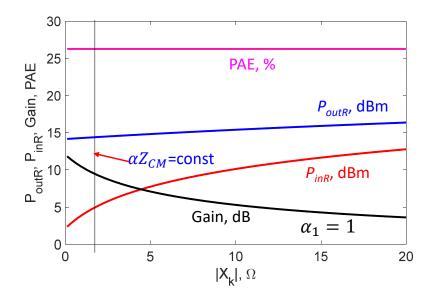

| 3.11         | Real output power, input power, PAE, and Gain, versus the base reactance.               | 40         |

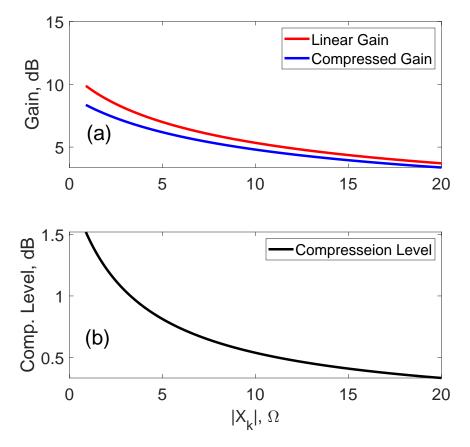

|--------------|-----------------------------------------------------------------------------------------|------------|

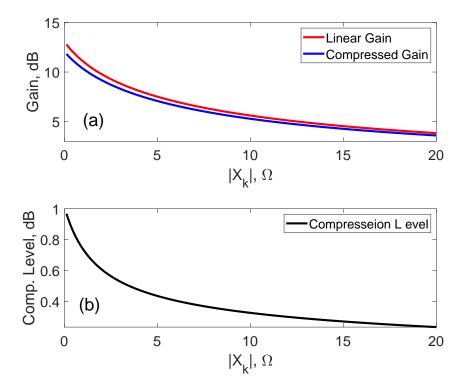

| 3.12         | a) Compressed Gain, Linear Gain versus the base reactance b) Compres-                   |            |

|              | sion level versus the base reactance                                                    | 41         |

| 3.13         | a) Real output power, input power, PAE, gain, and total gain versus the                 |            |

|              | base reactance showing the optimum stack stage location using lossless                  |            |

|              | matching network b) Block diagram for the amplifier                                     | 42         |

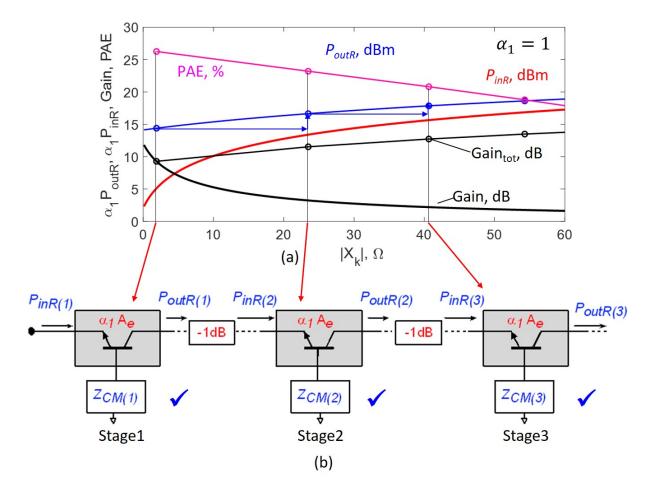

| 3.14         | a) Real output power, input power, ideal PAE, PAE including loss , gain,                |            |

|              | and total gain versus the base reactance showing the optimum stack stage                |            |

|              | location using lossy matching network (1dB per each interstage matching).               |            |

|              | b) Block diagram for the amplifier                                                      | 44         |

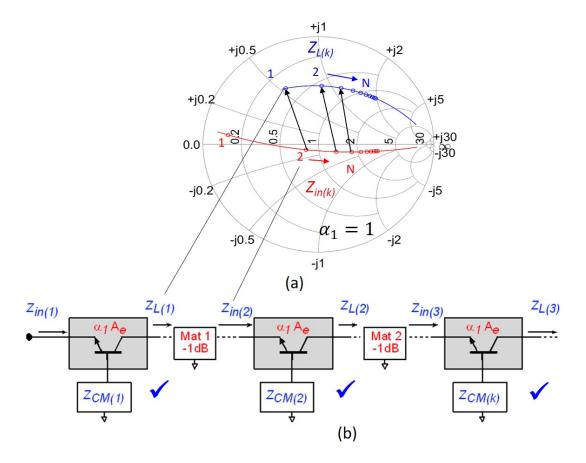

| 3.15         | a) Required load impedance and actual input impedance contours versus                   |            |

|              | the stack index. The black arrows show the required interstage impedance                |            |

|              | transformation in lossy network (1dB per each interstage matching) b)                   |            |

|              | Block diagram for the amplifier                                                         | 45         |

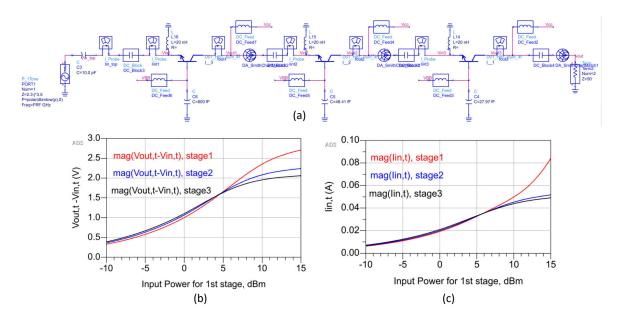

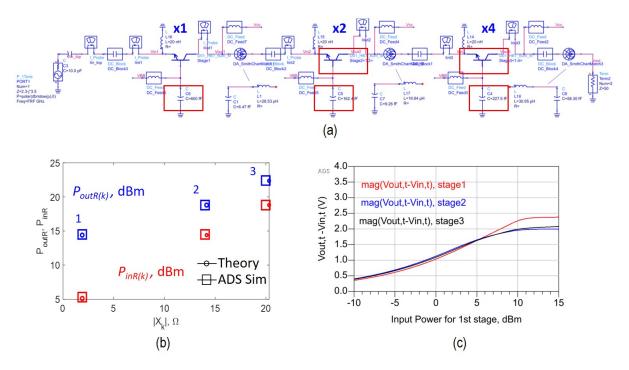

| 3.16         | CB example: a) schematic diagram of three CB stacked amplifier. b)                      |            |

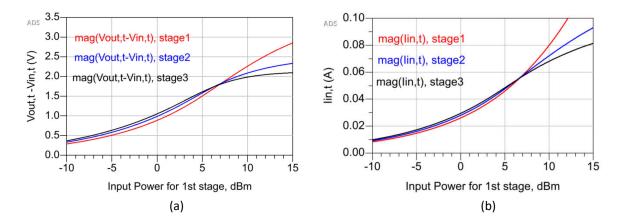

|              | Magnitudes of the internal voltages $(V_{out,t} - V_{in,t})$ versus the input power     |            |

|              | for the first stage c) Magnitudes of the internal currents $(I_{int})$ versus the       |            |

| 0 4 <b>-</b> | input power for the first stage                                                         | 46         |

| 3.17         | CB example: a) Simulated and theoretical stages power are in perfect                    |            |

|              | agreement. b) Simulated and theoretical stages impedances are in perfect                | 4 -        |

| 0.10         | agreement                                                                               | 47         |

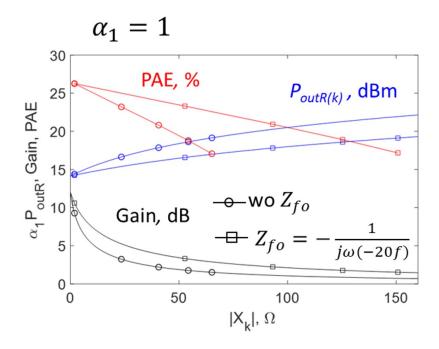

| 3.18         | 0,                                                                                      | 48         |

| 3.19         | Real output power, input power, PAE, and Gain versus the emitter reactance for CE stack | <b>F</b> 0 |

| 3.20         |                                                                                         | 50         |

| 3.20         | sion level versus the emitter reactance                                                 | 51         |

| 3.21         |                                                                                         | 91         |

| 9.21         | Simulated and theoretical stages power showing the location of the proper               |            |

|              | emitter reactance. c) Simulated and theoretical stages impedances high-                 |            |

|              | lighted at the location of the proper emitter reactance value                           | 52         |

| 3.22         | CE example: a) Magnitudes of the internal voltages $(V_{out,t} - V_{in,t})$ versus      | 02         |

| J            | the input power for the first stage b) Magnitudes of the internal currents              |            |

|              | $(I_{int})$ versus the input power for the first stage                                  | 53         |

| 3.23         | General form of neutralization.                                                         | 54         |

|              | Pout, gain, PAE with 20fF $C_{CB}$ neutralization for lossless matching                 | 55         |

|              | $P_{outR}$ , gain, PAE with 20fF $C_{CB}$ neutralization for lossy matching             | 56         |

|              | Amplifier design using area progression technique: a) Block diagram. b)                 |            |

|              | Visual representation. c) unit cell                                                     | 58         |

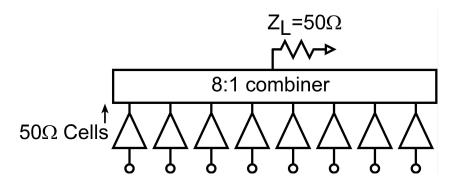

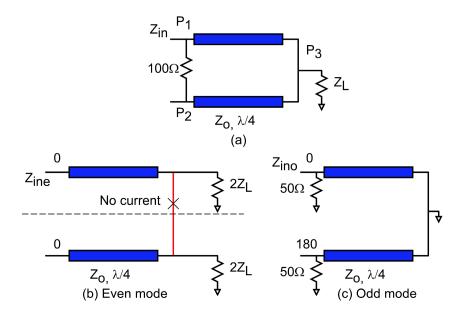

| 3.27         | Block diagram of eight-50 $\Omega$ cells                                                | 61         |

| 3.28         | Quarter wave transformation                                                             | 61         |

| 3.29         | (a) 2:1 Wilkinson combiner. (b) Even mode analysis. (b) Odd mode analysis.              | 62         |

| 3.30 | a) Proposed 8:1 transmission-line combiner for $50\Omega$ load. b) An 8:1 Wilkin-  |          |    |

|------|------------------------------------------------------------------------------------|----------|----|

|      | son combiner (with bridging resistors omitted)                                     | 63       |    |

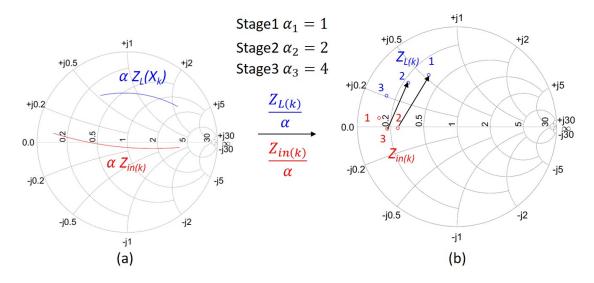

| 3.31 | Stack design contours at constant normalized base impedance                        | 66       |    |

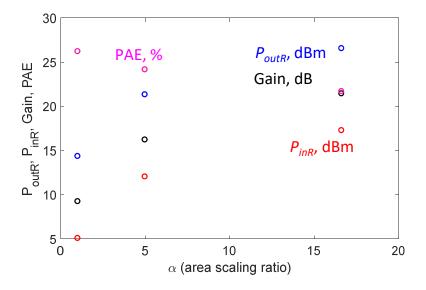

| 3.32 | a) Output power, input power, gain, and PAE versus the areas scaling               |          |    |

|      | factor. b) Amplifier block diagram                                                 | 67       |    |

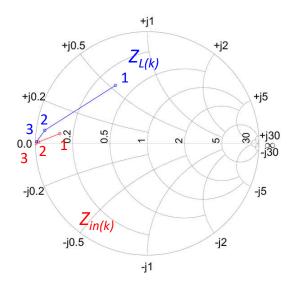

| 3.33 | $Z_L$ and $Z_{in}$ as a function of the stage index. It shows the required inter-  |          |    |

|      | stage impedance transformation contours                                            | 68       |    |

| 3.34 | $P_{outR}$ , gain, PAE versus the area progression factor including splitter loss. | 69       |    |

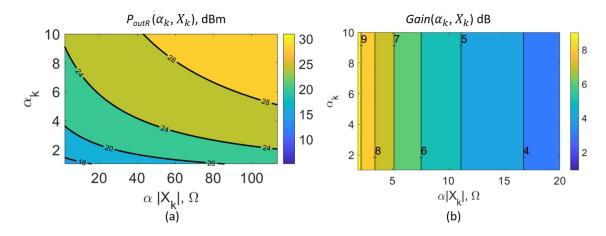

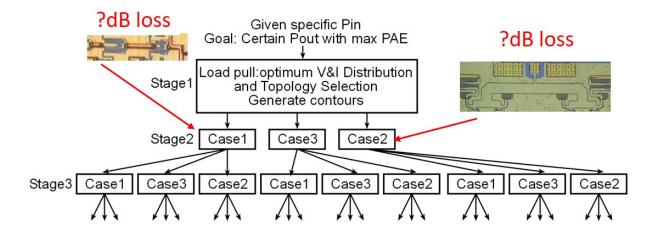

| 3.35 | a) Contour plots for the output power function of the normalized base              |          |    |

|      | impedance and area progression factor. b) Contour plots for the gain               |          |    |

|      | function of the normalized base impedance and area progression factor              | 71       |    |

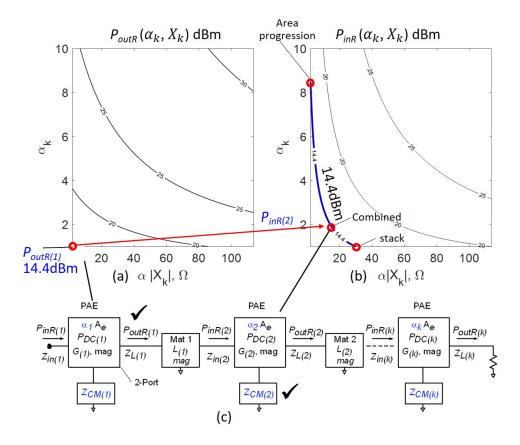

| 3.36 | a) Output power contours showing the power of the first stage's power.             |          |    |

|      | b) Contour for the input power highlighting the design contour for the             |          |    |

|      | second stage. c) General amplifier form considering impedance and area             |          |    |

|      | progression techniques                                                             | 72       |    |

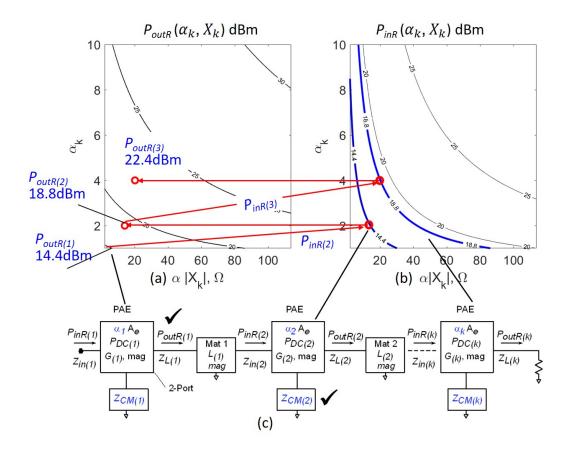

| 3.37 | , 1 1                                                                              |          |    |

|      | the input power highlighting the design contours. c) Block diagram for             |          |    |

|      | amplifier designed with area and stacking techniques                               | 73       |    |

| 3.38 | a) Impedance chart showing the load and input impedance versus the                 |          |    |

|      | normalized base impedance. b) Impedance values for the amplifier after             |          |    |

|      | applying the proper scaling factor                                                 | 74       |    |

| 3.39 |                                                                                    |          |    |

|      | diagram. b) Simulated and theoretical stages power showing the loca-               |          |    |

|      | tion of the proper base reactance. c) Simulated and theoretical stages             |          |    |

| 0.40 | impedances highlighted at the location of the proper base reactance value.         | 75<br>75 |    |

| 3.40 | Amplifier design guideline                                                         | 75       |    |

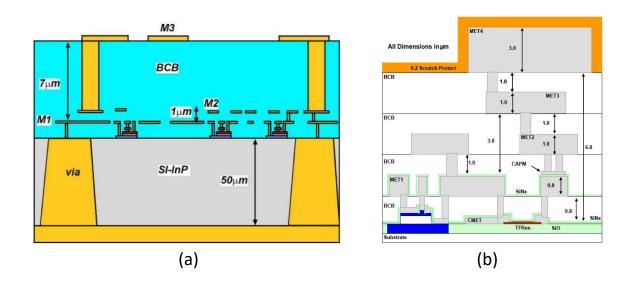

| 4.1  | Schematic cross section of a) 130nm InP HBT. b) 250nm InP HBT technologie          | s[2].    | 79 |

| 4.2  | Schematic diagram of: (a) CE. (b) CB with grounded base. (c) CB with               | L J      |    |

|      | 600fF base capacitor                                                               | 80       |    |

| 4.3  | $P_{out}$ , gain, and PAE for CE, grounded CB, and CB with base capacitor          | 81       |    |

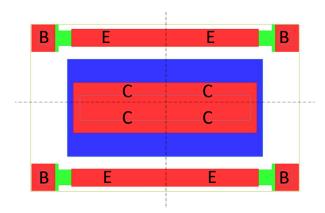

| 4.4  | Transistor footprint for compact 4 fingers connected together. Each is             |          |    |

|      | $6\mu$ m emitter length. Total emitter periphery is $24\mu$ m                      | 82       |    |

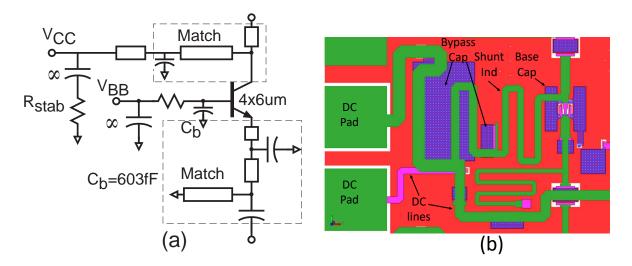

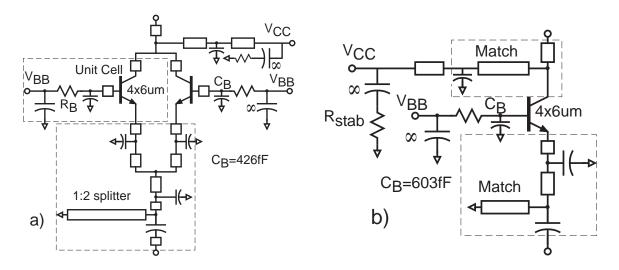

| 4.5  | (a) Schematic diagram of two combined power amplifier cells driven by a            |          |    |

|      | single driver cell. (b) Corresponding layout                                       | 83       |    |

| 4.6  | Schematic diagram of: (a) Driver stage with input/output matching cir-             |          |    |

|      | cuits. (b) Driver layout                                                           | 84       |    |

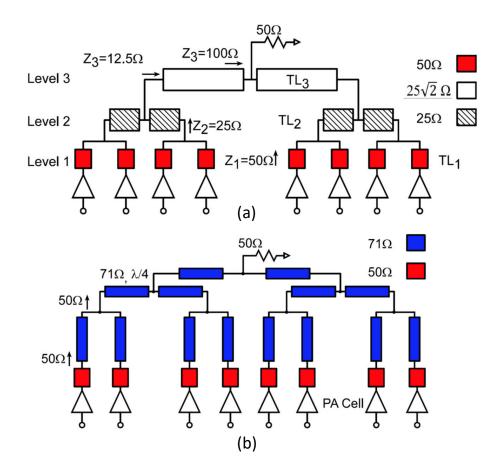

| 4.7  | Schematic diagram (a) 4:1 low loss transmission line combiner for $50\Omega$       |          |    |

|      | load. (b) 4:1 Wilkinson power combiner (with bridging resistors omitted)           |          |    |

|      | for $50\Omega$ load                                                                | 85       |    |

| 4.8  | (a) Chip micrograph of the power amplifiers. The area is 1.08mm 0.63mm             |          |    |

|      | including the pads. (b) Amplifier block diagram.                                   | 86       |    |

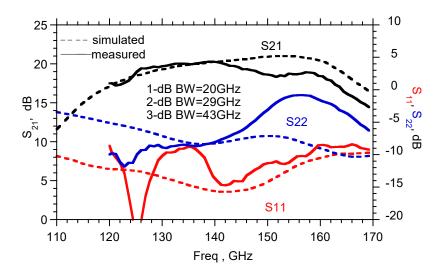

| 4.9  | Measured (solid) and simulated (dashed) S-parameters                                                                                               | 8' |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

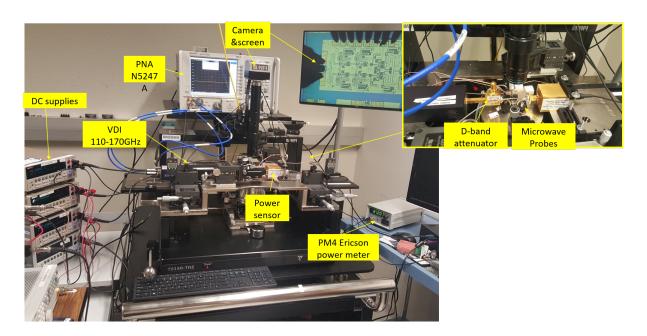

| 4.10 | Power measurement setup                                                                                                                            | 88 |

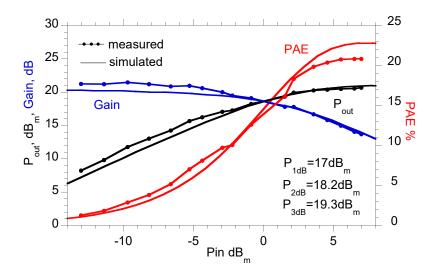

| 4.11 | Measured and simulated output power, PAE, and gain versus the input                                                                                |    |

|      | power at 140GHz                                                                                                                                    | 89 |

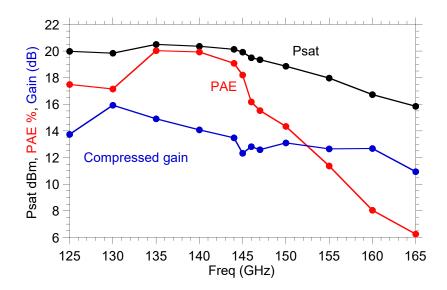

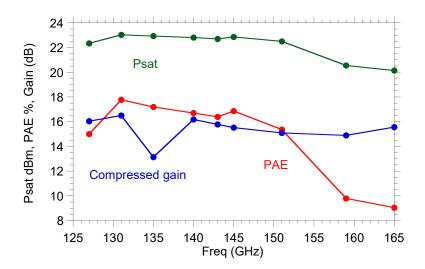

| 4.12 | Measured saturated output power, PAE and the compressed gain versus                                                                                |    |

|      | frequency                                                                                                                                          | 90 |

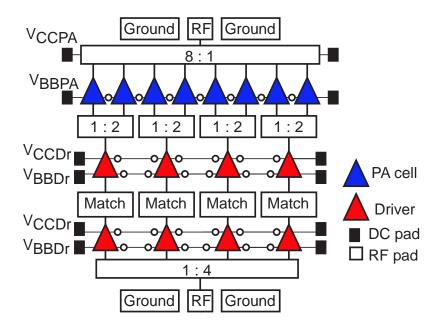

| 4.13 | Amplifier block diagram                                                                                                                            | 92 |

| 4.14 | Schematic diagram of: a) Two combined power amplifier cells. The pair of power cells are driven by a single driver cell. b) Driver cell with input |    |

|      | and output matching networks                                                                                                                       | 9; |

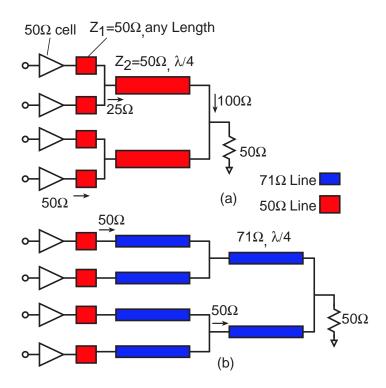

| 4.15 | a) Proposed 8:1 transmission-line combiner for $50\Omega$ load. b) an 8:1 Wilkin-                                                                  |    |

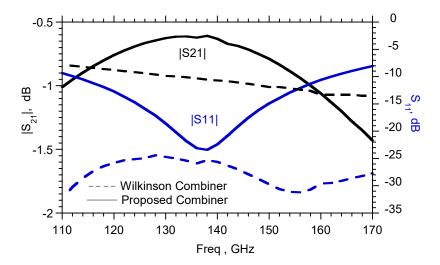

|      | son combiner (with bridging resistors omitted)                                                                                                     | 9  |

| 4.16 | Simulations comparing the insertion losses and input reflection coefficients                                                                       |    |

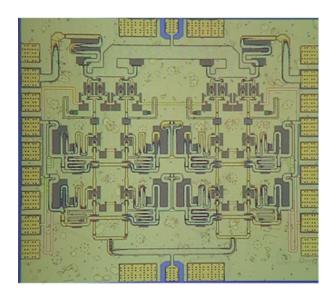

|      | of the two designs.                                                                                                                                | 9. |

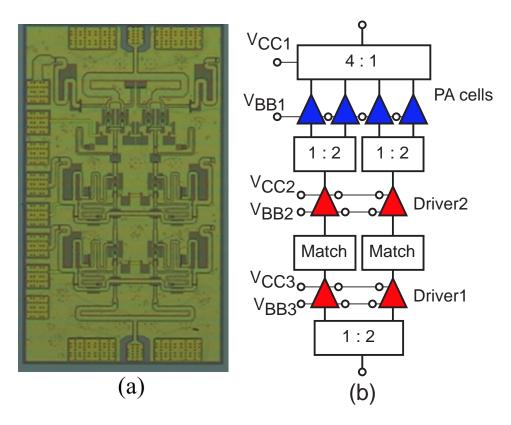

|      | Chip micrograph of the PA (1.23mm 1.09mm) including the pads                                                                                       | 90 |

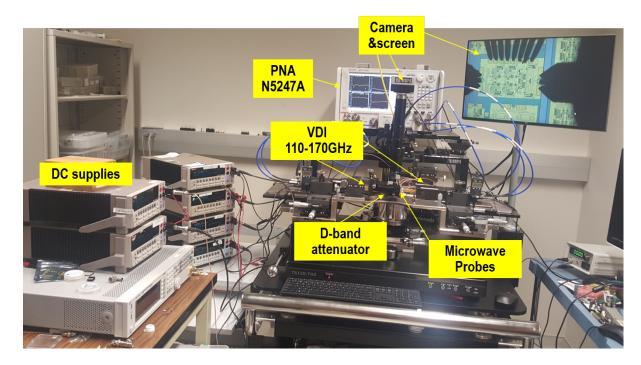

|      | S-parameters measurements setup                                                                                                                    | 9  |

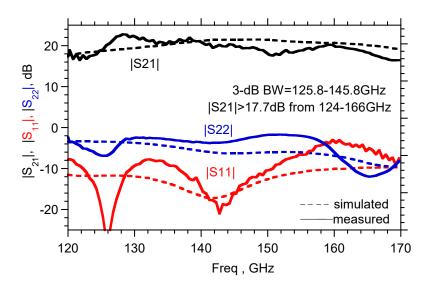

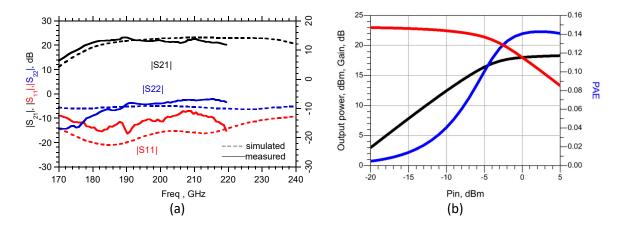

|      | Measured (solid) and simulated (dashed) S-parameters                                                                                               | 9  |

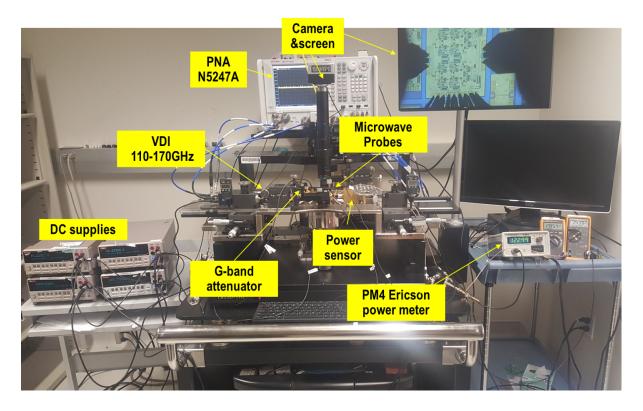

|      | Power measurement setup                                                                                                                            | 9  |

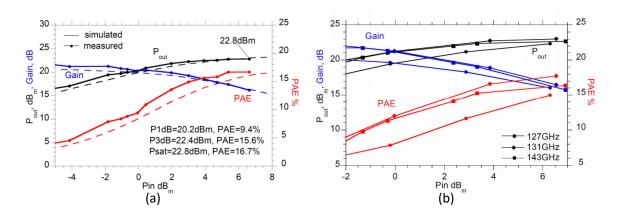

| 4.21 | a) Measured and simulated output power, PAE, and gain versus the input                                                                             |    |

|      | power at 140GHz. b) Measured $P_{out}$ , PAE, and gain versus the input                                                                            |    |

|      | power at 127, 131, and 143GHz                                                                                                                      | 10 |

| 4.22 | Measured saturated output power, PAE and the compressed gain versus                                                                                |    |

|      | frequency                                                                                                                                          | 10 |

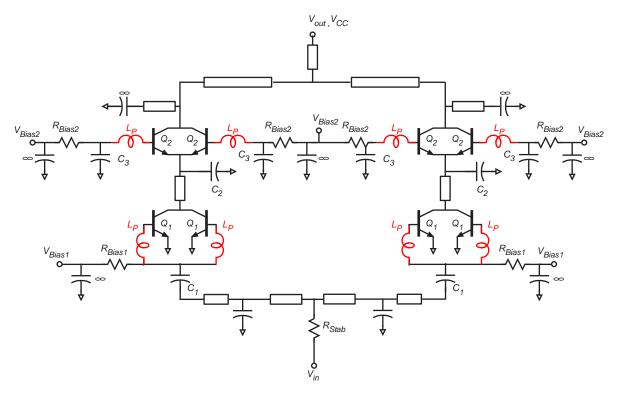

| 4.23 | Simplified schematic diagrams of a 204GHz, 3:1 series-connected stack                                                                              |    |

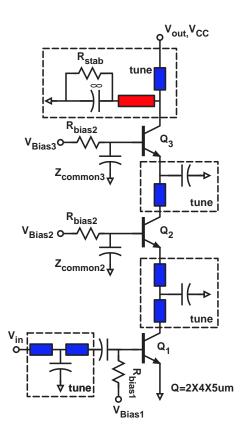

|      | with gain-matching on $Q_1$ and power-matching on $Q_2$ and $Q_3$                                                                                  | 10 |

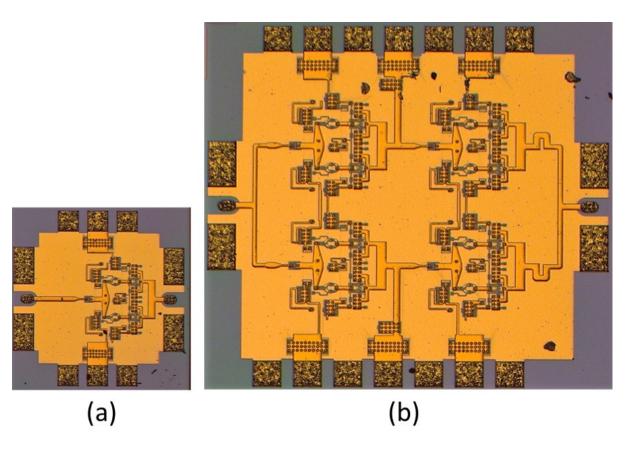

| 4.24 | (a) Die photo of design 1, and (b) Design 2, with 2:1 transmission-line                                                                            |    |

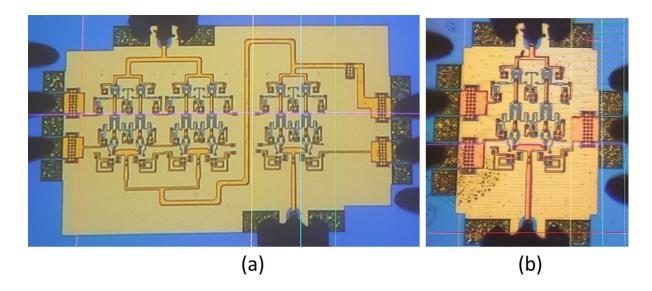

|      | combining. The die areas are 0.63 mm $\times$ 0.54 mm, and 0.7 mm $\times$ 1.3 mm                                                                  |    |

|      | respectively.                                                                                                                                      | 10 |

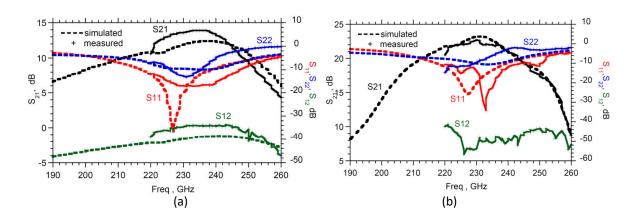

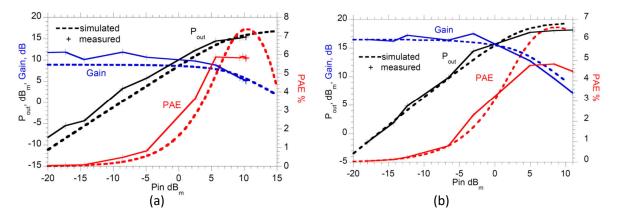

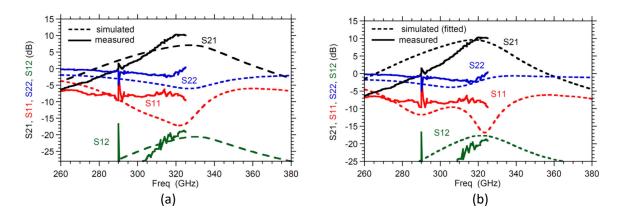

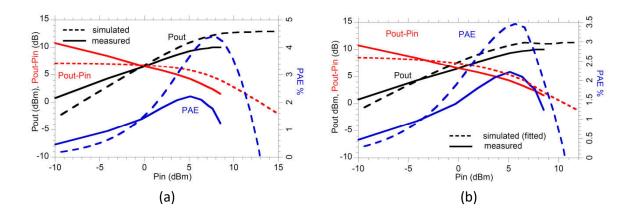

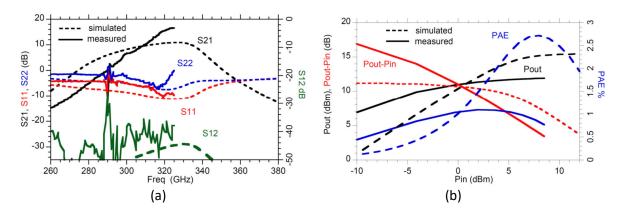

|      | Measured and simulated S-parameters of a) Design 1 a) Design 2                                                                                     | 10 |

| 4.26 | a) Measured and simulated output power, PAE, and gain for Design 1. b)                                                                             |    |

|      | Measured and simulated output power, PAE, and gain for Design 2                                                                                    | 10 |

| 4.27 | PA unit cell (two stacked HBTs with matching circuits). $Q_1$ and $Q_2$ are                                                                        |    |

|      | two finger transistors each $5\mu m$ emitter length. The inductors (red) are                                                                       |    |

|      | added to represent the base inductance model and are not real inductors.                                                                           | 10 |

| 4.28 | PA unit cell (Chip micrograph of the power amplifiers: a) Design #1                                                                                |    |

|      | (dimensions = 600 $\mu$ m 585 $\mu$ m). b) Design #2 (dimensions = 0.98 mm 1                                                                       |    |

|      | mm)                                                                                                                                                | 10 |

| 4.29 | PA unit cell (a) Simulated and measured s-parameters of the unit-cell                                                                              |    |

|      | design. b) Comparison of measured and resimulated s-parameters of the                                                                              |    |

|      | unit-cell design assuming an additional 3.5 pH base feed inductance per                                                                            |    |

|      | two-finger each 5 $\mu$ m emitter length HBT                                                                                                       | 10 |

| 4.30       | a) Simulated and measured power transfer characteristics at 325GHz of the unit-cell design. b) Comparison of measured and resimulated power transfer characteristics at 325GHz of the unit-cell design assuming an additional 3.5 pH base feed inductance per two-finger each 5 $\mu$ m emitter |                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

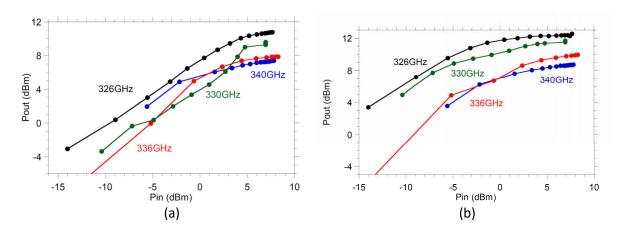

| 4.31       | length HBT                                                                                                                                                                                                                                                                                      | <ul><li>110</li><li>111</li></ul> |

| 4.32       | a) Measured output power at different frequencies versus the input power for design#1. b) Measured output power at different frequencies versus the input power for design#2.                                                                                                                   | 112                               |

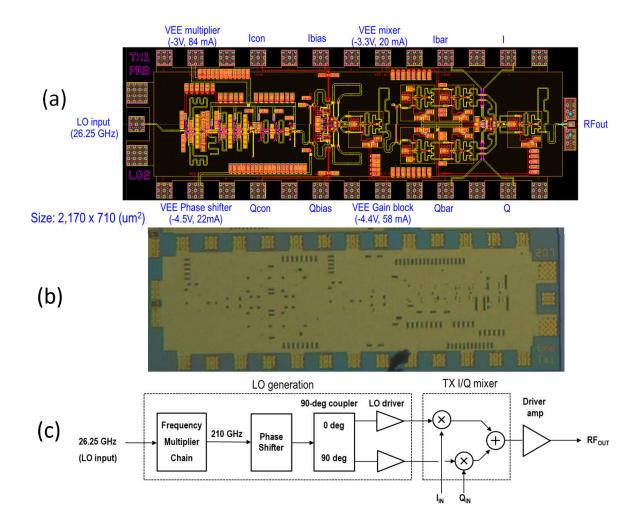

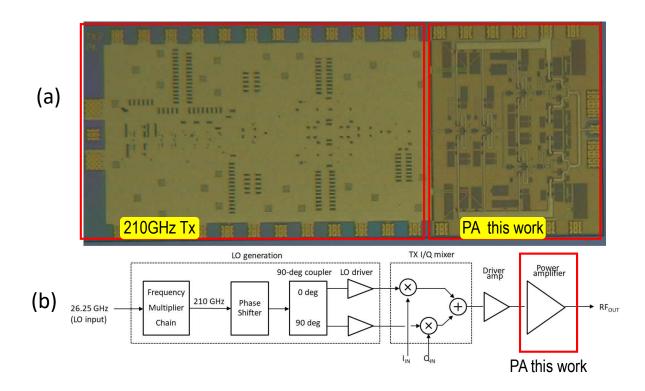

| 5.1        | 210GHz transmitter with a $\sim$ 2dBm output power (Courtesy of Munkyo Seo)                                                                                                                                                                                                                     | 115                               |

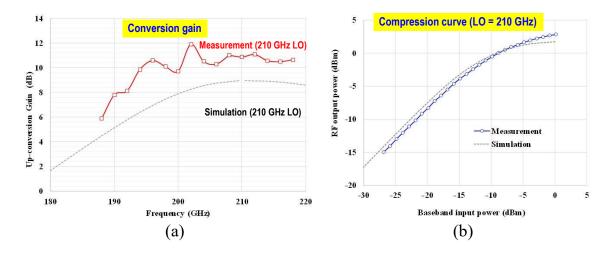

| 5.2        | Measured and simulated results for the 210GHz transmitter with 2dBm output power. a) Conversion gain. b) Output power versus the baseband input power (Courtesy of Munkyo Seo)                                                                                                                  | 116                               |

| 5.3        | 210GHz transmitter with simulated ~18dBm output power                                                                                                                                                                                                                                           | 110 $117$                         |

| 5.4        | a) Die photo, area is 1.2mmx0.95mm. b) Amplifier block diagram                                                                                                                                                                                                                                  | 118                               |

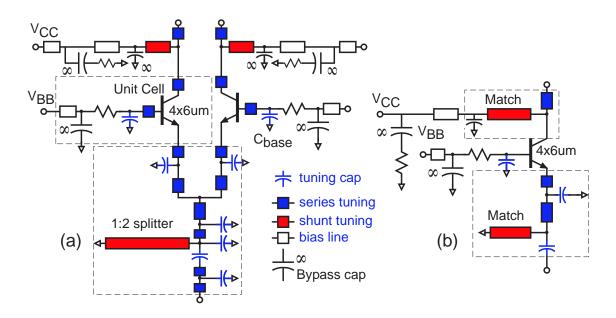

| 5.5        | Schematic diagram of: a) Two combined power amplifier cells. b) Driver                                                                                                                                                                                                                          |                                   |

| 5.6        | cell                                                                                                                                                                                                                                                                                            | 119                               |

|            | conditions a) DC power (445mW). b) DC power (858mW)                                                                                                                                                                                                                                             | 120                               |

| 5.7<br>5.8 | Power measurement setup: a) calibration mode. b) measuring the PA Power measurement setup: a) Measured output power with associated PAE and compressed gain versus the frequency reported at saturated output power. b) Measured and output power, PAE, and gain versus the                     | 122                               |

|            | input power at 194GHz                                                                                                                                                                                                                                                                           | 123                               |

| 5.9        | Simulation results for 210GHz transmitter with $\sim$ 19dBm. a) Up conversion gain. b) Large signal characteristic                                                                                                                                                                              | 124                               |

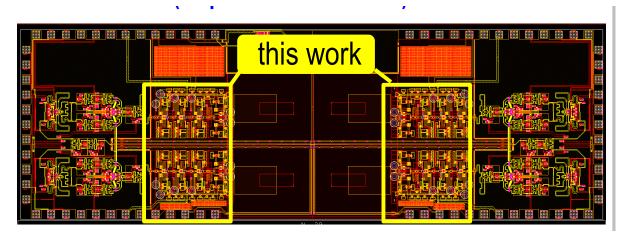

| 5.10       | a) Die photo, area is 0.58mmx1.1mm. b) Amplifier block diagram                                                                                                                                                                                                                                  | 126                               |

| 5.11       | a) Measured (solid) and simulated (dashed) S-parameters at different bias conditions. b) Simulated large-signal characteristics at 210GHz                                                                                                                                                       | 127                               |

| 5.12       | Quartz Design: a) EM simulation stack, b) Patch and coupler dimensions                                                                                                                                                                                                                          |                                   |

|            | (Courtesy of Zhe).                                                                                                                                                                                                                                                                              | 128                               |

| 5.13       | 2x2 Transmitter array with Quartz antenna. The thesis work is highlighted by yellow boxes. Other blocks are designed by Munkyo and antenna is                                                                                                                                                   |                                   |

|            | designed by Zhe                                                                                                                                                                                                                                                                                 | 129                               |

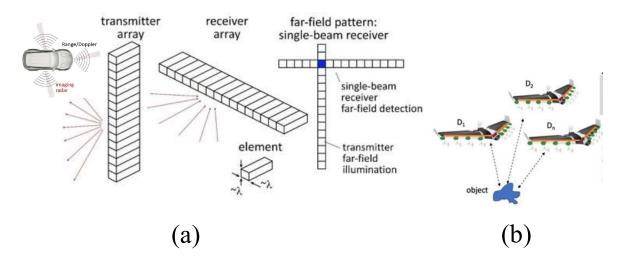

| 6.1        | a) Hardware-efficient imaging. b) Cooperative/sparse imaging (Courtesy of Mark Rodwell)                                                                                                                                                                                                         | 131                               |

| 6.2        | a) Point to point MIMO array. b) Cartoon drawing for single tile (Courtesy                                                                                                                                                                                                                      | 101                               |

| J - =      | of Mark Rodwell)                                                                                                                                                                                                                                                                                | 132                               |

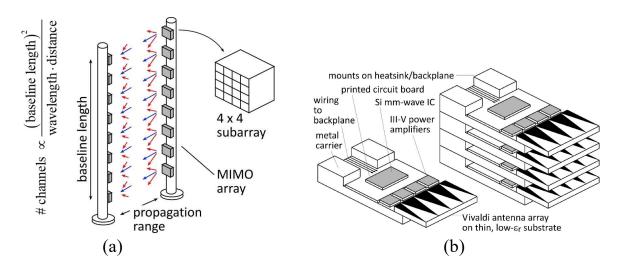

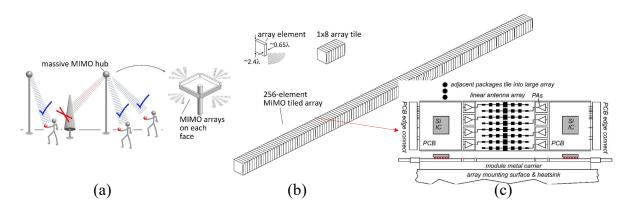

| 6.3  | a) Massive MIMO hub. b) Cartoon drawing for MIMO array. c) Single tile (Courtesy of Mark Rodwell)                                                                                                            | 132          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

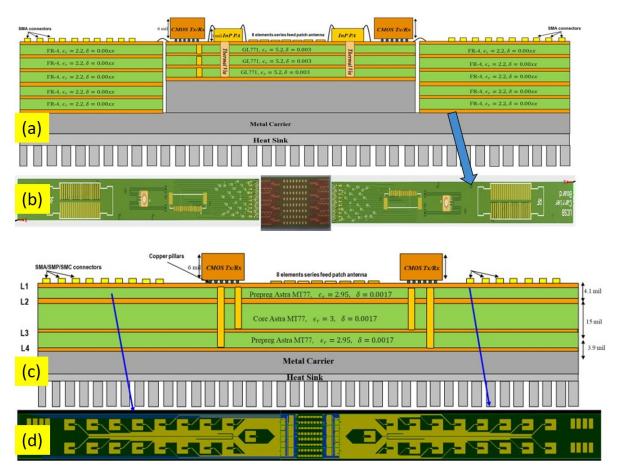

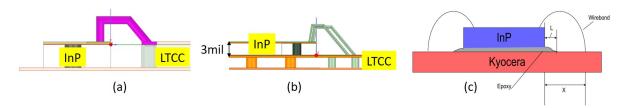

| 6.4  | a) Cross section of the LTCC approach (this work) showing the interposer, chips, PCB carrier board with the DC and RF connectors. b) Top view of the LTCC approach. c) Cross section of the low-cost PCB ap- |              |

|      | proach (Courtesy of Ali Farid). d) Top view of the low-cost PCB approach.                                                                                                                                    | 134          |

| 6.5  | a) Cavity approach to reduce the wirebond length. b) Chip mounted on                                                                                                                                         |              |

|      | the surface of the LTCC. c) Epoxy leaking problem                                                                                                                                                            | 138          |

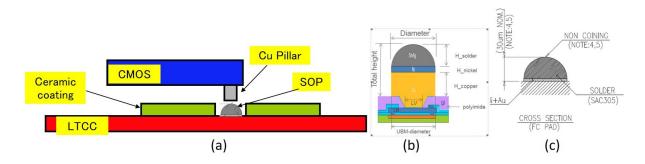

| 6.6  | a) Sketch for the CMOS chip filpped on the interposer. b) Drawing for                                                                                                                                        |              |

|      | the copper pillar. c) Drawing for the SOP                                                                                                                                                                    | 139          |

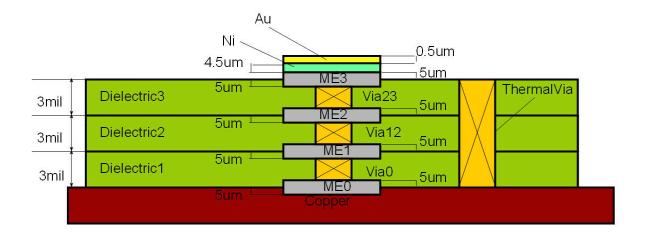

| 6.7  | Wiring stack for the ceramic interposer                                                                                                                                                                      | 142          |

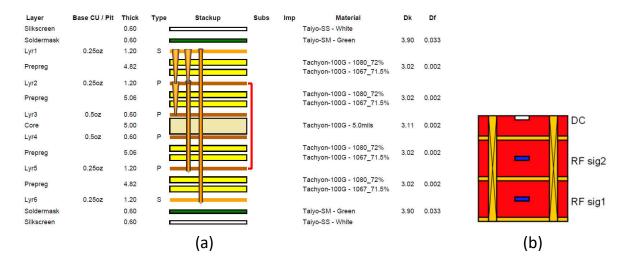

| 6.8  | a) Wiring stack of the PCB. b) Cross section in the wiring stack showing                                                                                                                                     |              |

|      | the RF and DC routing techniques                                                                                                                                                                             | 143          |

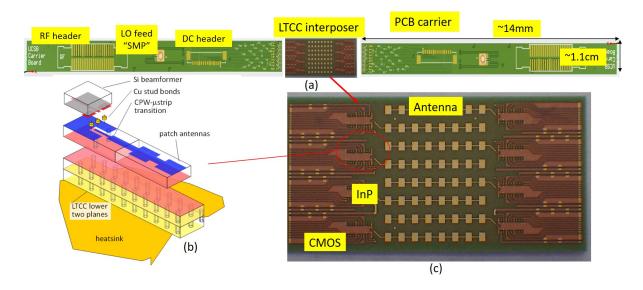

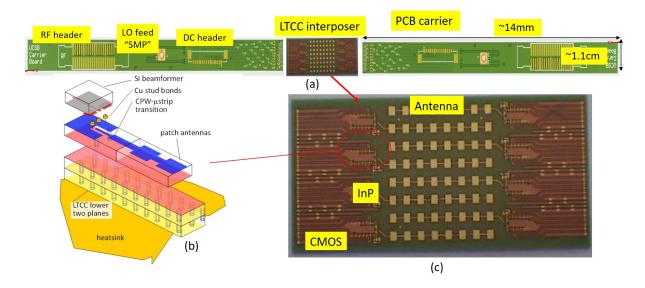

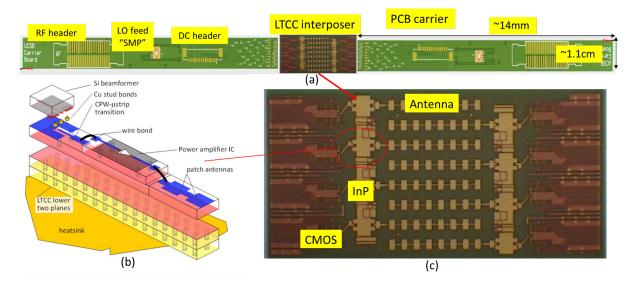

| 6.9  | a) Photos for the transmitter module showing the LTCC ceramic inter-                                                                                                                                         |              |

|      | poser and PCB carrier board. b) Cartoon drawing for the CMOS trans-                                                                                                                                          |              |

|      | mitter chip to the interposer showing the different type of transitions. c)                                                                                                                                  |              |

|      | Close look on the LTCC ceramic interposer showing the antenna arrays                                                                                                                                         |              |

|      | and chip footprints                                                                                                                                                                                          | 144          |

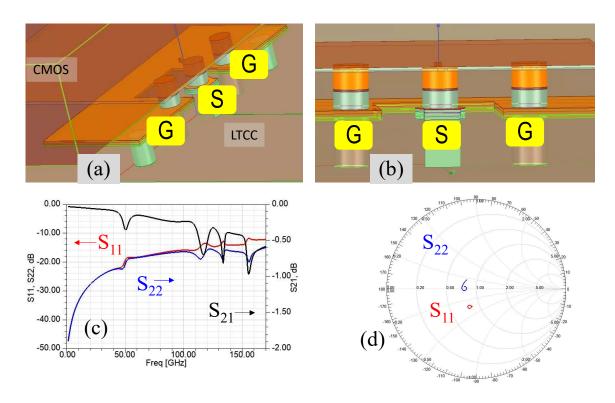

| 6.10 | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                      | 1 12         |

| C 11 | S-parameters simulations. d) S-parameters simulations on smith chart.                                                                                                                                        | 145          |

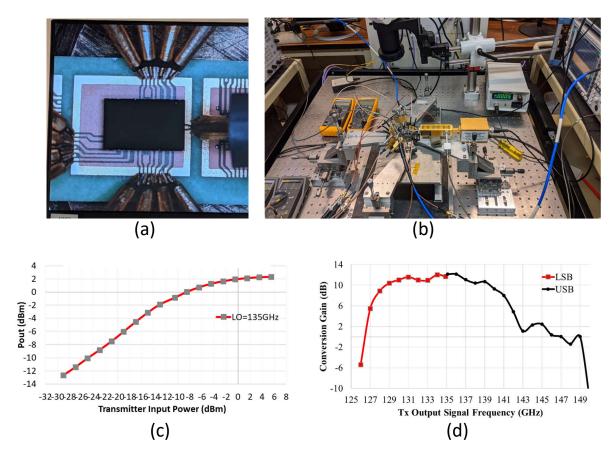

| 6.11 |                                                                                                                                                                                                              |              |

|      | CMOS transmitter chip mounted on LTCC interposer. b) Measurement                                                                                                                                             |              |

|      | setup. c) Measured transmitter's output power versus the input power including the copper pillar transition loss d) Transmitter conversion gain                                                              |              |

|      | versus the output frequency                                                                                                                                                                                  | 146          |

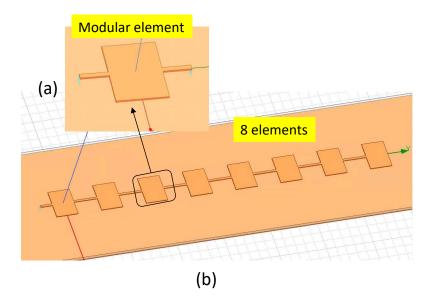

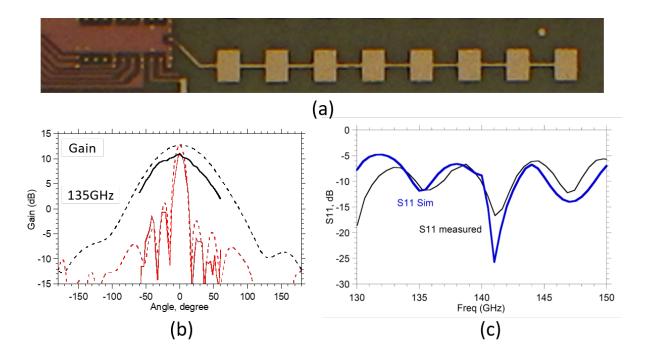

| 6 19 | Antenna Design: a) Modular element. b) Eight series fed patch antenna.                                                                                                                                       | $140 \\ 147$ |

|      | a) Photo for the eight-element series fed patch antenna and the chip foot-                                                                                                                                   | 141          |

| 0.10 | print. b) Measured and simulated radiation patterns at the azimuth and                                                                                                                                       |              |

|      | elevation. at 135GHz. c) Measured and simulated input reflection coeffi-                                                                                                                                     |              |

|      | cient and gain                                                                                                                                                                                               | 149          |

| 6 14 | Antenna radiation pattern Setup from different angles (Courtesy of Ali                                                                                                                                       | 110          |

| 0.11 | Farid)                                                                                                                                                                                                       | 150          |

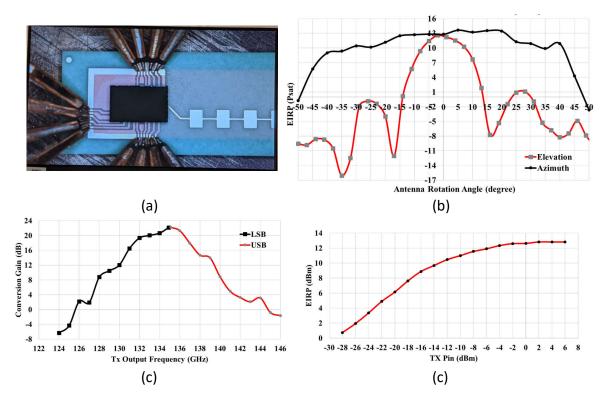

| 6.15 | Single CMOS transmitter channel with eight series fed patch antenna ar-                                                                                                                                      | 100          |

| 00   | ray) a) photo. b) EIRP at elevation and azimuth. c) conversion gain                                                                                                                                          |              |

|      | versus the output frequency. d) EIRP at broadside direction at 135GHz                                                                                                                                        |              |

|      | versus the input power (Courtesy of Ali Farid)                                                                                                                                                               | 151          |

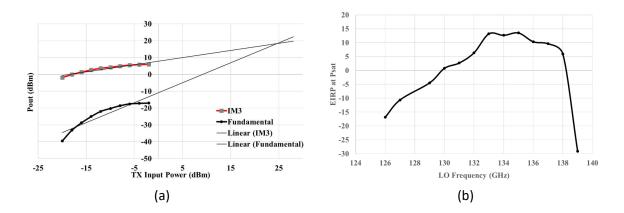

| 6.16 | Single CMOS transmitter channel with eight series fed patch antenna array                                                                                                                                    |              |

|      |                                                                                                                                                                                                              |              |

|      | IM3 b) LO tuning range versus the LO frequency (Courtesy of Ali Farid).                                                                                                                                      | 152          |

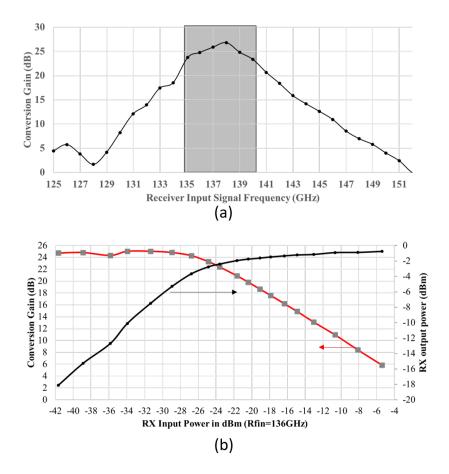

|      | a) Output power versus the input power at 135GHz at fundamental and                                                                                                                                          | 1            |

| 6.17 | Packaging results for 135GHz receiver with copper pillar transition: a)       |      |

|------|-------------------------------------------------------------------------------|------|

|      | Receiver conversion gain versus the output frequency. b) Measured re-         |      |

|      | ceiver's output power versus the input power, including the copper pillar     |      |

|      | transition loss.                                                              | 153  |

| 6.18 | a) Photos for the receiver module showing the LTCC ceramic interposer         |      |

|      | and PCB carrier board. b) Cartoon drawing for the CMOS receiver chip          |      |

|      | to the interposer showing the different type of transitions. c) Close look on |      |

|      | the LTCC ceramic interposer showing the antenna arrays and chip footprints    | .154 |

| 6.19 | a) Photos for the high-power transmitter module (CMOS with InP PAs)           |      |

|      | showing the LTCC ceramic interposer and PCB carrier board. b) Car-            |      |

|      | toon drawing for the CMOS transmitter and InP chips to the interposer         |      |

|      | showing the different type of transitions. c) Close look on the LTCC ce-      |      |

|      | ramic interposer showing the antenna arrays and InP and CMOS chips            |      |

|      | footprints                                                                    | 155  |

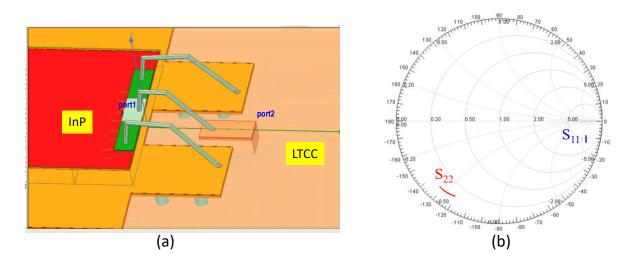

| 6.20 | a) HFSS model for the wirebond transition. b) Simulated S-parameters.         | 156  |

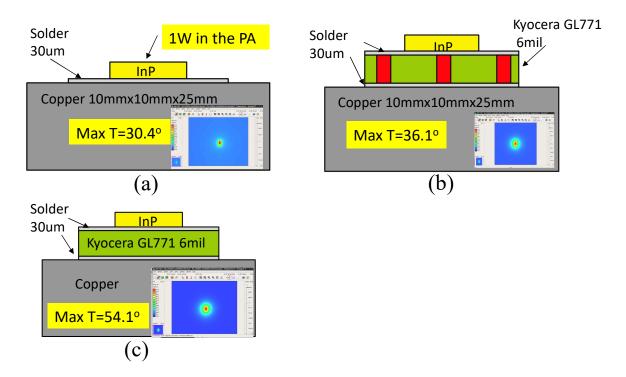

| 6.21 | Thermal simulation: a) Amplifier is mounted directly on a copper block.       |      |

|      | b) Amplifier is mounted on ceramic layer with thermal vias. c) Amplifier      |      |

|      | is mounted on ceramic piece without thermal vias                              | 156  |

| 6.22 | a) CMOS integrated to an InP chip and an eight-element series-fed patch       |      |

|      | antenna. b) Simulated S-parameters for the transition between InP and         |      |

|      | CMOS chips. c) Simulated antenna gain and the input reflection coeffi-        |      |

|      | ciont                                                                         | 157  |

# List of Tables

| 4.1 | DC biases for S-parameters                                | 86  |

|-----|-----------------------------------------------------------|-----|

| 4.2 | DC biases for power measurements                          | 88  |

| 4.3 | Comparison between state-of-the-art D-band amplifiers     | 90  |

| 4.4 | Comparison between state-of-the-art 130-140GHz amplifiers | 100 |

| 5.1 | State-of-the-art High-Efficiency G-Band Amplifiers        | 125 |

# Chapter 1

# Introduction

# 1.1 Millimeter Wave for Next Communication Generation

There is an increasing demand for high data rate wireless communication [3]. The population is getting larger and everyone demands access to high-speed internet, HD video, Skype... etc. On the other hand, we have a limited spectrum. Communication engineers are doing their best to increase spectrum efficiency by using higher-order modulation schemes to send more bits in the same frequency. But there is a point where we need to exploit more frequency bands.

Considering millimeter frequencies for the next communication generation exploits more frequency spectrum and the shorter wavelengths support massive spatial multiplexing [4], [5], and [3]. Unfortunately,  $\lambda^2/R^2$  path loss and weather attenuation are high. This demands building mm-wave transceivers with high output powers [1]. Building transceivers at high frequency requires advanced technologies with high power gain cutoff frequency ( $f_{max}$ ) such as InP [2].

Figure 1.1: Atmospheric loss [1].

In this thesis, we provide solutions beyond the research limit. It is great to have a working transceiver on the circuit level. However, there are limited applications for the bare die. We spent a considerable amount of time thinking about how to package the IC so they can be usable in a real communication system. Millimeter-wave packaging is one of the most challenging parts of the design. It requires different types of expertise. We had lots of interactions with the assembly houses such as Kyocera [6] to comply with their specifications and tolerance.

# 1.2 Dissertation Contributions and Organization

Chapter 2 reviews the millimeter-wave power amplifier fundamentals. We provide the necessary background for beginners. We start from the system level that defines the requirements for the power amplifier. The power amplifier basics are covered and the concepts of loadline and load-pull matching for maximum saturated output power are introduced. The power amplifier design starts from a single cell, moving to a practical

power amplifier which demands more gain and power. The design techniques are briefly discussed here while the following chapter presents detailed analysis and design. Power amplifier stability is demonstrated in different ways such as stability factors, transient analysis... etc.

Chapter 3 provides a design guide for optimum amplifier design. The amplifier's degrees of freedom are discussed. We can get higher output power by stacking, by scaling the stage's area, or combined approach. We propose a network theory that is considered the core of the chapter. The network theory introduces a new design technique by a two-port network. First, the conventional stack is reviewed and the limitations are discussed. Then we use the network theory to design the stack with two-port network techniques. Using the network theory in the stack adds more degrees of freedom and simplifies the design. The interstage matching is designed as a two-port network with full impedance matching. From the network theory, we can easily design with arbitrarily complex transistor models, complex interconnects, arbitrarily matching circuits, include neutralization techniques, and more.

We also cover parallel power combining techniques such as Wilkinson. We present the pros and cons of Wilkinson then we introduced a proposed general transmission line combiner. The proposed combiner is much more compact and has lower loss compared to the Wilkinson combiner. We present different ways of implementation based on the number of combined cells.

Finally, we combined the area progression techniques with the stack approach to provide a design guide for power amplifier considering most of the degrees of freedom. The network theory computes the efficiency for different design techniques so we can select the approach that gives the highest PAE. This chapter covers most of the intellectual

points in power amplifier design.

Chapter 4 presents lots of experimental results. We have designed lots of amplifiers at 140GHz, ~210GHz, and ~310GHz. The amplifiers are designed in 250nm and 130nm InP HBT technologies from Teledyne. The amplifiers demonstrate record PAE across all frequency bands. This chapter discusses the practical circuit implementation in real life. For each of the presented amplifiers, we analyze the power and driver cells. We stated the justification for such a choice. The combiner design is also demonstrated. After presenting the design details, we present the experimental verification. We have done S-parameters measurements and large-signal power measurements for most of the amplifiers. There are still ongoing measurements for newer versions. Most of the data are presented in several publications.

In Chapter 5, we demonstrate different variants of 210GHz transmitter. Prof. Munkyo Seo is the leading designer for the transmitter. Munkyo designed all the transmitter building blocks except for the power amplifier. The amplifiers are designed by the thesis author. To reduce the risk, the first transmitter does not have a high-output power amplifier. The second transmitter integrates a high-efficiency power amplifier. We also considered packaging options for the transmitter. We designed a 2x2 transmitter array. We followed the packaging approach that is proposed by UCSD and Zhe designed the Quartz antenna that is integrated with the 210GHz transmitter.

Massive MIMO demonstration and mm-wave packaging is covered in **Chapter 6**. We have 140GHz CMOS transceivers, designed by Ali Farid. GlobalFoundries gave us access to the advanced Copper pillar option. We also have bare dies for InP power amplifiers. The purpose of this chapter is to package those chips and build a tile in a modular fashion. We go step by step, starting from chip to package transition and matching.

Then demonstrating a single channel transmitter and receiver which consists of CMOS transmitter or receiver matched to a series fed patch antenna. Then we present the tile design which holds eight transmitters or receivers. We repeat the same steps for the higher power module where we have high output power InP power amplifiers. The chapter gives a great depth for mm-wave packaging design and challenges.

### 1.3 Permissions and Attributions

The material in this dissertation is partly based on the following publications. The dissertation author is the primary contributor to these published works and the co-authors have approved the use of the material for this dissertation.

- A. S. H. Ahmed, Munkyo Seo, A. A. Farid, M. Urteaga, and M. J. W. Rodwell, "A 140GHz power amplifier with 20.5dBm output power and 20.8% PAE in 250-nm InP HBT technology," 2020 IEEE/MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 2020, pp. 492-495.

- A. S. H. Ahmed, Munkyo Seo, A. A. Farid, M. Urteaga, and M. J. W. Rodwell,

"A 200mW D-band Power Amplifier with 17.8% PAE in 250-nm InP

HBT Technology," accepted to 2020 15th (EuMIC), Utrecht, 2020

- A. S. H. Ahmed, A. Simsek, A. A. Farid, A. D. Carter, M. Urteaga, and M. J. W. Rodwell, "A W-Band transmitter channel with 16dBm output power and a receiver channel with 58.6mW DC power consumption using heterogeneously integrated InP HBT and Si CMOS technologies", 2019 (IMS), Boston, MA, USA, 2019.

- 4. A. S. H. Ahmed, A. A. Farid, M. Urteaga, and M. J. W. Rodwell, "204GHz Stacked-Power Amplifiers Designed by a Novel Two-Port Technique, 2018

13th European Microwave Integrated Circuits Conference (EuMIC), Madrid, 2018, pp. 29-32.

5. A. S. H. Ahmed, A. Simsek, M. Urteaga, and M. J. W. Rodwell, "8.6-13.6 mW Series-Connected Power Amplifiers Designed at 325 GHz Using 130 nm InP HBT Technology, 2018 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), San Diego, CA, 2018, pp. 164-167.

# Chapter 2

# Millimeter-Wave Power Amplifier

# **Fundamentals**

## 2.1 Introduction

Power amplifiers are the key components in any transmitter. Based on Friis [7] equation (2.1), the amplifier's output power limits the transmission range for a required minimum received power. Efficiency is one of the key factors in PA. High-efficiency PA dissipates less heat and the battery lasts longer. This is necessary for any practical communication system. The power amplifier design starts with a unit cell. There are many different matching techniques (gain, power, PAE... etc.). Proper matching should be considered to achieve the required purpose. PA biasing defines the class of operation. Each class has its own characteristics (different gain, efficiency, and power) [8]. In practical cases, a single unit does not satisfy the system level requirement in terms of the required output power or gain. Multiple cells could be combined with various power combining techniques to reach the required power level. Driver stages are necessary to

increase the gain.

$$\frac{P_r}{P_t} = \frac{A_r A_t}{d^2 \lambda^2} \tag{2.1}$$

This chapter will review the unit cell and driver design considerations. Different matching techniques will be reviewed. Then, we will cover briefly the tradeoff between different classes especially at mm-wave frequencies. Different power combining techniques will be presented. Finally, we will show the challenges in the PA stability simulation.

## 2.2 Unit Cell Design

There are different types of matching to achieve different purposes. In power amplifiers, the main objective is to deliver the maximum saturated output power from the cell. This matching is called load line matching [8] or load-pull techniques. We will focus on class A design.

## 2.2.1 Loadline Matching

The relation between the collector (drain) current and collector to emitter (drain to source) voltage could be represented graphically (Fig. 2.1). There is a maximum voltage which is defined by the transistor breakdown and maximum current density. Each technology defines those values and is usually referred to as a safe operating area (SOA). The transistor should reach the maximum voltage and current simultaneously to deliver the maximum output power. The blue straight line represents the ideal contour for maximum output power. Any deviation from the straight line leads to early saturation for the current or the voltage and leads to lower power.

Figure 2.1: Ideal and Real Loadline for class A operation plotted on the SOA.

Real transistors have parasitics. Therefore, the relation between the internal collector (drain) current and  $V_{CE}$  ( $V_{DS}$ ) becomes elliptical and no longer linear (red curve in Fig. 2.1). In addition, the slope of the loadline is defined by  $1/(R_L)$  where  $R_L$  is the load impedance presented to the transistor. Generally, there is no guarantee that this impedance matches the optimum loadline impedance for maximum output power. The blue line represents the real loadline contours for a real transistor. The transistor will not reach the maximum voltage and current swing simultaneously. Either the voltage or the current will clip earlier.