### University of California Santa Barbara

# Design and Characterization of Circuits for Next-Generation Wireless Communications Systems

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Electrical & Computer Engineering

by

Robert Maurer

### Committee in charge:

Professor Mark Rodwell (Advisor), Chair Professor James Buckwalter (Committee Member) Professor Larry Coldren (Committee Member) Dr. Miguel Urteaga (Committee Member)

| The Dissertation of Robert Maurer is approved.    |

|---------------------------------------------------|

|                                                   |

| Professor James Buckwalter (Committee Member)     |

|                                                   |

| Professor Larry Coldren (Committee Member)        |

|                                                   |

| Dr. Miguel Urteaga (Committee Member)             |

|                                                   |

| Professor Mark Rodwell (Advisor), Committee Chair |

June 2017

# Design and Characterization of Circuits for Next-Generation Wireless Communications Systems

Copyright © 2017

by

Robert Maurer

### Acknowledgements

I've been incredibly privileged to spend the last 6 years working alongside so many brilliant minds from all over the world in the Rodwell group in beautiful Santa Barbara. Never in my life have I met anyone with the level of dedication and passion for their work that Professor Mark Rodwell has - not only as a scientist and an engineer, but as a teacher and a mentor. To him, I express my deepest and most sincere gratitude for giving me the opportunity to be here and making this all possible. He's relentlessly enthusiastic for his endless quest to learn, innovate, and succeed, but he always prioritizes the well-being of his students first and foremost. I believe this is a truly remarkable quality that deserves acknowledgement. I would also like to thank my PhD committee members, Professor James Buckwalter, Professor Larry Coldren, and Dr. Miguel Urteaga for their valuable advice and criticism during my qualifier and dissertation.

I'm extremely grateful to all of my Rodwell group colleagues, past and present, who have helped me and supported me along the way. Our post-doc, Dr. Seong-Kyun Kim has taught me a tremendous amount about IC design and measurements and he deserves special acknowledgement for the role he played in my academic development. Hyun-Chul Park, Thomas Reed, Zach Griffith, Munkyo Seo, and Colin Sheldon laid much of the groundwork upon which I built my research. The other circuit designers, Arda Simsek, Ahmed Ahmed, Hai Yu, and Ali Farid have all played a significant role in this work as well. I'd also like to thank my colleagues and mentors on the devices team from my past life working in device fabrication - Andy Carter, Johann Rode, Prateek Choudhary, Hanwei Chiang, Cheng-Ying Huang, Sanghoon Lee, Jeremy Law, Evan Lobisser, Vibhor Jain, and Doron Elias. Our newest devices team members, Brian Markman, Yihao Fang, Hsin-Ying Tseng, and Jun Wu have also been a tremendous help.

I'd like to thank the entire cleanroom staff, especially Brian Thibeault, Bill Mitchell,

Tony Bosch, Don Freeborn, Biljana Stamenic, Brian Lingg, Aiden Hopkins, and Tom Reynolds for their tireless work and interest in helping the students learn and succeed.

A special thanks to Teledyne Scientific and Global Foundries for fabricating the ICs used in my research.

Last but not least, I'd like to thank my family - my parents, Dan and Kathy, and my sister, Stephanie, provided me with unconditional love and support through my whole life. My loving wife, Barbara has stood by me, supporting and encouraging me through the most trying times of my career. Without her, I don't believe I'd be here at this point.

### Curriculum Vitæ Robert Maurer

#### Education

June 2011 - Present M.S/Ph.D. in Electrical and Computer Engineering (Expected), University of California, Santa Barbara

August 2007- May 2011 B.S. in Electrical Engineering, University of Notre Dame

#### **Publications**

**R Maurer**, S-K Kim, M Urteaga, MJW Rodwell, Ultra-wideband mm-Wave InP Power Amplifiers in 130 nm InP HBT Technology, Compound Semiconductor IC Symposium (2016)

**R Maurer**, S-K Kim, M Urteaga, MJW Rodwell, High-linearity W-band Amplifiers in 130 nm InP HBT Technology, Compound Semiconductor IC Symposium (2016)

S-K Kim, R Maurer, A Simsek, M Urteaga, MJW Rodwell, Ultra-Low-Power Components for a 94 GHz Transceiver, Compound Semiconductor IC Symposium (2016)

S-K Kim, **R Maurer**, A Simsek, M Urteaga, MJW Rodwell, A High-Dynamic-Range W-band Frequency-Conversion IC for Microwave Dual-Conversion Receivers, Compound Semiconductor IC Symposium (2016)

#### Abstract

Design and Characterization of Circuits for Next-Generation Wireless Communications

Systems

by

#### Robert Maurer

Demand for wireless data transfer has been increasing rapidly with the rise of smart devices and mobile video streaming. With dozens of wireless applications currently in use and only a finite bandwidth to work with, engineers are challenged to both expand the upward frequency limit of high-performance, high-efficiency wireless systems and to increase the spectral efficiency of the frequency bands already in use. The development of deep sub- $\mu$ m silicon-on-insulator transistor technology and powerful computer-aided circuit designing tools have allowed us to create more affordable silion-based phased array ICs at frequencies previously achievable by only military applications. The 5th generation of mobile systems (5G) is now expected to use this type of IC to offer increased wireless data capacity in densely-populated areas using mm-wave frequencies. Demand for wireless data is only expected to continue rising, particularly as new IoT applications such as autonomous vehicles become commercially viable.

The work presented in this dissertation addresses both the need for expanding the usable frequency spectrum and the need to increase spectral efficiency in available bands. It includes a design for an analog beamforming matrix for a spatially multiplexed phased array receiver in silicon SOI technology, low-power high-linearity w-band amplifiers in InP HBT technology, and ultra-wideband mm-wave power amplifiers in InP HBT technology. Spatially multiplexed phased array transceivers have the potential to greatly increase the spectral efficiency of mm-wave frequency bands by re-using frequency spectrum for many

data channels. This type of system can be used to create short-range high-capacity line-of-sight wireless backhaul for crowded city squares or event venues. Mm-wave power amplifiers and high-linearity amplifiers in new 130 nm InP HBT technology represent an IC performance boost which pushes the frequency limits of feasible power-efficient wireless systems.

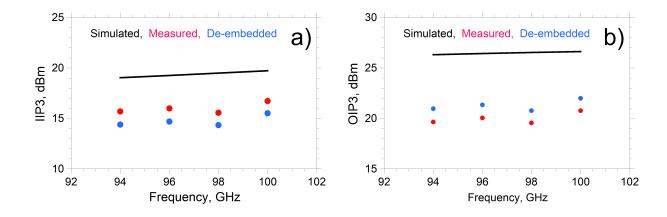

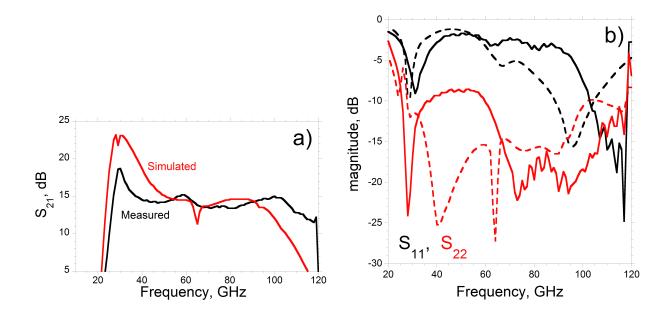

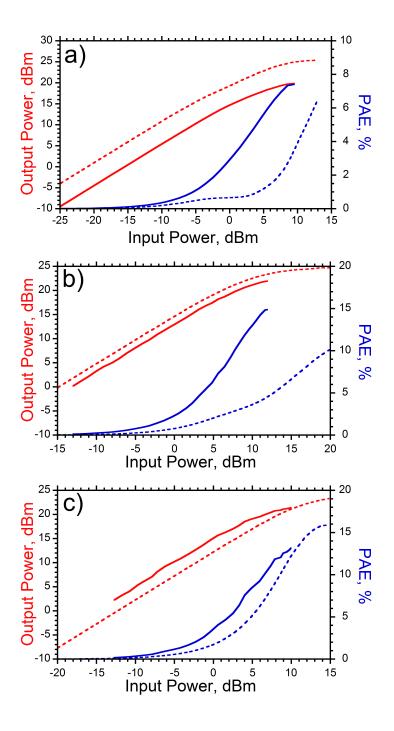

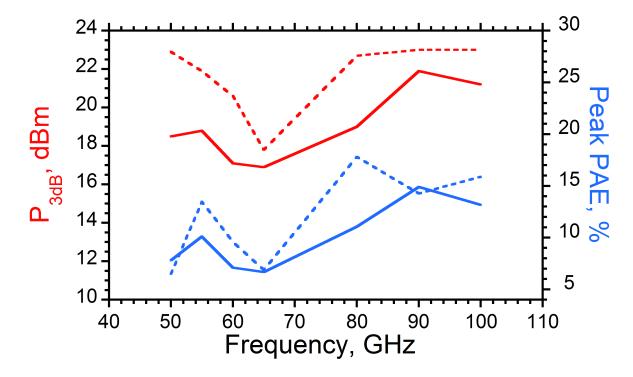

The measured power amplifier ICs produce output power of larger than 16.5 dBm at the 3-dB gain compression condition from 50 GHz to 100 GHz, and a small signal gain of 15 dB over a 90 GHz 3-dB bandwidth. The peak power-added efficiency (PAE) is larger than 8% over that same frequency range. At 90 GHz, the ICs produce 22 dBm of saturated output power and 14.7% PAE. The measured high-linearity amplifier ICs demonstrate an output-referred 3rd order intercept (OIP3) of 22 dBm, a gain of 6.4 dB, and a noise figure below 7 dB at 100 GHz. New designs for an analog MIMO beamforming matrix IC, a 100-165 GHz power amplifier, and an improved w-band high-linearity amplifier are also outlined in this dissertation.

# Contents

| $\mathbf{C}_{1}$ | Curriculum Vitae                                                  |                                                   |     |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------|---------------------------------------------------|-----|--|--|--|--|--|--|--|

| $\mathbf{A}$     | bstra                                                             | et                                                | vii |  |  |  |  |  |  |  |

| 1                | Bac                                                               | kground                                           | 1   |  |  |  |  |  |  |  |

|                  | 1.1                                                               | Introduction                                      | 1   |  |  |  |  |  |  |  |

|                  | 1.2                                                               | Basic Architecture of Wireless Links              | 2   |  |  |  |  |  |  |  |

|                  | 1.3                                                               | Linearity and Output Power                        | 6   |  |  |  |  |  |  |  |

|                  | 1.4                                                               | Noise                                             | 8   |  |  |  |  |  |  |  |

|                  | 1.5                                                               | Capacity and Bandwidth                            | 11  |  |  |  |  |  |  |  |

|                  | 1.6                                                               | Microwave and Mm-wave Design                      | 14  |  |  |  |  |  |  |  |

|                  | 1.7                                                               | Transistor Amplifiers                             | 19  |  |  |  |  |  |  |  |

|                  | 1.8                                                               | Mixers                                            | 23  |  |  |  |  |  |  |  |

|                  | 1.9                                                               | Modulation                                        | 26  |  |  |  |  |  |  |  |

| 2                | Nex                                                               | Next-generation Commercial Communications Systems |     |  |  |  |  |  |  |  |

|                  | 2.1                                                               | Introduction                                      | 32  |  |  |  |  |  |  |  |

|                  | 2.2                                                               | Frequency Expansion and Performance Tradeoffs     | 34  |  |  |  |  |  |  |  |

|                  | 2.3                                                               | Silicon on Insulator Technology                   | 36  |  |  |  |  |  |  |  |

|                  | 2.4                                                               | Phased Arrays and Beamforming                     | 38  |  |  |  |  |  |  |  |

|                  | 2.5                                                               | Spatial Multiplexing                              | 45  |  |  |  |  |  |  |  |

| 3                | Mm-Wave Power Amplifiers and High-linearity Amplifiers            |                                                   |     |  |  |  |  |  |  |  |

|                  | 3.1                                                               | Introduction                                      | 50  |  |  |  |  |  |  |  |

|                  | 3.2                                                               | Design of Mm-wave Power Amplifiers                | 51  |  |  |  |  |  |  |  |

|                  | 3.3                                                               | Mm-wave High-Linearity Amplifier Designs          | 59  |  |  |  |  |  |  |  |

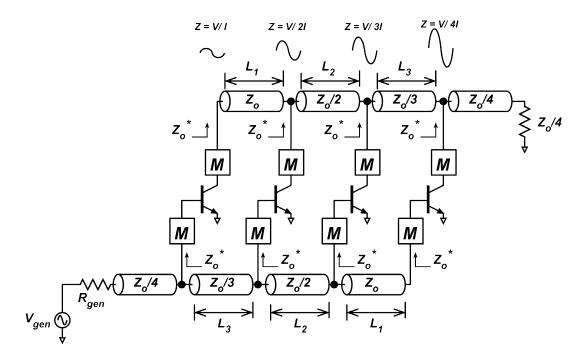

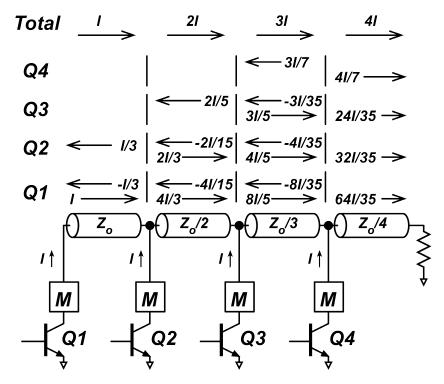

|                  | 3.4                                                               | Tapered-line Distributed Amplifiers               | 62  |  |  |  |  |  |  |  |

|                  | 3.5                                                               | Sub-Quarter Wavelength Baluns                     | 66  |  |  |  |  |  |  |  |

| 4                | Analog Beamformer Matrix IC Designs, Simulations, and Limitations |                                                   |     |  |  |  |  |  |  |  |

|                  | 4.1                                                               | Introduction                                      | 73  |  |  |  |  |  |  |  |

|                  | 4.2                                                               | Theory and Architecture                           | 74  |  |  |  |  |  |  |  |

| 5 | DARPA ACT Designs                                            |  |      | 94  |

|---|--------------------------------------------------------------|--|------|-----|

|   | 5.1 DARPA ACT Overview                                       |  |      | _   |

|   | 5.2 TSC 130nm InP HBT Process                                |  |      |     |

|   | 5.3 High-Linearity Amplifier 1st Design                      |  |      |     |

|   | 5.4 High-Linearity Amplifier 2nd Design                      |  |      |     |

|   | 5.5 Ultra-wideband Power Amplifier Lowside Injection Design  |  |      |     |

|   | 5.6 Ultra-wideband Power Amplifier Highside Injection Design |  | <br> | 102 |

|   | 5.7 High-Linearity Amplifier Measurements                    |  | <br> | 104 |

|   | 5.8 Ultra-wideband Power Amplifier Measurements              |  | <br> | 107 |

| 6 | Future Work and Conclusions                                  |  |      | 113 |

|   | 6.1 Future Work                                              |  | <br> | 113 |

|   | 6.2 Conclusion                                               |  | <br> | 114 |

|   |                                                              |  |      | 116 |

# Chapter 1

# Background

### 1.1 Introduction

In the 1890s, wireless communication was transforming from a laboratory novelty into a practical method of broadcast and communication [1]. Much earlier in 1865, James Clerk Maxwell predicted the existence of electromagnetic waves through Maxwell's equations. This was experimentally confirmed by Heinrich Hertz in 1888, which showed that wireless communications were possible. By the early 1900s, Guglielmo Marconi was building stations capable of wirelessly transmitting telegraph messages across the Atlantic via electromagnetic waves [1]. Wireless technologies for military radar and communications and commercial broadcasting developed rapidly through the 1900s. The airwaves quickly had to be regulated to avoid interference from multiple signals on the same frequency bands. Demand for wireless at both the consumer level and the military level has only continued to increase as technological developments have opened the door to new applications.

Today, mobile phones are ubiquitous throughout much of the world. In the age of digital information, consumers now want more than the ability to communicate while on

the go. They want access to the internet and video streaming even when they are far away from their WiFi router. The demand for larger overall network capacity continues to skyrocket. The military continues to seek high frequency hardware for applications in detection, imaging, electronic warfare, and battlefield control over communications channels.

There are many architectures of wireless link front-end modules, but almost every modern RF wireless link shares some unifying design principles that are critical for communications engineers and analog circuit designers to understand. In this chapter, I will discuss background information on the basics of integrated circuits (ICs) in modern RF wireless links, network capacity, and circuit techniques, as well as the benchmarks for high-performance designs.

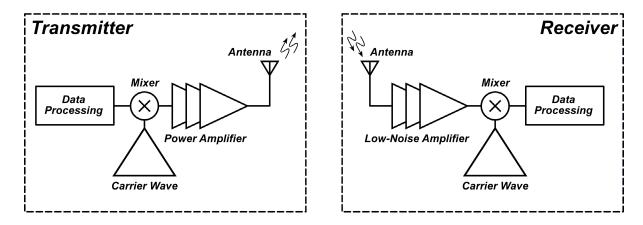

# 1.2 Basic Architecture of Wireless Links

Figure 1.1 shows a basic block-level illustration of a simple direct-conversion wireless link [1] [2] [3]. The ultimate goal of the system is to take a set of analog or digital data, and send it from one point to another via electromagnetic waves with minimal digital errors or analog distortion. The transmitter contains a mixer, a linear power amplifier, and an antenna. The reciprocal receiver has an antenna, a low-noise amplifier, and a mixer. In this section, I will explain the principles of wireless links which provide a successful transmission of data.

Wireless links are used to transport either an analog set of data in the form of an arbitrary waveform, or digital data in the form of an arbitrary string of bits (1s and 0s) from one place to another. The dataset exists within a complex-valued baseband signal, and must be arranged in a form that can be transmitted within a single channel. Therefore, the data must be encoded, or modulated, into a waveform with a narrow

Figure 1.1: Block diagram of a basic wireless link.

channel bandwidth, called a passband [1][4]. The signal is symmetrically de-encoded, or de-modulated, back into the original dataset form at the receive end of the link [4]. There are various types of modulation schemes that are used (AM, FM for analog; PSK, QAM for digital), depending on the application, but all of them use some type of mixer (or multiple mixers) to achieve this goal [1][4]. Mixers and modulation schemes will be discussed further in sections 1.8 and 1.9.

At any point along the wireless link circuitry, the signal carries some average power level. This is expressed mathematically in equation 1.1, where the boldface V and  $I^*$  are the complex voltage phasor and the complex conjugate of the current phasor respectively [5]. The power of the associated signal can be increased by introducing gain. In modern architectures, gain is achieved via transistor amplification. Depending on the context, gain can refer to an increase in the voltage or current signal amplitude, or the average power level [6]. The design considerations and goals for different types of transistor amplifiers will be discussed in more depth in section 1.7.

$$P_{signal} = \frac{1}{2} \Re(\mathbf{VI}^*) \tag{1.1}$$

A power amplifier (PA) should be used at the output of the transmitter to send the

data set with as much range as possible [1]. The free-space path loss (FSPL) of an electromagnetic wave is defined by equation 1.2, where d is the propagation distance and  $\lambda$  is the wavelength of the carrier wave [7]. This means, for a given channel frequency, the received power drops rapidly with distance, and this problem is exacerbated at higher frequencies. In addition, there is frequency-dependent atmospheric absorption based on the weather and humidity [8]. This is a major design challenge, considering the receiver has a finite sensitivity [1]. In the case of commercial applications, there is an FCC-imposed safety limit for effective isotropic radiated power (EIRP), so power outputs for hardware for these applications are typically designed up to near this limit. The military are not subject to the same set of regulations, and therefore wireless hardware for their applications is often designed for maximum possible transmit power for optimum range and resolution. Power amplifier design considerations and further applications will be discussed more in section 1.4.

$$FSPL = \left(\frac{4\pi d}{\lambda}\right)^2 \tag{1.2}$$

At the receive end, a low-noise amplifier (LNA) is used to maximize receiver sensitivity, thereby maximizing the transmission distance [1]. There is a background level of noise produced by gas molecules in our atmosphere that washes out the desirable signal. Additionally, all transistors, diodes, and resistors generate noise on their own, meaning that at any point along the wireless link, there is a desired signal power and an unwanted noise power [1] [4] [3]. The ratio between these two powers is called the signal to noise ratio, or SNR, which is mathematically expressed in equation 1.3 [5] [1]. As designers, we would like this value to be kept as large as possible to preserve the integrity of the

transmitted data set.

$$SNR = \frac{P_{signal}}{P_{noise}} \tag{1.3}$$

Amplifiers such as PAs and LNAs can be used to increase the power level of the desired signal, however, the noise power will inevitably see the same factor of power increase, or gain [5] [1]. Therefore, since any circuit elements introduce noise into the system, there is a degradation of the signal to noise ratio associated with any circuit block. This degradation is called the noise factor, F, shown in equation 1.4 [5]. This degradation is important, because it sets the minimum acceptable level of received signal power to achieve desired performance at the back end of the receiver [1]. A low-noise amplifier is designed to provide a large amount of gain while simultaneously minimizing the associated degradation of SNR [1]. Design considerations for LNAs will be discussed in greater depth in section 1.5.

$$F = \frac{SNR_{out}}{SNR_{in}} \tag{1.4}$$

Keep in mind that these are just the very most basic building blocks that must be used to achieve reliable wireless transmission. In almost any practical application, there is a local oscillator used to generate the carrier waveform. There are usually multiple filters used throughout the system to block unwanted harmonics and tones from distorting the desired signal. This is also excluding phase-controlling and clock-syncing circuitry used to enable advanced forms of data modulation [1]. These techniques are of critical importance to the function of modern wireless links, however, they will only be peripherally addressed within the scope of this dissertation.

# 1.3 Linearity and Output Power

One of the important benchmarks for RF performance is linearity. A circuit block is perfectly linear if the transfer function of the amplifier H(x) has the property H(Ax + By) =AH(x) + BH(y) [1]. In qualitative terms, the output signal is a perfect duplication of the input signal, only larger or smaller. In reality, there is always some level of distortion inherent in any amplifier, mixer, or filter which manifests itself in the form of unwanted harmonic tones [1]. Odd-ordered distortion products (3rd order, 5th order, etc), as opposed to even-ordered harmonics, appear at or near the design frequency, and therefore cannot easily be filtered out. As input power is increased, the log of the output power of the 3rd order distortion product signal increases at 3 times the rate as that of the log of the fundamental tone. This is the reason why bias-point amplifiers are biased with a voltage right between the maximum and minimum voltages of the safe linear operating region. It allows the amplifier to handle a larger voltage swing without causing high levels of distortion. Class-A amplifiers are biased such that current is conducting through the entire voltage swing, which creates low levels of distortion at low power with relatively low drain/collector efficiency, while class-B and class-C are biased such that current is conducted for a fraction of the time. Hence class-B and class-C amplifiers have moderate levels of distortion even at low power levels, but higher efficiency than class-A amplifiers [1] [5].

Linearity is quantified in terms of IP3, or 3rd order intercept, in units of watts or dBm [1] [5]. This can be measured using a 2-tone measurement. If there are 2 slightly offset fundamental tones,  $f_1$  and  $f_2$  which are applied to a circuit block simultaneously, 3rd-order intermodulation products will appear at the frequencies  $2f_1 - f_2$  and  $2f_2 - f_1$  [1]. The 2 fundamental tones are applied at equal power levels below gain compression, and the output power levels are measured along with the power of the 3rd-order intermodula-

tion tones. The output power levels can be plotted vs. input power in terms of dBm [1]. The 3rd-order intermodulation product power levels will follow along a line with a slope of 3, and the fundamental output powers will follow along a line with a slope of 1 [1]. If those lines are extrapolated, there will be a power where the lines intercept. The input power at which this occurs is referred to as the IIP3 or input-referred 3rd-order intercept and the output power at which this occurs is called the output-referred 3rd order intercept or OIP3 [1] [5].

The most high-performance mixers used in RF receivers and transmitters are passive diode mixers [1]. These require a very high-power signal driving the local oscillator port to reduce the distortion introduced by the mixer [1]. Therefore, when designing a power amplifier to drive the local oscillator port of a passive mixer, output power is sometimes quantified in terms of saturated output power. This is the value of  $P_{out}$  at which it no longer increases with an increase in  $P_{in}$ .

The boundaries on linearity in a class A amplifier are determined by the breakdown voltage,  $V_{br}$ , current cutoff, where  $I_c$  or  $I_d$  reaches zero, and the collector or drain saturation voltage or knee voltage. As the output signal becomes more distorted, the apparent gain drops, resulting in a saturation of the  $P_{in}$  vs.  $P_{out}$  curve [5]. Therefore, in the case of a class-A amplifier, the optimum output impedance for high linearity is also the optimum output impedance for maximum output power for a given bias point. The compression in the gain curve is quantified in different ways depending on the purpose which the amplifier serve. The 1-dB compression point,  $P_{1dB}$ , is the output power at which the amplifier's gain has reduced by 1-dB from the small signal value, and the 3-dB compression point,  $P_{3dB}$  is the output power at which the amplifier's gain has dropped by 3-dB from the small signal value. For driver amplifiers, it is often useful to quantify the saturated output power,  $P_{sat}$ , which is the very maximum amount of power the amplifier is capable of emitting. As a transmitting amplifier, the output should have low levels of

distortion to keep the out-of-band interference small, and, in systems with very complex modulation constellations, to avoid bit errors. Therefore, it is common for transmitter amplifiers to quantify output power in terms of 1-dB compression point,  $P_{1dB}$  [1].  $P_{1dB}$  is the value of output power at which the power gain is 1 dB lower than it is at small signal [1] [5].

The linearity of a receiver is particularly important for both military communications systems and consumer and commercial applications. In military applications, enemies may be trying to block communications with high-power in-band jammers. High-power signals that fall within the receiver passband are capable of distorting the desired signal and creating unwanted products which also fall within the receiver passband. Therefore, in any battlefield-applicable wireless application, it is desirable to achieve extremely high linearity. In commercial applications, depending on the quality of filtering in the receiver, linearity is very important to prevent interference from nearby frequency bands. Thus, for any application, linearity is a desirable trait for both transmit and receive functions. Oftentimes, the limiting factor on wireless transceiver linearity is the cost of the hardware.

### 1.4 Noise

If you have ever been in your car searching for a radio station and landed on a channel which is not currently broadcasting, youve heard the loud irritating sound we usually refer to as white noise or radio static. It's reasonable to wonder why you hear this rather than silence. If nothing is broadcast, why does our radio make any sound at all? In addition to the many other channels which are being broadcast simultaneously at other frequencies, there are also thermally-induced electromagnetic fluctuations in the circuit elements of the receiver which produce random voltage and current variations [1] [4] [5]. Furthermore, there is a background level of thermal noise produced in the atmosphere [1]. We refer to

all of these random electromagnetic fluctuations collectively as noise. In general, if we are to successfully transmit a set of data wirelessly, the data signal at the de-modulated end of the receiver must have more power than the noise at that same point, therefore noise determines the minimum power level required for successful wireless data reception [1]. Ideally, the signal power is significantly larger than the noise power so that the probability of errors in the data is minimized. In this section, I will discuss the basics of noise and the role it plays in wireless communications.

The Boltzmann constant is a physical constant which relates the average kinetic energy in particles of gas with the temperature of the gas. The result is that there is a spectral density of noise power produced in the background depending on the background temperature. The background noise power is kTBW where k is the Boltzmann constant, T is the temperature in Kelvin, and BW is the receiver bandwidth. At room temperature, this is  $4.14*10^{-21}$  Joules per Hertz, or in logrithmic units,  $-173.9\frac{dBm}{Hz}$  [1]. The receiver will detect the desired signal with a particular power level depending on the transmit power and distance, antenna directivities, attenuation due to weather, etc, which provides the receiver with an initial SNR. Unfortunately, since any circuit elements introduce additional noise into the system and any amplification of the desired signal will also apply to the noise signal, the SNR cannot be improved and will only ever be degraded [1] [5]. The degradation of the SNR associated with a circuit block is called the Noise Factor F as discussed earlier. This is often expressed in terms of Noise Figure, NF, expressed in dB instead of magnitude, shown in equation 1.5 [5].

$$NF = 10\log\left(F\right) \tag{1.5}$$

The noise signal at the input of a group of series-combined amplifiers is going to be amplified more than noise introduced after gain has been introduced. Equation 1.6 shows

the overall noise factor of N series-combined amplifier stages, where  $G_m$  is the magnitude of the gain of stage m [1] [4] [5].

$$F_{total} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \dots + \frac{F_N - 1}{G_1 G_2 \dots G_{N-1}}$$

(1.6)

So the noise contribution from each gain stage is smaller than the stages that came before it. This is why, for the very first gain stage of a receiver, it is critical to use a low-noise amplifier which adds gain while introducing as little noise as possible into the system to maximize sensitivity.

As mentioned earlier, a larger SNR produces a lower probability of errors for each bit transmitted. The bit error rate or BER is the probability of a transmission error for each bit which is transmitted - depending on the application, the acceptable level of BER can be on the order of  $10^{-3}$  or can be even lower than  $10^{-12}$ . When quantifying the sensitivity of a receiver in terms of the lowest acceptable received signal power, we need to first determine the minimum acceptable BER and the minimum acceptable SNR,  $SNR_{min}$ .

The sensitivity of a receiver,  $S_{dBm}$  [9] [10], in terms of minimum acceptable received signal power is therefore:

$$S_{dBm} = 10 \log_{10} \left( \frac{kTBW}{1mW} \right) + NF_{Receiver} + SNR_{min,dB}$$

(1.7)

The dynamic range of a system is the difference between the highest amount of power a system can receive, and the lowest amount of power a system can receive [1]. Therefore, the boundaries of dynamic range are set by the noise floor on the low end and linearity on the high end. This is an important figure of merit for high-performance receivers [1].

### 1.5 Capacity and Bandwidth

Commercial wireless technology is driven by the demand for increased capacity. At the individual consumer level, people want to talk on their phones, send text messages, surf the internet, and stream videos all from their phone even when they are far away from their WiFi router. Streaming videos wirelessly over mobile channels in particular requires a large data capacity on individual channels. At the network level, mobile phone usage continues to become more ubiquitous. Allowing many people in a local area to simultaneously consume and send data on their mobile phones requires the use of many channels. The FCC must allocate a finite frequency bandwidth for mobile networks so that it does not interfere with other bands reserved for radio, TV, navigation systems, radio astronomy, military, and many other applications. Unfortunately, within a limited bandwidth, it is impossible to limitlessly increase both the number of channels in a given area and the capacity of each channel [1] [11]. The limits of bandwidth and capacity and the ways to improve them will be discussed in this section.

The foundation of communication theory is the Shannon Capacity, C. For a channel with additive white Gaussian noise, of bandwidth BW and signal to noise ratio of SNR, the capacity is in equation 1.8 [11].

$$C = BWlog_2 (1 + SNR) \tag{1.8}$$

In 1948, Claude Shannon showed that the fundamental limit of bits per second for a given band-limited noisy channel is directly related to the bandwidth and the signal-to-noise ratio of the signal [11]. Since the bandwidth of a network is typically fixed by standards and regulations, this makes it the designers job to design links with the largest possible SNR within a given power budget, maximizing spectral efficiency (data rate per bandwidth) [1]. However, in the context of next-generation technologies, it is important

to note that developing viable circuit and device technologies at previously unreachable frequencies gives the FCC more bandwidth to allocate in the future, which will ultimately play an important role in the expansion of network capacities. This is a concept that will be addressed in this dissertation, particularly in the 3rd chapter.

It is important to note that Shannon's proof relies on channel codes of arbitrarily great length, and does not show how to attain this capacity with practical codes of moderate length and hence moderate computational complexity within the receiver. Within the scope of this thesis, I will not devote much attention to the various ways that modulation can be used to minimize the bit error rate at Shannon capacity. Instead, more attention will be devoted to ways the limit can be increased through bandwidth expansion and spatial multiplexing techniques which can efficiently improve spectral efficiency.

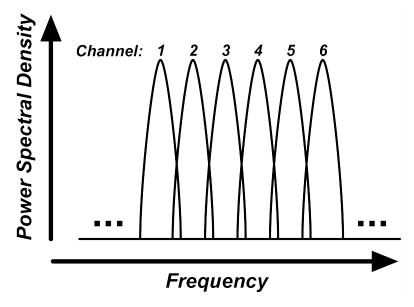

Historically, channels are divided up using frequency multiplexing (figure 1.2) within the allotted bandwidth for a local mobile network, although Code Division Multiple Access (CDMA) uses a set of non-orthogonal codes [1]. For hardware designers, the total allowable frequency band has already been pre-determined by regulations, so to accommodate a large number of users, many channels with narrow bandwidths are employed within the range of each cell tower. In urban areas with high population densities, this becomes a major issue as mobile data usage becomes more ubiquitous. One possible solution to increase network capacity is to increase the number of channels within a given bandwidth by using spatial multiplexing [12]. This can be done using phased antenna arrays, which will be discussed in more depth in the next chapter.

Expanding usable frequency limits to open up more usable bandwidth is limited at the circuit level by limited device performance at high frequencies [1] [5]. In the consumer market, device limitations at high frequencies are especially problematic. Since commercial RF ICs are designed with the intention of feasible mass production, they are often designed in silicon CMOS technology, which is cheap and can be produced entirely

Figure 1.2: Frequency multiplexing involves allocating discrete sections of network bandwidth to separate different channels

with optical lithography. RF ICs for military applications and instrumentation are often developed less cost-effective process technologies, such as InP HBT technology, which is much faster, but is capable of high performance at much higher frequencies [13].

Another method opening up wireless communication channels at higher frequencies is with the use of highly directional phased antenna arrays to combat severe free space path losses and atmospheric absorption at higher frequencies [14]. Any antenna has a radiation pattern which determines how much of the delivered power is radiated in any given direction [1]. Only the portion of the beam directly pointing at the receiver is useful, and larger beam widths and secondary lobes of the radiation pattern limit the power of the received signal. Improving the directionality, D, of an antenna on either the transmitter or receiver improves the antenna gain, G, as seen in equation 1.9 [7]. The effect of this on received power can be seen in the Friis Transmission Equation (equation 1.10) [7].

$$G = E_{ant}D (1.9)$$

$$\frac{P_r}{P_t} = G_t G_r \left(\frac{\lambda}{4\pi R}\right)^2 \tag{1.10}$$

where  $E_{ant}$  is the antenna efficiency,  $G_t$  and  $G_r$  are the gain of the transmit and receive antennas respectively,  $P_t$  and  $P_r$  are the transmit and receive powers, and  $\lambda$  is the wavelength of the signal [7]. As frequency increases,  $\lambda$  decreases, which reduces the received power, limiting the range of the link. The transmit power is typically limited by FCC regulations for many applications, so the most sensible knobs to turn in this equation are the antenna gains. The FCC also limits the effective isotropic radiated power, EIRP, which is equal to  $G_t * P_t$ . Consequently, at some point, the gain of the transmit antenna will reach a maximum allowed value, and the only knob to turn is the gain of the receive antenna  $G_r$ . Increasing the directionality of the antennas can improve SNR and enable channels at higher frequencies, which will improve network capacity [11] [7]. This is not a simple task, as most antennas are mechanically stationary, and a directional antenna needs to be pointed at its target. This is difficult for a mobile phone user who is moving around or does not have a direct line of sight to the tower. Directional antennas for mobile usage will be addressed in the next chapter.

### 1.6 Microwave and Mm-wave Design

Extending usable bandwidth to higher frequencies requires advanced circuit design techniques beyond traditional analog design methods [1] [5]. As wavelengths shrink to dimensions comparable to wire lengths, the inductive and capacitive interconnect parasitics must be carefully tracked and taken into design consideration to prevent unwanted reflections and impedance transformations [5]. At these frequencies, because interconnect inductive and capacitive parasitics are significant, interconnects with controlled

impedances are used to propagate confined electromagnetic modes. This way, the parasitic effects are predictable and can be included in the IC design. As frequencies continue to increase, even smaller, previously insignificant parasitic capacitances and inductances also begin to have a larger impact on circuit and device performance. In the past few decades, advances in computer aided design, electromagnetic modeling software, fabrication technology, and computational power have enabled reliable integrated circuit designs at frequencies larger than 100 GHz. As computing power and RF device frequency performance continue to progress, there is a path forward to improving the available bandwidth of wireless technologies. Circuit designers will be required to use techniques described in this section to make more energy-efficient designs

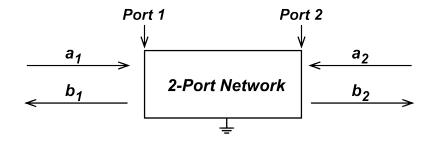

Typically, in dealing with circuit blocks at high frequencies, scattering parameters, or S-parameters, are used most often, and are often supplemented with Y- and Z- parameters for device model extraction [5]. Figure 1.3 shows how scattering parameters are quantified. Here, we are quantifying the amplitude of incident waves at port n with the variable  $a_n$  and the amplitude of the outgoing wave at port n with the variable  $b_n$  [5]. The S-parameters for a 2-port network can be represented by the matrix shown in equation 1.11 [5]. Since  $S_{21}$  is the amplitude of the wave outgoing from port 2 of a 2-port network divided by the amplitude of the incident wave to port 1, it follows that  $S_{21}$  is the insertion voltage gain (or loss) of a 2-port network and  $|S_{21}|^2$  is the insertion power gain [5].

$$\begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} = \begin{bmatrix} \frac{b_1}{a_1} & \frac{b_1}{a_2} \\ \frac{b_2}{a_1} & \frac{b_2}{a_2} \end{bmatrix}$$

(1.11)

Designing circuits at microwave frequencies requires a solid understanding of analog circuit design principles and impedance tuning. For any circuit, there are optimum impedance conditions for various intended outcomes [1] [5]. For example, to design a

Figure 1.3: 2-port network showing incident and reflected components

two-stage amplifier with maximum power transfer between stages, the designer would like to ensure that the input impedance of the second stage is the complex conjugate of the output impedance of the first stage [6]. In a low-frequency analog design, one generally focuses on voltage gain at a given specified load impedance. In a microwave frequency design, where transistor available power gains can be low, to obtain adequate gain, one may need to provide impedance matching so as to obtain gain close to the maximum available gain. It is efficient to introduce a carefully modeled passive impedance transformation network [1]. To understand why this works, consider equation 1.12 representing the input impedance of a transmission line terminated with a load resistor.  $\beta$  is the phase constant,  $Z_0$  is the characteristic impedance of the transmission line, and  $Z_L$  is the load resistance [5]. Note that at frequencies where  $l << \lambda$ , the imaginary component approaches 0, and the input impedance approaches  $Z_L$  [5]. As frequency increases and wavelength decreases, it takes less space to provide passive transmission line impedance transformations.

$$Z_{in}(l) = Z_o \frac{Z_L + jZ_o \tan(2\pi l/\lambda)}{Z_o + jZ_L \tan(2\pi l/\lambda)}$$

(1.12)

As one could imagine, dealing with these complex expressions for multi-stage circuits and taking minute parasitic elements into account using analytical numeric expressions is extremely unwieldy for designs of any appreciable complexity. This is why Smith

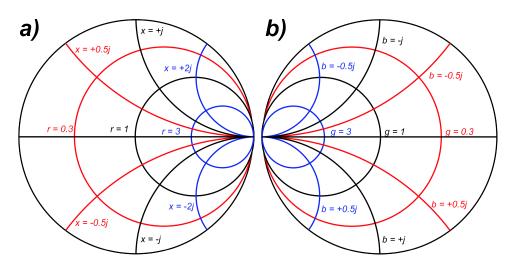

charts and computer-aided electromagnetic modeling are used to quickly visualize and determine impedance or admittance transformations, and take small parasitic values into account. The Smith chart is a graphical representation of normalized complex numbers which can easily transform numbers between impedance-space and admittance-space.

The center of the chart, seen in figure 1.4, is the normalized impedance of 1 + j0. Typically, the system impedance (commonly 50  $\Omega$ ) is the normalization impedance [5]. The horizontal line across the center of the chart represents a geometric progression of the real component of the impedance where the left corner is a short circuit (no resistance or infinite conductance) and the right corner is an open circuit (infinite resistance or no conductance). Radial lines extend from the right or left side of the chart, representing the lines of constant reactance or susceptance, respectively (figure 1.5a, b). These radial lines of constant reactance or susceptance are always perpendicular to circles of constant resistance or conductance respectively. If S-parameters are plotted on the chart, a parameter or reflection with a magnitude larger than 1 will fall outside the boundaries of the unit circle [5]. In bilateral amplifiers, for example,  $S_{11}$  or  $S_{22}$  landing outside of the Smith chart is an indication of negative input or output impedance and hence instability [1] [5].

Figure 1.4: Normalized Smith charts in a) Impedance space, b) Admittance space

Stability can also be determined by calculating the Rollet stability factor, K, and the  $\mu$  stability factor from S-parameters at each frequency as shown in equations 1.13 and 1.14 [5].

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{21}S_{12}|}$$

(1.13)

$$\mu = \frac{1 - |S_{11}|^2}{|S_{22} - S_{11}^* \Delta| + |S_{21} S_{12}|}$$

(1.14)

where  $\Delta = S_{11}S_{22} - S_{12}S_{21}$  is the radius of the stability circle at that frequency. The circuit is unconditionally stable if  $\mu > 1$  and K > 1.

When dealing with lumped reactive elements, such as inductors and capacitors, the Smith chart is a helpful tool for visualizing how the impedance is transformed with each element, starting from the load and moving backwards towards the input. For an added inductance, the impedance moves upwards along a circular path by the normalized imaginary impedance associated with the inductor. If the inductor is a shunt element, it moves along the circle of constant conductance, and if it is a series element, it moves along the circle of constant resistance in impedance space. Similarly, adding a shunt or series capacitance results in a downwards move along the circle of constant conductance or constant resistance respectively [5].

Transmission line impedance transformations can also be easily made using Smith charts. A series transmission line with length l creates a clockwise rotation of  $\frac{\pi\lambda}{4l}$  radians about the circle centered at the point on the Smith chart representing the normalized characteristic impedance of the transmission line. Adding a shunt transmission line moves the impedance upwards along the circle of constant conductance an angle equal to  $\frac{\pi\lambda}{4l}$  radians. Being able to easily plot and visualize impedances this way also makes it easier to design for optimum noise or power transfer conditions. As I will explain in more detail

later, the impedance optimized for different conditions can also be plotted on the Smith chart to help design for high linearity, high output power, or low noise [1] [5].

As design frequencies become a substantial fraction of the transistor  $f_{max}$  (maximum frequency of unity power gain), the maximum available stable gain drops [1] [6] [5]. When the transistor gain is high, it allows the designer to use techniques to trade gain for linearity or reduced noise. This makes it more difficult to achieve high linearity, output power, or efficiency while still achieving enough gain to be of use to the overall system and low noise figure. At high frequencies, transistor cell size and bias conditions should be planned carefully to minimize the insertion losses and parasitic elements introduced by passive impedance matching networks. Transmission lines are not entirely lossless, and the associated insertion losses can introduce thermal noise on the input of an LNA or eat into power gains (and therefore power-added efficiency) at the output of a PA. As we continue to push the limits of high frequency circuit design to open up usable wireless bandwidth, these techniques and ideas will continue to play a more important role for circuit designers.

### 1.7 Transistor Amplifiers

Quantitatively, the vast majority of transistors in use today are used for digital logic, however, for front-end wireless link design, we are generally more interested in the minority which are used for analog amplification of arbitrary waveforms. There are 2 broad categories of transistors - MOSFETs and BJTs, and both of them can be used for either digital or analog applications [6]. In digital logic, circuit blocks are designed to provide either a high (1) or low (0) output, depending on the inputs and functionality of the circuit block. In analog applications, circuit blocks are designed to take an arbitrary waveform and reproduce it with a desired effect. Filters remove unwanted frequencies,

mixers modulate or de-modulate frequencies, and amplifiers prodive linear gain to a signal in a particular frequency range. In this section, I will discuss the basic techniques and concepts used to design amplifiers using transistors.

Gain is the quality of a transistor that makes amplification of an arbitrary waveform possible. This means that a signal applied to one terminal of the device, is reproduced at another terminal, only larger. Gain can refer to voltage gain, current gain, transconductance (current from voltage), transimpedance (voltage from current), or power gain in terms of which quantity of the signal is being amplified. Power gain is simply output power  $P_{out}$  divided by input power  $P_{in}$ . Gain can vary over a large range of magnitudes, so it is often expressed in logarithmic form in terms of dB, such as for power gain as expressed in equation 1.15 where  $G_{power}$  is the amplifier power gain [5].

$$G_{power} = 20 \log \left( \frac{P_{out}}{P_{in}} \right) \tag{1.15}$$

BJTs have a number of advantages over MOSFETs in terms of RF circuit performance. They generally have a higher switching speed for comprably advanced technology nodes, making them preferable for very high-frequency applications [13]. They demonstrate higher drive current per unit of area which makes them superior for power applications. They have a higher output impedance, which makes them better current sources, and they have better noise performance. For applications where mass-production is not an issue, such as high-performance measurement instruments and specialized military-grade equipment, BJTs are used more often. For most consumer applications such as mobile phones, MOSFETs are predominantly used because of cost. The fastest silicon-based CMOS technology can be patterned entirely via optical lithography, making the effective cost per chip very small aside from the design and mask development costs. This brings some extra limitations for circuit designers working in these areas.

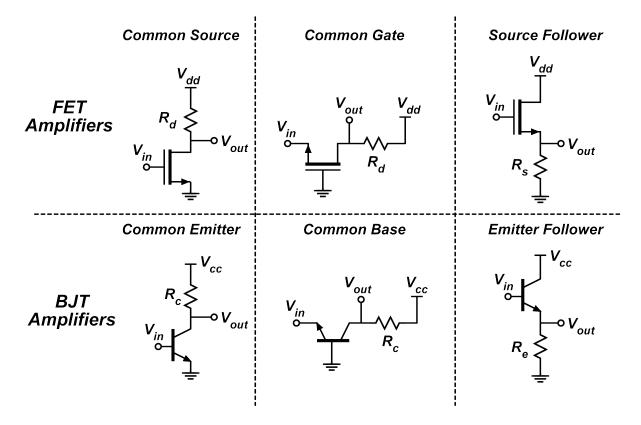

The three common forms of amplifier are common emitter/source, common base/gate, and emitter/source follower [6]. These are shown in figure 1.5.

Figure 1.5: Amplifier topologies

Common emitter/source amplifiers are used most often, as they provide a high voltage gain and current gain and a moderate input and output impedance. Common base/gate amplifiers can have a very large voltage gain, but unity or smaller current gain. They have a low input impedance and a high output impedance. Emitter/source follower amplifiers have a voltage gain at or smaller than unity and can have a high current gain. They have a large input impedance and a small output impedance. Common base and common collector configurations are often used as buffer amplifiers or impedance transformers. Each of these amplifier topologies requires that the transistor be biased in forward active mode to function correctly [6].

Transistor amplifiers are almost always designed to provide some type of gain or an impedance transformation, however, depending on the application, they may be designed to optimize for other properties, such as high power or linearity or low noise.

### 1.7.1 Power Amplifiers

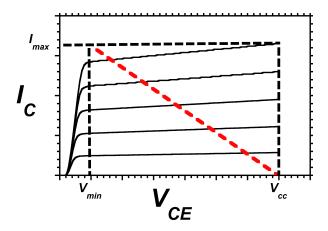

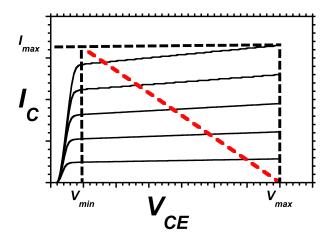

As their name suggests, the key function of a power amplifier is to deliver a large amount of power to a load. Like other transistor amplifiers, it consumes DC power and converts it into AC power under the control of the input signal. The key classes of interest in the scope of this dissertation are class A, class B, and class AB. There are many other classes of power amplifiers, but most of these rely on harmonic cancellation to reduce distortion or increase efficiency, which is not practical at very high frequencies. A class-A amplifier has the lowest levels of distortion, but does not provide gain as efficiently as a class-B amplifier. An example of a class-A amplifier circuit with a bipolar transistor may look similar to a single-stage common emitter or common base amplifier as shown in figure 1.5. Figure 1.6 shows the IV curves in the safe linear operating region for a common-emitter amplifier. The red dashed line represents the current and voltage conditions that should be met through a full 360 degree cycle to achieve the highest possible output power. For class A operation, we assume that the DC voltage and DC current are chosen to such that the quiescent point in figure 1.6 is at the center of the red dashed line. In this case,  $V_{dc} = \frac{V_{cc} - V_{min}}{2}$ ,  $I_{dc} = \frac{V_{dc}}{R_L}$ , and  $P_{l,dc} = V_{dc}I_{dc} = \frac{(V_{cc} - V_{min})^2}{4R}$ where  $P_{l,dc}$  is the DC power consumed by the load. This same amount of power is also consumed by the transistor, since any current flowing through the resistive load also flows through the collector of the transistor and it sees the same voltage swings from the collector to the emitter, so  $P_{t,dc} = \frac{(V_{cc} - V_{min})^2}{4R}$ . The RMS power supplied to the resistive load is  $P_{ac} = \frac{1}{8}V_{pp}I_{pp} = \frac{(V_{cc}-V_{min})^2}{8R}$ . Therefore in this ideal condition, the efficiency of

the amplifier is  $\eta = \frac{P_{ac}}{P_{l,dc} + P_{t,dc}} = 25\%$ . This is the maximum efficiency limit of a class-A amplifier with a purely resistive load with DC coupling between the amplifier and load [6] [1].

Figure 1.6: Load line for a class-A common emitter amplifier with a purely resistive load

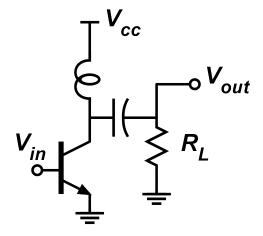

This efficiency value can be improved by AC coupling to the load using a DC blocking capacitor and an inductor as shown in figure 1.7 [1]. This improves the maximum possible efficiency by allowing the DC collector voltage to simply be  $V_{cc}$  and by allowing the maximum AC voltage value to be larger than the supply voltage. In this way, the AC power delivered to the load is effectively doubled and the DC power consumption stays the same. This increases the maximum efficiency to 50%. The 50% limit can also be applied if there is an impedance transformation between the collector and the load resistance.

### 1.8 Mixers

Mixers are frequency conversion elements, and are used in transmitters and receivers to shift the signal information, lying at baseband frequencies, to frequencies surrounding that of the RF carrier [1] [4]. Mixers can be active or passive. A mixer has 3 ports - an RF port, an IF port, and an LO port. In this section I will give a mathematical description of

Figure 1.7: Class-A common emitter amplifier with capacitively coupled load for improved efficiency

mixing in the time domain and the frequency domain and discuss the relative advantages and disadvantages of passive diode mixers and active transistor mixers.

A mixer is a non-linear device that multiplies two signals to produce desired harmonics of the two input signals. To demonstrate this mathematically, I will consider the time-domain case of a received RF signal  $V_{RF}(t) = S(t) \times A \times \cos(\omega_c t)$  mixing with an LO signal  $V_{LO}(t)(t) = \cos(\omega_c t)$  to produce an IF signal which consists of transmitted data lying at the baseband frequency  $V_{IF}(t) = S(t)$ . We will consider an idealized case where the mixer will simply multiply the RF signal by the LO signal in the time domain. The unwanted harmonics will then be filtered out to isolate the desired signal. A useful trigonometric identity to analyze this is  $\cos\theta \times \cos\phi = \frac{1}{2}\cos(\theta - \phi) + \frac{1}{2}\cos(\theta + \phi)$ . Note that this results in two terms, each with an amplitude of 1/2, as the amplitude of the input terms are divided among the two output terms. If we use this to multiply  $V_{RF}(t) \times V_{LO}(t)$ , we get the expression  $\frac{S(t)}{2}(1 + \cos(2\omega_c))$ . At this point, to isolate the baseband-frequency component, a low-pass filter would be used to remove the unwanted harmonic which lies at twice the carrier frequency. If a phase shift were applied, the amplitude of the

baseband-frequency signal would be multiplied by the cosine of the phase offset. If the LO signal were offset 90 degrees from the RF carrier frequency, the resulting baseband component would be 0.

In the frequency domain, an idealized mixer that sees two input signals at frequencies  $f_1$  and  $f_2$  produces an output signal with components at  $|f_1 + f_2|$  and  $|f_1 - f_2|$ , as multiplication in the time domain is the same as convolution in the frequency domain. In any practical circuit, it is impossible to create this perfect idealized mixer. If we use a switching device like a diode or a transistor, the transfer function does not behave as a perfect multiplier - it also has higher-order nonlinearities in the transfer function that will create higher-order harmonics in the output signal. In the frequency domain, an unbalanced diode or transistor mixer will produce harmonics at any frequency satisfying equation 1.16, where for an Lth-order nonlinearity, +/-m+/-n = L [1].

$$f_{spur} = mf_{RF} + nf_{LO} (1.16)$$

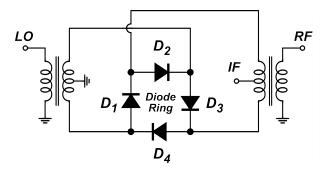

The amplitudes of these tones depend on the amplitudes of the input tones and the coefficients of the higher-order polynomial terms in the transfer function of the mixer. A balanced mixer cofiguration, such as the ring diode mixer in figure 1.8 can be used to eliminate the even-ordered harmonics, although the unwanted odd-ordered harmonics must still be filtered out to isolate the desired output. Passive mixers like this that use diodes as the non-linear mixing element always produce an output signal that has a lower power than the input signals.

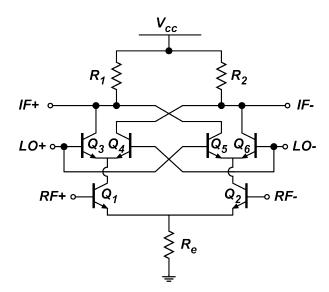

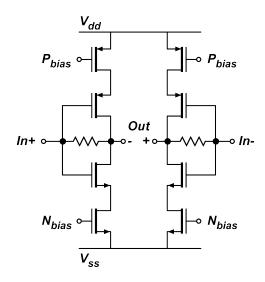

An example of an active mixer is shown in figure 1.8. This gilbert cell mixer uses two cross-coupled differential amplifier stages. The differential RF ports drive a differential common-emitter amplifier with RF transistors Q1 and Q2. The differential LO port provides either a 0 or 180 degree phase shift depending on the sign of the LO signal at

Figure 1.8: Diode ring mixer circuit diagram

a given point in time. An active mixer like this, in contrast to a passive diode mixer, consumes DC power. It also will likely have a much higher noise figure and be more easily overloaded. The key advantage of an active mixer is that it can provide conversion gain, where a passive mixer will always have loss.

Figure 1.9: Gilbert cell circuit diagram

# 1.9 Modulation

Wirelessly transmitted data must have a radio carrier frequency (RF) and a separable set of modulated data. Whether arranged in digital or analog form, raw data is

at frequencies much lower than typical RF carrier frequencies, and therefore cannot be transmitted on its own along an individual frequency channel. It is therefore mixed with RF carrier [4]. Common historical modulation formats include AM (Amplitude Modulation) and FM (Frequency Modulation), both widely used in analog radio transmission. Digital schemes include PSK (phase shift keying) and QAM (Quadrature amplitude modulation) [1] [4].

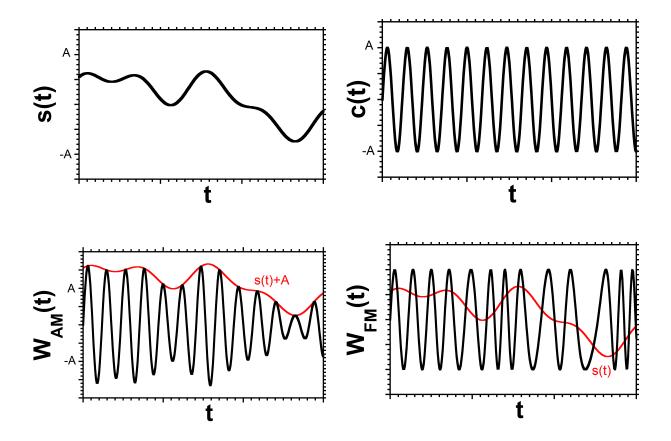

To get a basic understanding of how data can be modulated into an RF signal, let us first briefly look at AM and FM schemes. The goal in this case, is to send auditory data in the form of a bandlimited set of time-dependent sound waves, s(t), within an individual carrier frequency defined by the sinusoidal equation  $c(t) = A\sin(\omega_c t)$  shown in figure 1.10. In the case of an AM scheme, the sound wave s(t) will be encoded in the amplitude of the sinusoidal carrier frequency such that the total transmitted wave is  $W_{AM}(t) = [A + s(t)]\sin(\omega_c t)$ . An FM signal, on the other hand, has a constant amplitude, but has a variable frequency shift determined by the sound wave and a modulation scaling constant that has units of radian per volt. The resulting wave in this case would be  $W_{FM}(t) = A\sin[\omega_c t + Ks(t)]$ . These waveforms can be seen in figure 1.10. The baseband signal s(t) is called the complex baseband representation or complex envelope [4].

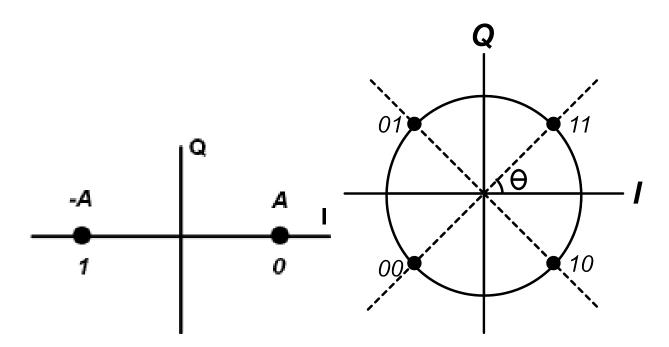

Digital data is generally transmitted as PSK, QPSK, or QAM. Raw bits of data are mapped into symbols using a bit-to-symbol map [4]. This map can be as simple as setting a 0 to one voltage and a 1 to another, or it could involve an incremental phase shift and change in amplitude to represent a longer string of bits. For each symbol period, the phase of the carrier is be adjusted between two values, depending upon the binary data. This is phase shift keying (PSK), and can be done in binary (BPSK) form (single bit per symbol) or quadrature (QPSK) form (2 bits per symbol) [1] [4].

In binary phase shift keying (BPSK), a mixer, driven by the baseband binary data, which provide a +1/-1 modulation, provides either a 0 or 180 degree phase shift depend-

Figure 1.10: Arbitrary sound waveform (top left) mixed with single-frequency sinusoidal carrier waveform (top right) in AM (bottom left) and FM (bottom right) form

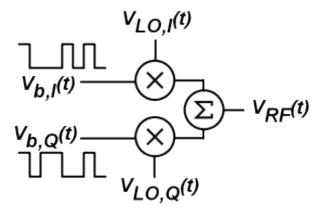

ing on the data input [4]. This results in a gain of A or -A, which can be mapped to the bits 0 and 1 respectively. A block diagram of a QPSK quadrature vector modulator can be seen in figure 1.11. There are two binary bit streams,  $V_{b,I}(t)$  and  $V_{b,Q}(t)$ . Each of these is mixed with a corresponding carrier signal  $V_{LO,I}(t) = V_{LO}\cos(\omega_c t)$  or  $V_{LO,Q}(t) = V_{LO}\sin(\omega_c t)$ . The outputs are added together to create an RF signal of  $V_{RF}(t) = V_{LO}V_{b,I}(t)\cos(\omega_c t) + V_{LO}V_{b,Q}(t)\sin(\omega_c t)$ . Since these two bit streams are modulated into carrier signals that are 90 degrees out of phase from one another, they are orthogonal, and can downconverted and separated into the two original binary bitstreams using a similar IQ downconversion vector modulator. Two bits are therefore encoded into each symbol that is transmitted. An example BPSK and QPSK constellation diagram

Figure 1.11: QPSK upconversion quadrature vector modulator block diagram are shown in figure 1.12 [4].

Figure 1.12: BPSK (left) and QPSK (right) constellation diagrams

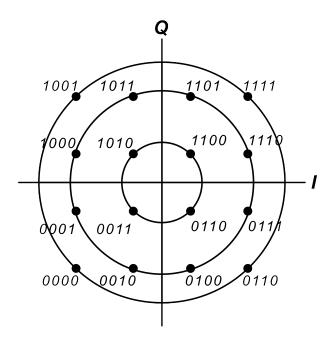

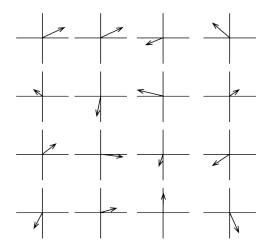

The number of bits in each symbol can be increased, which creates a more complex constellation pattern. One can do this by applying an N-bit digital to analog converter to both the I and the Q signals, mixing the Q signal with a sine wave of the carrier frequency and the I signal with a cosine wave from the carrier frequency, and then adding these

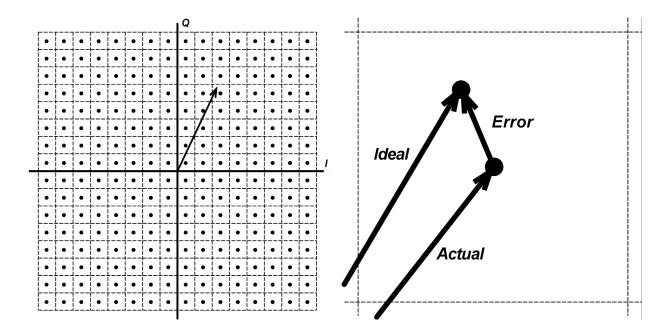

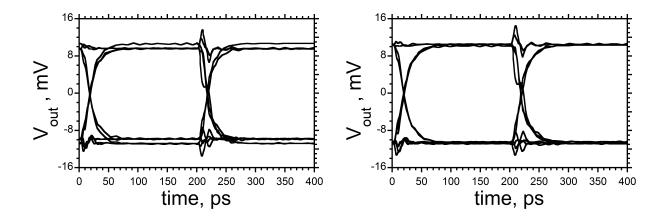

two outputs. Now the RF signal carries two orthogonal data sets (90 degrees out of phase) with variable amplitude. This is quadrature amplitude modulation or QAM. An example constellation diagram of 16QAM (16 possible symbol values or 4 bits per symbol) can be seen in figure 1.13. The drawback is that a larger number of bits per symbol requires a larger amount of received power per bit of information, i.e. a larger SNR. This is reflected in Shannon's expression, as a more complex constellation provides a greater channel capacity in a fixed channel bandwidth. Noise brings in a degree of uncertainty in both the amplitudes of the I and Q components of the signal. These I/Q constellations represent the received signal in the absence of noise or other receiver impairments. The scale of I/Q constellations are usually normalized such that the radius of the signal vector, i.e. the point of the (I,Q) plane, corresponds to the square root of the signal energy received per modulation symbol, or, equivalently, the received signal power multiplied by the duration of the modulation symbol period. The receiver noise then perturbs each received signal, in both the I and Q directions, by a deflection whose variance is kTF.

The receiver SNR is the ratio of the square of the sifnal radius squared, averaged over the constellation, to kTF. Clearly the closer each symbol is to adjacent symbols in I/Q space, the larger the chance of error [1] [4]. They can be more widely spaced, but this requires a greater received signal power. Remember that the Shannon Capacity only defines the upper limit on the data rate of a channel, and the optimum modulation scheme is chosen to get the actual data rate close to the Shannon Capacity. Hardware limitations will ultimately dictate the most efficient choice for modulation scheme.

Within the scope of this dissertation, it is not necessary to fully comprehend how advanced modulation schemes can be chosen to optimize for power consumption and maximizing channel capacity. It is, however, necessary to understand how a phase shift can be applied to a signal by breaking it into an I and Q components and applying a

Figure 1.13: Ideal constellation diagram of 16QAM

variable gain to each of them.

## Chapter 2

## Next-generation Commercial

## Communications Systems

#### 2.1 Introduction

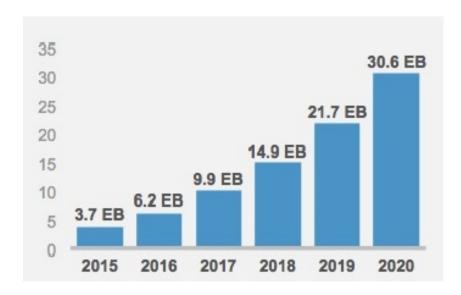

At-the dawn of wireless telegraphy in the late 1800s, our capabilities were limited by technology - diodes, transistors, and even vacuum tubes had not yet been invented. The development of various technologies has since transformed our capacity to instantaneously transfer information over distances from a modern marvel to a universal necessity in the modern world. Wirelessly transmitting a byte of data (8 binary bits), an implausible idea at the time of Samuel Morse, is now much more than an everyday occurrence. It's projected by Cisco that by 2020, roughly 30.6 exabytes ( $30.6 \times 10^{18}$  bytes) will be requested wirelessly through mobile phones and other devices every single month (figure 2.1) [Cisco VNI Mobile 2017]. That is an order of magnitude higher than the 3.7 exabytes requested monthly in 2015. Much of this is attributed to the explosion of mobile high-resolution video streaming. The development of wireless technologies and the consumer demand for them have been feeding off of one another for the past

Figure 2.1: Projected monthly wireless data demands worldwide (exabytes per month)

century. As technologies develop to meet demand, it enables new applications, which increases demand further. Even as cellular service providers prepare to implement the 5th generation of mobile infrastructure (5G), we must anticipate further increasing demand and look at more avenues for wireless data expansion by expanding speed in a given channel and by increasing channel density in a given bandwidth.

As technologies develop and bandwidth demands on commercial infrastructure continues to grow, FCC-allocated frequency bands are rearranged to adapt. Increased demands on speed and network bandwidth have prompted the FCC to open up frequency bands at 27.5-29.5 GHz, 37-40.5 GHz, 47.2 - 50.2 GHz, 50.4-52.6 GHz, and 59.3 - 71 GHz to be used for 5G studies and research [FCC 2015]. As of now, they have not yet committed to specific frequency bands for 5G standard. These frequency bands are not only wider than those that were previously used for mobile systems, but they are also at a notably higher frequency than the 2.4 GHz range that was used for the previous generation. In this section, I will look beyond 5G and examine architectures and the design and characterization of circuit blocks which can be used for future generations of commercial

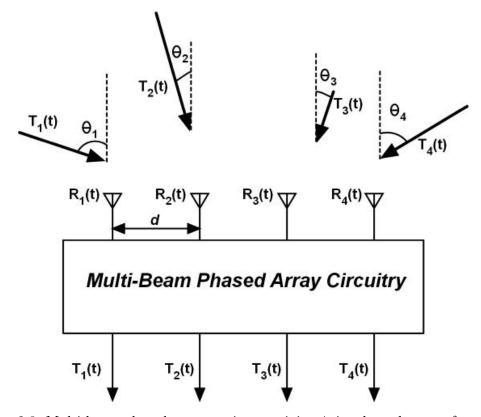

wireless links. The work presented here includes the design and characterization of a low-power scalable multi-channel beamforming matrix which can be used to spatially multiplex multiple channels within a single frequency for high-capacity communications networks.

## 2.2 Frequency Expansion and Performance Tradeoffs

One direction commercial mobile systems can go to increase network capacity is to increase the network bandwidth. Unfortunately, this is limited in several ways. First, the free space path loss of a propagating beam in the absence of atmospheric attenuation is directly proportional to the square of frequency, so if link frequency doubles, the reliable range is reduced to  $\frac{1}{4}$  the distance; given the increased atmospheric attenuation at higher frequencies, the range will become even shorter. Second, it is more difficult to achieve high-performance circuitry at higher frequencies. Power consumption and noise figure will increase and transmitted output power will be reduced. Third, the FCC must allocate frequency bands for many applications with only a finite usable bandwidth, so to open up a broader frequency range for future commercial systems, the wireless industry as a whole must develop high-efficiency, high-performance circuitry to unlock more bandwidth. In this section, I will discuss some of the challenges and tradeoffs involved in designing hardware at higher frequencies.

To generate signals at extremely high frequencies, one method is to generate signals at low frequencies and then to generate the higher frequency signal by harmonic generation using a nonlinear element. This is called frequency multiplication. [15]. The conversion loss for a passive mm-wave multiplier is large, so for most applications, a large amount

of power must be generated at a low frequency before frequency multiplication [15]. An active multiplier can be used which provides gain, but these also have low DC-to-RF efficiency. Producing large AC power at very high frequencies directly is also inefficient [16]. State-of-the-art solid state transistor power amplifiers above 200 GHz can produce an output power on the order of 200 mW, but they do so with power added efficiency below 3% [16].

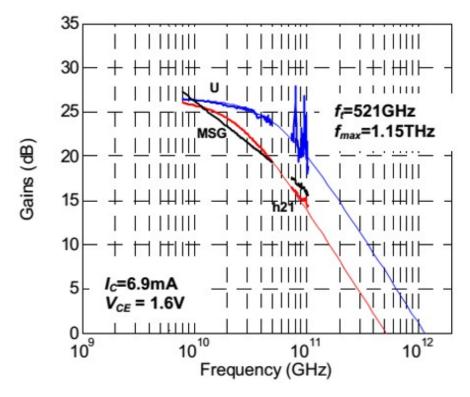

One reason for the poor performance at high frequencies, is that the maximum stable power gain for a single-transistor amplifier is greatly reduced as frequency is increased [5]. For any transistor technology, there is a maximum frequency of unity power gain, called  $f_{max}$ , at which the maximum available power gain and the unilateral power gain are both unity. At frequencies approaching  $f_{max}$ , the transistor available power gain is low, and may not be much greater than the resistive losses associated with the transmission-line impedance-matching networks. Transistor amplifier design at greater than 75% of  $f_{max}$  is therefore difficult. The maximum stable gain and Mason's unilateral gain for a 130 nm InP HBT from Teledyne Scientific Company is shown in figure 2.2 [17].

To make things even more difficult, it is in general not possible to simultaneously optimize a design for high power output and for maximum gain or for minimum noise figure and maximum gain [5]. The load impedance for maximum  $P_{sat}$  and maximum gain are different, and the source impedance for minimum noise figure and maximum gain are different.

In addition to increased atmospheric attenuation and increased free space path loss at high frequencies, the effects of multi-path fading are also increased at higher frequencies, especially when considering mobile phone applications [4]. This occurs when the transmitted wave takes multiple paths to the receiver, potentially bouncing off of multiple stationary or moving objects. If the line-of-sight (LOS) and non-line-of-sight (NLOS) signals arrive at the receiver during the same symbol period, the signals can interfere

Figure 2.2: Maximum stable gain and Mason's unilateral gain vs. frequency for Teledyne's 130 nm InP HBT process

destructively, causing reduced received signal power. If, on the other hand, the LOS and NLOS signals arrive in different signal periods, then the signals between successive periods will interfere. This is called intersymbol interference. At extremely high frequencies, the beams have a small 1st Fresnel zone, so the LOS signal path is readily blocked. As will be explained in the following sections, the spectral efficiency of these high frequency bands can be greatly expanded using line-of-sight point-to-point spatially-multiplexed low-power mm-Wave communications systems for this type of application [18] [19] [20].

#### 2.3 Silicon on Insulator Technology

Companies in the commercial market are aiming to maximize their profits. Therefore, it is important that they are able to produce a massive number of units for as low a price

as possible. Silicon has been scaled aggressively for computing and VLSI applications for decades, so highly scaled silicon technologies are cheaply available for other markets such as wireless. Thanks to nearly 50 years of aggressive transistor scaling for VLSI applications, there is an extremely mature infrastructure for silicon CMOS technologies. The issue is that silicon technology does not feature as large of an  $f_{max}$  as some other material systems, such as InP [13]. Bipolar transistor technologies generally have superior switching speed due to reduced capacitances, so they often are the optimal choice for high-frequency RF applications from a performance standpoint, but are power inefficient for logic and VLSI applications. Bipolar transistor technologies are developed for a smaller volume of customers, and therefore are more expensive for each customer [17].

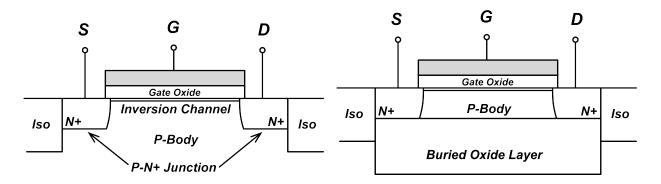

The key driving force for the development of silicon technologies has been digital VLSI applications. Scaling the dimensions of transistors downwards increases the complexity level of the circuits, allows for lower supply voltages (and lower power consumption), and increases the cost efficiency for large-scale production. There is an added benefit that the reduction in  $C_{GS}$  and parasitic access resistances also increases both transistor  $f_T$  and  $f_{max}$  [21]. Unfortunately, the scaling limits of silicon CMOS technology are getting closer as channel lengths/thicknesses approach the dimensions of individual atoms. Furthermore, the performance benefits of scaling for VLSI applications are starting to be overcome by short-channel effects. Therefore, device engineers have come up with technology innovations to marginally extend performance [21]. One of these innovations is called silicon on insulator (SOI) technology. A cross sectional comparison of a classical planar n-type MOSFET is compared to an n-type SOI MOSFET in figure 2.3. This was developed for VLSI technology for multiple reasons, including reduced short-channel effects, higher resistance to latch-up due to improved inter-device isolation, and reduced power supply voltages. This buried oxide layer also benefits wireless/RF applications through reduced drain-bulk and source-bulk capacitances, which allows faster switching speeds [22] [23].

Figure 2.3: Standard FET (left) and SOI FET (right) cross-section

One downside of SOI device technology is the floating body effect. This is the negative consequence of complete isolation between the transistor and the substrate [23]. Since the body of the transistor is isolated from the substrate, holes created by impact ionization under a large electric field in the transistor body tend to move towards the region of lowest potential (the p-type floating body) while the electrons created are quickly swept into the drain. The holes therefore accumulate and build up positive charge. This phenomenon leads to several negative consequences including the kink-effect, potential single-transistor instabilities, negative device conductance and trans-conductance, preventing the transistor from turning off, and premature transistor breakdown [24]. This effect can be avoided by using body-contacted devices for every transistor, but this generally requires larger device widths and potentially increased power consumption depending on the application.

#### 2.4 Phased Arrays and Beamforming

At higher frequencies, free space path loss increases and circuit performance degrades. To overcome these obstacles without drastically increasing power consumption,

Figure 2.4: 6-element Phased antenna array with no relative phase shift

one method is to use more directional antennas. As opposed to omnidirectional antennas, which are optimum for broadcasting applications, directional antennas steer a beam to a particular location, reducing the amount of power wasted by sending it in the wrong direction. For point-to-point communications, this is the optimum solution. The issue for mobile phones, however, is that one cannot predict exactly where they will be as the antenna is constructed, and mechanically steering a directional antenna is not an efficient strategy either. Therefore, one technique that is now expected to be used for the coming 5G cellular network is to use electrically steerable antenna arrays, called phased arrays. This section will outline the utility of phased arrays and how electrically forming a dynamically steerable beam in this way can increase the effective directionality of an antenna without any unwieldy mechanical hardware or apparatus.

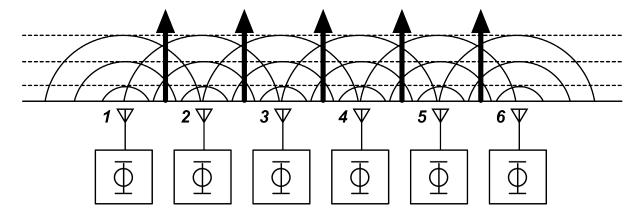

First, see figure 2.4.

First, see figure 2.4. In the figure, there are 6 antenna elements in a linear onedimensional array. Each antenna element has an electronically controlled RF phase-shift,  $\Phi$ . First, consider the case where  $\Phi$  for each antenna element is identical. In this case, every antenna radiates the signal in unison as in figure 2.4. The planes of constant phase (the equiphase fronts) are horizontal along the page, and, effectively, a single beam is formed traveling upwards along the page, or normal to the equiphase front. Much of

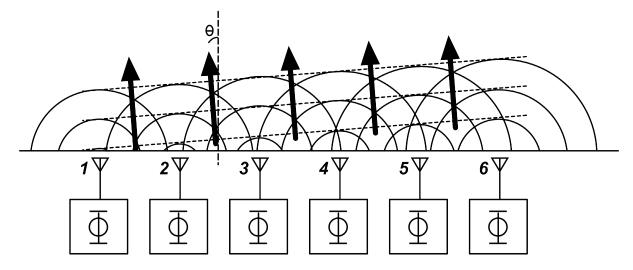

Figure 2.5: 6-element Phased antenna array with relative phase shift

the power that is radiated outwards in unwanted directions is canceled out by varying levels of sinusoidal destructive interference. There is also the added benefit that phased array antennas are bi-directional. In other words, they are equally effective in a receiver as they are in a transmitter, thus doubling their benefit within the Friis transmission equation if used at both ends of the link [7]. By adding a constant increment of phase shift between each adjacent antenna element, the beam can be steered. This technique is called beamforming. If we wanted to transmit or detect a beam at angle  $\Theta$  as shown in the figure, the difference in phase shift needed between each adjacent element,  $\Delta\Phi$ , can be seen in equation 2.1 [25].

$$\Delta \Phi = \frac{2\pi}{\lambda} dsin\Theta \tag{2.1}$$

The maximum directivity of the antenna array is determined by the number of antenna elements, the arrangement of the antennas (linear or planar), and also the directivity of each antenna element. Assuming each antenna element is equally spaced and has the same directivity, the directivity of the array  $D_{array}$  can be expressed as the product of the directivity of each array element, D, and the array factor, AF, which is the number

of elements in the array [25], (equation 2.2) [25].

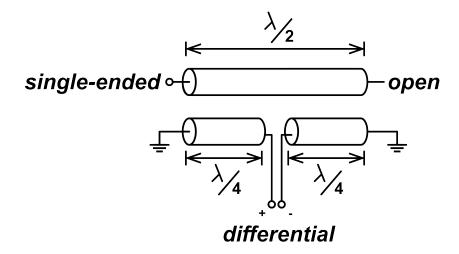

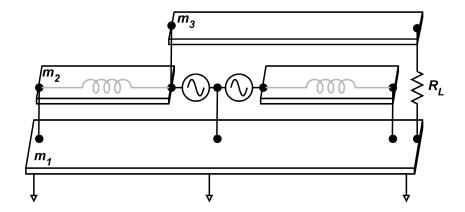

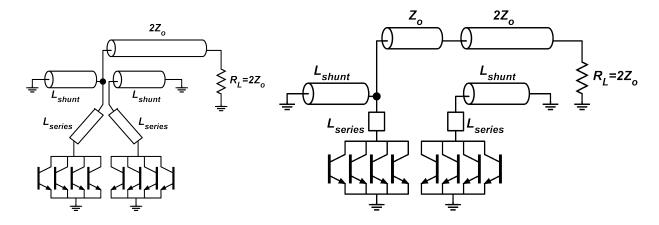

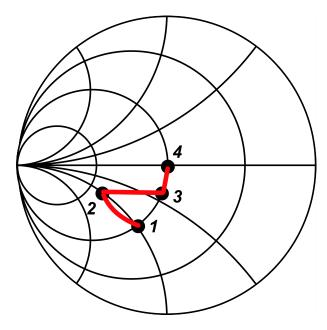

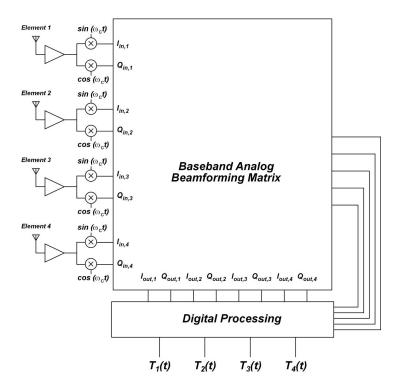

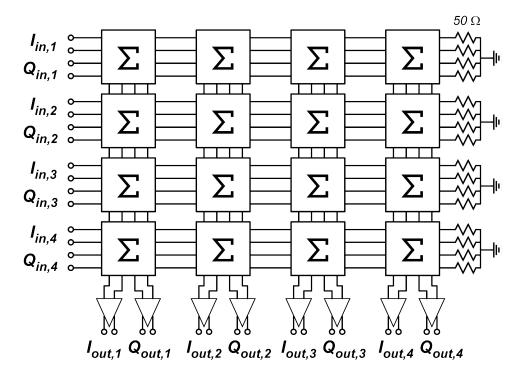

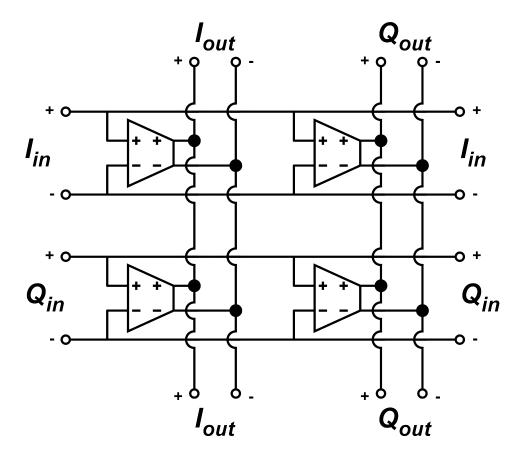

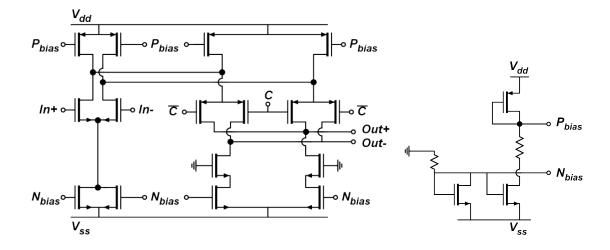

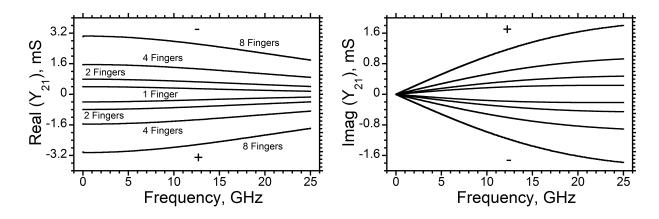

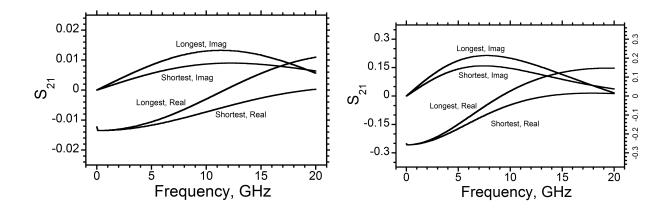

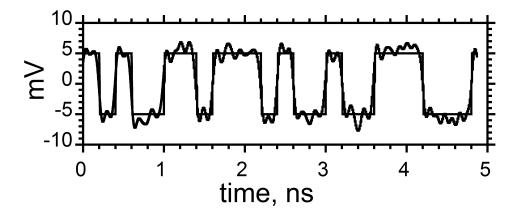

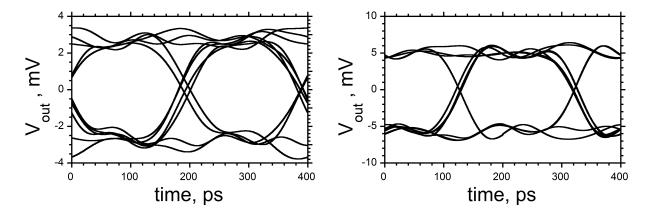

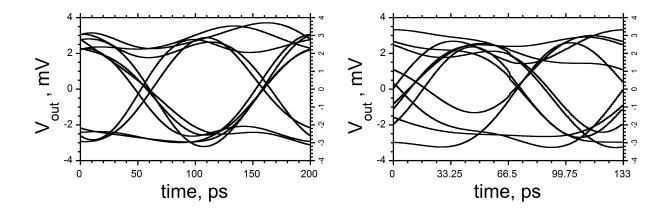

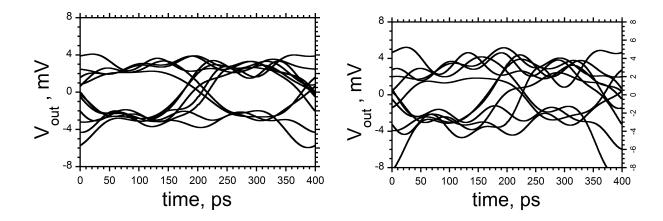

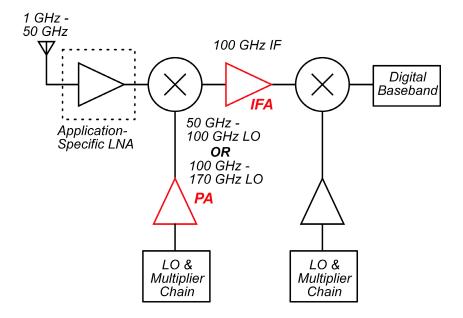

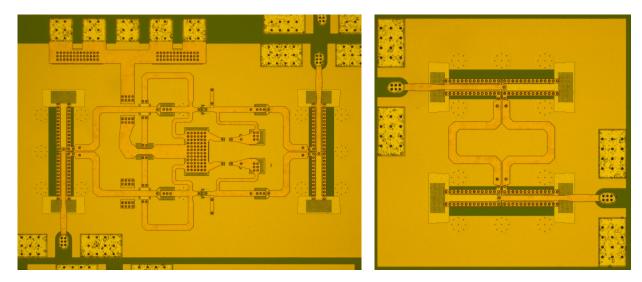

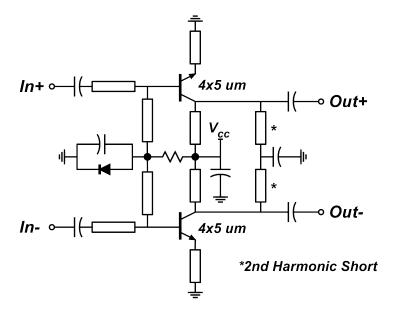

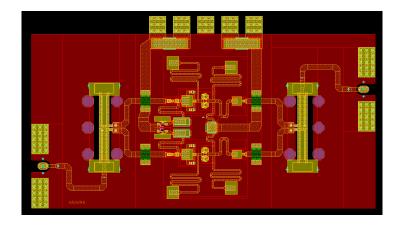

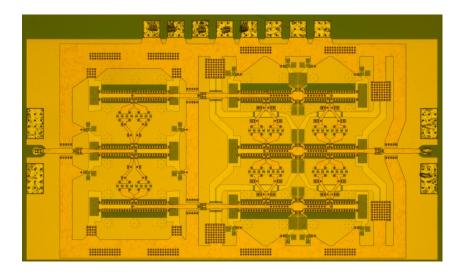

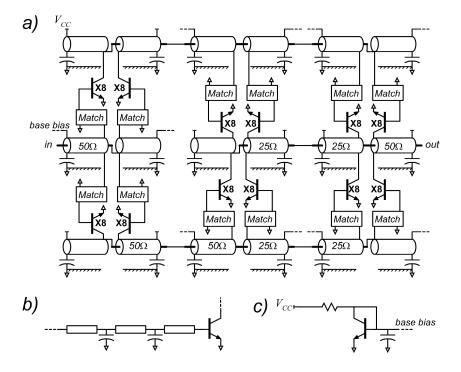

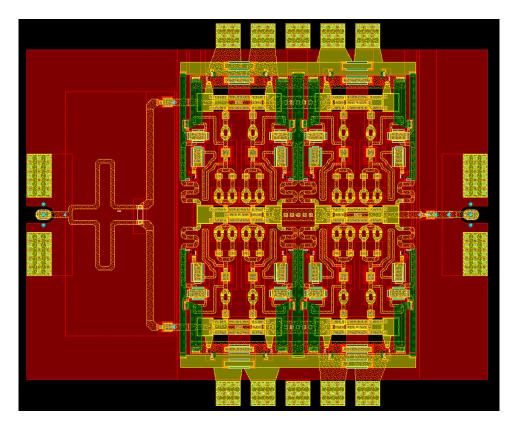

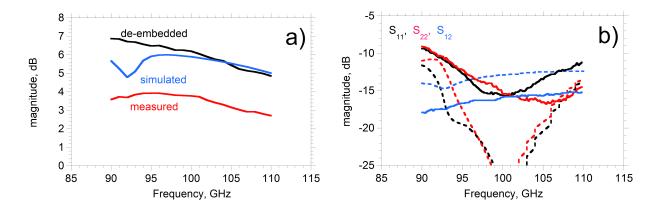

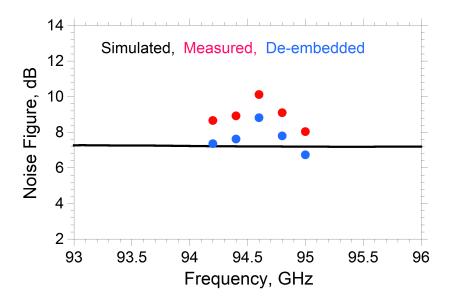

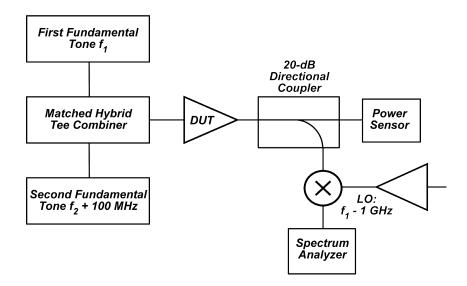

$$D_{array} = AF \cdot D \tag{2.2}$$