### UNIVERSITY of CALIFORNIA Santa Barbara

### Ultra High Speed InGaAs / InP DHBT Devices and Circuits

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

by

Zachary M. Griffith

### Committee in charge:

Professor Mark Rodwell, Chair Professor Umesh Mishra Professor Evelyn Hu Professor Steve Long

September 2005

## Ultra High Speed InGaAs / InP DHBT Devices and Circuits

Copyright 2005

by

Zachary M. Griffith

### Curriculum Vitæ Zachary M. Griffith

### **EDUCATION**

Bachelor of Science in Electrical Engineering

University of California, Santa Barbara, March 2001

Master of Science in Electrical Engineering

University of California, Santa Barbara, December 2001

Doctor of Philosophy in Electrical Engineering

University of California, Santa Barbara, August 2005

### PROFESSIONAL EMPLOYMENT

1999 - 2005 Research assistant, Dept. of Electrical and Computer Engineering, University of California, Santa Barbara 1999, 2000 Summer intern, Conexant Systems Inc., Newbury Park, CA

### FIELDS OF STUDY

Major Field: Design and fabrication of highly scaled, ultra high speed InP based double heterojunction bipolar transistors (DHBTs) and small scale circuits.

### **PUBLICATIONS**

- **Z. Griffith**, Y. Dong, D. Scott, Y. Wei, N. Parthasarathy, M. Dahlström, C. Kadow, V. Paidi, M.J.W. Rodwell, M. Urteaga, R. Pierson, P. Rowell, B. Brar, S. Lee, N. Nguyen, and C. Nguyen, "Transistor and Circuit Design for 100-200 GHz ICs", *IEEE Journal of Solid-State Circuits*, vol. 40, no. 10, 2005.

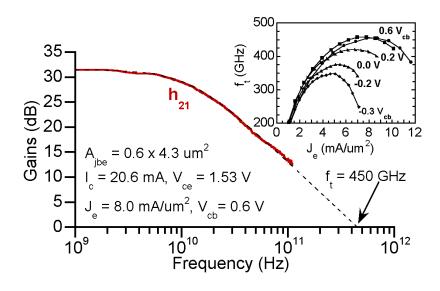

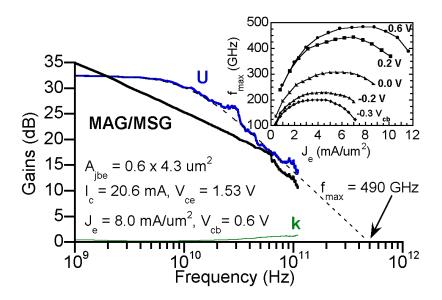

- **Z.** Griffith, M. J. W. Rodwell, X.-M. Fang, D. Loubychev, Y. Wu, J. M. Fastenau, and W. K. Lui, "InGaAs/InP DHBTs with 120 nm collector having simultaneously high  $f_{\tau}$ ,  $f_{max} \geq 450$  GHz", *IEEE Electron Device Letters*, vol. 26, no. 8, pp. 530-532, 2005.

- **Z.** Griffith, M. J. W. Rodwell, X.-M. Fang, D. Loubychev, Y. Wu, J. M. Fastenau, and W. K. Lui, " $In_{0.53}Ga_{0.47}As/InP$  Type-I DHBTs having 450 GHz  $f_{\tau}$  and 490 GHz  $f_{max}$  w/  $C_{cb}/I_c$  = 0.38 ps/V", *Device Research Conference*, Santa Barbara, CA, pp. 265-266, 20-22 June, 2005.

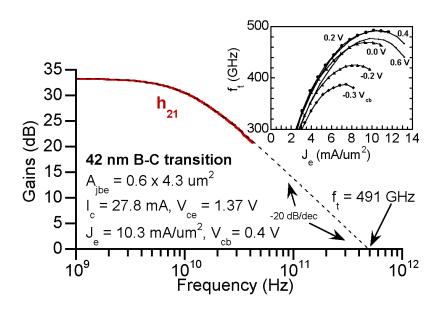

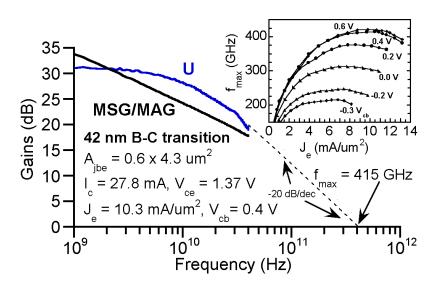

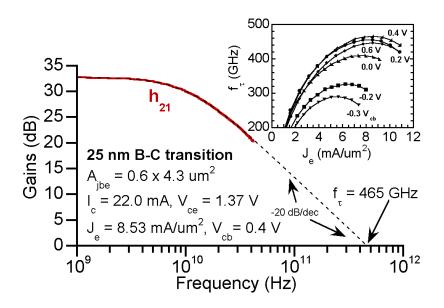

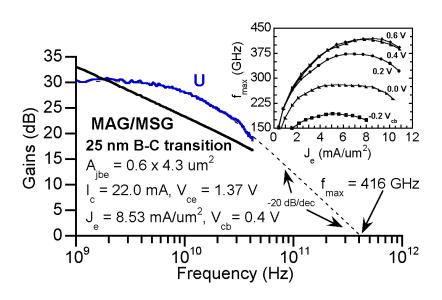

- **Z.** Griffith, M. Dahlström, M. J. W. Rodwell, X.-M. Fang, D. Loubychev, Y. Wu, J. M. Fastenau, and W. K. Lui, "In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP Type-I DHBTs w/ 100 nm Collector and 491 GHz  $f_{\tau}$ , 415 GHz  $f_{max}$ ", *IEEE International Conference on Indium Phosphide and Related Materials*, Glasgow, Scotland, 8-13 May, 2005.

- V. Paidi, **Z. Griffith**, Y. Wei, M. Dahlström, M. Urteaga, N. Parthasarathy, M. Seo, L. Samoska, A. Fung, and M.J.W Rodwell, "G-Band (140-220 GHz) and W-Band (75-110 GHz) InP DHBT Medium Power Amplifiers", *IEEE Transactions on Microwave Theory and Techniques*, vol. 53, no. 2, pp. 598-605, 2005.

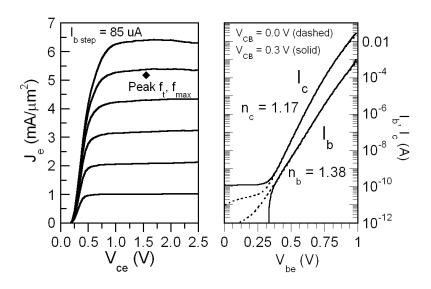

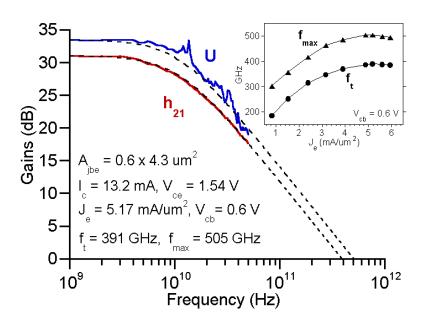

- **Z.** Griffith, M. Dahlström, M. J. W. Rodwell, X.-M. Fang, D. Loubychev, Y. Wu, J. M. Fastenau, and W. K. Lui, "InGaAs/InP DHBTs for Increased Digital IC Bandwidth having a 391 GHz  $f_{\tau}$  and 505 GHz  $f_{max}$ ", *IEEE Electron Device Letters*, vol. 26, no. 1, pp. 11-13, 2005.

- M. Rodwell, **Z. Griffith**, D. Scott, Y. Wei, Y. Dong, V. Paidi, M. Dahlström, N. Parthasarathy, C. Kadow, M. Urteaga, R. Pierson, P. Rowell, B. Brar, S. Lee, N. Nguyen, and C. Nguyen, "Transistor and Circuit Design for 100-200 GHz ICs", *IEEE Compound Semiconductor IC Symposium*, Monterey, CA, 24-27 October, 2004.

- **Z. Griffith**, M. Dahlström, M. J. W. Rodwell, M. Urteaga, R. Pierson, P. Rowell, B. Brar, S. Lee, N. Nguyen, and C. Nguyen, "Ultra High Frequency Static Dividers > 150 GHz in a Narrow Mesa InGaAs/InP DHBT Technology", *IEEE Bipolar/BiCMOS Circuits and Technology Meeting*, Montreal, Canada, pp. 176-179, 13-14 September, 2004.

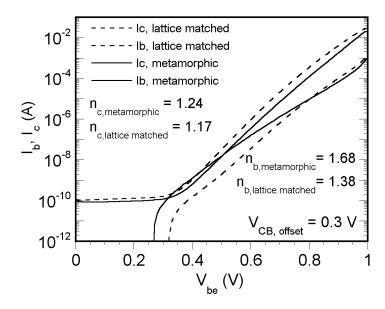

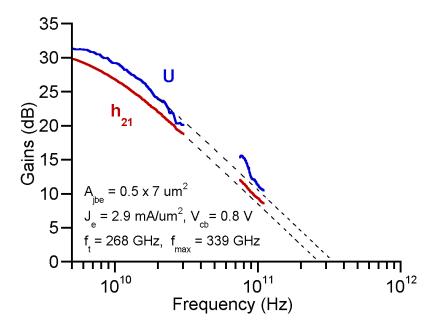

- **Z.** Griffith, Y-M. Kim, M. Dahlström, A. C. Gossard, and M. J. W. Rodwell, "In-GaAs/InP Metamorphic DHBTs Grown on GaAs with Lattice Matched Device Performance and  $f_{\tau}$ ,  $f_{max} > 268$  GHz", *IEEE Electron Device Letters*, vol. 25, no. 9, pp. 675-677, 2004.

- M. Urteaga, P. Rowell, R. Pierson, B. Brar, M. Dahlström, **Z. Griffith**, M. J. W. Rodwell, S. Lee, N. Nguyen, and C. Nguyen, "Deep Submicron InP DHBT Technology with Electroplated Emitter and Base Contacts", *Device Research Conference*, Notre Dame, IN, pp. 239-240, 21-23 June, 2004.

- Y. Dong, **Z. Griffith**, M. Dahlström, and M. J. W. Rodwell, " $C_{CB}$  Reduction in InP Heterojunction Bipolar Transistor with Selectively Implanted Collector Pedestal", *Device Research Conference*, Notre Dame, IN, pp. 67-68, 21-23 June, 2004.

- V. Paidi, **Z. Griffith**, Y. Wei, M. Dahlström, M. Urteaga, M. J. W. Rodwell, A. Fung, and L. Samoska, "Common Base Amplifier with 7 dB Gain at 176 GHz in an InP Mesa DHBT Technology", *IEEE Radio Frequency IC Symposium*, Fort Worth, TX, 6-8 June, pp. 189-192, 2004.

- **Z. Griffith**, M. Dahlström, M. J. W. Rodwell, M. Urteaga, R. Pierson, P. Rowell, B. Brar, S. Lee, N. Nguyen, and C. Nguyen, "Ultra High Frequency Static Dividers in a Narrow Mesa InGaAs/InP DHBT Technology", *IEEE International Conference on Indium Phosphide and Related Materials*, Kagoshima, Japan, 31 May 4 June, pp. 663-666, 2004.

- **Z.** Griffith, Y-M. Kim, M. Dahlström, A. C. Gossard, and M. J. W. Rodwell, "Low Leakage Current Metamorphic InGaAs/InP DHBTs with  $f_{\tau}$  and  $f_{max} > 268$  GHz on a GaAs Substrate", *IEEE International Conference on Indium Phosphide and Related Materials*, Kagoshima, Japan, 31 May 4 June, pp. 750-752, 2004.

- M. Dahlström, **Z. Griffith**, Y-M. Kim, and M. J. W. Rodwell, "High Current Density and High Power Density Operation of Ultra High Speed InP DHBTs", *IEEE International Conference on Indium Phosphide and Related Materials*, Kagoshima, Japan, 31 May 4 June, pp. 761-764, 2004.

- **Z.** Griffith, M. Dahlström, M. Urteaga, M. J. W. Rodwell, X.-M. Fang, D. Loubychev, Y. Wu, J. M. Fastenau, and W. K. Lui, "InGaAs/InP Mesa DHBTs with Simultaneously High  $f_{\tau}$  and  $f_{max}$  and Low  $C_{cb}/I_c$  Ratio", *IEEE Electron Device Letters*, vol. 25, no. 5, pp. 250-252, 2004.

- I. Harrison, M. Dahlström, S. Krishnan, **Z. Griffith**, Y-M. Kim, and M. J. W. Rodwell, "Thermal Limitations of InP HBTs in 80- and 160-Gb ICs", *IEEE Transactions on Electron Devices*, vol. 51, no. 4, pp. 529-534, 2004.

- Y-M. Kim, **Z.** Griffith, M. J. W. Rodwell, and A. C. Gossard, "High Bandwidth and Low-Leakage Current InP/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP DHBTs on GaAs Substrates", *IEEE Electron Device Letters*, vol. 25, no. 4, pp. 170-172, 2004.

- M. Urteaga, D. Scott, S. Krishnan, Y. Wei, M. Dahlström, **Z. Griffith**, N. Parthasarathy, and M. J. W. Rodwell, "G-band (140-220 GHz) InP-based HBT Amplifiers", *IEEE Journal of Solid-State Circuits*, vol. 38, no. 9, pp. 1451-1456, 2003.

- S. Krishnan, D. Scott, **Z. Griffith**, M. Urteaga, Y. Wei, N. Parthasarathy, and M. J. W. Rodwell, "An 8-GHz Continuous Time  $\delta$   $\sigma$  Analog-Digital Converter in an InP-based HBT Technology", *IEEE Transactions on Microwave Theory and Techniques*, vol. 51, no. 12, pp. 2555-2561, 2003.

- M. Dahlström, **Z. Griffith**, M. Urteaga, M. J. W. Rodwell, X.-M. Fang, D. Loubychev, Y. Wu, J. M. Fastenau, and W. K. Lui, "InGaAs/InP DHBTs with > 370 GHz  $f_{\tau}$  and  $f_{max}$  Using a Graded Carbon-Doped Base", *Device Research Conference*, Salt Lake City, UT, 23-25 June, Late news, 2003.

- Y. Wei, M. Urteaga, **Z. Griffith**, D. Scott, S. Xie, V. Paidi, N. Parthasarathy, and M. J. W. Rodwell, "75 GHz 80 mW InP DHBT Power Amplifier", *IEEE MTT-S International Microwave Symposium Digest*, vol. 2, 8-13 June, pp. 919-921, 2003.

- S. Krishnan, **Z. Griffith**, M. Urteaga, Y. Wei, D. Scott, M. Dahlström, N. Parthasarathy, and M. J. W. Rodwell, "87 GHz Static Frequency Divider in an InP-based Mesa DHBT Technology", *IEEE Gallium Arsenide Integrated Circuit Symposium*, Monterey, CA, 20-23 October, pp. 294-296, 2002.

### **Abstract**

## Ultra High Speed InGaAs / InP DHBT Devices and Circuits

by

### Zachary M. Griffith

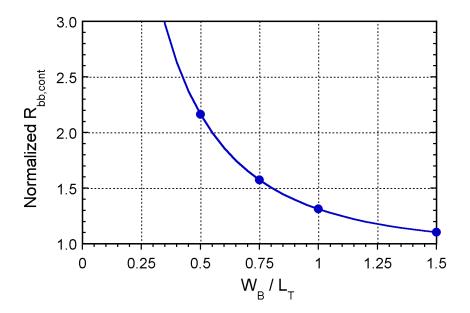

This work examines the efforts pursued through vertical and lateral scaling to increase the bandwidth of InP based DHBTs. Through process development, device performance has improved from lateral scaling and reduced contact resistances. A high-yield 0.5  $\mu$ m narrow mesa emitter junction technology has been realized. The contact resistivity  $\rho_c$  for the emitter, base, and collector layers has been reduced to less than  $10~\Omega \cdot \mu \text{m}^2$ , a 2:1 improvement. With this base-contact  $\rho_c$  and a typical base sheet  $\rho_s \cong 600~\Omega/\Box$ , the metal-semiconductor transfer length  $L_t$  has been reduced to 120 nm, and 0.3  $\mu$ m base contacts have been realized. This has substantially reduced the extrinsic  $C_{cb}$  with minimal increase to the base resistance  $R_{bb}$ .

The reductions to the extrinsic capacitive and resistive parasitics allow the active collector thickness  $T_c$  to be thinned for increased device bandwidth. To achieve minimum  $C_{cb}/I_c$  ratio as  $T_c$  is reduced, the maximum current density will increase  $J_e = J_{Kirk} \propto T_c^{-2}$ . The power density will similarly increase  $P = I_c \cdot V_{ce} = J_e A_e \cdot V_{ce}$ . Improved device heat-sinking to the high thermally-conductive InP substrate for reduced HBT thermal resistance  $\theta_{JA}$  (K· $\mu$ m²/mW) must be considered during HBT

design to prevent excessive device self-heating as the operating power density increases. For the device improvements discussed, the follow results have ensued from each collector scaling generation:

$$T_c$$

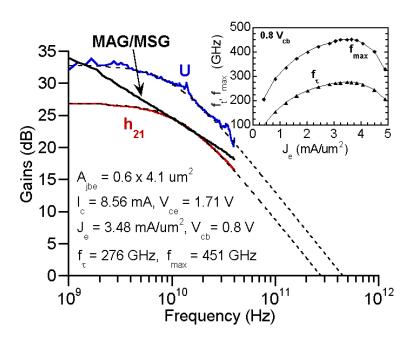

= 210 nm  $\to f_\tau/f_{max}$  = 276/451 GHz,  $T_c$  = 150 nm  $\to f_\tau/f_{max}$  = 391/505 GHz,  $T_c$  = 120 nm  $\to f_\tau/f_{max}$  = 450/490 GHz,  $T_c$  = 100 nm  $\to f_\tau/f_{max}$  = 491/415 GHz.

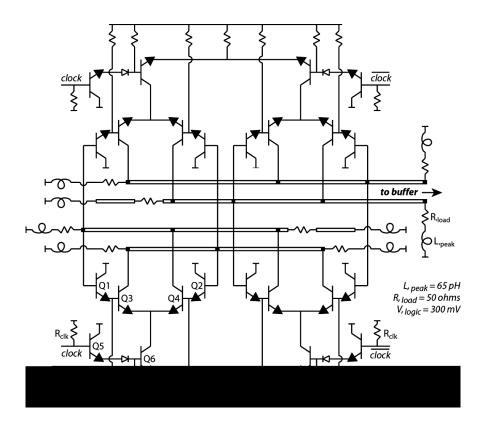

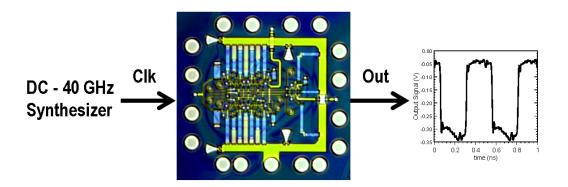

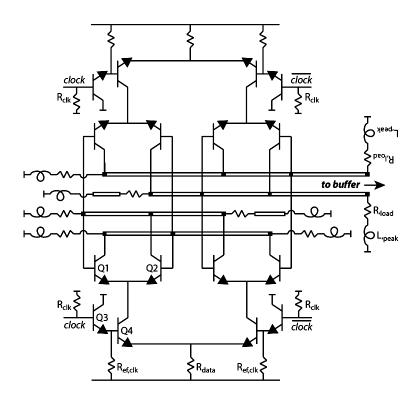

Static frequency dividers were designed and fabricated utilizing an HBT with a collector thickness of 150 nm. The amount of  $\Delta V_{logic}$  consumed by the parasitic emitter resistance was the scaling limit for these circuits. A dense wiring scheme is utilized to reduce interconnect delays, and the signal integrity was maintained through the use of a low- $\varepsilon_r$ , thin-film microstrip environment. Divide-by-2 designs fabricated at GCS and UCSB had a maximum toggle rate of  $f_{clk,max}$  = 153 GHz and 142 GHz, respectively.

## Contents

| Li | st of I | igures             |                                                             | xiii |

|----|---------|--------------------|-------------------------------------------------------------|------|

| Li | st of T | <b>Sables</b>      |                                                             | xvii |

| 1  |         | oduction<br>rences | on<br>                                                      | . 5  |

| 2  | InP     | DHBT               | Theory and Design                                           | 7    |

|    | 2.1     |                    | HBT structure                                               | . 8  |

|    | 2.2     |                    | carrier transit times                                       |      |

|    | 2.3     | Collec             | etor design and maximum current density                     | . 13 |

|    |         | 2.3.1              | Correction to account for UCSB base-collector grade         | . 15 |

|    | 2.4     | HBT r              | resistance and capacitance                                  | . 19 |

|    |         | 2.4.1              | Base-collector depletion capacitance, $C_{cb}$              | . 19 |

|    |         | 2.4.2              | Base resistance                                             | . 19 |

|    |         | 2.4.3              | Sub-collector resistance                                    | . 23 |

|    |         | 2.4.4              | Emitter resistance                                          |      |

|    | 2.5     |                    | stor figures of merit                                       |      |

|    | 2.6     | Device             | e modeling                                                  |      |

|    |         | 2.6.1              | Small-signal equivalent circuit modeling                    |      |

|    |         | 2.6.2              | Large-signal HBT modeling                                   |      |

|    | 2.7     | HBT o              | lelays within digital ICs                                   | . 35 |

|    | 2.8     | HBT s              | scaling principles                                          | . 41 |

|    | 2.9     |                    | scaling limits and solutions                                |      |

|    |         | 2.9.1              | Collector pedestal implant – reduced $C_{cb}$               |      |

|    |         | 2.9.2              | Emitter junction regrowth                                   |      |

|    |         |                    | scaling efforts in this work                                |      |

|    | Refe    | rences             |                                                             | . 54 |

| 3  | нвт     | scalin             | g and process improvements                                  | 56   |

|    | 3.1     | Impro              | ved metal-semiconductor contact deposition                  | . 59 |

|    |         | 3.1.1              | Indium rich InGaAs contact layers                           | . 59 |

|    |         | 3.1.2              | Surface preparation before metal deposition                 |      |

|    |         | 3.1.3              | Thin interfacial Pd layer to the P <sup>+</sup> InGaAs base | 61   |

|    | 3.2     | Advan              | ice lithographic scaling, device formation                  | . 64 |

|   |       | 3.2.1    | Emitter lithography and scaling                              |

|---|-------|----------|--------------------------------------------------------------|

|   |       | 3.2.2    | Base lithography and scaling                                 |

|   | 3.3   | Old de   | vice passivation and interconnect process 69                 |

|   |       | 3.3.1    | Polyimide passivation                                        |

|   |       | 3.3.2    | Interconnect step coverage                                   |

|   | 3.4   | New d    | evice passivation and interconnect process                   |

|   |       | 3.4.1    | Interconnect posts for a planar wiring environment 76        |

|   |       | 3.4.2    | Metal adhesion to the spin-on dielectric surface             |

|   |       | 3.4.3    | BCB passivation                                              |

|   | 3.5   |          | Im microstrip for mesa HBTs                                  |

|   | 3.6   | Proces   | s challenges for UCSB metamorphic DHBTs 89                   |

|   |       | 3.6.1    | Difficulties etching the emitter mesa                        |

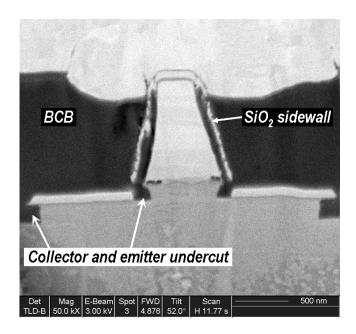

|   |       | 3.6.2    | SiO <sub>2</sub> dielectric sidewall solution                |

|   | 3.7   | Summ     | ary                                                          |

|   | Refe  | rences.  | 97                                                           |

|   | . D   | DIIDE    |                                                              |

| 4 |       |          | Device Results 99                                            |

|   | 4.1   |          | ralibration methods                                          |

|   | 4.2   |          | n collector, 30 nm base – DHBT 19b                           |

|   | 4.3   |          | n collector, 30 nm base – DHBT 22                            |

|   | 4.4   |          | n collector, 35 nm base – DHBT 24                            |

|   | 4.5   |          | n collector, 30 nm base – DHBT 25 and 26                     |

|   | 1.6   | 4.5.1    |                                                              |

|   | 4.6   |          | n collector, 30 nm base – DHBT 27                            |

|   | 4.7   |          | orphic DHBTs                                                 |

|   | Refe  | rences.  |                                                              |

| 5 | Stati | ic frequ | ency divider results 153                                     |

| , | 5.1   |          | divider testing and measurement equipment                    |

|   | 5.2   |          | nanufactured dividers                                        |

|   | 5.2   |          | First wafer lots, October 2003–excessively high $C_{cb}$ 159 |

|   |       | 5.2.1    | Good wafer lots, February 2004–150 GHz dividers 163          |

|   | 5.3   | J.Z.Z    | nta Barbara manufactured dividers                            |

|   | 5.4   |          | rell Scientific manufactured dividers                        |

|   |       |          |                                                              |

|   | KCIC  | rences.  |                                                              |

| 6 | Con   | clusions | 176                                                          |

|   | 6.1   | Accom    | iplishments                                                  |

|   |       | 6.1.1    | Process development                                          |

|   |       | 6.1.2    | HBT results                                                  |

|   |       |          |                                                              |

| В | InP  | mesa H                                 | BT / Circuit Process Flow             |  |  |  |   |  |  |   |     | 190 |

|---|------|----------------------------------------|---------------------------------------|--|--|--|---|--|--|---|-----|-----|

|   | Refe | erences.                               |                                       |  |  |  | • |  |  | • | •   | 189 |

| A | Met  | Metal-semiconductor contact resistance |                                       |  |  |  |   |  |  |   | 186 |     |

|   | Refe | erences.                               |                                       |  |  |  | • |  |  | • |     | 185 |

|   |      | 6.2.2                                  | Ultra low power CML static dividers   |  |  |  |   |  |  |   |     | 183 |

|   |      | 6.2.1                                  | 150 GHz CML static frequency dividers |  |  |  |   |  |  |   |     | 181 |

|   | 6.2  | Future                                 | work                                  |  |  |  |   |  |  |   |     | 180 |

|   |      | 6.1.3                                  | 150 GHz ECL static frequency dividers |  |  |  |   |  |  |   |     | 178 |

## List of Figures

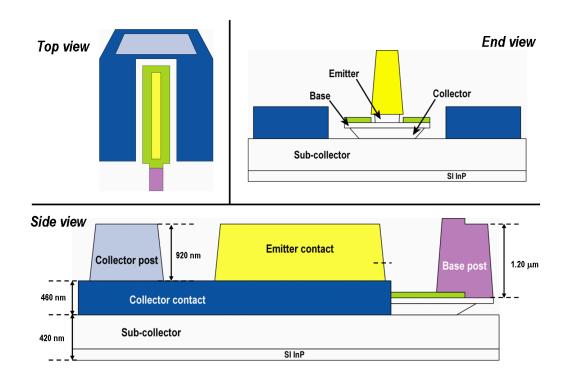

| 2.1  | Mesa HBT structure w/ self-aligned base contact                                                     | 8  |

|------|-----------------------------------------------------------------------------------------------------|----|

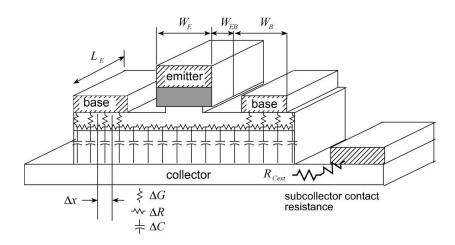

| 2.2  | Mesa HBT showing distributed device resistances and capacitances                                    | 9  |

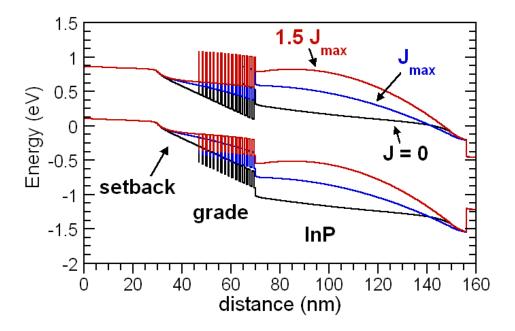

| 2.3  | Variation of band diagram at $V_{cb} = 0$ , $J = 0$ , $J_{max}$ , and 1.5 $J_{max}$                 | 18 |

| 2.4  | Non-pinched TLM structure – the base semiconductor is exposed                                       | 21 |

| 2.5  | Pinched TLM structure – the emitter resides atop the base semicon-                                  |    |

|      | ductor                                                                                              | 21 |

| 2.6  | Measured TLMs – Pinched and Non-pinched for DHBT 27                                                 | 22 |

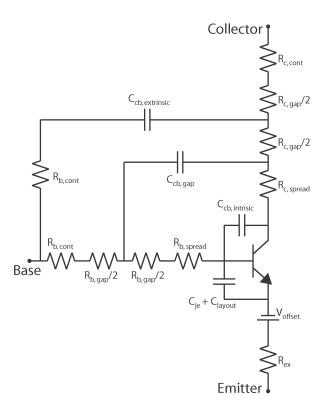

| 2.7  | Hybrid-pi equivalent circuit HBT model                                                              | 27 |

| 2.8  | Measured (solid line) and simulated S-parameters (data points) of                                   |    |

|      | the HBT and hybrid- $\pi$ equivalent circuit                                                        | 30 |

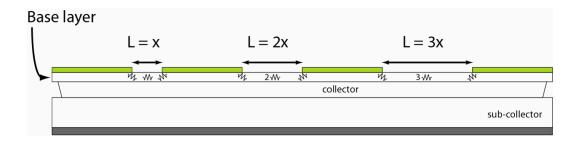

| 2.9  | Distributed parasitics of mathematical device model                                                 | 32 |

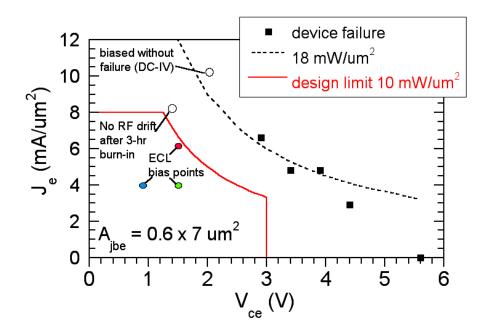

| 2.10 | InP DHBT safe operating area plot – 150 nm collector, 30 nm base.                                   | 34 |

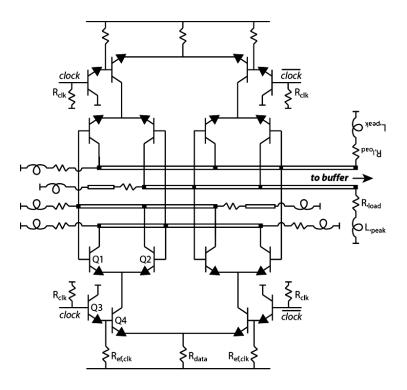

| 2.11 | Schematic of CML static frequency divider                                                           | 36 |

| 2.12 | Delay path and capacitors charged during clock transition                                           | 37 |

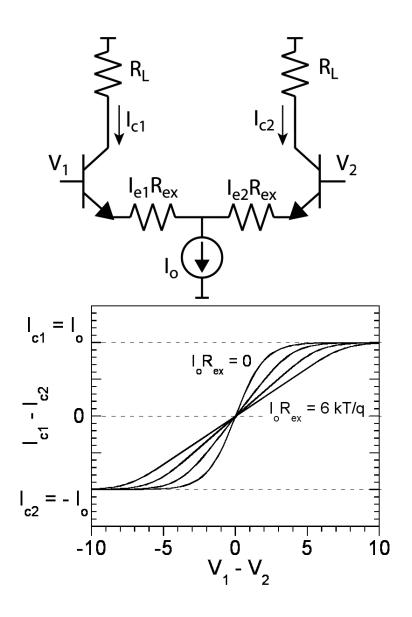

| 2.13 | Current flow of a differential pair in the presence of emitter resis-                               |    |

|      | tance – $I_oR_{ex} = 0, 2kT/q, 4kT/q$ , and $6kT/q$ . $V_1 - V_2$ is normalized                     |    |

|      | to $kT/q$                                                                                           | 40 |

| 2.14 | Variance of the contact resistance (normalized to $\frac{\sqrt{\rho_c \rho_c}}{2L_c}$ ) as the base |    |

|      | contact is scaled                                                                                   | 49 |

| 2.15 | Pedestal process schematic                                                                          | 50 |

| 2.16 | Regrown-emitter process schematic                                                                   | 52 |

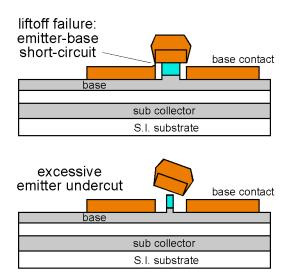

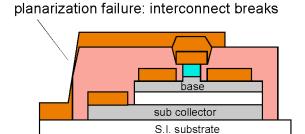

| 3.1  | Failure mechanisms that limit yield for mesa HBTs                                                   | 58 |

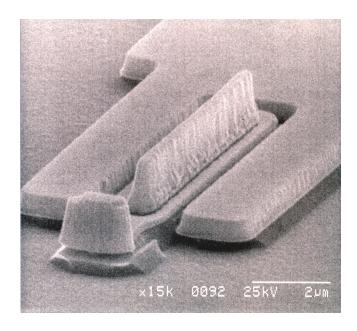

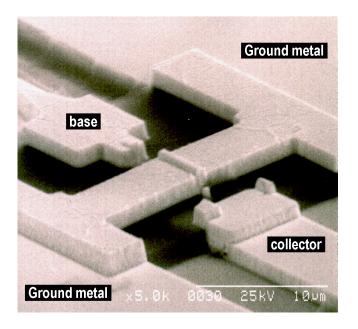

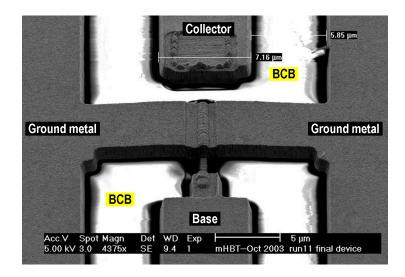

| 3.2  | Angled SEM of an HBT before passivation                                                             | 68 |

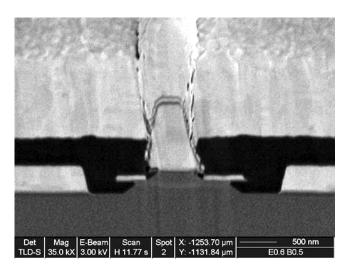

| 3.3  | Cross-sectional SEM of an HBT after passivation and interconnect                                    | 00 |

| 0.0  | metal                                                                                               | 68 |

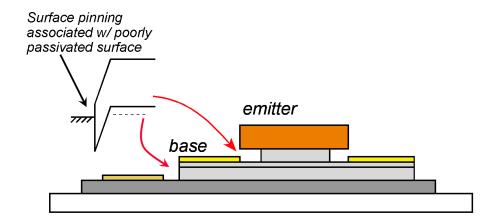

| 3.4  | Device cross-section showing leakage paths for poorly passivated                                    | 00 |

|      | surfaces                                                                                            | 70 |

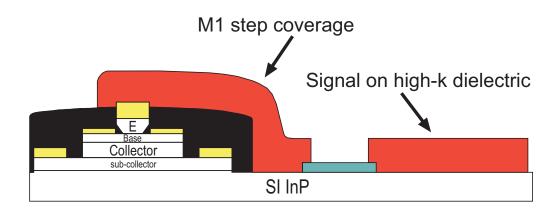

| 3.5  | Old HBT process after passivation and Metal-1 interconnect                                          | 72 |

| 3.6  | Old device interconnect scheme showing tall Metal-1 step-coverage                                   | 73 |

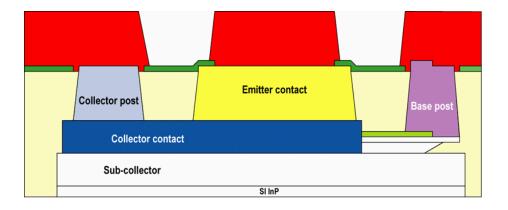

| 3.7  | Updated HBT cross-section after passivation and Metal-1 interconnect                                | 75 |

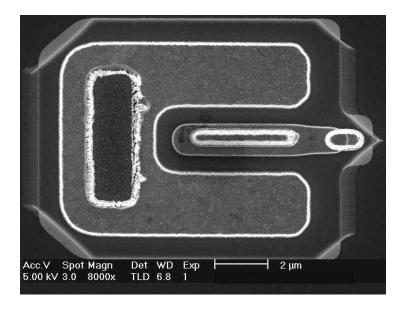

| 3.8  | SEM, top view – 0.6 $\mu$ m emitter width, 1.3 $\mu$ m collector mesa width                         | 77 |

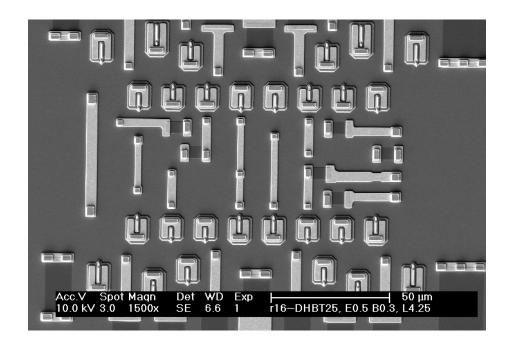

| 3.9  | SEM of divider core before device passivation and metal interconnects                               | 78 |

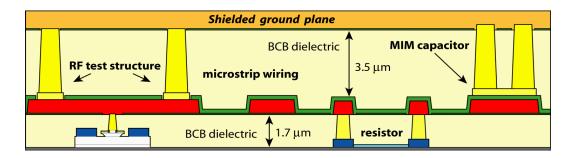

| 3.10 | Planar device interconnect scheme: metal interconnect on 1.7 $\mu$ m of               |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | BCB above InP substrate                                                               | 81  |

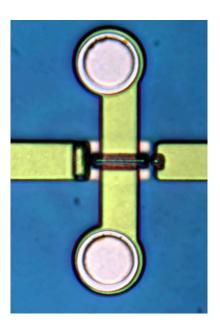

| 3.11 | IC micrograph photo of device within test structure after passivation                 | 81  |

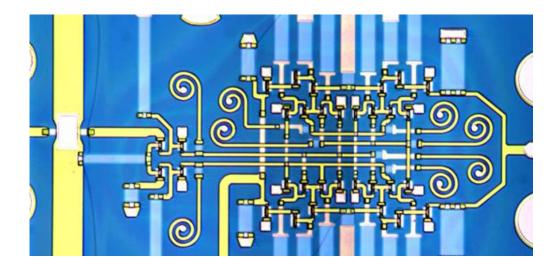

|      | IC micrograph photo of a static frequency divider interconnect bus                    |     |

|      | after Metal-1 interconnect                                                            | 82  |

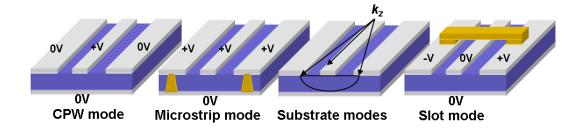

| 3.13 | Coplanar wiring environment – showing the CPW and parasitic modes                     | 83  |

|      | Cross-section of the mesa HBT process, showing its thin-film mi-                      |     |

|      | crostrip wiring environment                                                           | 86  |

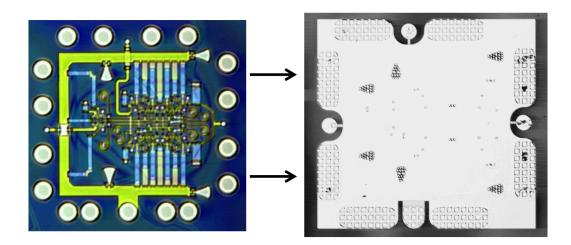

| 3.15 | Fabricated divide-by-2 before and after final ground-plane metalization               | 87  |

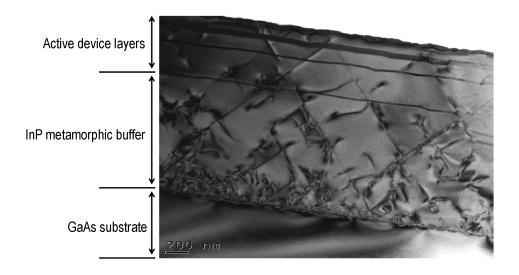

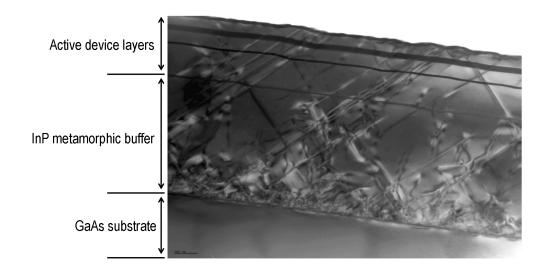

|      | Observed InP metamorphic buffer defects from epitaxy growth                           | 90  |

|      | Observed InP metamorphic buffer defects–different location                            | 90  |

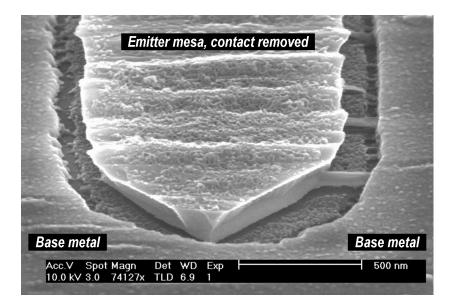

|      | Inspection of emitter mesa after wet-etching. Note, the emitter con-                  |     |

|      | tact has been removed                                                                 | 93  |

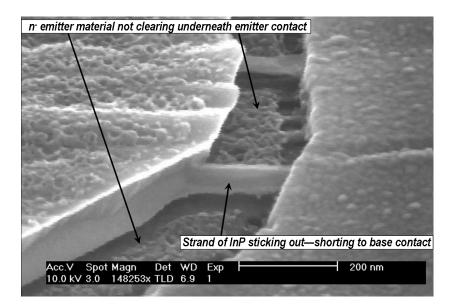

| 3.19 | Inspection of the $N^-$ semiconductor between the etched emitter mesa                 |     |

|      | and self-aligned base contact                                                         | 94  |

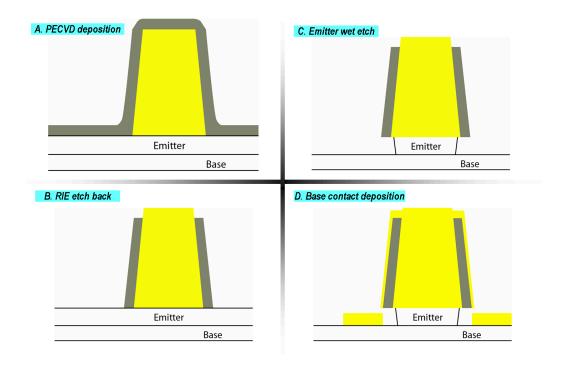

| 3.20 | Process flow for emitter dielectric sidewall spacer                                   | 95  |

|      | Cross-sectional SEM of an mHBT after passivation and device in-                       |     |

|      | terconnect                                                                            | 96  |

|      |                                                                                       |     |

| 4.1  | 00 7 00                                                                               | .08 |

| 4.2  | ,                                                                                     | 10  |

| 4.3  | E , , , , , , , , , , , , , , , , , , ,                                               | 11  |

| 4.4  |                                                                                       | 12  |

| 4.5  | •                                                                                     | 14  |

| 4.6  | <i>y</i> , , <i>y</i> , , , , , , , , , , , , , , , , , , ,                           | 15  |

| 4.7  | , , , , , , , , , , , , , , , , , , ,                                                 | 16  |

| 4.8  | 00 , 60                                                                               | 20  |

| 4.9  | ,                                                                                     | 20  |

| 4.10 | 0 0                                                                                   | 21  |

| 4.11 | J 17 9 110000                                                                         | 22  |

|      |                                                                                       | 26  |

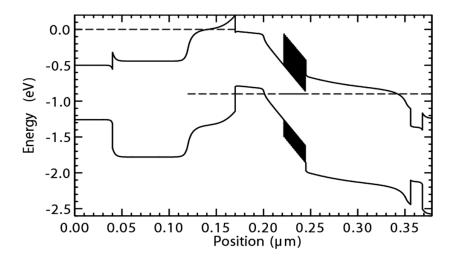

| 4.13 | Simulated band-structure DHBT $26 - V_{be} = 0.9 \text{ V}, V_{cb} = 0.0 \text{ V}$ 1 | 26  |

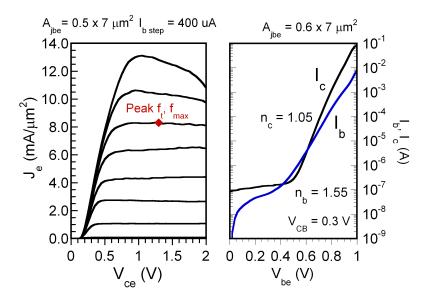

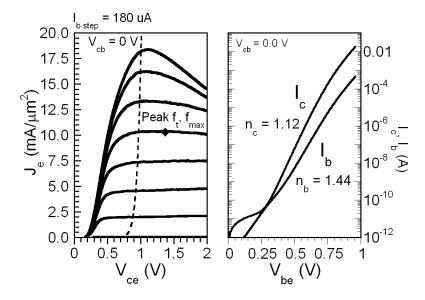

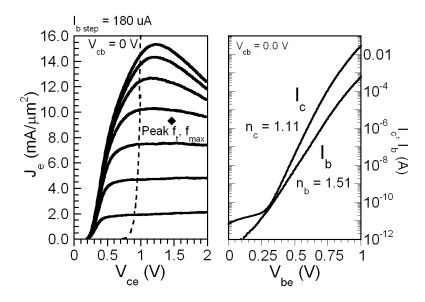

| 4.14 | Common-emitter I-V and Gummel characteristics, DHBT 25 1                              | 27  |

| 4.15 | Common-emitter I-V and Gummel characteristics, DHBT 26 1                              | 28  |

|      | £ , , , , , , , , , , , , , , , , , , ,                                               | 29  |

|      | · · · · · · · · · · · · · · · · · · ·                                                 | 29  |

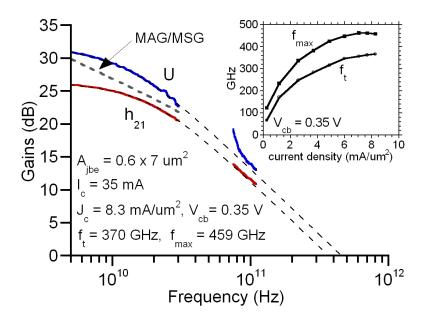

|      | Measured microwave gains, DHBT 26 – Peak $f_{\tau}$                                   |     |

| 4.19 | Measured microwave gains, DHBT 26 – Peak $f_{max}$                                    | 30  |

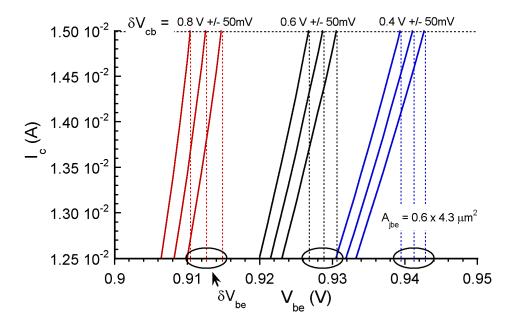

| 4.20 | Change in $V_{be}$ associated with differences in operating temperature                                  |            |

|------|----------------------------------------------------------------------------------------------------------|------------|

|      | for changes in $V_{ce}$ ( $\delta V_{ce} = \delta V_{be} + \delta V_{cb}$ ), keeping $I_c$ constant. The |            |

|      | Gummel measurement technique is used to acquire device thermal                                           |            |

|      | data                                                                                                     | 132        |

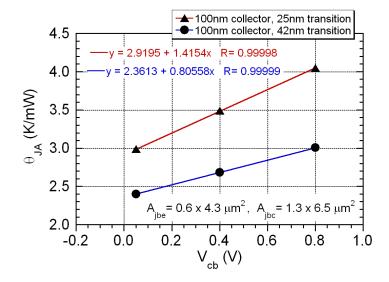

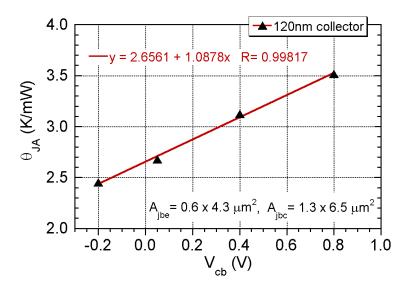

| 4.21 | Variance of thermal resistance $\theta_{JA}$ with changing collector potential                           |            |

|      | $V_{cb}$                                                                                                 | 133        |

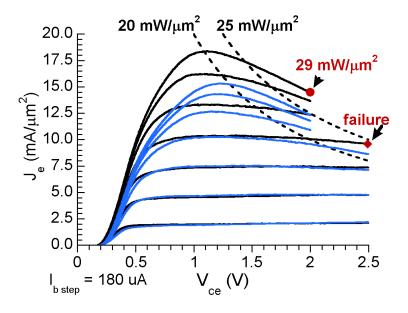

| 4.22 | High-power density common-emitter curves – 42 nm transition (DHBT                                        | 25)        |

|      |                                                                                                          | 135        |

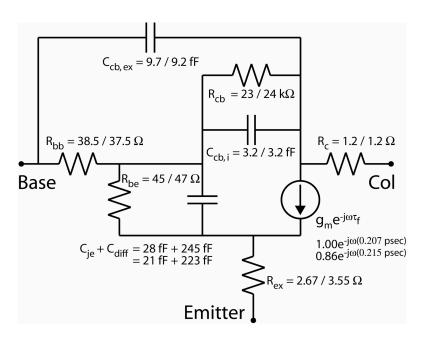

| 4.23 | Hybrid- $\pi$ models, 100 collector, 42 / 25 nm transitions – Peak $f_{\tau}$ , $f_{max}$                | 135        |

|      | Comparison of $C_{cb}$ vs $J_e$ and $V_{cb}$ for both 100 nm collector devices—                          |            |

|      | 42 nm transition (DHBT 25) filled, 25 nm transition (DHBT 26)                                            |            |

|      | hollow                                                                                                   | 136        |

| 4.25 | Simulated band-structure DHBT 27 – $V_{be} = 0.9 \text{ V}$ , $V_{cb} = 0.0 \text{ V}$                   | 138        |

|      |                                                                                                          | 139        |

|      |                                                                                                          | 140        |

| 4.28 | Variance of thermal resistance $\theta_{JA}$ with changing collector potential                           | 141        |

| 4.29 | Measured microwave gains, DHBT 27 – Peak $f_{\tau}$                                                      | 141        |

| 4.30 | Measured microwave gains, DHBT 27 – Peak $f_{max}$                                                       | 142        |

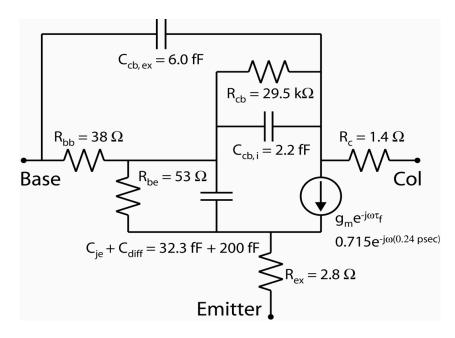

| 4.31 | Hybrid- $\pi$ model, DHBT 27 – Peak $f_{\tau}$ , $f_{max}$                                               | 143        |

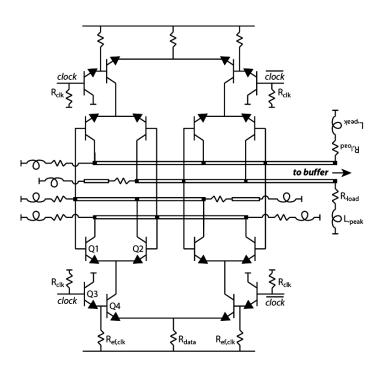

| 4.32 | Comparison of $C_{cb}$ vs $J_e$ and $V_{cb}$ , DHBT 27, labeled to show the                              |            |

|      | corresponding device switching endpoints within a CML divider                                            |            |

|      | schematic Fig. 4.33. Lines connecting the switching endpoints have                                       |            |

|      | been superimposed to act as a guide                                                                      | 144        |

| 4.33 | Schematic of current mode logic (CML) static frequency divider                                           | 145        |

| 4.34 | Simulated band-structure mHBT – $V_{be}$ = 0.9 V, $V_{cb}$ = 0.0 V                                       | 147        |

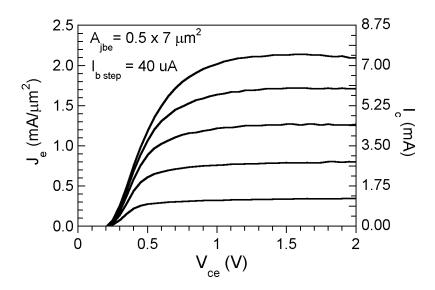

| 4.35 | Common-emitter current-voltage characteristics, mHBT                                                     | 148        |

| 4.36 | Gummel curves – comparing metamorphic and lattice-matched DHBT                                           |            |

|      | characteristics                                                                                          | 149        |

| 4.37 | Measured microwave gains for 200 nm collector metamorphic DHBT –                                         |            |

|      | Peak $f_{\tau}, f_{max}$                                                                                 | 150        |

| 5 1  | Circuit diagram of ECL static frequency divider w/ design details                                        | 154        |

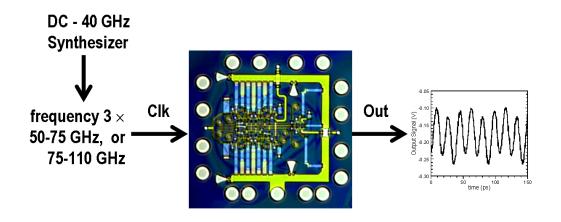

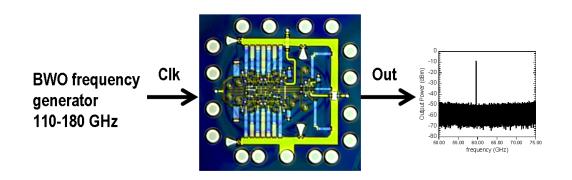

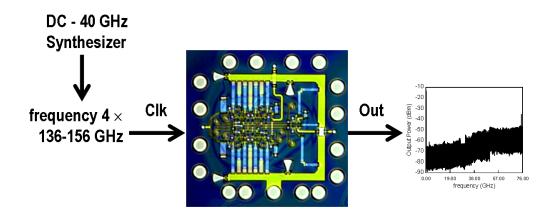

| 5.2  |                                                                                                          | 156        |

| 5.3  | <u>e</u>                                                                                                 | 150<br>157 |

| 5.4  |                                                                                                          | 157<br>157 |

| 5.5  | <u> </u>                                                                                                 | 157<br>158 |

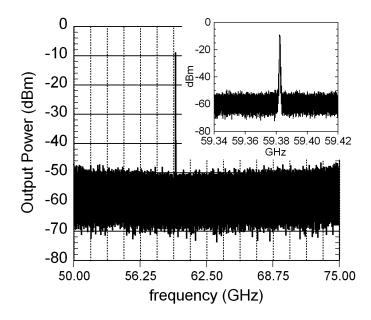

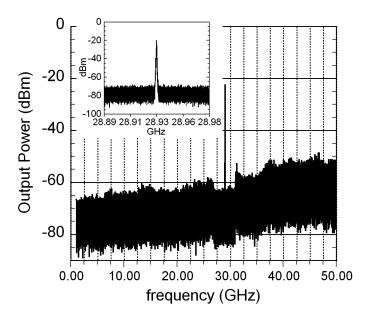

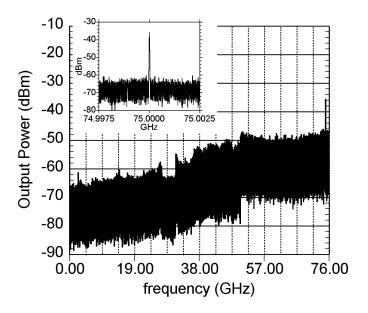

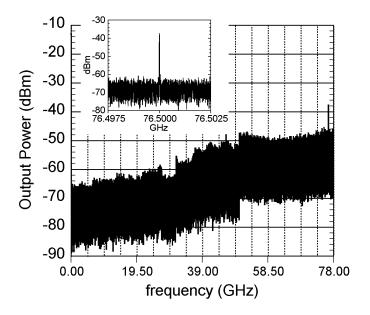

| 5.6  | GCS fabricated divide-by-2 output spectrum, $f_{clk} = 118.70$ GHz,                                      | 150        |

| 5.0  |                                                                                                          | 160        |

| 5.7  | GCS fabricated divide-by-4 output spectrum, $f_{clk} = 115.72$ GHz,                                      | 100        |

| 2.7  | • • • • • • • • • • • • • • • • • • • •                                                                  | 161        |

|      | 1000                                                                                                     | 1          |

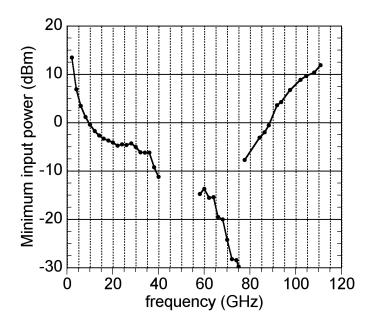

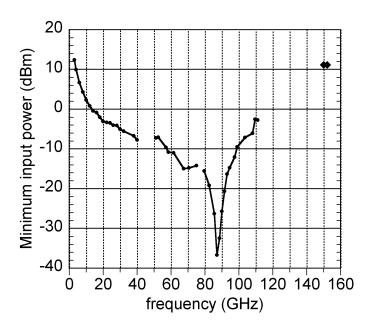

| 5.8        | Sensitivity plot of 118.7 GHz divide-by-2                                              |

|------------|----------------------------------------------------------------------------------------|

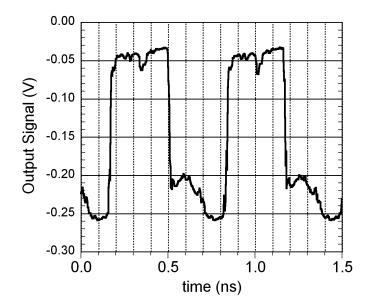

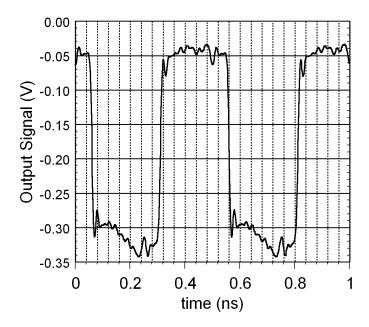

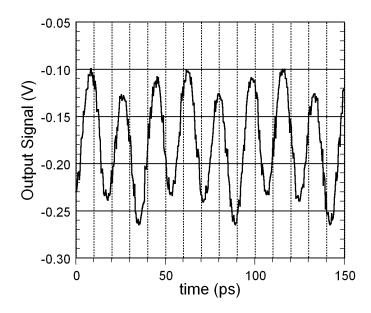

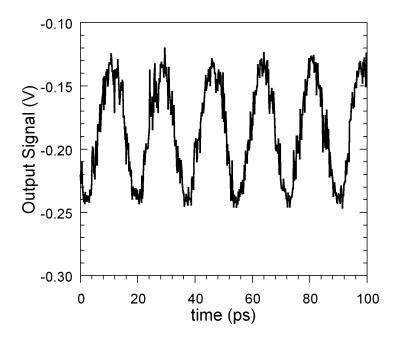

| 5.9        | GCS divide-by-2 output waveform, $f_{clk}$ = 3 GHz, $f_{out}$ = 1.5 GHz 164            |

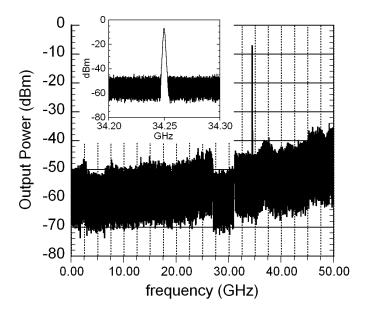

| 5.10       | GCS fabricated divide-by-4 output spectrum, $f_{clk}$ = 137 GHz, $f_{out}$ =           |

|            | 34.25 GHz                                                                              |

| 5.11       | GCS fabricated divide-by-2 output spectrum, $f_{clk} = 150 \text{ GHz}$ , $f_{out} =$  |

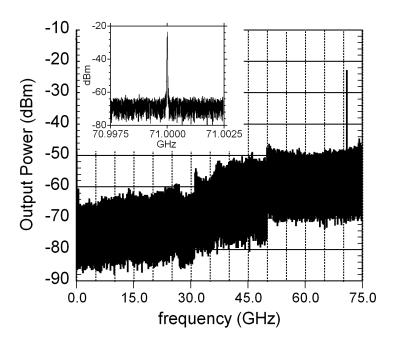

|            | 75 GHz at $T = 25^{\circ}$ C                                                           |

| 5.12       | GCS fabricated divide-by-2 output spectrum, $f_{clk}$ = 153 GHz, $f_{out}$ =           |

|            | 76.5 GHz at $T = 20^{\circ}$ C                                                         |

| 5.13       | Sensitivity plot of 150 GHz divide-by-2                                                |

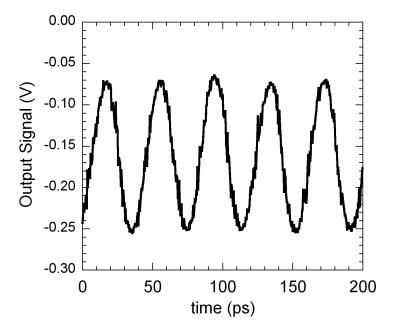

| 5.14       | UCSB divide-by-2 output waveform, $f_{clk} = 4$ GHz, $f_{out} = 2$ GHz 170             |

| 5.15       | UCSB divide-by-2 output waveform, $f_{clk}$ = 113.1 GHz, $f_{out}$ = 56.55 GHz-        |

|            | the highest available sampling scope measurement 171                                   |

| 5.16       | UCSB fabricated divide-by-2 output spectrum, $f_{clk} = 142 \text{ GHz}$ , $f_{out} =$ |

|            | 71 GHz                                                                                 |

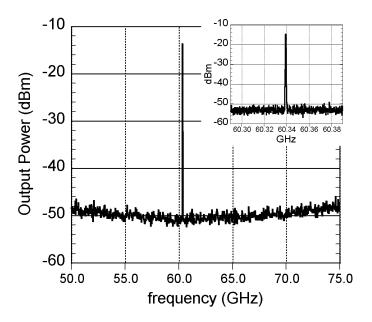

| 5.17       | RSC fabricated divide-by-2 output spectrum, $f_{clk} = 120.68$ GHz,                    |

|            | $f_{out} = 60.34 \text{ GHz} \dots 173$                                                |

| <i>c</i> 1 | Summary of f and f manfarmana from various HDT manufac                                 |

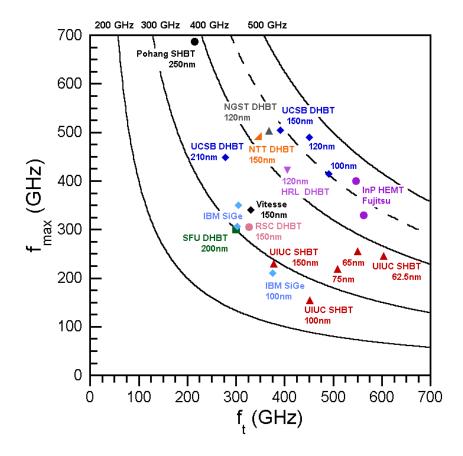

| 6.1        | Summary of $f_{\tau}$ and $f_{max}$ performance from various HBT manufac-              |

| 6.2        | turers at the collector thickness cited – updated June 2005 179                        |

|            | Circuit diagram of current mode logic (CML) static frequency divider 181               |

| 6.3        | CML divide-by-2 output waveform $-f_{clk,max} = 112.5$ GHz, $f_{out} = 56.25$ GHz      |

| 6.4        | Ultra low power CML divide-by-2 output waveform $-f_{clk,max} = 51 \text{ GHz}$ ,      |

| 0.4        | $f_{out} = 25.5 \text{ GHz} \dots 184$                                                 |

|            | $J_{out} = 25.5 \text{ GHz} \dots 164$                                                 |

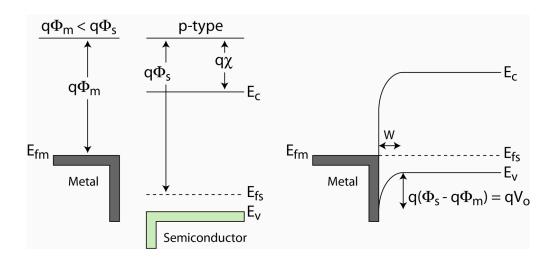

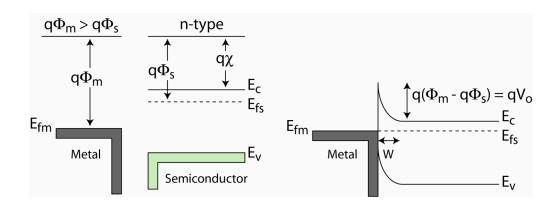

| A.1        | Band line-up of p-type ohmic contact                                                   |

| A.2        | Band line-up of n-type ohmic contact                                                   |

|            |                                                                                        |

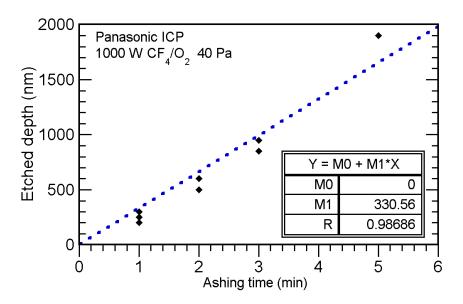

| B.1        | BCB etch rate for the given $CF_4/O_2$ recipe                                          |

## List of Tables

| 2.1  | Summary of simultaneous parameter scaling for a $\gamma$ :1 increase in HBT and circuit bandwidth                                                                                                                                                                             | 41  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1  | Summary of InP HBT ohmic contact progress. Note, for these HBTs a base doping grade is employed and the values listed below reflect the doping value of the semiconductor the metal makes contact to                                                                          | 63  |

| 4.1  | Layer structure DHBT 19b – 150 nm collector, 30 nm base                                                                                                                                                                                                                       | 107 |

| 4.2  | Summary of electrical characteristics, DHBT 19b                                                                                                                                                                                                                               | 109 |

| 4.3  | Layer structure DHBT 22 – 150 nm collector, 30 nm base                                                                                                                                                                                                                        | 113 |

| 4.4  | Summary of electrical characteristics, DHBT 22                                                                                                                                                                                                                                | 115 |

| 4.5  | Layer structure DHBT 24 – 210 nm collector, 35 nm base                                                                                                                                                                                                                        | 119 |

| 4.6  | Summary of electrical characteristics, DHBT 24                                                                                                                                                                                                                                | 119 |

| 4.7  | Layer structure DHBT $25 / 26 - 100$ nm collector, $30$ nm base                                                                                                                                                                                                               | 125 |

| 4.8  | Summary of electrical characteristics, DHBT 25 and 26                                                                                                                                                                                                                         | 131 |

| 4.9  | Thermal resistance and device operating temperature – $A_{je} = 0.6 \times$                                                                                                                                                                                                   |     |

|      | $4.3 \mu \text{m}^2 \dots \dots$                                                                                                                                        | 134 |

|      | Layer structure DHBT 27 – 120 nm collector, 30 nm base                                                                                                                                                                                                                        | 137 |

|      | Summary of electrical characteristics, DHBT 27                                                                                                                                                                                                                                | 140 |

|      | Layer structure <i>metamorphic</i> DHBT – 200 nm collector, 30 nm base                                                                                                                                                                                                        | 146 |

| 4.13 | Summary of electrical characteristics, mHBT                                                                                                                                                                                                                                   | 148 |

| 5.1  | Key device parameters of the 118.7 GHz static divider                                                                                                                                                                                                                         | 159 |

| 5.2  | Key device parameters of the 150 GHz static divider                                                                                                                                                                                                                           | 163 |

| 6.1  | Summary of electrical characteristics for all HBTs fabricated in this work – from April 2003 to January 2005, listed sequentially. <b>Bold</b> listed values of $f_{\tau}$ and $f_{max}$ indicate record performance for InP-DHBTs at the time of measurement and publication | 178 |

# Introduction

ESPITE formidable progress in CMOS, bipolar transistors remain competitive due to the larger breakdown voltages obtainable and the larger lithographic feature sizes required for a transistor at a given bandwidth. Compared to the SiGe material system, InP heterojunction bipolar transistors (HBTs) have  $\approx$  3.5:1 higher collector electron velocity and  $\approx$  10:1 higher base electron diffusivity. Consequently, at the same scaling generation InP HBTs would have  $\approx$  3:1 greater bandwidth than SiGe HBTs. Today the maturity of advanced silicon processes has enabled SiGe HBTs to be fabricated with 100 nm emitter junctions with minimal extrinsic parasitics, while efforts to aggressively scale InP HBTs are described in this work. With that, SiGe HBTs have demonstrated simultaneous 300 GHz  $f_{\pi}$  and 350 GHz  $f_{max}$  [1] and 102 GHz static frequency dividers [2], while InP DHBTs from UCSB have obtained simultaneous 450 GHz  $f_{\pi}$  and 490 GHz  $f_{max}$  [3], 176 GHz power amplifiers with 5-dB power gain [4], and > 150 GHz static frequency dividers [5]. Consequently, the two technologies today have comparable bandwidth,

with SiGe offering much higher levels of integration. Continued bandwidth improvement and increased integration of InP HBTs requires careful consideration be given to scaling laws and limits, and the requirements placed upon transistor design for wideband circuits must be clearly understood [6, 7].

The InP HBTs described in this work utilize a triple-mesa structure. Collector, base, and emitter layers are grown atop of each other and device layers are isolated by mesa formation once electrical contacts have been made. Under bias, the carriers are swept vertically across the emitter, base, and collector by their respective transport mechanisms to realize transistor behavior. The dominant delay associated with the electrons traversing the HBT layers is the base and collector transit times,  $\tau_b + \tau_c = \tau_f$ . Because mesa HBTs are a vertical transport device, the unity current gain frequency  $f_{\tau} \approx (2\pi\tau_f)^{-1}$  will increase by thinning the active base and collector layers through growth. However, the resistances associated with the ohmic contacts, the link resistances between the contacts and active layers, and the extrinsic base-collector capacitance  $C_{cb,ex}$  underneath the base contact (a consequence of the mesa device topology, needed to supply bias to the base terminal of the HBT) must be similarly scaled. If they are not, the maximum oscillation frequency  $f_{max}$ will decrease significantly, the  $C_{cb}/I_c$  ratio (a digital IC figure of merit for HBTs) will increase, and no benefit from epitaxial scaling will be realized.

This thesis is separated into two parts. The first details design, scaling and fabri-

cation challenges addressed in this work. In Chapter 2 the mesa HBT technology is described. Scaling laws for increasing HBT and digital IC bandwidth, and physical limits to scaling are presented. Advanced process modules for continued increases to HBT bandwidth are briefly discussed – they include collector pedestal implants for reduced  $C_{cb}$  and regrown-emitter junctions for reduced  $R_{ex}$  and  $R_{bb}$ . Chapter 3 summarizes the fabrication efforts undertaken to aggressively scale the mesa HBT footprint and its parasitics. A high-yield 0.5  $\mu$ m narrow mesa emitter junction technology has been realized. The contact resistivity  $\rho_c$  for the emitter, base, and collector layers has been reduced to less than  $10 \Omega \cdot \mu m^2$ . With this base-contact  $\rho_c$  and a typical base sheet  $\rho_s \cong 600 \ \Omega/\Box$ , the metal-semiconductor transfer length  $L_t$  is  $\sim$ 120 nm. When combined with i-line stepper lithography having less than 150 nm registration error and collector undercut during mesa formation  $\sim$  150 nm, 0.3  $\mu$ m base contacts have been realized. This has substantially reduced the  $C_{cb,ex}$  with minimal increase to the base resistance  $R_{bb}$ . Device performance has thus increased at the same epitaxial scaling generation.

The reductions to the extrinsic capacitive and resistive parasitics have allowed the active collector thickness  $T_c$  to be thinned for increased device bandwidth. To achieve minimum  $C_{cb}/I_c$  ratio as  $T_c$  is reduced, the maximum current density will increase  $J_e = J_{Kirk} \propto T_c^{-2}$ . The power density will similarly increase  $P = I_c \cdot V_{ce}$  =  $J_e A_e \cdot V_{ce}$ . Improved device heat-sinking to the high thermally-conductive InP

substrate for reduced HBT thermal resistance  $\theta_{JA}$  (K· $\mu$ m²/mW) must be considered during HBT design to prevent excessive device self-heating as the operating power density increases. A barrier to heat flow from the active collector region to the InP substrate is a thin layer of low-thermally conductive In<sub>0.53</sub>Ga<sub>0.47</sub>As. This layer provides low contact resistance  $\rho_c$  for the InP sub-collector. In this work, this layer has been progressively thinned from 25 nm to 6.5 nm to minimize  $\theta_{JA}$ , without significantly increasing  $\rho_c$ .

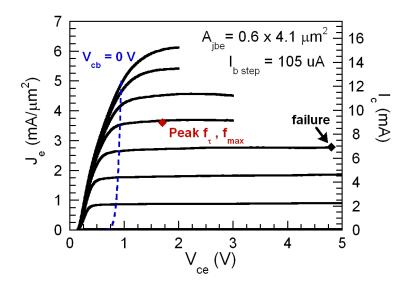

The second part of this thesis reports discrete InP DHBT performance and static frequency divider designs from UCSB. Chapter 4 presents many device results of varying collector thicknesses, they include,

$T_c=210~{\rm nm} \rightarrow f_\tau/f_{max}=276/451~{\rm GHz}, T_c=150~{\rm nm} \rightarrow f_\tau/f_{max}=391/505~{\rm GHz},$   $T_c=120~{\rm nm} \rightarrow f_\tau/f_{max}=450/490~{\rm GHz}, T_c=100~{\rm nm} \rightarrow f_\tau/f_{max}=491/415~{\rm GHz}.$  Calibration methods used to make on-wafer and off-wafer network analyzer measurements to 110 GHz are discussed. In addition to demonstrating high bandwidths, these HBTs showed very low-leakage currents  $\sim 100~{\rm pA}$  and could operate to a power density of  $20~{\rm mW}/\mu{\rm m}^2$  before failure. This is the first work to present such devices. Chapter 5 reports static frequency dividers (digital benchmark circuits for a device technology) designed and fabricated utilizing an HBT with a collector thickness of 150 nm. The devices within the circuits were biased at or close to  $J_{Kirk}$  to minimize the dominant gate delay term  $\tau=C_{cb}\Delta V_l/I_c$ . The amount of logic

swing consumed by the emitter resistance  $\Delta V_{parasitic}$  was the HBT scaling limit for these circuits. A dense wiring scheme is used to reduce interconnect delays, and the signal integrity was maintained through the use of a low- $\varepsilon_r$ , thin-film microstrip environment. Divide-by-2 designs from UCSB, fabricated at Global Communication Systems (GCS), had a maximum toggle rate of  $f_{clk,max}$  = 153 GHz. The same divide-by-2 circuits fabricated at UCSB had a maximum toggle rate  $f_{clk,max}$  = 142 GHz.

### References

- [1] M. Khater, J.-S. Rieh, T. Adam, A. Chinthakindi, J. Johnson, R. Krishnasamy, M. Meghelli, F. Pagette, D. Sanderson, C. Schnabel, K.T. Schonenberg, P. Smith, K. Stein, A. Stricker, S.-J. Jeng, D. Ahlgren, and G. Freeman, "SiGe HBT Technology with  $f_{max}$  /  $f_{\tau}$  = 350/300 GHz and gate delay below 3.3 ps", *Proc. IEEE Int. Electron Device Mtg*, San Francisco, CA, Dec. 13-15, 2004, pp. 247-250.

- [2] J. Böck, H. Schäfer, H. Knapp, K. Aufinger, M. Wurzer, S. Boguth, T. Böttner, R. Stengl, W. Perndl, T.F. Meister, "3.3 ps SiGe bipolar technology", *Proc. IEEE Int. Electron Device Mtg*, San Francisco, CA, Dec. 13-15, 2004, pp. 255-258.

- [3] Z. Griffith, M.J.W. Rodwell, X.-M. Fang, D. Loubychev, Y. Wu, J.M. Fastenau, and W.K. Lui, "InGaAs/InP DHBTs with 120 nm collector having simultaneously high  $f_{\tau}$ ,  $f_{max} \geq 450$  GHz", *IEEE Electron Device Lett.*, vol. 26, August 2005.

- [4] V. Paidi, Z. Griffith, Y. Wei, M. Dahlström, M. Urteaga, N. Parthasarathy, M. Seo, L. Samoska, A. Fung, and M.J.W. Rodwell, "G-Band (140-220 GHz) and W-Band (75-110 GHz) InP DHBT medium power amplifiers", *IEEE Tran. on Microwave Theory and Techniques*, vol. 53, pp. 598-605, Feb. 2005.

- [5] Z. Griffith, M. Dahlström, M.J.W. Rodwell, M. Urteaga, R. Pierson, P. Rowell, B. Brar, S. Lee, N. Nguyen, and C. Nguyen, "Ultra high frequency static dividers > 150 GHz in a narrow mesa InGaAs/InP DHBT technology", *IEEE Bipolar/BiCMOS Circuits and Technology Meeting*, Montreal, Canada, September 13-14, 2004, pp. 176-179.

- [6] M.J.W. Rodwell, M. Urteaga, Y. Betser, D. Scott, M. Dalhström, S. Lee, S. Krishnan, T. Mathew, S. Jaganathan, Y. Wei, D. Mensa, J. Guthrie, R. Pullela, Q. Lee, B. Agarwal, U. Bhattacharya, S. Long, "Scaling of InGaAs/InAlAs HBTs for high speed mixed-signal and mm-wave ICs", *Int. J. High-Speed Electron. Syst.*, vol. 11, no. 1, pp. 159-215, 2001.

- [7] M.J.W. Rodwell, M. Urteaga, T. Mathew, D. Scott, D. Mensa, Q. Lee, J. Guthrie, Y. Betser, S.C. Martin, R. P. Smith, S. Jaganathan, S. Krishnan, S. I. Long, R. Pullela, B. Agarwal, U. Bhattacharya, L. Samoska, and M. Dahlström. "Submicron Scaling of HBTs" *IEEE Trans. on Electron Devices*, Vol. 48, pp. 2606-2624, November 2001.

## 2

## InP DHBT Theory and Design

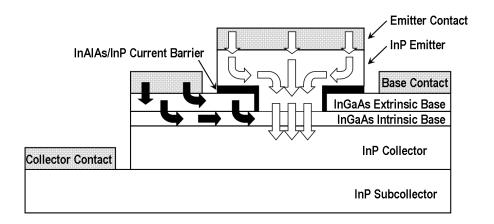

NP heterojunction bipolar transistors (HBT) utilizing a mesa topology have been under development at UCSB since 2002. It was pursued as an alternative to the transferred-substrate technology (TS-HBT), where the active collector is defined lithographically after substrate removal and the extrinsic base-collector capacitance  $C_{cb,ex}$  can be made small in comparison to the entire  $C_{cb}$  of the HBT. However, this process is very complicated and the device yield was low, motivating the mesa structure as an alternative topology for UCSB HBTs.

In this chapter, the mesa HBT technology is described. The carrier delays, resistances, and capacitances are presented, with emphasis on their physical origins from the device topology. From that, the RF HBT figures-of-merit  $f_{\tau}$  and  $f_{max}$  are introduced. The base and collector transit delays are the dominant contributors to  $f_{\tau}$  and  $f_{max}$ , but their values do not correlate well to the delays associated with a digital latch, regularly employed as retiming elements and decision circuits. HBT scaling laws are considered here for increased circuit bandwidth. Lastly, device modeling,

scaling limits, and advanced process modules intended to alleviate these limitations are discussed.

### 2.1 mesa HBT structure

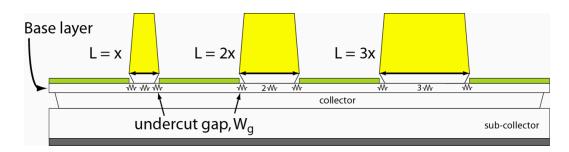

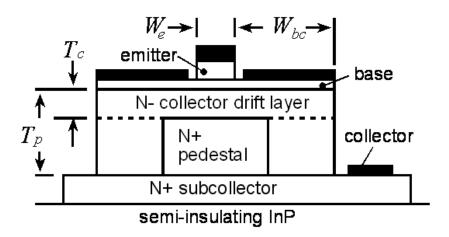

Figure 2.1: Mesa HBT structure w/ self-aligned base contact

The InP HBTs described in this work utilize a triple-mesa structure, shown in Fig. 2.1 and Fig. 2.2. Collector, base, and emitter layers are grown atop of each other and device layers are isolated by mesa formation once electrical contacts have been made. Under bias, the carriers are swept vertically across the emitter, base,

Figure 2.2: Mesa HBT showing distributed device resistances and capacitances

and collector by their respective transport mechanisms to realize transistor behavior. A metal-semiconductor contact is utilized to electrically link the emitter, base, and collector semiconductor to their respective interconnects. Because the emitter is the top-most layer, its contact can lie above the active region of the device. The base however must be accessed externally through a contact that resides adjacent to the emitter stripe. Spreading resistance underneath the emitter mesa within the intrinsic part of the base is unavoidable. The horizontal gap between the base contact and emitter mesa, and the contact adds additional extrinsic resistances. Furthermore, the base mesa ( $W_{mesa} = 2W_{cont} + 2W_{gap} + W_e$ ) defines the width of the collector

mesa and hence the total  $C_{cb}$  of the HBT. Minimizing the base gap and width of the contacts will avoid unwanted increases to  $R_{bb}$  and  $C_{cb}$ . To ensure this, a self-aligned base contact is employed. After the emitter contact is formed, the emitter mesa is etched down to the base. During the emitter semiconductor etch, an undercut is formed. The undercut serves as a shadow-mask such that the base contact can be deposited overtop the emitter contact and adjacent periphery to contact the base semiconductor, such that only the emitter mesa undercut  $\sim 50$  nm contributes to the base gap resistance. The collector is accessed externally and adjacent to the base. Because the collector is depleted, a thick, highly doped  $N^+$  sub-collector is utilized to provide collector bias. This layer lies underneath the collector mesa, has similar spreading, gap, and contact resistances as described for the base, and is contacted on both sides using a non-self aligned 'horseshoe' like contact. To isolate devices, the sub-collector is etched from the field through to the semi-insulating InP substrate. Further fabrication details are given in Chapter 3 and Appendix B.

### 2.2 HBT carrier transit times

The time it takes for an electron entering from the emitter to traverse across the base is given by,

$$\tau_b = \frac{T_b^2}{2D_n} + \frac{T_b}{v_{exit}} \tag{2.2.1}$$

where  $T_b$  is the base thickness and  $D_n$  is the electron minority diffusivity in the base. Often the  $T_b/v_{exit}$  contribution is ignored by assuming that the electron concentration at the collector side of the base is zero. For a thin base this assumption is not valid and the correction term accounts for how quickly the finite electron concentration exits the base, at a velocity proportional to the thermionic emission velocity  $v_{exit} \sim (2kT/\pi m^*)^{1/2}$  [1]. This transit time calculation assumes uniform composition and doping in the base. To reduce  $\tau_b$ , a quasi-electric field can be established to accelerate electrons more quickly across the base. Assuming the grading of the base conduction band is linear, Equ. 2.2.1 is rewritten as [2],

$$\tau_b = \frac{T_b^2}{D_n} \left( \frac{kT}{\Delta E} \right) \left[ 1 - \frac{kT}{\Delta E} \left( 1 - \exp^{-\Delta E/kT} \right) \right] + \frac{T_b}{v_{exit}} \left( \frac{kT}{\Delta E} \right) \left( 1 - \exp^{-\Delta E/kT} \right)$$

(2.2.2)

where  $\Delta E$  is the energy difference across the base conduction band. The HBTs presented in this work employ a doping grade producing a  $\Delta E \sim 50$  meV. This in turn reduces  $\tau_b$  by  $\sim 50\%$  compared to an ungraded base. Note Equ. 2.2.2 does not consider hot carrier or quasi-ballistic transport in the base due to the abrupt InP/InGaAs emitter-base junction utilized by UCSB HBTs.

Electrons injected from the base into the collector create a displacement current across the junction. The mean delay associated with this current is related to the change in stored base charge (equivalent induced image charge) at the collector side

of the base terminal  $\delta Q_{base}$ , given by

$$\tau_c = \int_0^{T_c} \frac{1 - x/T_c}{\upsilon(x)} dx \equiv \frac{T_c}{2\upsilon_{eff}}$$

(2.2.3)

where  $\tau_c$  is the collector transit time,  $T_c$  is the collector thickness, and  $\upsilon(x)$  and  $\upsilon_{eff}$  are the position-dependent and effective electron velocities in the collector drift region.

As electrons enter the collector, they acquire kinetic energy and experience ballistic transport, typically referred to as a velocity overshoot regime. Because of the large energy separation between the  $\Gamma$ -L conduction band valleys (0.55 eV for  $In_{0.53}Ga_{0.47}As$ , 0.6 eV for InP), electrons are able to traverse a significant fraction of the collector before attaining sufficient kinetic energy to cause scattering to the higher effective mass, lower velocity L-valley [3, 4]. By modeling the collector velocity as a two-step profile, Equ. 2.2.3 can be written as,

$$\tau_c = \frac{1}{T_c} \int_0^{T_s} \frac{T_c - x}{v_1} dx + \frac{1}{T_c} \int_{T_s}^{T_c} \frac{T_c - x}{v_2} dx$$

(2.2.4)

and solved to give,

$$\tau_c = \frac{1}{T_c} \left[ \frac{2T_c T_s - T_s^2}{2\nu_1} + \frac{(T_c - T_s)^2}{2\nu_2} \right]$$

(2.2.5)

Because the collector transit time is more heavily weighted on the rate at which  $\delta Q_{base}$  decreases as the displacement current traverses the collector, higher electron velocities near the base are desired. This is shown in the following example. Consider two scenarios:  $v_1 = v_o$ ,  $v_2 = \frac{1}{2}v_o$  and  $v_1 = \frac{1}{2}v_o$ ,  $v_2 = v_o$ . Assume the velocity

transition is at  $T_s=\frac{1}{2}T_c$ . In the first case where the velocity is higher near the base  $v_{eff}=\frac{4}{5}v_o$ , and in the second case where the velocity is lower near the base  $v_{eff}=\frac{4}{7}v_o$  – a difference of  $\sim 40\%$ .

### 2.3 Collector design and maximum current density

As the collector current density is varied, the injected electrons screen the background doping and modify the electric field profile in the collector. To account for this injected charge, Poisson's equation to describe the collector can be written,

$$-\frac{d^2\phi}{dx^2} = \frac{dE}{dx} = \frac{1}{\varepsilon_o \varepsilon_r} \left[ qN_c - \frac{J(x)}{\upsilon(x)} \right]$$

(2.3.1)

where  $\varepsilon_o \varepsilon_r$  is the dielectric constant,  $N_c$  the collector doping, J(x) the collector current density, and v(x) the electron velocity in the collector. Integrating Equ. 2.3.1 to solve for the electric field,

$$E(x) = \frac{1}{\varepsilon_o \varepsilon_r} \int_0^x q N_c - \frac{J(x)}{v(x)} dx$$

(2.3.2)

Electrons spread outward as they traverse the collector (current spreading) creating a position dependent current density. In the collector transit time discussion, a step function is used to describe a position dependent electron velocity due to overshoot and scattering. Assuming J(x) and v(x) to be constant and integrating across the

electric field,

$$\phi_{bi} + V_{cb} \ge -\frac{T_c^2}{2\varepsilon_o\varepsilon_r} \left[ qN_c - \frac{J_e}{v_{eff}} \right]$$

(2.3.3)

where  $\phi_{bi}$  is approximately the base bandgap potential difference,  $V_{cb}$  is the applied potential difference across the base-collector junction, and  $T_c$  is the collector thickness. When this relationship is equal, the current density (injected electrons) modifies the electric field profile such that it is equal to zero at the base-side of the collector, E(0) = 0. This is often referred to as the Kirk threshold current density,

$$J_{Kirk} = J_{max} = \frac{2\varepsilon_o \varepsilon_r v_{eff}}{T_c^2} (\phi_{bi} + V_{cb}) + q N_c v_{eff}$$

(2.3.4)

At higher  $J_e > J_{max}$  for an InP-SHBT (InGaAs base and collector), holes are no longer confined to the base as the conduction and valence bands progressively flatten within the collector to a distance  $T_1$ ,  $0 \le x < T_1$ , E(x) = 0. This causes the base transit time  $\tau_b$  and collector-base capacitance  $C_{cb}$  to increase, while slightly reducing the collector transit time  $\tau_c$ . This is the classical definition of the Kirk effect [5]. For an InP DHBT (InGaAs base, InP collector), the valence band discontinuity at the base-collector heterojunction blocks holes from entering the collector region. As  $J_e$  exceeds  $J_{max}$ , this barrier prevents holes from compensating the excessive electron density and the field will reverse acting as a barrier to the injected collector current. This current barrier will cause a collapse in the current gain and the reduced electron velocity will significantly increase  $\tau_c$  – a phenomena not experienced by SHBTs.

Higher HBT bandwidths are achieved when  $J_{max}$  is increased at a given collector thickness. From Equ. 2.3.4, this can be done by increasing the externally applied  $V_{cb}$  and/or increasing the collector doping  $N_c$ . When designing an HBT for use in a digital circuit, two bias conditions need to be considered:  $V_{cb} = 0$ ,  $J_e = J_{max}$  and  $J_e = 0$ . To maximize  $J_e$ , the collector doping should be as high as possible, however it should not be so high as to cause depletion layer collapse within the drift collector when there is no current,  $E(x = T_c) = 0$ . From Equ. 2.3.3 this is satisfied when,

$$N_{c,max} = \frac{2\varepsilon_o \varepsilon_r \phi_{bi}}{qT_c^2} \tag{2.3.5}$$

and Equ. 2.3.4 can be rewritten as

$$J_{max} = \frac{4\varepsilon_o \varepsilon_r v_{eff}}{T_c^2} (\phi_{bi} + V_{cb})$$

(2.3.6)

At the doping level prescribed by Equ. 2.3.5,  $J_{max}$  is  $2 \times$  higher compared to a collector that is undoped, greatly influencing logic speed through the use of smaller devices at a given operating current  $I_c$ .

### 2.3.1 Correction to account for UCSB base-collector grade

InP DHBTs from UCSB utilize an InGaAs base and InP collector, often referred to as Type-I DHBTs. The conduction band discontinuity between  $In_{0.53}Ga_{0.47}As$  and  $InP (\Delta E_c = 0.26 \text{ eV})$  is removed through a combined transition scheme employing an InGaAs setback layer and chirped-superlattice InGaAs/InAlAs grade [6, 7].

The grade acts to smooth out the energy discontinuity such that there is no effective potential drop across the length of the grade. A dipole electric field is formed between the  $P^+$  base and an N-doped pulse layer inserted to restore the expected field across the graded region, determined from the relationship,

$$N_{\delta}T_{\delta} = \frac{\varepsilon_{o}\varepsilon_{r}\Delta E_{c}}{q^{2} \cdot T_{grade}}$$

(2.3.7)

where  $N_{\delta}$  and  $T_{\delta}$  are the doping concentration and thickness of the pulse layer. To ensure electrons traverse through the grade and are not reflected, kinetic energy is supplied to them over the setback region. Note, Equ. 2.3.7 does not consider this layer, and the setback potential difference  $\Delta\phi_{setback}$  can be a significant fraction of  $\phi_{bi}$ . The amount of kinetic energy needed by the electrons over the setback layer for the employed grade design is not well understood at this time. The InP DHBTs reported in Chapter 4 show no signs of current blocking utilizing a launching energy  $\Delta\phi_{setback}\sim 0.35$  eV. To account for the dipole field across the setback and grade, Poisson's equation is modified,

$$\phi_{bi} + V_{cb} \ge \frac{qN_cT_c^2}{2\varepsilon_o\varepsilon_r} + \frac{qN_\delta T_\delta (T_{setback} + T_{grade})}{\varepsilon_o\varepsilon_r}$$

(2.3.8)

From this expression the maximum allowable collector doping to ensure full collector depletion is,

$$N_{c,max} = \frac{1}{T_c^2} \left[ \frac{2\varepsilon_o \varepsilon_r}{q} (\phi_{bi} + V_{cb}) - 2N_\delta T_\delta (T_{setback} + T_{grade}) \right]$$

(2.3.9)

Assuming standard values for  $N_{\delta}=3\cdot 10^{18}$  cm<sup>-3</sup>,  $T_{\delta}=3$  nm,  $T_{setback}=20$  nm, and  $T_{grade}=24$  nm at  $V_{cb}=0$  V, the dipole field reduces the maximum collector doping by  $\sim 2/3$ . This is a significant reduction that must be accounted for in design.

An alternative way to determine  $N_{d,max}$  and solve for  $J_{max}$  is to only consider the portion of the collector between the pulse doping and sub-collector. Poisson's equation solved over this region is,

$$\phi_{bi} - \Delta\phi_{setback+grade} + V_{cb} \frac{T_{InP}}{T_c} \ge -\frac{T_{InP}^2}{2\varepsilon_o \varepsilon_r} \left[ qN_c - \frac{J(x)}{\upsilon(x)} \right]$$

(2.3.10)

where  $T_{InP}$  is the thickness of the InP portion of the collector and the potential difference across the setback and grade is,

$\Delta \phi_{setback+grade} \approx$

$$(\phi_{bi} + V_{cb}) \frac{T_{setback}}{T_c} + \frac{q N_{\delta} T_{\delta} (T_{setback} + T_{grade})}{\varepsilon_o \varepsilon_r} + \left[ q N_c - \frac{J_e}{v_o} \right] \frac{T_c (T_{setback} + T_{grade})}{2\varepsilon_o \varepsilon_r}$$

(2.3.11)

where  $v_o$  is the electron overshoot velocity in the setback and grade. From Equ. 2.3.10,  $N_{d,max}$  and  $J_{max}$  are,

$$N_{c,max} = \frac{2\varepsilon_o \varepsilon_r \cdot (\phi_{bi} - \Delta \phi_{setback+grade} + V_{cb}(T_{InP}/T_c)}{qT_{InP}^2}$$

(2.3.12)

$$J_{max} = \frac{2\varepsilon_o \varepsilon_r v'_{eff}}{T_{InP}^2} \left( \phi_{bi} - \Delta \phi_{setback+grade} + V_{cb} \frac{T_{InP}}{T_c} \right) + q N_c v'_{eff}$$

(2.3.13)

where  $\upsilon_{eff}'$  is used to denote the effective velocity in the InP layer.

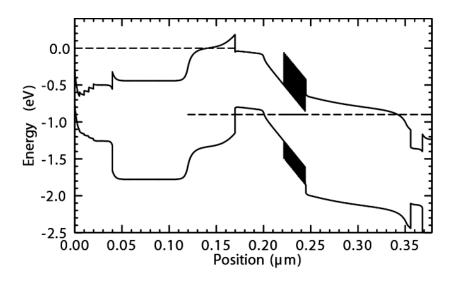

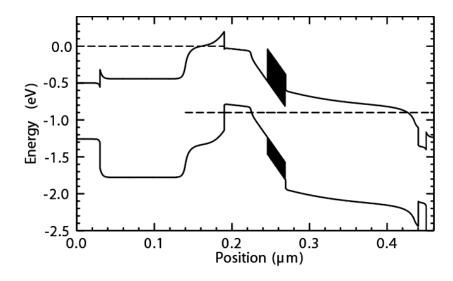

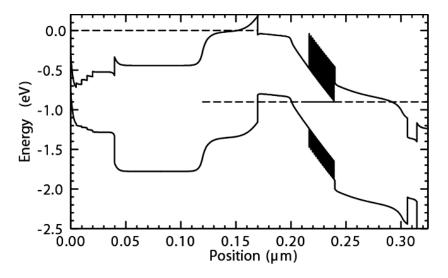

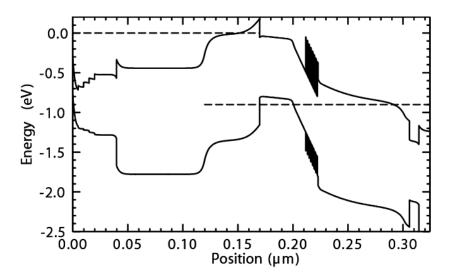

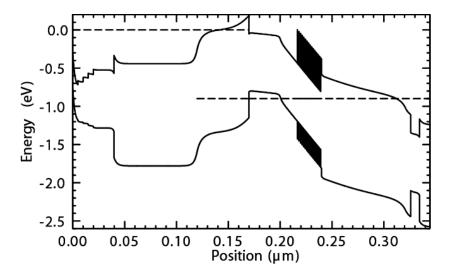

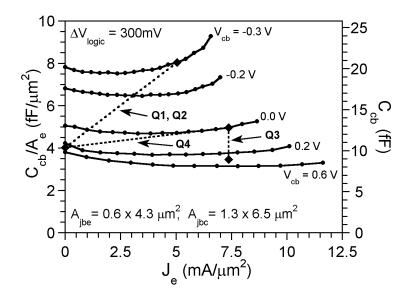

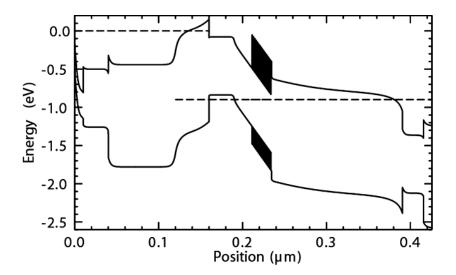

Figure 2.3: Variation of band diagram at  $V_{cb} = 0$ , J = 0,  $J_{max}$ , and 1.5  $J_{max}$

A band-diagram for the base-collector junction is shown in Fig. 2.3 for  $J_e=0$ ,  $J_{max}$ , and 1.5  $J_{max}$  at  $V_{cb}=0$ . Notice from the band-diagram and Equ. 2.3.11,  $\Delta\phi_{setback+grade}$  decreases as  $J_e$  increases, significantly influencing  $J_{max}$  by increasing the potential difference across the InP layer. However, at  $J_e>J_{max}$ , the reductions to  $\Delta\phi_{setback+grade}$  cause a positive potential increase across the grade. At 1.5  $J_{max}$ , the field is beginning to reverse in the InP layer, but the potential difference across the grade  $\approx \Delta E_e/q$  has become sufficiently large to block electrons and/or reduce their velocity, exacerbating the field reversal at higher  $J_e$ . This behavior has been witnessed from fabricated UCSB DHBTs of varying collector thicknesses;

$C_{cb}$  increases slowly,  $f_{\tau}$  and  $f_{max}$  decrease gradually as  $J_{e}$  exceeds  $J_{max}$ . At much higher  $J_{e}$ , the increase of  $C_{cb}$  is rapid, and  $f_{\tau}$  and  $f_{max}$  both roll-off sharply.

### 2.4 HBT resistance and capacitance

### **2.4.1** Base-collector depletion capacitance, $C_{cb}$

With respect to the mesa HBT structure shown in Fig. 2.1, the three components of the collector-base capacitance are,

$$C_{cb} = C_{cb,ex} + C_{cb,qap} + C_{cb,i} (2.4.1)$$

$$C_{cb,ex} = 2 \frac{\varepsilon_o \varepsilon_r L_e W_b}{T_c} , \quad C_{cb,gap} = 2 \frac{\varepsilon_o \varepsilon_r L_e W_{gap}}{T_c} , \quad C_{cb,i} = \frac{\varepsilon_o \varepsilon_r L_e W_e}{T_c}$$

where  $W_b$  is the width of the base metal-semiconductor junction,  $W_{b,gap}$  is the spacing between the base contact and emitter mesa, and  $W_e$  and  $L_e$  are the width and length of the emitter junction.

### 2.4.2 Base resistance

The three components that contribute to the base resistance of an HBT are the metal-semiconductor contact  $R_{b,cont}$ , the gap or link resistance between the base contact and emitter mesa  $R_{b,gap}$ , and the spreading resistance within the active region where recombination takes place,  $R_{b,spread}$ . Assuming the base is contacted on both

sides of the emitter,

$$R_{bb} = R_{b,cont} + R_{b,gap} + R_{b,spread} (2.4.2)$$

$$R_{b,cont} = \frac{\sqrt{\rho_c \cdot \rho_s}}{2L_e} \coth \frac{W_b}{L_t} , \quad R_{b,gap} = \rho_s \frac{W_{b,gap}}{2L_e} , \quad R_{b,spread} = \rho_s \frac{W_e}{12 \cdot L_e}$$

where  $\rho_c$  ( $\Omega \cdot \mu m^2$ ) and  $\rho_s$  ( $\Omega/\Box$ ) are the specific contact and sheet resistivities of the base, and  $L_t$  is the ohmic transfer length equal to  $\sqrt{\rho_c/\rho_s}$ . Equation 2.4.2 can be rewritten to more clearly show how the base resistance varies with the emitter dimensions and the width of the base mesa,

$$R_{bb} = \frac{1}{2} \frac{\rho_s}{L_e} \left[ L_t \coth \frac{W_b}{L_t} + W_{gap} + \frac{W_e}{6} \right]$$

(2.4.3)

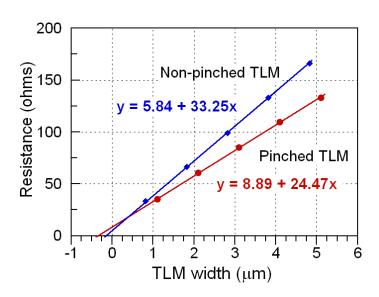

During HBT fabrication, the base sheet and contact resistivities are monitored using four-point-probe transmission line measurements (TLM) from non-pinched and pinched structures. For each TLM pattern measured, the distance between the probe pads progressively increases such that an excellent linear dependence should be observed for the base resistance versus TLM spacing. A non-pinched TLM structure is shown in Fig. 2.4, where the emitter semiconductor has been removed and the base semiconductor to be measured is exposed, used to extract  $\rho_c$ . A pinched TLM structure is shown in Fig. 2.5, where the emitter semiconductor resides atop the base semiconductor, used to determine  $\rho_s$ . Why both structures are needed is explained.

By removing the emitter semiconductor, surface states are formed on the exposed base of the non-pinched TLM. For a 30 nm base where the exposed semiconductor

Figure 2.4: Non-pinched TLM structure – the base semiconductor is exposed

Figure 2.5: Pinched TLM structure – the emitter resides atop the base semiconductor

is doped at  $7 \cdot 10^{19}$  cm<sup>-3</sup>, the surface is depleted by 20%, increasing  $\rho_s$  by the same amount. A Pinched TLM does not experience this. However, the undercut formed during the emitter mesa etch introduces an additive gap resistance term to the extrapolated contact resistance, making the extracted  $\rho_c$  fictitiously high.

Equations 2.4.4 and 2.4.5 show how the non-pinched and pinched TLMs behave,

$$R_{non-pin} = 2R_{cont} + R'_{slope} \cdot L \tag{2.4.4}$$

$$R_{pin} = 2R_{cont} + 2R'_{gap} + R_{slope} \cdot L \tag{2.4.5}$$

The prime notation is used to identify resistive paths of a depleted surface. From the non-pinched relation, the ohmic transfer length is  $L_t = R_{cont}/R'_{slope}$ . From the pinched TLM relation, the base sheet resistance is  $\rho_s = R_{slope} \cdot W_{TLM}$ , where  $W_{TLM}$  is the width of the TLM. The contact resistivity can be determined from the relation  $L_t = \sqrt{\rho_c/\rho_s}$ . Fig. 2.6 shows a plot of measured non-pinched and pinched TLMs from the same wafer.

Figure 2.6: Measured TLMs – Pinched and Non-pinched for DHBT 27

The contact resistivities achieved in this work are very low and necessitate the use of this extraction method. Error is further minimized by examining the fabricated TLMs by SEM so as to use their exact dimensions in the extrapolation.

# 2.4.3 Sub-collector resistance

The contact, gap, and spreading resistances described for the base similarly exist for the sub-collector,

$$R_{cc} = R_{c,cont} + R_{c,qap} + R_{c,spread}$$

(2.4.6)

$$R_{cc} = \frac{1}{2} \frac{\rho_s}{L_e} \left[ L_t + W_{c,gap} + \frac{W_{cb}}{6} \right]$$

where  $\rho_c$  ( $\Omega \cdot \mu m^2$ ) and  $\rho_s$  ( $\Omega/\Box$ ) are the specific contact and sheet resistivities of the collector,  $W_{cb}$  is the width of the collector mesa,  $W_{c,gap}$  is the spacing between the collector mesa and contact,  $L_e$  is the emitter junction length, and  $L_t$  is the ohmic transfer length equal to  $\sqrt{\rho_c/\rho_s}$ . The exponential term associated with  $R_{c,cont}$  can be ignored as the contact is much wider than the  $L_t$  associated with the collector contact.

The sub-collector is thick and highly doped to minimize the sheet resistance. The doping cannot be so high as to introduce defects within the growth of the subsequent layers, and making it unnecessarily thick will introduce problems during wafer planarization because it must be etched away in the field in order to isolate devices. HBTs from UCSB typically employ a 300 nm sub-collector doped with Si at  $2 \cdot 10^{19}$  cm<sup>-3</sup>. Non-pinched TLMs are utilized to measure the sheet and contact resistance of the sub-collector. Any TLM surface depletion is ignored because its thickness is much smaller in comparison to the sub-collector.

# 2.4.4 Emitter resistance

The emitter resistance is dominated by the metal-semiconductor contact, with a small contribution from the tall mesa required for a self-aligned base contact,

$$R_{ex} = R_{ex,cont} + R_{ex,bulk} (2.4.7)$$

$$R_{ex,cont} = \frac{\rho_c}{A_{e,cont}}, \quad R_{ex,bulk} = \rho_{bulk} \frac{h_{mesa}}{A_{je}}$$

After the growth of the  $N^-$  InP emitter, a 120 nm thick  $N^{++}$  InP and InGaAs emitter cap is grown. Because the current transport through the emitter is vertical, standard TLM measurements are not possible. RF parameter extraction is used instead to determine  $R_{ex}$ , and the bulk resistivity  $\rho_{bulk}$  of the emitter cap can be approximated from sub-collector TLM measurements, typically  $3.6~\Omega \cdot \mu m$ . For the 120 nm emitter cap employed in HBTs from UCSB,  $\rho_{bulk}$  contributes  $\sim 0.45~\Omega \cdot \mu m^2$  to  $R_{ex}$ . It is assumed that any surface depletion can be ignored because the emitter junction is much wider and the cap doping is very high. This assumption must be reconsidered when the emitter junction is scaled more narrowly. Nonetheless, if the surface is depleted 50 nm for the  $0.5~\mu m$  emitter HBTs reported in this work (20% cap depletion), the contribution from  $\rho_{bulk}$  would be less than 7 % of the total  $R_{ex}$ .

# 2.5 Transistor figures of merit

The HBT common-emitter unity current-gain cutoff frequency  $f_{\tau}$  is,

$$\frac{1}{2\pi f_{\tau}} = \tau_c + \tau_b + C_{cb} \cdot (R_{ex} + R_c) + \frac{\eta kT}{qI_e} (C_{cb} + C_{je})$$

(2.5.1)

where  $\tau_c$  and  $\tau_b$  are the collector and base transit times,  $C_{cb}$  and  $C_{je}$  are the depletion capacitances for the collector and emitter,  $R_c$  and  $R_{ex}$  are the resistances of the collector and emitter, and  $(\eta kT/qI_c)^{-1}$  is the transconductance of the HBT.

The HBT maximum oscillation (unity power-gain) frequency is,

$$f_{max} = \sqrt{\frac{f_{\tau}}{8\pi (RC)_{eff}}} \tag{2.5.2}$$

dependent upon the HBT  $f_{\tau}$  and a general time constant  $RC_{eff}$  that includes the effects of the distributed base-collector network, the emitter and collector resistances, and the device transconductance  $g_m$  [8]. When the base resistance is much larger than the emitter and collector resistances, their effects become secondary and only the distributed base-collector network needs to be considered. Furthermore, the components of  $C_{cb}$  should only consider the resistance in its path when determining the charging time constants. Utilizing the definitions for  $C_{cb}$  and  $R_{bb}$  from Equ. 2.4.1 and 2.4.3,

$$f_{max} = \sqrt{\frac{f_{\tau}}{8\pi (R_{bb}C_{cb})_{eff}}}$$

(2.5.3)

and

$$(R_{bb}C_{cb})_{eff} = C_{cb,i}R_{bb} + C_{cb,gap}(R_{b,cont} + R_{b,gap}/2) + C_{cb,ex}(R_{b,cont,0}||R_{b,cont,1})$$

(2.5.4)

where the collector-base capacitance underneath the emitter stripe  $C_{cb,i}$  is charged through the entire base resistance, and the gap capacitance  $C_{cb,gap}$  between the emitter mesa and base contact is charged through  $(R_{b,cont} + R_{b,gap}/2)$ . The extrinsic collector-base capacitance  $C_{cb,ex}$  underneath the base contact is charged by currents traversing vertically through the contact above it, having a resistance  $R_{b,cont,0} = \rho_c/(2 \cdot L_eW_b)$ . If the collector mesa has been undercut during fabrication, a parallel charging path is formed by currents traversing laterally through the base contact (semiconductor sheet resistance ignored) in the region associated with the undercut  $W_u$ . This path has a resistance  $R_{b,cont,1} = \rho_s L_t \cdot \coth(W_u/L_t)/2L_e$ , and  $R_{b,cont,0}$  is equal to  $\rho_c/(2 \cdot L_e(W_b - W_u))$

# 2.6 Device modeling

This section describes the two modeling schemes most often used to characterize InP HBTs from UCSB. The first technique makes use of the measured S-parameters of the HBT in order to extract their electron transit time, resistances, and capacitances to create a hybrid- $\pi$  equivalent circuit. It is an accurate, simplified representation of an HBT compared to the true distributed nature of RC elements within

the device. The second device modeling technique utilizes a bias dependent, highly detailed, equation based physical model of the HBT geometry for use in circuit designs.

# 2.6.1 Small-signal equivalent circuit modeling

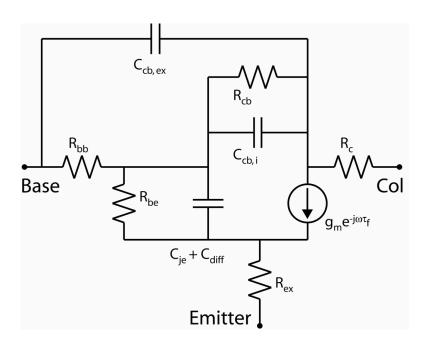

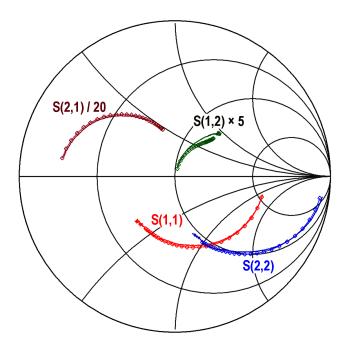

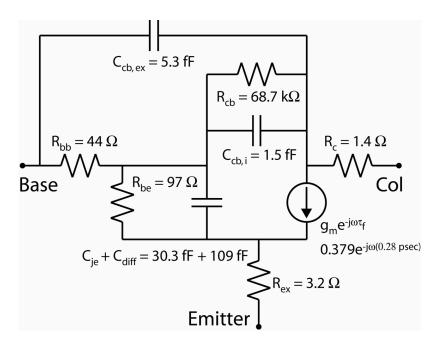

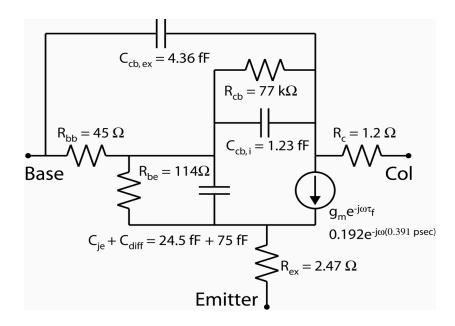

Fig. 2.7 shows the hybrid- $\pi$  equivalent circuit for an HBT. It is a modified voltage controlled current source where the RC elements of the device are placed between their respective nodes. The extraction procedure for determining the model components from S-parameter measurements at different bias currents is discussed.

Figure 2.7: Hybrid-pi equivalent circuit HBT model

The device transconductance  $g_m$ , input diffusion capacitance  $C_{diff}$ , and input resistance  $R_{be}$  are given by,

$$g_m = \frac{qI_e}{\eta kT} \tag{2.6.1}$$

$$C_{diff} = g_m \cdot \tau_f \tag{2.6.2}$$

$$R_{be} = \frac{\beta}{g_m} \tag{2.6.3}$$

$\beta = \partial I_c/\partial I_b$  is used for RF modeling and determined from the low frequency value of  $h_{21}$ . From this,  $R_{ex} + R_{bb}/\beta$  and  $\eta$  can be determined at low frequencies by plotting,

$$Re(Y_{21})^{-1} = R_{ex} + \frac{R_{bb}}{\beta} + \frac{\eta kT}{qI_e}$$

(2.6.4)

for various bias currents. The intercept at  $1/I_e=0$  gives  $R_{ex}+R_{bb}/\beta$ , leaving  $\eta$  to be found from a  $Re(Y_{21})^{-1}$ ,  $1/I_e$  pair.

The collector-base conductance  $1/R_{cb}$  and total collector-base capacitance  $C_{cb}$  can be determined from the real and imaginary parts of  $Y_{12}$  from the network expression at low frequencies,

$$Y_{12} = \left(\frac{1}{R_{cb}} + \omega^2 (C_{be} + C_{cb,i}) C_{cb,i} R_{bb}\right) + j\omega (C_{cb,i} + C_{cb,ex})$$

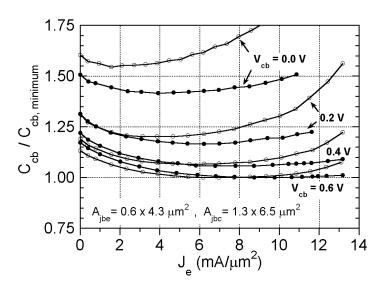

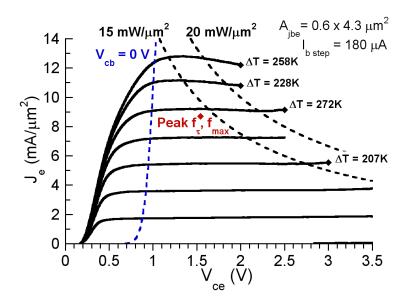

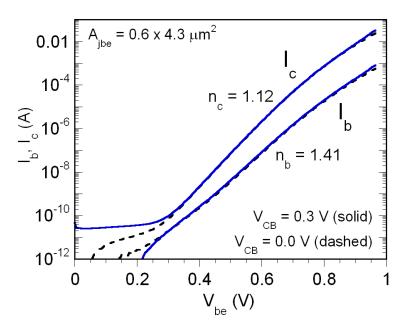

(2.6.5)