# **Table of Contents**

# Low Inductance Capacitors

| ntroduction                                                 |

|-------------------------------------------------------------|

| ow Inductance Chip Capacitors 0612/0508/0306 LICC           |

| nterDigitated Capacitors 0612/0508 IDC                      |

| ICA <sup>®</sup> Low Inductance Decoupling Capacitor Arrays |

| echnical Articles                                           |

NOTICE: Specifications are subject to change without notice. Contact your nearest AVX Sales Office for the latest specifications. All statements, information and data given herein are believed to be accurate and reliable, but are presented without guarantee, warranty, or responsibility of any kind, expressed or implied. Statements or suggestions concerning possible use of our products are made without representation or warranty that any such use is free of patent infringement and are not recommendations to infringe any patent. The user should not assume that all safety measures are indicated or that other measures may not be required. Specifications are typical and may not apply to all applications.

As switching speeds increase and pulse rise times decrease the need to reduce inductance becomes a serious limitation for improved system performance. Even the decoupling capacitors, that act as a local energy source, can generate unacceptable voltage spikes: V = L (di/dt). Thus, in high speed circuits, where di/dt can be quite large, the size of the voltage spike can only be reduced by reducing L.

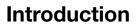

Figure 1 displays the evolution of ceramic capacitor toward lower inductance designs over the last few years. AVX has been at the forefront in the design and manufacture of these newer more effective capacitors.

Figure 1. The evolution of Low Inductance Capacitors at AVX (values given for a 100 nF capacitor of each style)

## LOW INDUCTANCE CHIP CAPACITORS

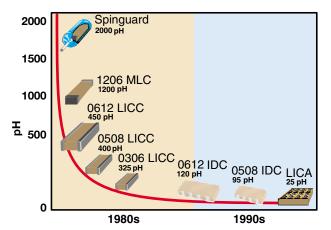

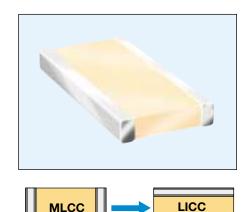

The total inductance of a chip capacitor is determined both by its length to width ratio and by the mutual inductance coupling between its electrodes. Thus a 1210 chip size has lower inductance than a 1206 chip. This design improvement is the basis of AVX's low inductance chip capacitors, LI Caps, where the electrodes are terminated on the long side of the chip instead of the short side. The 1206 becomes an 0612 as demonstrated in Figure 2. In the same manner, an 0805 becomes an 0508 and 0603 becomes an 0306. This results in a reduction in inductance from around 1200 pH for conventional MLC chips to below 400 pH for Low Inductance Chip Capacitors. Standard designs and performance of these LI Caps are given on pages 29 and 30.

Figure 2. Change in aspect ratio: 1206 vs. 0612

## **INTERDIGITATED CAPACITORS**

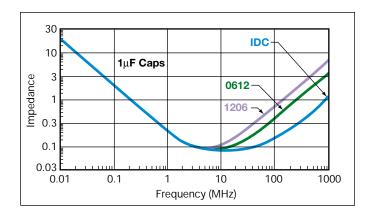

Multiple terminations of a capacitor will also help in reducing the parasitic inductance of the device. The IDC is such a device. By terminating one capacitor with 8 connections the ESL can be reduced even further. The measured inductance of the 0612 IDC is 120 pH, while the 0508 comes in around 95 pH. These FR4 mountable devices allow for even higher clock speeds in a digital decoupling scheme. Design and product offerings are shown on pages 31 and 32.

## LOW INDUCTANCE CHIP ARRAYS (LICA®)

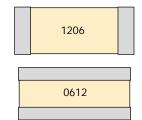

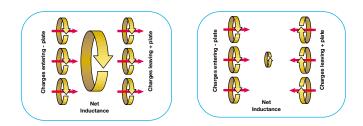

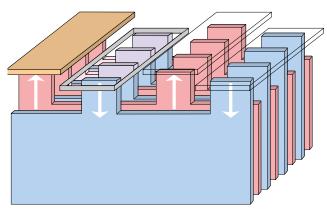

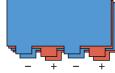

Further reduction in inductance can be achieved by designing alternative current paths to minimize the mutual inductance factor of the electrodes (Figure 3). This is achieved by AVX's LICA® product which was the result of a joint development between AVX and IBM. As shown in Figure 4, the charging current flowing out of the positive plate returns in the opposite direction along adjacent negative plates. This minimizes the mutual inductance.

The very low inductance of the LICA capacitor stems from the short aspect ratio of the electrodes, the arrangement of the tabs so as to cancel inductance, and the vertical aspect of the electrodes to the mounting surface.

Figure 3. Net Inductance from design. In the standard Multilayer capacitor, the charge currents entering and leaving the capacitor create complementary flux fields, so the net inductance is greater. On the right, however, if the design permits the currents to be opposed, there is a net cancellation, and the inductance is much lower.

# Introduction

Figure 4. LICA's Electrode/Termination Construction. The current path is minimized – this reduces self-inductance. Current flowing out of the positive plate, returns in the opposite direction along the adjacent negative plate – this reduces the mutual inductance. Also the effective current path length is minimized because the current does not have to travel the entire length of both electrodes to complete the circuit. This reduces the self inductance of the electrodes. The self inductance is also minimized by the fact that the charging current is supplied by both sets of terminals reducing the path length even further!

The inductance of this arrangement is less than 50 pH, causing the self-resonance to be above 100 MHz for the same popular 100 nF capacitance. Parts available in the LICA design are shown on pages 33 and 34.

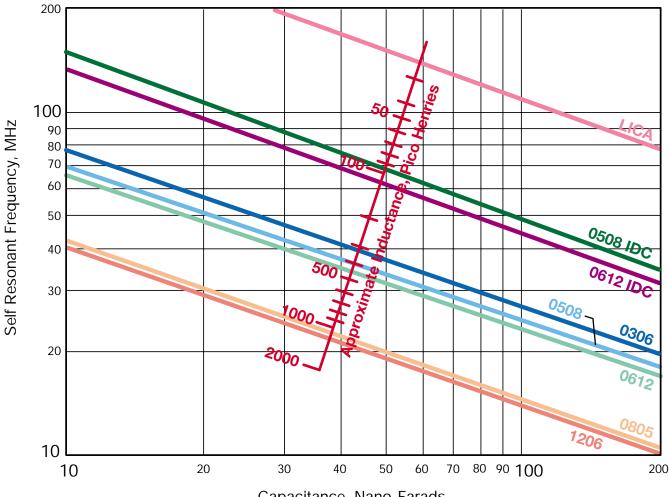

Figure 5 compares the self resonant frequencies of various capacitor designs versus capacitance values. The approximate inductance of each style is also shown.

Active development continues on low inductance capacitors. C4 termination with low temperature solder is now available for plastic packages. Consult AVX for details.

Figure 5

# 0612/0508/0306 LICC (Low Inductance Chip Capacitors)

# **GENERAL DESCRIPTION**

The total inductance of a chip capacitor is determined both by its length to width ratio and by the mutual inductance coupling between its electrodes.

Thus a 1210 chip size has a lower inductance than a 1206 chip. This design improvement is the basis of AVX's Low Inductance Chip Capacitors (LICC), where the electrodes are terminated on the long side of the chip instead of the short side. The 1206 becomes an 0612, in the same manner, an 0805 becomes an 0508, an 0603 becomes an 0306. This results in a reduction in inductance from the 1nH range found in normal chip capacitors to less than 0.4nH for LICCs. Their low profile is also ideal for surface mounting (both on the PCB and on IC package) or inside cavity mounting on the IC itself.

## **PERFORMANCE CHARACTERISTICS**

| Capacitance Tolerances                  | $K = \pm 10\%; M = \pm 20\%$                                                 |

|-----------------------------------------|------------------------------------------------------------------------------|

| Operation                               | X7R = -55°C to +125°C;                                                       |

| Temperature Range                       | X5R = -55°C to +85°C                                                         |

| Temperature Coefficient                 | ±15% (0VDC)                                                                  |

| Voltage Ratings                         | 6.3, 10, 16, 25 VDC                                                          |

| Dissipation Factor                      | 6.3V = 6.5% max; 10V = 5.0% max;<br>16V = 3.5% max; 25V = 3.0% max           |

| Insulation Resistance<br>(@+25°C, RVDC) | 100,000M $\Omega$ min, or 1,000M $\Omega$ per $\mu F$ min.,whichever is less |

# **TYPICAL INDUCTANCE**

| Package Style | Measured<br>Inductance (pH) |

|---------------|-----------------------------|

| 1206 MLCC     | 1200                        |

| 0612 LICC     | 450                         |

| 0508 LICC     | 400                         |

| 0306 LICC     | 325                         |

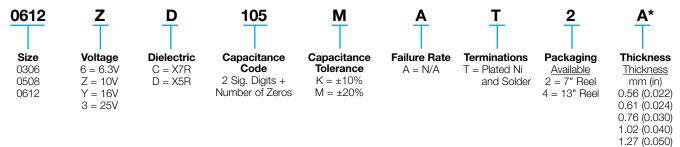

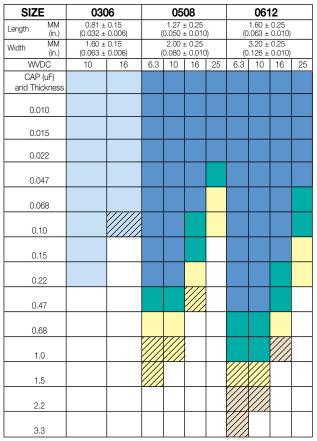

<sup>\*</sup>Note: See Range Chart for Codes

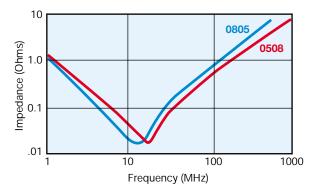

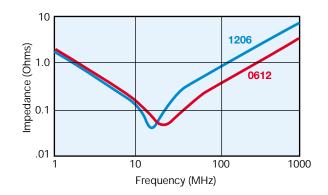

# **TYPICAL IMPEDANCE CHARACTERISTICS**

mm (in)

0612/0508/0306 LICC (Low Inductance Chip Capacitors)

#### Consult factory for additional requirements

= X5R

ſ

Code

s

A

#### Solid = X7R

mm (in.)

0306

Code Thickness

0.61 (0.024)

| mm (in.)     |      | mm (in.)     |  |  |  |  |

|--------------|------|--------------|--|--|--|--|

| )508         | 0612 |              |  |  |  |  |

| Thickness    | Code | Thickness    |  |  |  |  |

| ).56 (0.022) | S    | 0.56 (0.022) |  |  |  |  |

| ).76 (0.030) | V    | 0.76 (0.030) |  |  |  |  |

| 1.02 (0.040) | W    | 1.02 (0.040) |  |  |  |  |

|              | Α    | 1.27 (0.050) |  |  |  |  |

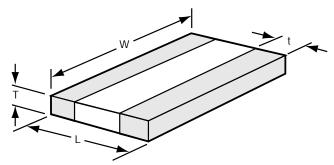

## PHYSICAL DIMENSIONS AND PAD LAYOUT

## **PHYSICAL CHIP DIMENSIONS**

|      | L                              | t                                                     |              |  |

|------|--------------------------------|-------------------------------------------------------|--------------|--|

| 0612 | 1.60 ± 0.25                    | 3.20 ± 0.25                                           | 0.13 min.    |  |

|      | (0.063 ± 0.010)                | (0.126 ± 0.010)                                       | (0.005 min.) |  |

| 0508 | 1.27 ± 0.25<br>(0.050 ± 0.010) | 2.00 ± 0.25 0.13 min.<br>(0.080 ± 0.010) (0.005 min.) |              |  |

| 0306 | 0.81 ± 0.15                    | 1.60 ± 0.15                                           | 0.13 min.    |  |

|      | (0.032 ± 0.006)                | (0.063 ± 0.006)                                       | (0.005 min.) |  |

T - See Range Chart for Thickness and Codes

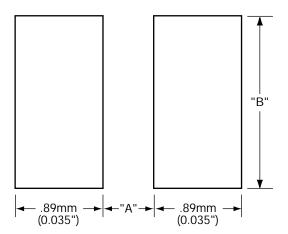

## PAD LAYOUT DIMENSIONS

|      | Α            | В            |

|------|--------------|--------------|

| 0612 | 0.76 (0.030) | 3.05 (0.120) |

| 0508 | 0.51 (0.020) | 2.03 (0.080) |

| 0306 | 0.31 (0.012) | 1.52 (0.060) |

# 0612/0508 IDC (InterDigitated Capacitors)

## **GENERAL DESCRIPTION**

- Very low equivalent series inductance (ESL), surface mountable, high speed decoupling capacitor in 0612 and 0508 case size.

- Measured inductances of 120 pH (for 0612) and 95 pH (for 0508) are the lowest in the FR4 mountable device family.

- Opposing current flow creates opposing magnetic fields. This causes the fields to cancel, effectively reducing the equivalent series inductance.

- Perfect solution for decoupling high speed microprocessors by allowing the engineers to lower the power delivery inductance of the entire system through the use of eight vias.

- Overall reduction in decoupling components due to very low series inductance and high capacitance.

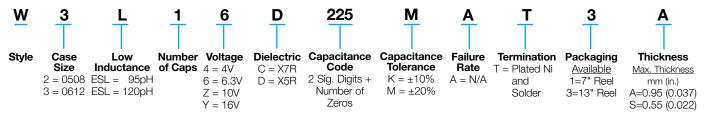

# **HOW TO ORDER**

# **PERFORMANCE CHARACTERISTICS**

| Capacitance Tolerance                   | ±20% Preferred (10% Available)                                               |

|-----------------------------------------|------------------------------------------------------------------------------|

| Operation                               | X7R = -55°C to +125°C;                                                       |

| Temperature Range                       | X5R = -55°C to +85°C                                                         |

| Temperature Coefficient                 | ±15% (0VDC)                                                                  |

| Voltage Ratings                         | 4, 6.3, 10, 16 VDC                                                           |

| Dissipation Factor                      | 4V, 6.3V = 6.5% max;                                                         |

| -                                       | 10V = 5.0% max;                                                              |

|                                         | 16V = 3.5% max                                                               |

| Insulation Resistance<br>(@+25°C, RVDC) | 100,000M $\Omega$ min, or 1,000M $\Omega$ per $\mu$ F min.,whichever is less |

| Dielectric Strength       | No problems observed after 2.5 x RVDC for 5 seconds at 50mA max current |

|---------------------------|-------------------------------------------------------------------------|

| CTE (ppm/C)               | 12.0                                                                    |

| Thermal Conductivity      | 4-5W/M K                                                                |

| Terminations<br>Available | Plated Nickel and Solder                                                |

| Max. Thickness            | 0.037" (0.95mm)                                                         |

|                           |                                                                         |

# **TYPICAL ESL AND IMPEDANCE**

| Package Style | Measured<br>Inductance (pH) |

|---------------|-----------------------------|

| 1206 MLCC     | 1200                        |

| 0612 LICC     | 450                         |

| 0612 IDC      | 120                         |

| 0508 IDC      | 95                          |

| SIZE                       |   | Thin                           | 0508           |    |   | 0                              | 508              |    |                                | Thin           | 0612 |                                | 0612                           |                       |                  |    |

|----------------------------|---|--------------------------------|----------------|----|---|--------------------------------|------------------|----|--------------------------------|----------------|------|--------------------------------|--------------------------------|-----------------------|------------------|----|

| Length MM<br>(in.)         |   | 2.03 ± 0.20<br>(0.080 ± 0.008) |                |    |   | 2.03 ± 0.20<br>(0.080 ± 0.008) |                  |    | 3.20 ± 0.20<br>(0.126 ± 0.008) |                |      |                                | 3.20 ± 0.20<br>(0.126 ± 0.008) |                       |                  |    |

| Width MM<br>(in.)          |   | 1.27 ± 0.20<br>(0.050 ± 0.008) |                |    |   | 1.27 ± 0.20<br>(0.050 ± 0.008) |                  |    | 1.60 ± 0.20<br>(0.063 ± 0.008) |                |      | 1.60 ± 0.20<br>(0.063 ± 0.008) |                                |                       |                  |    |

| Terminal MM<br>Pitch (in.) |   | 0.508 REF<br>0.020 REF         |                |    |   |                                | 08 REF<br>20 REF |    |                                | 0.76<br>0.030  |      |                                |                                | 0.76 REF<br>0.030 REF |                  |    |

| Thickness MM<br>(in.)      |   |                                | MAX.<br>) MAX. |    |   |                                | 5 MAX.<br>7) MAX |    |                                | 0.55<br>(0.022 |      |                                |                                |                       | 5 MAX.<br>7) MAX |    |

| Inductance (pH)            |   |                                | 95             |    |   |                                | 95               |    |                                | 12             | ·    |                                |                                |                       | 120              |    |

| WVDC                       | 4 | 6.3                            | 10             | 16 | 4 | 6.3                            | 10               | 16 | 4                              | 6.3            | 10   | 16                             | 4                              | 6.3                   | 10               | 16 |

| CAP (uF)<br>and Thickness  |   |                                |                |    |   |                                |                  |    |                                |                |      |                                |                                |                       |                  |    |

| 0.047                      |   |                                |                |    |   |                                |                  |    |                                |                |      |                                |                                |                       |                  |    |

| 0.068                      |   |                                |                |    |   |                                |                  |    |                                |                |      |                                |                                |                       |                  |    |

| 0.10                       |   |                                |                |    |   |                                |                  |    |                                |                |      |                                |                                |                       |                  |    |

| 0.22                       |   |                                |                |    |   |                                |                  |    |                                |                |      |                                |                                |                       |                  |    |

| 0.33                       |   |                                |                |    |   |                                |                  |    |                                |                |      |                                |                                |                       |                  |    |

| 0.47                       |   |                                |                |    |   |                                |                  |    |                                |                |      |                                |                                |                       |                  |    |

| 0.68                       |   |                                |                |    |   |                                |                  |    |                                |                |      |                                |                                |                       |                  |    |

| 1.0                        |   |                                |                |    |   |                                |                  |    |                                |                |      |                                |                                |                       |                  |    |

| 1.5                        |   |                                |                |    |   |                                |                  |    |                                |                |      |                                |                                |                       |                  |    |

| 2.2                        |   |                                |                |    |   |                                |                  |    |                                |                |      |                                |                                |                       |                  |    |

| 3.3                        |   |                                |                |    |   |                                |                  |    |                                |                |      |                                |                                |                       |                  |    |

Consult factory for additional requirements

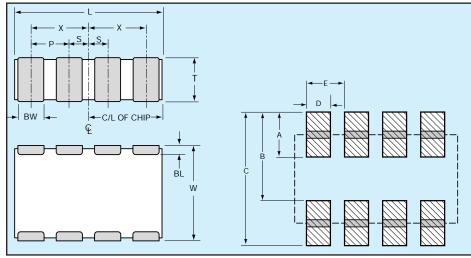

# PHYSICAL DIMENSIONS AND PAD LAYOUT

# PHYSICAL CHIP DIMENSIONS millimeters (inches)

### 0612

| L                              | W                              | BW                             | BL                                                                   | Р                       | Х                              | S                              |

|--------------------------------|--------------------------------|--------------------------------|----------------------------------------------------------------------|-------------------------|--------------------------------|--------------------------------|

| 3.20 ± 0.20<br>(0.126 ± 0.008) | 1.60 ± 0.20<br>(0.063 ± 0.008) | 0.41 ± 0.10<br>(0.016 ± 0.004) | $\substack{0.18 \ ^{+0.25}_{-0.08} \\ (0.007 \ ^{+0.010}_{-0.003})}$ | 0.76 REF<br>(0.030 REF) | 1.14 ± 0.10<br>(0.045 ± 0.004) | 0.38 ± 0.10<br>(0.015 ± 0.004) |

### 0508

| L                          | W                          | BW                          | BL                                              | Р                        | Х                          | S                            |

|----------------------------|----------------------------|-----------------------------|-------------------------------------------------|--------------------------|----------------------------|------------------------------|

| 2.03±0.20<br>(0.080±0.008) | 1.27±0.20<br>(0.050±0.008) | 0.254±0.10<br>(0.010±0.004) | 0.18 +0.25<br>-0.08<br>(0.007 +0.010<br>-0.003) | 0.508 REF<br>(0.020 REF) | 0.76±0.10<br>(0.030±0.004) | 0.254±0.10<br>(0.010±.0.004) |

## PAD LAYOUT DIMENSIONS 0612

| 0012            |                 |                 |                 |                 |  |

|-----------------|-----------------|-----------------|-----------------|-----------------|--|

| Α               | В               | С               | D               | Е               |  |

| 0.89<br>(0.035) | 1.65<br>(0.065) | 2.54<br>(0.100) | 0.46<br>(0.018) | 0.76<br>(0.030) |  |

# 0508

| Α       | В       | С       | D       | Е       |

|---------|---------|---------|---------|---------|

| 0.64    | 1.27    | 1.91    | 0.28    | 0.51    |

| (0.025) | (0.050) | (0.075) | (0.011) | (0.020) |

# LICA® (Low Inductance Decoupling Capacitor Arrays)

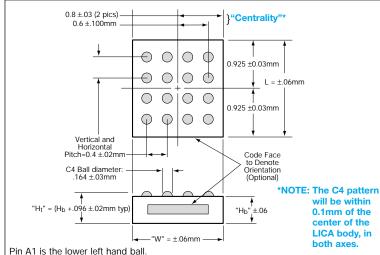

LICA<sup>®</sup> arrays utilize up to four separate capacitor sections in one ceramic body (see Configurations and Capacitance Options). These designs exhibit a number of technical advancements:

Low Inductance features-

Low resistance platinum electrodes in a low aspect ratio pattern Double electrode pickup and perpendicular current paths C4 "flip-chip" technology for minimal interconnect inductance

> facing up A = 2"x2" Black Waffle Pack w/ termination facing up C = 4"x4" Waffle Pack w/ clear lid

### **HOW TO ORDER**

| LICA  | 3       | Ţ          | 183            | M              | 3           | F               | C                      | 4         | A               | A             |

|-------|---------|------------|----------------|----------------|-------------|-----------------|------------------------|-----------|-----------------|---------------|

| Style | Voltage | Dielectric | Cap/Section    | Capacitance    | Height      | Termination     | Reel Packaging         | # of      | Inspection      | Code          |

| &     | 25V = 3 | T = T55T   | (EIA Code)     | Tolerance      | Code        | F = C4 Solder   | M = 7" Reel            | Caps/Part | Code            | Face          |

| Size  | 50V = 5 | S = High K | 102 = 1000  pF | $M = \pm 20\%$ | 1 = 0.875mm | Balls- 97Pb/3Sn | R = 13" Reel           | 1 = one   | A = Standard    | A = Bar       |

|       |         | T55T       | 103 = 10 nF    | P = GMV        | 3 = 0.650mm | P = Cr-Cu-Au    | 6 = 2"x2" Waffle Pack  | 2 = two   | B = Established | B = No Bar    |

|       |         |            | 104 = 100 nF   |                | 5 = 1.100mm | N = Cr-Ni-Au    | 8 = 2"x2" Black Waffle | 4 = four  | Reliability     | C = Dot, S55S |

|       |         |            |                |                | 7 = 1.600mm | X = None        | Pack                   |           | Testing         | Dielectrics   |

|       |         |            |                |                |             |                 | 7 = 2"x2" Waffle Pack  |           | -               |               |

|       |         |            |                |                |             |                 | w/ termination         |           |                 |               |

#### TABLE 1

| <b>T55T</b>       | Units                                                                                    |

|-------------------|------------------------------------------------------------------------------------------|

| Со                | Nanofarads                                                                               |

| 1.4 x Co          | Nanofarads                                                                               |

| Со                | Nanofarads                                                                               |

| 12                | Percent                                                                                  |

| 0.2               | Ohms                                                                                     |

| 2.0               | Megaohms                                                                                 |

| 500               | Volts                                                                                    |

| 8.5               | ppm/°C 25-100°                                                                           |

| 15 to 120         | Pico-Henries                                                                             |

| DC to 5 Gigahertz |                                                                                          |

| -55° to 125°C     |                                                                                          |

|                   | Co<br>1.4 x Co<br>Co<br>12<br>0.2<br>2.0<br>500<br>8.5<br>15 to 120<br>DC to 5 Gigahertz |

### **C4 AND PAD DIMENSIONS**

| Code<br>(Body Height) | Width<br>(W) | Length<br>(L) | Height<br>Body (H <sub>b</sub> ) |  |

|-----------------------|--------------|---------------|----------------------------------|--|

| 1                     | 1.600mm      | 1.850mm       | 0.875mm                          |  |

| 3                     | 1.600mm      | 1.850mm       | 0.650mm                          |  |

| 5                     | 1.600mm      | 1.850mm       | 1.100mm                          |  |

| 7                     | 1.600mm      | 1.850mm       | 1.600mm                          |  |

# TERMINATION OPTIONS

### C4 SOLDER (97% Pb/3% Sn) BALLS

### **TERMINATION OPTION P OR N**

LICA® (Low Inductance Decoupling Capacitor Arrays)

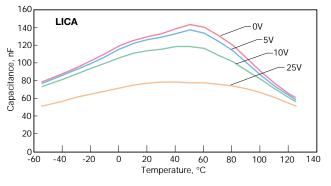

# LICA® TYPICAL PERFORMANCE CURVES

Effect of Bias Voltage and Temperature on a 130 nF LICA® (T55T)

# LICA VALID PART NUMBER LIST

| Part Number      | Voltage | Thickness (mm) | Capacitors per<br>Package |

|------------------|---------|----------------|---------------------------|

| LICA3T183M3FC4AA | 25      | 0.650          | 4                         |

| LICA3T143P3FC4AA | 25      | 0.650          | 4                         |

| LICA3T134M1FC1AA | 25      | 0.875          | 1                         |

| LICA3T104P1FC1AA | 25      | 0.875          | 1                         |

| LICA3T253M1FC4AA | 25      | 0.875          | 4                         |

| LICA3T203P1FC4AA | 25      | 0.875          | 4                         |

| LICA3T204M5FC1AA | 25      | 1.100          | 1                         |

| LICA3T164P5FC1AA | 25      | 1.100          | 1                         |

| LICA3T304M7FC1AB | 25      | 1.600          | 1                         |

| LICA3T244P7FC1AB | 25      | 1.600          | 1                         |

| LICA5T802M1FC4AB | 50      | 0.875          | 4                         |

| LICA5T602P1FC4AB | 50      | 0.875          | 4                         |

| Extended Range   |         |                |                           |

| LICA3T104M3FC1A  | 25      | 0.650          | 1                         |

| LICA3T803P3FC1A  | 25      | 0.650          | 1                         |

| LICA3T503M3FC2A  | 25      | 0.650          | 2                         |

| LICA3T403P3FC2A  | 25      | 0.650          | 2                         |

| LICA3S213M3FC4A  | 25      | 0.650          | 4                         |

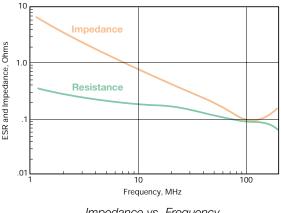

Impedance vs. Frequency

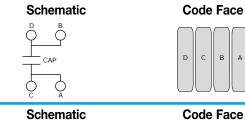

## **CONFIGURATION**

С в Α

B1 Ç Q B2 CAP 2 Q Ċ Ċ C

Schematic B1 D2 Ç Q AP 2 Ċ Ó A2  $O_{C2}$ D3 Р D4 Ç CAP 3 Ċ

**Code Face**

| D1 C1 | )<br>(B1) | (A1) |

|-------|-----------|------|

| D2 C2 | ) (B2)    | (A2) |

| D3 C3 | ) (ВЗ)    | (A3) |

| D4 C4 | )(в4)     | A4   |

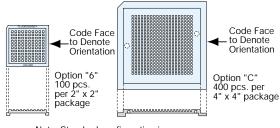

# WAFFLE PACK OPTIONS FOR LICA®

Note: Standard configuration is Termination side down

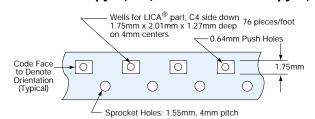

## LICA® PACKAGING SCHEME "M" AND "R"

8mm conductive plastic tape on reel: "M"=7" reel max. qty. 3,000, "R"=13" reel max. qty. 8,000

# **Technical Articles**

# TO DOWNLOAD ANY OF THESE COMPLETE TECHNICAL ARTICLES VISIT OUR WEBSITE AT: http://www.avxcorp.com

## **DECOUPLING: BASICS**

By Arch Martin AVX Corporation Myrtle Beach, SC

This paper discusses the characteristics of multilayer ceramic capacitors in decoupling applications and compares their performance with other types of decoupling capacitors. A special high-frequency test circuit is described and the results obtained using various types of capacitors are shown.

http://www.avxcorp.com/docs/techinfo/dcplbsc.pdf

### FUNCTIONAL TESTING OF DECOUPLING CAPACITORS FOR DYNAMIC RAMS

| By Arch G. Martin | Ward Parkinson          |

|-------------------|-------------------------|

| AVX Corporation   | Micron Technology, Inc. |

| Myrtle Beach, SC  | Boise, Idaho            |

Comparative performance of various types of distributed decoupling capacitors both with and without bulk tantalum capacitors is shown under actual operating conditions in a 64K dynamic RAM memory board designed especially for high-frequency in-use testing. Multilayer ceramic capacitors are shown to be effective and economical even without using bulk tantalum capacitors for decoupling.

http://www.avxcorp.com/docs/techinfo/dynamic.pdf

### IMPROVED NOISE SUPPRESSION VIA MULTILAYER CERAMIC CAPACITORS (MLCs) IN POWER-ENTRY DECOUPLING

| By Arch G. Martin | R. Kenneth Keenan |

|-------------------|-------------------|

| AVX Corporation   | TKC               |

| Myrtle Beach, SC  | Pinellas Park, FL |

A new decoupling technique is proposed for surface mounted designs that recommends using 0.1  $\mu$ F MLCs as the circuit-level decoupling capacitors and 1.0  $\mu$ F to 10  $\mu$ F MLCs in place of the tantalum as the board-level power-entry capacitor. This combination of MLCs on each PCB coupled with a single system

level tantalum or aluminum is probably an optimum arrangement; performance is enhanced, and cost is not increased.

http://www.avxcorp.com/docs/techinfo/supvmlc.pdf

### INDUCTANCE MEASUREMENTS FOR MULTI-TERMINAL DEVICES

By Ben Smith AVX Corporation 801 17th Avenue South Myrtle Beach, SC 29578

New innovations in both the telecommunication industry as well as the computer industry have mandated a need for using low inductance capacitive devices in power supply decoupling applications. With this being the case, different concepts for the construction of these devices have recently been the key to the success of reaching inductances of less than 50pH. There is, however, a significant bottleneck to the new innovation process due to measurement techniques. Most of the newer devices are using techniques such as multi-path current flow, short length, and equal and opposite current injection techniques to achieve low inductance levels. Also, coupled with these new designs is the need for higher energy storage capabilities and thus more capacitance. All of these effects are presenting more complex tasks in the measurement process. This paper gives both a generic approach for measurement as well as an exact approach specifically for the Interdigitated (IDC) type devices.

http://www.avxcorp.com/docs/techinfo/immtd.pdf

# TO DOWNLOAD ANY OF THESE COMPLETE TECHNICAL ARTICLES VISIT OUR WEBSITE AT: http://www.avxcorp.com

#### INTERCONNECT SCHEMES FOR LOW INDUCTANCE CERAMIC CAPACITORS

By Jeff Cain, Ph.D. AVX Corporation Myrtle Beach, SC 29578 (843) 946-0484

As digital electronic systems continue to operate at higher and higher frequencies, the use of low inductance decoupling capacitors continues to increase. The parasitic inductance of the devices themselves is important, but the method used to connect the components to the system, such as printed circuit boards (PCB), is also a considerable factor. Adding inductance in the connection scheme can eliminate some of the effectiveness of the use of these low inductance elements. This paper will examine some of the different schemes utilized at the board level to minimize the loop inductance of the decoupling capacitors.

http://www.avxcorp.com/docs/techinfo/intercs.pdf

### INTRODUCTION TO CHOOSING MLC CAPACITORS FOR BYPASS/DECOUPLING APPLICATIONS

By Yun Chase AVX Corporation 801 17th Avenue South Myrtle Beach, SC 29577

Methods to ensure *signal integrity* using decoupling capacitors have been the topic of many papers in the past as well as in the present. One can find equally many methods of decoupling as well. This paper will illustrate one of these established methods and introduce it in a *theoretical* sense using the most simplistic of terms. The paper will also describe the methods of the past (in slow speed systems) and the practices of the present (in high speed systems).

http://www.avxcorp.com/docs/techinfo/mlcbypas.pdf

# LOW INDUCTANCE CAPACITORS FOR DIGITAL CIRCUITS

By John Galvagni AVX Corporation Myrtle Beach, SC

Ceramic capacitors have become one of the limiting factors in digital circuits because of intrinsic characteristics such as equivalent series resistance and inductance. There are many things which could be done to mitigate that, and we describe some of those in this paper. AVX's DCAP capacitor, (developed with and for IBM) is used as a benchmark to show how much can be done to improve the situation. We compare and contrast that part to those currently available.

http://www.avxcorp.com/docs/techinfo/LI\_TI.pdf

## PARASITIC INDUCTANCE OF MULTILAYER CERAMIC CAPACITORS

By Jeff Cain, Ph.D. AVX Corporation

The parasitic inductance of multilayer ceramic capacitors (MLCCs) is becoming more important in the decoupling of high speed digital systems. There exists conflicting data and statements on the parasitic inductance of the MLCC. This work shows the measurement techniques of the inductance parameters, focusing mainly on the fixturing needed to accurately measure the chips. The effects of various compensation and calibration methods will also be demonstrated. A comprehensive table will be shown that includes the parasitic inductance for a range of MLCCs from 0402 through 1210.

New, more recent data supports the conclusions of this study, however they prove the original data in this article to be inaccurate. New data shown in this catalog is believed to be true but is subject to measure and test fixture accuracy.

http://www.avxcorp.com/docs/techinfo/parasitic.pdf

# TO DOWNLOAD ANY OF THESE COMPLETE TECHNICAL ARTICLES VISIT OUR WEBSITE AT: http://www.avxcorp.com

### PE SERIES CAPACITORS DECOUPLING AND/OR FILTERING

By John D. Prymak AVX Corporation

Decoupling is a means of eliminating or reducing those elements which restrict high speed operations. Filtering is driven by two considerations - emission and susceptance. The noise generated in high speed digital operations may need to be reduced, to achieve accepted levels of emission to prevent interference with other systems. Also, the system itself may have its distinct level of noise tolerance which would require filtering selected inputs to maintain integrity of the logic circuit operations. The solution to a decoupling problem may assist filtering, and vice versa; but, the optimum solution to either is not the optimum solution for the other. The PE devices were originally designed for filtering, and then were later designed for decoupling. The application defines the requirement and the optimum design.

http://www.avxcorp.com/docs/techinfo/peseries.pdf

### So many electrons, so little time... THE NEED FOR LOW INDUCTANCE CAPACITORS

By John Galvagni, Sara Randall, Paul Roughan and Allen Templeton AVX Corporation 17th Ave. South Myrtle Beach, SC 29578

High di/dt ratios, large current pulses over short times, are an inevitable part of today's fast electronic circuitry. They can cause high voltage spikes when passing through paths that have inductance. The task of the designer then, is to have high energies available, but not the associated voltage excursions, by reducing the total inductance. Eliminating wire bonds, reducing path lengths, and using low inductance components is the regimen. This paper describes the availability of capacitors that can go a long way to providing the energies needed, but simultaneously, lower the intrinsic inductance it contributes. We will review the source of the inductance, the current components available, and other advances that will give the designer a more useful menu.

http://www.avxcorp.com/docs/techinfo/needli.pdf

## THE EFFECTS OF ESR AND ESL IN DIGITAL DECOUPLING APPLICATIONS

By Jeff Cain, Ph.D. AVX Corporation

It is common place for digital integrated circuits to operate at switching frequencies of 100 MHz and above, even at the circuit board level. As these frequencies continue to increase, the parasitic of the decoupling capacitors must be considered. A study on the effects of equivalent series resistance (ESR) and equivalent series inductance (ESL) in a typical digital decoupling application is presented. Utilizing SPICE, it can be shown that the ESR and ESL of chip capacitors can dramatically alter the voltage seen by the integrated circuit (IC) By changing the values of the parasitics and comparing the results to the ideal case for a variety of frequencies, some common decoupling design rules are formulated.

http://www.avxcorp.com/docs/techinfo/esr\_esl.pdf

## USA

AVX Myrtle Beach, SC Corporate Offices Tel: 843-448-9411 FAX: 843-626-5292

AVX Northwest, WA Tel: 360-669-8746 FAX: 360-699-8751

AVX North Central, IN Tel: 317-848-7153 FAX: 317-844-9314

AVX Mid/Pacific, MN Tel: 952-974-9155 FAX: 952-974-9179

AVX Southwest, AZ Tel: 480-539-1496 FAX: 480-539-1501

AVX South Central, TX Tel: 972-669-1223 FAX: 972-669-2090

AVX Southeast, NC Tel: 919-878-6357 FAX: 919-878-6462

AVX Canada Tel: 905-564-8959 FAX: 905-564-9728 EUROPE

AVX Limited, England European Headquarters Tel: ++44 (0) 1252 770000 FAX: ++44 (0) 1252 770001

AVX S.A., France Tel: ++33 (1) 69.18.46.00 FAX: ++33 (1) 69.28.73.87

AVX GmbH, Germany - AVX Tel: ++49 (0) 8131 9004-0 FAX: ++49 (0) 8131 9004-44

AVX GmbH, Germany - Elco Tel: ++49 (0) 2741 2990 FAX: ++49 (0) 2741 299133

AVX srl, Italy Tel: ++390 (0)2 614571 FAX: ++390 (0)2 614 2576

AVX Czech Republic, s.r.o. Tel: ++420 (0)467 558340 FAX: ++420 (0)467 558345

# ASIA-PACIFIC

AVX/Kyocera, Singapore Asia-Pacific Headquarters Tel: (65) 258-2833

FAX: (65) 350-4880

AVX/Kyocera, Hong Kong Tel: (852) 2-363-3303 FAX: (852) 2-765-8185

> AVX/Kyocera, Korea Tel: (82) 2-785-6504 FAX: (82) 2-784-5411

AVX/Kyocera, Taiwan Tel: (886) 2-2696-4636 FAX: (886) 2-2696-4237

AVX/Kyocera, China Tel: (86) 21-6249-0314-16 FAX: (86) 21-6249-0313

AVX/Kyocera, Malaysia Tel: (60) 4-228-1190 FAX: (60) 4-228-1196

> Elco, Japan Tel: 045-943-2906/7 FAX: 045-943-2910

Kyocera, Japan - AVX Tel: (81) 75-604-3426 FAX: (81) 75-604-3425

Kyocera, Japan - KDP Tel: (81) 75-604-3424 FAX: (81) 75-604-3425

Contact: