# Verilog Tutorial

25-Oct-2003 Deepak Kumar Tala

Comments :<u>deeps@deeps.org</u> Website : <u>http://www.deeps.org</u>

## Index

- Introduction.

- History of Verilog.

- Design and Tool Flow.

- My First Program in Verilog.

- Verilog HDL Syntax and Semantics.

- Verilog Gate Level Modeling Tutorial.

- Verilog Operators.

- Verilog behavioral modeling.

- Procedural Timing Controls.

- Tasks and Function.

- System Tasks and Functions.

- Art of writing test benches.

- Werilog Tutorial on Modeling Memories and FSM.

- Parameterized Modules.

- Verilog Synthesis Tutorial.

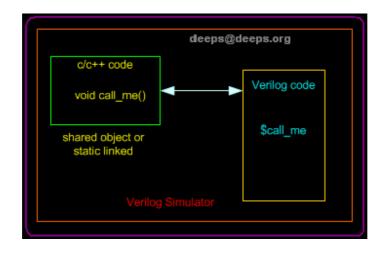

- Verilog PLI Tutorial ? : 20% Complete

- What's new in Verilog 2001? : 50% Complete

- Werilog Quick Reference.

- Verilog in One Day : This tutorial is in bit lighter sense, with humor, So take it cool and enjoy.

## **INTRODUCTION**

#### Introduction.

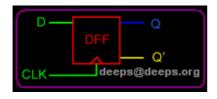

Verilog is a HARDWARE DESCRIPTION LANGUAGE (HDL). A hardware description Language is a language used to describe a digital system, for example, a microprocessor or a memory or a simple flip-flop. This just means that, by using a HDL one can describe any hardware (digital ) at any level.

module d\_ff ( d, clk, q, q\_bar); input d ,clk; ouput q, q\_bar;

always @ (posedge clk) begin q <= d; q\_bar <= !d; end endmodule

One can describe a simple Flip flop as that in above figure as well as one can describe a complicated designs having 1 million gates. Verilog is one of the HDL languages available in the industry for designing the Hardware. Verilog allows us to design a Digital design at Behavior Level, Register Transfer Level (RTL), Gate level and at switch level. Verilog allows hardware designers to express their designs with behavioral constructs, deterring the details of implementation to a later stage of design in the final design.

Many engineers who want to learn Verilog, most often ask this question, how much time it will take to learn Verilog?, Well my answer to them is " It may not take more then one week, if you happen to know at least one programming language".

#### Design Styles

Verilog like any other hardware description language, permits the designers to design a design in either Bottom-up or Top-down methodology.

#### Notion-Up Design

The traditional method of electronic design is bottom-up. Each design is performed at the gate-level using the standard gates (Refer to the Digital

Section for more details) With increasing complexity of new designs this approach is nearly impossible to maintain. New systems consist of ASIC or microprocessors with a complexity of thousands of transistors. These traditional bottom-up designs have to give way to new structural, hierarchical design methods. Without these new design practices it would be impossible to handle the new complexity.

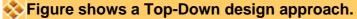

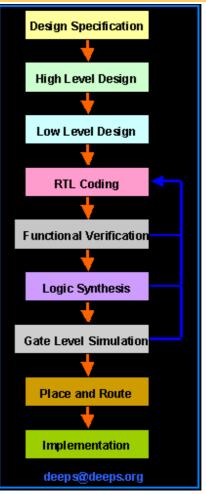

#### 🗞 Top-Down Design

The desired design-style of all designers is the top-down design. A real topdown design allows early testing, easy change of different technologies, a structured system design and offers many other advantages. But it is very difficult to follow a pure top-down design. Due to this fact most designs are mix of both the methods, implementing some key elements of both design styles.

Verilog supports a design at many different levels of abstraction. Three of them are very important:

- ? Behavioral level

- ? Register-Transfer Level

- ? Gate Level

#### 🗞 Behavioral level

This level describes a system by concurrent algorithms (Behavioral). Each algorithm itself is sequential, that means it consists of a set of instructions that are executed one after the other. Functions, Tasks and Always blocks are the main elements. There is no regard to the structural realization of the design.

#### Register-Transfer Level

Designs using the Register-Transfer Level specify the characteristics of a circuit by operations and the transfer of data between the registers. An explicit clock is used. RTL design contains exact timing possibility, operations are scheduled to occur at certain times. Modern definition of a RTL code is **"Any code that is synthesizable is called RTL code".**

#### 🎨 Gate Level

Within the logic level the characteristics of a system are described by logical links and their timing properties. All signals are discrete signals. They can only have definite logical values (`0', `1', `X', `Z`). The usable operations are predefined logic primitives (AND, OR, NOT etc gates). Using gate level modeling might not be a good idea for any level of logic design. Gate level code is generated by tools like synthesis tools and this netlist is used for gate level simulation and for backend.

# **History of Verilog**

Verilog was started initially as a proprietary hardware modeling language by Gateway Design Automation Inc. around 1984. It is rumored that the original language was designed by taking features from the most popular HDL language of the time, called HiLo as well as from traditional computer language such as C. At that time, Verilog was not standardized and the language modified itself in almost all the revisions that came out within 1984 to 1990.

Verilog simulator was first used beginning in 1985 and was extended substantially through 1987. The implementation was the Verilog simulator sold by Gateway. The first major extension was Verilog-XL, which added a few features and implemented the infamous "XL algorithm" which was a very efficient method for doing gate-level simulation.

The time was late 1990. Cadence Design System, whose primary product at that time included Thin film process simulator, decided to acquire Gateway Automation System. Along with other Gateway product, Cadence now became the owner of the Verilog language, and continued to market Verilog as both a language and a simulator. At the same time, Synopsys was marketing the top-down design methodology, using Verilog. This was a powerful combination.

In 1990, Cadence recognized that if Verilog remained a closed language, the pressures of standardization would eventually cause the industry to shift to VHDL. Consequently, Cadence organized Open Verilog International (OVI), and in 1991 gave it the documentation for the Verilog Hardware Description Language. This was the event which "opened" the language.

OVI did a considerable amount of work to improve the Language Reference Manual (LRM), clarifying things and making the language specification as vendor-independent as possible.In 1990.

Soon it was realized, that if there were too many companies in the market for Verilog, potentially everybody would like to do what Gateway did so far - changing the language for their own benefit. This would defeat the main purpose of releasing the language to public domain. As a result in 1994, the IEEE 1364 working group was formed to turn the OVI LRM into an IEEE standard. This effort was concluded with a successful ballot in 1995, and Verilog became an IEEE standard in December, 1995.

When Cadence gave OVI the LRM, several companies began working on Verilog simulators. In 1992, the first of these were announced, and by 1993 there were several Verilog simulators available from companies other than Cadence. The

most successful of these was VCS, the Verilog Compiled Simulator, from Chronologic Simulation. This was a true compiler as opposed to an interpreter, which is what Verilog-XL was. As a result, compile time was substantial, but simulation execution speed was much faster.

In the meantime, the popularity of Verilog and PLI was rising exponentially. Verilog as a HDL found more admirers than well-formed and federally funded VHDL. It was only a matter of time before people in OVI realized the need of a more universally accepted standard. Accordingly, the board of directors of OVI requested IEEE to form a working committee for establishing Verilog as an IEEE standard. The working committee 1364 was formed in mid 1993 and on October 14, 1993, it had its first meeting.

The standard, which combined both the Verilog language syntax and the PLI in a single volume, was passed in May 1995 and now known as IEEE Std. 1364-1995.

After many years, new features have been added to Verilog, and new version is called Verilog 2001. This version seems to have fixed lot of problems that Verilog 1995 had. This version is called 1364-2000. Only waiting now is that all the tool vendors implementing it.

# **DESIGN AND TOOL FLOW**

#### Introduction

Being new to Verilog you might want to try some examples and try designing something new. I have listed the tool flow that could be used to achieve this. I have personally tried this flow and found this to be working just fine for me. Here I have taken only front end design part of the tool flow and bit of FPGA design flow that can be done without any fat money spent on tools. If you have any suggestions or questions please don't hesitate to mail me. (Note : I have missed steps in P&R, Will add then shortly)

#### Service Stages of ASIC/FPGA

- ? Specification : Word processor like Word, Kwriter, AbiWord

- ? High Level Design : Word processor like Word, Kwriter, AbiWord, for drawing waveform use tools like waveformer or testbencher or Word.

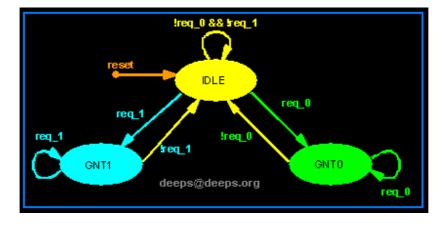

- ? **Micro Design/Low level design:** Word processor like Word, Kwriter, AbiWord, for drawing waveform use tools like waveformer or testbencher or Word. For FSM StateCAD or some similar tool.

- ? RTL Coding : Vim, Emacs, conTEXT, HDL TurboWriter

- ? Simulation : Modelsim, VCS, Verilog-XL, Veriwell, Finsim, iVerilog, VeriDOS.

- ? Synthesis : Design Compiler, FPGA Compiler, Synplify, Leonardo Spectrum. You can download this from FPGA vendors like Altera and Xilinx for free.

- ? Place & Route : For FPGA use FPGA' vendors P&R tool. ASIC tools require expensive P&R tools like Apollo. Students can use LASI, Magic.

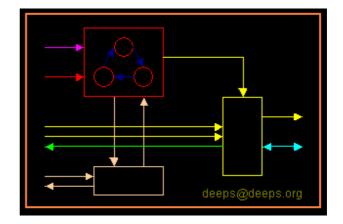

Figure : Typical Design flow

#### Specification

This is the stage at which we define what are the important parameters of the system/design that you are planning to design. Simple example would be, like I want to design a counter, it should be 4 bit wide, should have synchronous reset, with active high enable and reset signal, When reset is active, counter output should go to "0". You can use Microsoft Word, or GNU Abiword or Openoffice for entering the specification.

#### 🗞 High Level Design

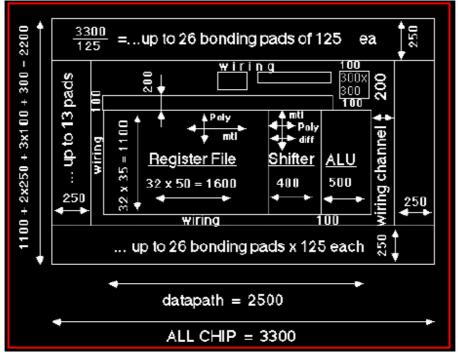

This is the stage at which you define various blocks in the design and how they communicate. Lets assume that we need to design microprocessor, High level design means splitting the design into blocks based on their function, In our case various blocks are registers, ALU, Instruction Decode, Memory Interface, etc. You can use Microsoft Word, or KWriter or Abiword or Openoffice for entering high level design.

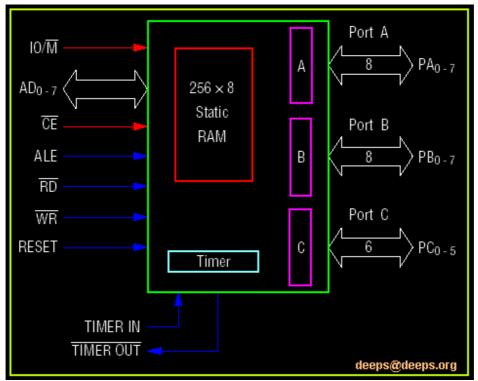

Figure : 18155 High Level Block Diagram

#### Nicro Design/Low level design

Low level design or Micro design is the phase in which, designer describes how each block is implemented. It contains details of State machines, counters, Mux, decoders, internal registers. For state machine entry you can use either Word, or special tools like StateCAD. It is always a good idea if waveform is drawn at various interfaces.

# Figure : Sample Low level design

In RTL coding, Micro Design is converted into Verilog/VHDL code, using synthesizable constructs of the language. Normally we use vim editor, but I prefer conTEXT and Nedit editor, it all depends on which editor you like. Some use Emacs.

| Figure | : Sam | ple RTL | code |

|--------|-------|---------|------|

|--------|-------|---------|------|

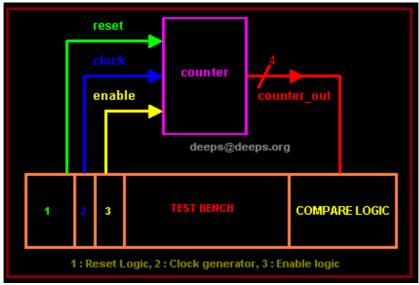

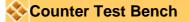

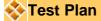

Simulation is the process of verifying the functional characteristics of models at any level of abstraction. We use simulators to simulate the the Hardware models. To test if the RTL code meets the functional requirements of the specification, see if all the RTL blocks are functionally correct. To achieve this we need to write testbench, which generates clk, reset and required test vectors. A sample testbench for a counter is as shown below.

Figure : Sample Testbench Env

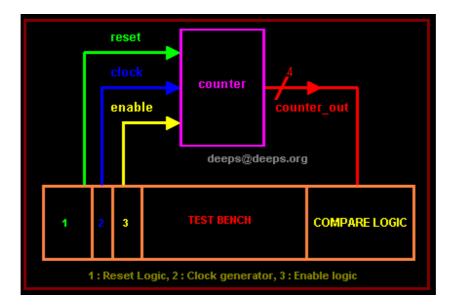

We use waveform output from the simulator to see if the DUT (Device Under Test) is functionally correct. Most of the simulators comes with waveform viewer, As design becomes complex, we write self checking testbench, where testbench applies the test vector, compares the output of DUT with expected value.

There is another kind of simulation, called *timing simulation*, which is done after synthesis or after P&R (Place and Route). Here we include the gate delays and wire delays and see if DUT works at rated clock speed. This is also called as *SDF simulation* or *gate simulation*.

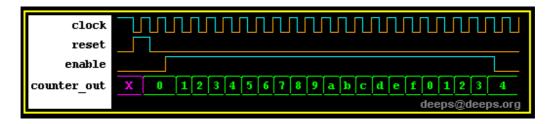

#### Figure : 4 bit Up Counter Waveform

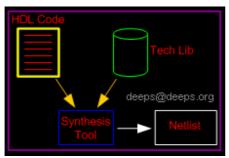

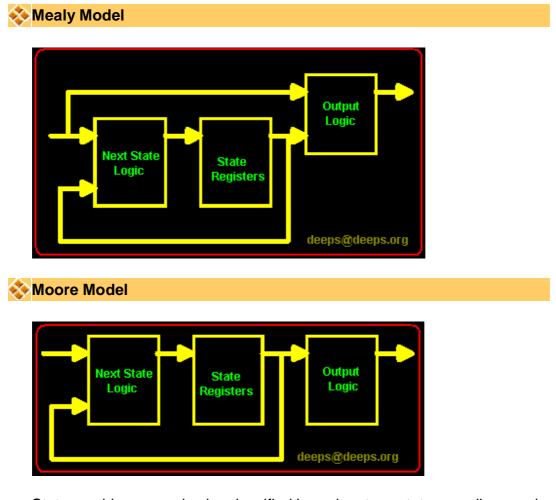

## 🗞 Synthesis

Synthesis is process in which synthesis tool like design compiler or Synplify takes the RTL in Verilog or VHDL, target technology, and constrains as input and maps the RTL to target technology primitives. Synthesis tool after mapping the RTL to gates, also do the minimal amount of timing analysis to see if the mapped design meeting the timing requirements. (Important thing to note is, synthesis tools are not aware of wire delays)

**Figure : Synthesis Flow**

Figure : Synthesis output

## Place & Route

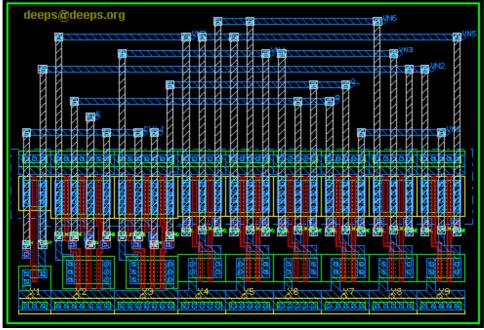

Figure : Sample micro-processor placement

Figure : J-K Flip-Flop Note : Under construction, please feel free to send your comments

# My first program in Verilog

#### Introduction

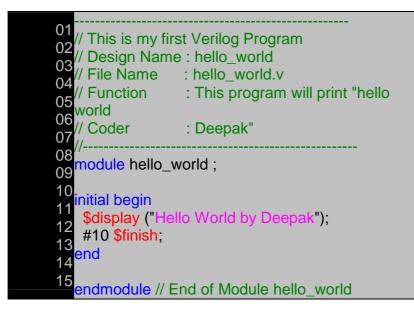

If you refer to any book on programming language it starts with "hello World" program, once you have written the program, you can be sure that

you can do something in that language

Well I am also going to show how to write a "hello world" program in Verilog, followed by "counter" design in Verilog.

#### Hello World Program

Words in green are comments, blue are reserved words, Any program in Verilog starts with reserved word module <module\_name>, In the above example line 7 contains module hello\_world;

Line 9 contains the initial block, this block gets executed only once after the simulation starts and at time=0 (0ns). This block contains two statements, which are enclosed with in begin at line 7 and end at line 12. In Verilog if you have multiple lines within a block, you need to use begin and end.

Hello World Program Output

C:\www.deeps.org>veridos hello\_world.v VeriWell for Win32 HDL <Version 2.1.4> Sun Nov 04 17:52:38 2001 This is a free version of the VeriWell for Win32 Simulator Distribute this freely; call 1-800-VERIWELL for ordering information See the file "!readme.1st" for more information

Copyright (c) 1993-97 Wellspring Solutions, Inc. All rights reserved

Memory Available: 0 Entering Phase I... Compiling source file : hello\_world.v The size of this model is [0%, 1%] of the capacity of the free version

Entering Phase II... Entering Phase III... No errors in compilation Top-level modules: hello\_world

Hello World by Deepak

Exiting VeriWell for Win32 at time 10 0 Errors, 0 Warnings, Memory Used: 0 Compile time = 0.0, Load time = 0.0, Simulation time = 0.0

Normal exit

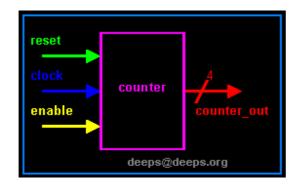

#### Counter Design Block

#### Counter Design Specs

- ? 4-bit synchronous up counter.

- ? active high, synchronous reset.

- ? Active high enable.

🗞 Counter Design

| 01//                        |                                                                  |

|-----------------------------|------------------------------------------------------------------|

|                             | ny second Verilog Design                                         |

|                             | Name : counter                                                   |

|                             | ne : counter.v                                                   |

|                             | : This is a 4 bit up-counter with                                |

| 00//                        | Synchronous active high reset and with active high enable signal |

| 07//<br>08//                | with active high enable signal                                   |

| 00//                        |                                                                  |

| 10 module co                | unter (                                                          |

|                             | , // Clock input ot the design                                   |

| 12 reset                    | , // active high, synchronous Reset                              |

| 13 input                    | ,                                                                |

| 14 enable                   | , // Active high enabel signal for                               |

| 15 counter                  |                                                                  |

|                             | ut // 4 bit vector output of the counter                         |

| 17); // End of              | f port list                                                      |

| 18                          |                                                                  |

| 19//                        | -Input Ports                                                     |

| 20 input                    |                                                                  |

| 21 input                    |                                                                  |

| 22 <mark>input</mark><br>23 | enable ;                                                         |

|                             | -Output Ports                                                    |

|                             | )] counter_out ;                                                 |

| 26 output [0.0              | j obuliter_out,                                                  |

| 27 //                       | -Input ports Data Type                                           |

|                             | all the input ports should be wires                              |

| 29 wire                     |                                                                  |

| 30 wire                     | reset ;                                                          |

| 31 wire                     | enable ;                                                         |

| 32                          |                                                                  |

|                             | -Output Ports Data Type                                          |

|                             | port can be a storage element (reg) or a                         |

| 35 wire                     |                                                                  |

|                             | counter_out ;                                                    |

| 37                          | Codo Storto Horo                                                 |

|                             | Code Starts Here<br>is counter is a positive edge trigged one,   |

|                             | er the below block with respect to positive                      |

| 40// we mgg<br>41// edge of |                                                                  |

|                             | (posedge clock)                                                  |

|                             | DUNTER // Block Name                                             |

|                             | rising edge of clock we check if reset is                        |

| 45 active                   |                                                                  |

|                             |                                                                  |

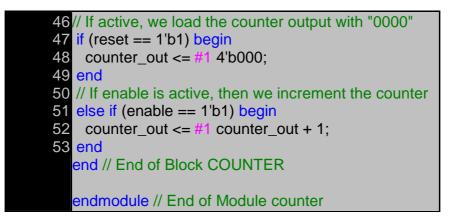

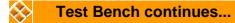

Counter testbench consists of clock generator, reset control, enable control and compare logic. Below is the simple code of testbench without the compare logic.

| 1module counter_tb();        |                            |  |

|------------------------------|----------------------------|--|

| 2// Declare inputs as i      | egs and outputs as wires   |  |

| 3 reg clock, reset, ena      | ble                        |  |

| 4wire [3:0] counter_ou       | ıt;                        |  |

| 5// Initialize all variable  | es                         |  |

| 6 <mark>initial begin</mark> |                            |  |

| 7 clock = 1;                 | // initial value of clock  |  |

| 8 reset = 0;                 | // initial value of reset  |  |

| 9 enable = 0;                | // initial value of enable |  |

| 10                           | // Assert the reset        |  |

| 11 <b>#5</b> reset = 0;                                       | // De-assert the reset        |

|---------------------------------------------------------------|-------------------------------|

| 12 <b>#5</b> enable = 1;                                      | // Assert enable              |

| 13 $\#100$ enable = 0;                                        | // De-assert enable           |

| 14 #10 \$finish;                                              | // Terminate simulation       |

| 15 <mark>end</mark>                                           |                               |

| 16// Clock generator                                          |                               |

| 17always begin                                                |                               |

| $\frac{18}{45} \operatorname{clock} = \operatorname{-clock};$ | // Toggle clock every 5 ticks |

| 19 <mark>end</mark>                                           |                               |

| 20// Connect DUT to te                                        | st bench                      |

| 21 counter U_counter (                                        |                               |

| 22 clock,                                                     |                               |

| 23 reset,                                                     |                               |

| 23 reset,<br>24 enable,                                       |                               |

| 25 counter_out                                                |                               |

| 26);                                                          |                               |

| 27                                                            |                               |

| 28endmodule                                                   |                               |

## Sounter Waveform

Note : Simulator used for this exercise can be got from here, If this is illegal, please let me know, I will remove it from my web page.

# **Verilog HDL Syntax and Semantics**

#### Lexical Conventions

The basic lexical conventions used by Verilog HDL are similar to those in the C programming language. Verilog HDL is a case-sensitive language. All keywords are in lowercase.

#### White Space

White space can contain the characters for blanks, tabs, newlines, and formfeeds. These characters are ignored except when they serve to separate other tokens. However, blanks and tabs are significant in strings.

White space characters are :

- ? Blank spaces

- ? Tabs

- ? Carriage returns

- ? New-line

- ? Form-feeds

#### **+** Examples of White Spaces

#### **Functional Equivalent Code**

| module addbit(a,b,ci,sum,co);<br>input a,b,ci;output sum co;<br>wire a,b,ci,sum,co; | module addbit (a,b,ci,sum,co);inputa;inputb;inputci;outputsum; |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------|

|                                                                                     | outputsum;outputco;wirea;wireb;wireci;wiresum;wireco;          |

| Never write code like this.                                                         | Nice way to write code.                                        |

|                                                                                     |                                                                |

There are two forms to introduce comments.

- ? Single line comments begin with the token // and end with a carriage return

- ? Multi Line comments begin with the token /\* and end with the token \*/

#### Examples of Comments

| few verilo<br>module ac<br>a,<br>b,<br>ci,<br>sum,<br>co); | der example for showing<br>g */ Multi line comment<br>ddbit (<br>orts Single line |

|------------------------------------------------------------|-----------------------------------------------------------------------------------|

| comment                                                    |                                                                                   |

| input                                                      | a;                                                                                |

| input                                                      | b;                                                                                |

| input                                                      | ci;                                                                               |

| // Output p                                                | oorts                                                                             |

| output                                                     | sum;                                                                              |

| output                                                     | CO;                                                                               |

| // Data Ty                                                 | pes                                                                               |

| wire                                                       | a;                                                                                |

| wire                                                       | b;                                                                                |

| wire                                                       | ci;                                                                               |

| wire                                                       | sum;                                                                              |

| wire                                                       | со;                                                                               |

#### Case Sensitivity

Verilog HDL is case sensitive

- ? Lower case letters are unique from upper case letters

- ? All Verilog keywords are lower case

Examples of Unique names

| input | // a Verilog Keyword                         |

|-------|----------------------------------------------|

| wire  | // a Verilog Keyword                         |

| WIRE  | <pre>// a unique name ( not a keyword)</pre> |

| Wire  | // a unique name (not a keyword)             |

**NOTE** : Never use the Verilog keywords as unique name, even if the case is different.

#### Identifiers

Identifiers are names used to give an object, such as a register or a module, a name so that it can be referenced from other places in a description.

- ? Identifiers must begin with an alphabetic character or the underscore character ( a-z A-Z \_ )

- ? Identifiers may contain alphabetic characters, numeric characters, the underscore, and the dollar sign ( a-z A-Z 0-9 \_ \$)

- ? Identifiers can be up to 1024 characters long.

#### Examples of legal identifiers

| data_input | mu      |

|------------|---------|

| clk_input  | my\$clk |

| i386       | А       |

#### Secaped Identifiers

Verilog HDL allows any character to be used in an identifier by **escaping** the identifier. Escaped identifiers provide a means of including any of the printable ASCII characters in an identifier (the decimal values 33 through 126, or 21 through 7E in hexadecimal).

- ? Escaped identifiers begin with the back slash (\)

- ? Entire identifier is escaped by the back slash

- ? Escaped identifier is terminated by white space

- Characters such as commas, parentheses, and semicolons become part of the escaped identifier unless preceded by a white space.

- ? Terminate escaped identifiers with white space, otherwise characters that should follow the identifier are considered as part of it.

Examples of escape identifiers:

| \486_up    | \Q~                       | \1,2,3        | \reset* |

|------------|---------------------------|---------------|---------|

| module \48 | <mark>36 (q,\q~,d,</mark> | clk,\reset*); |         |

#### Numbers in Verilog

You can specify constant numbers in decimal, hexadecimal, octal, or binary format. Negative numbers are represented in 2's complement form. When used in a number, the question mark (?) character is the Verilog alternative for the z character. The underscore character (\_) is legal anywhere in a number except as the first character, where it is ignored.

#### Integer Numbers

Verilog HDL allows integer numbers to be specified as

- ? Sized or unsized numbers (Unsized size is 32 bits)

- ? In a radix pf binary, octal, decimal, or hexadecimal

- ? Radix is case and hex digits (a,b,c,d,e,f) are insensitive

- ? Spaces are allowed between the size, radix and value

Syntax: <size>'<radix><value>

#### **Example of Integer Numbers**

| Integer    | Stored as                               | Description         |

|------------|-----------------------------------------|---------------------|

| 1          | 000000000000000000000000000000000000000 | unsized 32 bits     |

| 8'hAA      | 10101010                                | sized hex           |

| 6'b10_0011 | 100011                                  | sized binary        |

| 'hF        | 00000000000000000000000000000001111     | unsized hex 32 bits |

Verilog expands **<value>** to be fill the specified **<size>** by working from *right-to-left*

- ? When **<size>** is *smaller* than **<value>**, then left-most bits of **<value>** are truncated

- ? When **<size>** is *larger* than **<value>**, then left-most bits are filled, based on the value of the left-most bit in **<value>**.

- $\circ~$  Left most '0' or '1' are filled with '0', 'Z' are filled with 'Z' and 'X' with 'X'

Example of Integer Numbers

| Integer | Stored as         | Description                 |

|---------|-------------------|-----------------------------|

| 6'hCA   | 001010            | truncated, not 11001010     |

| 6'hA    | 001010            | filled with two '0' on left |

| 16'bZ   | ZZZZZZZZZZZZZZZZZ | filled with 16 Z's          |

| 8'bx    | x x x x x x x x x | filled with 8 X's           |

#### Real Numbers

- ? Verilog supports real constants and variables

- ? Verilog converts real numbers to integers by rounding

- ? Real Numbers can not contain 'Z' and 'X'

- ? Real numbers may be specified in either decimal or scientific notation

<value>.<value>

<mantissa>E<exponent>

? Real numbers are rounded off to the nearest integer.

#### **Example of Real Numbers**

| Real Number | Decimal notation |

|-------------|------------------|

| 1.2         | 1.2              |

| 0.6         | 0.6              |

| 3.5E6       | 3,500000.0       |

#### Signed and Unsigned Numbers

Verilog Supports both the type of numbers, but with certain restrictions. Like in C language we don't have int and unint types to say if a number is signed integer or unsigned integer.

Any number that does not have negative sign prefix is a positive number. Or indirect way would be "Unsigned"

Negative numbers can be specified by putting a minus sign before the size for a constant number, thus become signed numbers. Verilog internally represents negative numbers in 2's compliment format. An optional signed specifier can be added for signed arithmetic.

#### Examples

| 32'hDEAD_BEEF | Unsigned or signed positive Number |  |

|---------------|------------------------------------|--|

| -14'h1234     | Signed negative number             |  |

Below example file show how Verilog treats signed and unsigned numbers.

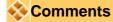

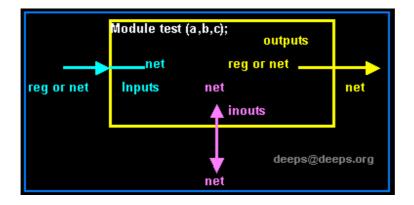

- ? Module are the building blocks of Verilog designs

- ? You create design hierarchy by *instantiating* modules in other modules.

- ? An *instant* of a module is a use of that module in another, higher-level module.

#### Hierarchical Identifiers

? Hierarchical path names are based on the **top module identifier** followed by **module instant identifiers**, separated by **periods**.

- ? Ports allow communication between a module and its environment.

- ? All but the top-level modules in a hierarchy have ports.

- ? Ports can be associated by order or by name.

You declare ports to be **input**, **output** or **inout**. The port declaration syntax is :

input [range\_val:range\_var] list\_of\_identifiers; output [range\_val:range\_var] list\_of\_identifiers; inout [range\_val:range\_var] list\_of\_identifiers;

| <b>NOTE</b> : As a good coding practice, th per line, as shown below                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nere should be only one port identifier |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Examples : Port Declaration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |

| inputclk; // clockinput[15:0]data_in; // 16 bitoutput[7:0]count; // 8 bit ofinoutdata_bi; // Bi-Di                                                                                                                                                                                                                                                                                                                                                                                                                              | data input bus<br>counter output        |

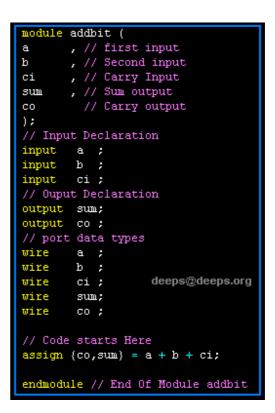

| Examples : A complete Example in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Verilog                                 |

| <pre>module addbit (     a  , // first input     b  , // Second input     ci  , // Carry Input     sum , // Sum output     co  // Carry output     );     // Input Declaration     input  a ;     input  b ;     input  b ;     input  ci ;     // Ouput Declaration     output  sum;     output  co ;     // port data types     wire  a ;     wire  b ;     wire  ci ;  deeps@deeps.org     wire  sum;     wire  co ;      // Code starts Here     assign {co,sum} = a + b + ci;     endmodule // End Of Module addbit </pre> |                                         |

## Modules connected by port order (implicit):

Here order should match correctly. Normally it not a good idea to connect ports implicit. Could cause problem in debug, when any new port is added or deleted.

```

module adder (

, // Output of the adder

result

, // Carry output of adder

carry

r1

, // first input

, // second input

r2

ci

// carry input

);

// Input Port Declarations

input [3:0] r1

;

input [3:0] r2

input

ci

// Output Port Declarations

output [3:0] result ;

output

carry

;

// Port Wires

wire

[3:0]

r1

wire

[3:0]

r2

ci

wire

wire

[3:0]

result

;

wire

carry

// Internal variables

wire

c1

c2

wire

;

c3

wire

// Code Starts Here

addbit u0 (

r1[0]

r2[0]

ci

result[0] ,

c1

);

addbit u1 (

r1[1]

r2[1]

c1

result[1] ,

c2

);

addbit u2 (

r1[2]

r2[2]

c2

result[2] ,

сЗ

);

addbit u3 (

r1[3]

r2[3]

```

| le adder<br>result                                             | , // O                                                 |                   | f the adder   |

|----------------------------------------------------------------|--------------------------------------------------------|-------------------|---------------|

| carry                                                          |                                                        |                   | tput of adder |

| r1<br>r2                                                       |                                                        | rst inpu          |               |

| rz<br>ci                                                       | •                                                      | econd<br>carry in |               |

| );                                                             | // 0                                                   |                   | put           |

| ),<br>// Input F                                               | Port Dec                                               | claratio          | ns            |

| input [                                                        |                                                        |                   | •             |

| •                                                              | 3:0] r2                                                |                   | •             |

| input                                                          |                                                        | ci .              | ;             |

| // Output                                                      |                                                        |                   | tions         |

| output                                                         |                                                        |                   |               |

|                                                                |                                                        | arry              | ,             |

| // Port W<br>wire [3                                           |                                                        |                   |               |

| -                                                              | 3:0] r1<br>3:0] r2                                     |                   | ,<br>,        |

| wire                                                           | 5.0j 12<br>C                                           |                   |               |

|                                                                |                                                        | esult             | ,             |

| wire                                                           | -                                                      | arry              |               |

| // Interna                                                     |                                                        |                   | ,             |

| wire                                                           |                                                        | :1                | ;             |

| wire                                                           | c                                                      | :2                | -             |

| wire                                                           | c                                                      | :3                | •             |

| // Code \$<br>addbit u(<br>.a<br>.b<br>.ci<br>.ci<br>.co<br>); |                                                        |                   | ,<br>,        |

| addbit u<br>.a<br>.b<br>.ci<br>.sum<br>.co<br>);               | 1 (<br>(r1[1])<br>(r2[1])<br>(c1)<br>(result[1<br>(c2) | 1]) ,             | ,<br>,        |

| addbit u<br>.a<br>.b<br>.ci<br>.sum<br>.co<br>);               | 2 (<br>(r1[2])<br>(r2[2])<br>(c2)<br>(result[2<br>(c3) | 2]) ,             | ,<br>,<br>,   |

| addbit u:<br>.a<br>.b                                          | 3 (<br>(r1[3])<br>(r2[3])                              |                   | ,             |

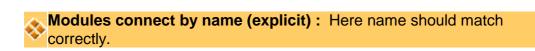

## 🚸 Instantiating a module

```

module parity (

, // First input

а

, // Second input

b

c , // Third Input

d , // Fourth Input

// Parity output

у

);

// Input Declaration

input a

;

input

b

input

С

input

d

// Ouput Declaration

output y

;

// port data types

wire

а

wire

b

wire

С

d

wire

wire

у

// Internal variables

wire

out_0 ;

out_1;

wire

// Code starts Here

xor u0 (

out_0,

а

,

b

);

xor u1 (

out_1,

С

,

d

);

xor u2 (

У

out_0,

out_1

);

endmodule // End Of Module parity

```

# Question : What is difference between u0 in module adder and u0 in module parity?

#### **Schematic**

#### Data Types

Verilog Language has two primary data types

- ? **Nets -** represents structural connections between components.

- ? **Registers -** represent variables used to store data.

Every signal has a data type associated with it:

- ? **Explicitly declared** with a declaration in your Verilog code.

- ? **Implicitly declared** with no declaration but used to connect structural building blocks in your code.

- ? Implicit declaration is always a net of type wire and is one bit wide.

#### Types of Nets

Each net type has functionality that is used to model different types of hardware (such as **PMOS**, **NMOS**, **CMOS**, etc)

| Net Data Type |         | Functionality                                              |  |

|---------------|---------|------------------------------------------------------------|--|

| wire          | tri     | Interconnecting wire - no special<br>resolution function   |  |

| wor           | trior   | Wired outputs OR together (models ECL)                     |  |

| wand          | triand  | Wired outputs AND together (models open-collector)         |  |

| tri0          | tri1    | Net pulls-down or pulls-up when not driven                 |  |

| supply0       | supply1 | Net has a constant logic 0 or logic 1<br>(supply strength) |  |

| trireg        |         |                                                            |  |

#### Note : Of all the net types, wire is the one which is most widely used

#### Register Data Types

- ? Registers store the last value assigned to them until another assignment statement changes their value.

- ? Registers represent data storage constructs.

- ? You can create arrays of the regs called memories.

- ? register data types are used as variables in procedural blocks.

- ? A register data type is required if a signal is assigned a value within a procedural block

- Procedural blocks begin with keyword *initial* and *always*.

| Data Types | Functionality                               |  |

|------------|---------------------------------------------|--|

| reg        | Unsigned variable                           |  |

| integer    | Signed variable - 32 bits                   |  |

| time       | e Unsigned integer - 64 bits                |  |

| real       | al Double precision floating point variable |  |

Note : Of all the register types, reg is the one which is most widely used

Question : What is the difference between wire and reg data type Denswer

#### Strings

A string is a sequence of characters enclosed by double quotes and all contained on a single line. Strings used as operands in expressions and assignments are treated as a sequence of eight-bit ASCII values, with one eight-bit ASCII value representing one character. To declare a variable to store a string, declare a register large enough to hold the maximum number of characters the variable will hold. Note that no extra bits are required to hold a termination character; Verilog does not store a string termination character. Strings can be manipulated using the standard operators.

When a variable is larger than required to hold a value being assigned, Verilog pads the contents on the left with zeros after the assignment. This is consistent with the padding that occurs during assignment of non-string values.

Certain characters can be used in strings only when preceded by an introductory character called an escape character. The following table lists these characters in the right-hand column with the escape sequence that represents the character in the left-hand column.

- \n New line character

- \t Tab character

- \\ Backslash (\) character

- \" Double quote (") character

- \ddd A character specified in 1-3 octal digits ( $0 \le d \le 7$ )

- %% Percent (%) character

#### Example

reg [8\*17:0] version ; // Declare a register variable that is 18 bytes

#### initial

version = "model version 1.0";

#### Port Connection Rules

- ? **Inputs** : internally must always be type *net*, externally the inputs can be connected to variable *reg* or *net* type.

- ? **Outputs :** internally can be type *net* or *reg*, externally the outputs must be connected to a variable net type.

- ? **Inouts :** internally or externally must always be type *net*, can only be connected to a variable net type.

- ? Width matching : It is legal to connect internal and external ports of different sizes. But beware, synthesis tools could report problems.

- ? Unconnected ports : unconnected ports are allowed by using a ","

- ? The net data types are used to connect structure

- ? A net data type is required if a signal can be driven a structural connection.

Example : Implicit

dff u0 ( q,,clk,d,rst,pre); // Here second port is not connected

Example : Explicit

| dff u0 (                                |           |  |

|-----------------------------------------|-----------|--|

| .q                                      | (q_out),  |  |

| .q_bar                                  | (),       |  |

| .clk                                    | (clk_in), |  |

| .d                                      | (d_in),   |  |

| .rst                                    | (rst_in), |  |

| .pre                                    | (pre_in)  |  |

| ); // Here second port is not connected |           |  |

# **Gate Level Modeling**

#### Introduction

Verilog has built in primitives like gates, transmission gates, and switches. This are rarely used for in design work, but are used in post synthesis world for modeling the ASIC/FPGA cells, this cells are then used for gate level simulation or what is called as SDF simulation.

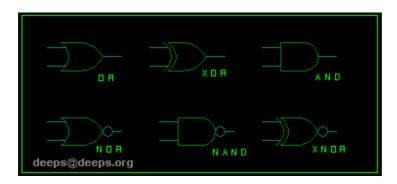

#### Gate Primitives

The gates have one scalar output and multiple scalar inputs. The 1st terminal in the list of gate terminals is an output and the other terminals are inputs.

| and  | N-input AND gate  |  |

|------|-------------------|--|

| nand | N-input NAND gate |  |

| or   | N-input OR gate   |  |

| nor  | N-input NOR gate  |  |

| xor  | N-input XOR gate  |  |

| xnor | N-input XNOR gate |  |

#### Examples

and U1(out,in); and U2(out,in1,in2,in3,in4); xor U3(out,in1,in2,in3);

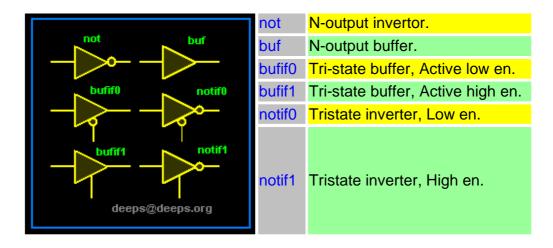

Transmission Gate Primitives

bufif0 U1(data\_bus,data\_drive, data\_enable\_low); buf U2(out,in); not U3(out,in);

## Switch Primitives

| 1                | pmos     | Uni-directional PMOS switch      |

|------------------|----------|----------------------------------|

|                  | rpmos    | Resistive PMOS switch            |

|                  | nmos     | Uni-directional NMOS switch      |

|                  | rnmos    | Resistive NMOS switch            |

|                  | cmos     | Uni-directional CMOS switch      |

|                  | rcmos    | Resistive CMOS switch            |

|                  | tranif1  | Bi-directional transistor (High) |

|                  | tranif1  | Resistive transistor (High)      |

|                  | tranif0  | Bi-directional transistor (Low)  |

| deeps@deeps.org  | rtranif1 | Resistive Transistor (Low)       |

| docho@acchoida 6 | tran     | Bi-directional pass transistor   |

|                  | rtran    | Resistive pass transistor        |

| deeps@deeps.org | pullup   | Pull up resistor.   |

|-----------------|----------|---------------------|

| deeps@deeps.org | pulldown | Pull down resistor. |

Transmission gates are bi-directional and can be resistive or non-resistive.

Syntax: keyword unique\_name (inout1, inout2, control);

tranif0 my\_gate1 (net5, net8, cnt); rtranif1 my\_gate2 (net5, net12, cnt);

Transmission gates *tran* and *rtran* are permanently on and do not have a control line. *Tran* can be used to interface two wires with separate drives, and *rtran* can be used to weaken signals. Resistive devices reduce the signal strength which appears on the output by one level. All the switches only pass signals from source to drain, incorrect wiring of the devices will result in high impedance outputs.

## Logic Values and signal Strengths

The Verilog HDL has got four logic values

| 0      | zero, low, false                   |  |

|--------|------------------------------------|--|

| 1      | one, high, true                    |  |

| z or Z | high impendence, floating          |  |

| x or X | unknown, uninitialized, contention |  |

## Strength Levels

| Strength<br>Level | Strength     | Specification<br>Keyword |         |

|-------------------|--------------|--------------------------|---------|

| 7                 | Supply Drive | supply0                  | supply1 |

| 6                 | Strong Pull  | strong0                  | strong1 |

| 5                 | Pull Drive   | pull0                    | pull1   |

| 4                     | Large Capacitance    | large  |       |

|-----------------------|----------------------|--------|-------|

| 3                     | Weak Drive weak0 wea |        | weak1 |

| 2                     | Medium Capacitance   | medium |       |

| 1                     | Small Capacitance    | small  |       |

| 0 Hi Impedance highz0 |                      | highz1 |       |

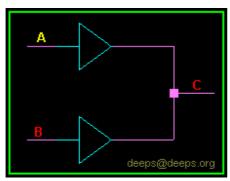

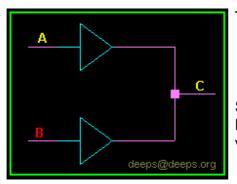

# Examples

Two buffers that has output A : Pull 1 B : Supply 0 Since supply 0 is stronger then pull 1, Output C takes value of B.

# Two buffers that has output A : Supply 1 B : Large 1

Since Supply 1 is stronger then Large 1, Output C takes the value of A

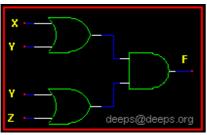

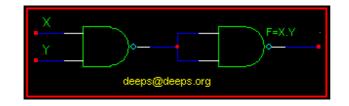

# Designing Using Primitives

# AND Gate from NAND Gate

Verilog Code

// Structural model of AND gate from two NANDS

module and\_from\_nand(X, Y, F);

input X, Y; output F; wire W; // Two instantiations of the module NAND nand U1(X, Y, W); nand U2(W, W, F);

endmodule

Verilog Code

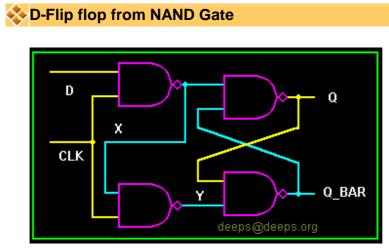

```

module dff(Q,Q_BAR,D,CLK);

output Q,Q_BAR;

input D,CLK;

```

nand U1 (X,D,CLK) ; nand U2 (Y,X,CLK) ; nand U3 (Q,Q\_BAR,X); nand U4 (Q\_BAR,Q,Y);

endmodule

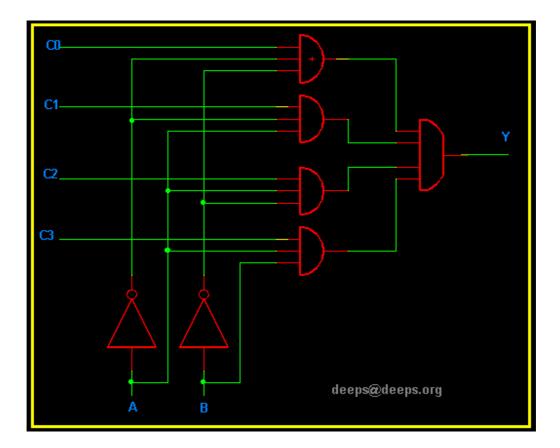

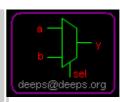

Multiplexer from primitives

# Verilog Code

//Module 4-2 Mux

module mux (c0,c1,c2,c3,A,B,Y);

input c0,c1,c2,c3,A,B;

ouput Y;

//Invert the sel signals

not (a\_inv, A);

not (b\_inv, B);

// 3-input AND gate

and (y0,c0,a\_inv,b\_inv);

and (y1,c1,a\_inv,B);

and (y2,c2,A,b\_inv);

and (y3,c3,A,B);

// 4-input OR gate

or (Y, y0,y1,y2,y3);

endmodule

Gate and Switch delays

In real circuits, logic gates haves delays associated with them. Verilog provides the mechanism to associate delays with gates.

- ? Rise, Fall and Turn-off delays.

- ? Minimal, Typical, and Maximum delays.

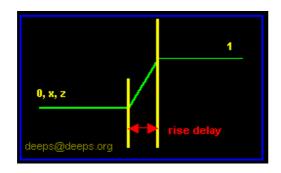

# 🗞 Rise Delay

The rise delay is associated with a gate output transition to 1 from another value (0,x,z).

## 🗞 Fall Delay :

The fall delay is associated with a gate output transition to 0 from another value (1,x,z).

## 🗞 Turn-off Delay

The fall delay is associated with a gate output transition to z from another value (0,1,x).

## 🗞 Min Value

The min value is the minimum delay value that the gate is expected to have.

The typ value is the typical delay value that the gate is expected to have.

## 🗞 Max Value

The max value is the maximum delay value that the gate is expected to have.

Examples

// Delay for all transitions

or #5 u\_or (a,b,c);

// Rise and fall delay

and #(1,2) u\_and (a,b,c);

// Rise, fall and turn off delay

nor # (1,2,3) u\_nor (a,b,c);

//One Delay, min, typ and max

nand #(1:2:3) u\_nand (a,b,c);

//Two delays, min,typ and max buf #(1:4:8,4:5:6) u\_buf (a,b);

//Three delays, min, typ, and max notif1 #(1:2:3,4:5:6,7:8:9) u\_notif1 (a,b,c);

**Gate Delay Code Example**

module not\_gate (in,out);

input in;

output out;

**not** #(5) (out,in);

endmodule

Gate Delay Code Example

module not\_gate (in,out);<br/>input in;<br/>output out;<br/>not #(2,3) (out,in);Image: Comparison of the second seco

Normally we can have three models of delays, typical, minimum and maximum delay. During compilation of a modules one needs to specify the delay models to use, else Simulator will use the typical model.

Verilog +minterms myfile.v

I have assumed Verilog-XL as simulator

### N-Input Primitives

The **and**, **nand**, **or**, **nor**, **xor**, and **xnor** primitives have one output and any number of inputs

- ? The single output is the first terminal

- ? All other terminals are inputs

### Examples

// Two input AND gate

and u\_and (out, in1, in2);

// four input AND gate

and u\_and (out, in1, in2, in3, in4);

// three input XNOR gate

xnor u\_xnor (out, in\_1, in\_2, in\_3);

### N-Output Primitives

The **buf** and **not** primitives have any number of outputs and one input

- ? The output are in first terminals listed.

- ? The last terminal is the single input.

// one output Buffer gate

buf u\_buf (out,in);

// four output Buffer gate

buf u\_buf (out\_0, out\_1, out\_2, out\_3, in);

// three output Invertor gate

not u\_not (out\_a, out\_b, out\_c, in);

# **Verilog Operators**

# Arithmetic Operators

- ? Binary: +, -, \*, /, % (the modulus operator)

- ? Unary: +, -

- ? Integer division truncates any fractional part

- ? The result of a modulus operation takes the sign of the first operand

- ? If any operand bit value is the unknown value x, then the entire result value is x

- ? Register data types are used as unsigned values

- o negative numbers are stored in two's complement form

## Relational Operators

| a <b< th=""><th>a less than b</th></b<> | a less than b                |

|-----------------------------------------|------------------------------|

| a>b                                     | a greater than b             |

| a<=b                                    | a less than or equal to b    |

| a>=b                                    | a greater than or equal to b |

- ? The result is a scalar value:

- ? 0 if the relation is false

- ? 1 if the relation is true

- ? x if any of the operands has unknown x bits

- ? Note: If a value is x or z, then the result of that test is false

## Equality Operators

| a === k | a equal to b, including x and z                                         |  |

|---------|-------------------------------------------------------------------------|--|

| a !== b | a not equal to b, including x and z                                     |  |

| a == b  | a equal to b, resulting may be unknown                                  |  |

| a != b  | a not equal to b, result may be unknown                                 |  |

|         |                                                                         |  |

| ?       | Operands are compared bit by bit, with zero filling if the two operands |  |

| (       | do not have the same length                                             |  |

| ?       | sult is 0 (false) or 1 (true)                                           |  |

| ?       | For the == and != operators the result is x, if either operand contains |  |

| :       | an x or a z                                                             |  |

- ? For the === and !== operators

- bits with x and z are included in the comparison and must match for the result to be true

- the result is always 0 or 1

### Logical Operators

| !  | logic negation |

|----|----------------|

| && | logical and    |

|    | logical or     |

- ? Expressions connected by && and || are evaluated from left to right

- ? Evaluation stops as soon as the result is known

- ? The result is a scalar value:

- 0 if the relation is false

- o 1 if the relation is true

- o x if any of the operands has unknown x bits

### Bit-wise Operators

| ~        | negation                    |

|----------|-----------------------------|

| &        | and                         |

|          | inclusive or                |

| ^        | exclusive or                |

| ^~ or ~^ | exclusive nor (equivalence) |

- ? Computations include unknown bits, in the following way:

- ~**X** = **X**

- 0**&**x = 0

- $\circ \quad 1\&x = x\&x = x$

- $\circ 1|x = 1$

- $\circ \quad 0|x = x|x = x$

- $\circ$  0^x = 1^x = x^x = x

- $\circ$  0^~x = 1^~x = x^~x = x

- ? When operands are of unequal bit length, the shorter operand is zerofilled in the most significant bit positions

### Reduction Operators

| &        | and  |

|----------|------|

| ~&       | nand |

|          | or   |

| ~        | nor  |

| ^        | xor  |

| ^~ or ~^ | xnor |

? Reduction operators are unary.

- ? They perform a bit-wise operation on a single operand to produce a single bit result.

- ? Reduction unary NAND and NOR operators operate as AND and OR respectively, but with their outputs negated.

- Unknown bits are treated as described before.

### Shift Operators

| << | left shift  |

|----|-------------|

| >> | right shift |

- ? The left operand is shifted by the number of bit positions given by the right operand.

- ? The vacated bit positions are filled with zeroes.

### Concatenation Operator

- ? Concatenations are expressed using the brace characters { and }, with commas separating the expressions within

- Examples

- {a, b[3:0], c, 4'b1001} // if a and c are 8-bit numbers,

the results has 24 bits

- ? Unsized constant numbers are not allowed in concatenations

- ? Repetition multipliers that must be constants can be used:

o {3{a}} // this is equivalent to {a, a, a}

- ? Nested concatenations are possible:

- $\circ$  {b, {3{c, d}}} // this is equivalent to {b, c, d, c, d, c, d}

### Conditional Operator

- ? The conditional operator has the following C-like format:

o cond\_expr ? true\_expr : false\_expr

- ? The true\_expr or the false\_expr is evaluated and used as a result depending on whether cond\_expr evaluates to true or false

## Example

out = (enable) ? data : 8'bz; // Tri state buffer

Operator Precedence

| Operator                            | Symbols                  |

|-------------------------------------|--------------------------|

| Unary, Multiply, Divide,<br>Modulus | + - ! ~ * / %            |

| Add, Subtract, Shift.               | +, - , <<, >>            |

| Relation, Equality                  | <,>,<=,>=,==,!=,===,!=== |

| Reduction                           | &, !&,^,^~, ,~           |

| Logic                               | &&,                      |

| Conditional                         | ?:                       |

# **Verilog Behavioral Modeling**

## Serilog HDL Abstraction Levels

- ? Behavioral Models : Higher level of modeling where behavior of logic is modeled.

- ? RTL Models : Logic is modeled at register level

- ? Structural Models : Logic is modeled at both register level and gate level.

### Procedural Blocks

Verilog behavioral code is inside procedures blocks, but there is a exception, some behavioral code also exist outside procedures blocks. We can see this in detail as we make progress.

There are two types of procedural blocks in Verilog

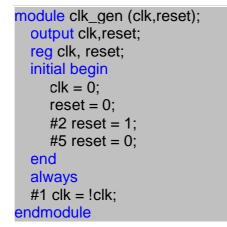

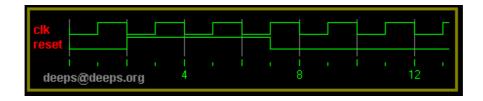

- ? **initial** : initial blocks execute only once at time zero (start execution at time zero).

- ? **always** : always blocks loop to execute over and over again, in other words as name means, it executes always.

## Example : initial and always

| initial     | always @ (posedge clk) |

|-------------|------------------------|

| begin       | begin : D_FF           |

| clk = 0;    | if (reset == 1)        |

| reset = 0;  | q <= 0;                |

| enable = 0; | else                   |

| data = 0;   | q <=d;                 |

| end         | end                    |

### Procedural Assignment Statements

- ? Procedural assignment statements assign values to registers and can not assign values to nets (wire data types)

- ? You can assign to the register (reg data type) the value of a net (wire), constant, another register, or a specific value.

+ Example : Bad and Good procedural assignment

wire clk, reset;

reg clk, reset;

| reg enable, data; | reg enable, data; |

|-------------------|-------------------|

| initial           | initial           |

| begin             | begin             |

| clk = 0;          | clk = 0;          |

| reset = 0;        | reset = 0;        |

| enable = 0;       | enable = 0;       |

| data = 0;         | data = 0;         |

| end               | end               |

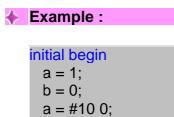

### Procedural Assignment Groups

If a procedure block contains more then one statement, those statements must be enclosed within

- ? Sequential **begin end** block

- ? Parallel fork join block

When using begin-end, we can give name to that group. This is called named blocks.

### **Example :** "begin-end" and "fork - join"

| initial        | initial        |

|----------------|----------------|

| begin          | fork           |

| #1 clk = 0;    | #1 clk = 0;    |

| #5 reset = 0;  | #5 reset = 0;  |

| #5 enable = 0; | #5 enable = 0; |

| #2 data = 0;   | #2 data = 0;   |

| end            | join           |

**Begin :** clk gets 0 after 1 time unit, reset gets 0 after 6 time units, enable after 11 time units, data after 13 units. All the statements are executed in sequentially.

**Fork :** clk gets value after 1 time unit, reset after 5 time units, enable after 5 time units, data after 2 time units. All the statements are executed in parallel.

### **+** Sequential Statement Groups

The **begin** - **end** keywords:

- ? Group several statements together.

- ? Cause the statements to be evaluated in sequentially (one at a time).

- Any timing within the sequential groups is relative to the previous statement.

- Delays in the sequence accumulate (each delay is added to the previous delay)

- o Block finishes after the last statement in the block.

### Parallel Statement Groups

The fork - join keywords:

- ? Group several statements together.

- ? Cause the statements to be evaluated in parallel ( all at the same time).

- Timing within parallel group is absolute to the beginning of the group.

- Block finishes after the last statement completes( Statement with high delay, it can be the first statement in the block).

### The Conditional Statement if-else

The **if - else** statement controls the execution of other statements, In programming language like c, if - else controls the flow of program.

```

if (condition)

statements;

if (condition)

statements;

else

statements;

if (condition)

statements;

else if (condition)

statements;

.....

else

statements;

```

```

// Simple if statement

if (enable)

q <= d;

// One else statement

if (reset == 1'b1)

q <= 0;;

else

q \ll d;

// Nested if-else-if statements

if (reset == 1'b0)

counter <= 4'b0000;

else if (enable == 1'b1 && up_en == 1'b1)

counter <= counter + 1'b1;

else if (enable == 1'b1 && down en == 1'b1);

counter <= counter - 1'b0;

else

counter <= counter; // Redundant code

```

Note : More to be added on if-else, as this is the one which is most widely used.

### The Case Statement

The **case** statement compares a expression to a series of cases and executes the statement or statement group associated with the first matching case

- ? case statement supports single or multiple statements.

- ? Group multiple statements using begin and end keywords.

case (<expression>)

<case1> : <statement>

<case2> : <statement>

.....

default : <statement>

endcase

Example : case

The Verilog case statement does an identity comparison (like the === operator), One can use the case statement to check for logic x and z values

case(enable) 1'bz : \$display ("enable is floating"); 1'bx : \$display ("enable is unknown"); default : \$display ("enable is %b",enable); endcase

### The casez and casex statement

Special versions of the case statement allow the x ad z logic values to be used as "don't care"

- ? casez uses the z as the don't care instead of as a logic value

- ? casex uses either the x or the z as don't care instead of as logic values

🗞 Example casez

```

casez(opcode)

4'b1zzz : out = a; // don't care about lower 3 bits

4'b01??: out = b; //the ? is same as z in a number

4'b001?: out = c;

default : out = $display ("Error xxxx does matches 0000");

endcase

```

### Looping Statements

Looping statements appear inside a procedural blocks only, Verilog has four looping statements like any other programming language.

- ? forever

- ? repeat

- ? while

- ? for

### The forever statement

The forever loop executes continually, the loop never ends

syntax : forever <statement>

Example : Free running clock generator

initial begin clk = 0; forever #5 clk = !clk; end

## The repeat statement

The repeat loop executes statement fixed <number> of times

syntax : repeat (<number>) <statement>

### **Example:**

```

if (opcode == 10) //perform rotate

repeat (8) begin

temp = data[7];

data = {data<<1,temp};

end</pre>

```

The while loop statement

The while loop executes as long as an <expression> evaluates as true

syntax : while (<expression>) <statement>

### Example :

```

loc = 0;

if (data = 0) // example of a 1 detect shift value

loc = 32;

else while (data[0] == 0); //find the first set bit

begin

loc = loc + 1;

data = data << 1;

end

```

### The for loop statement

The for loop is same as the for loop used in any other programming language.

- ? Executes an <initial assignment> once at the start of the loop.

- ? Executes the loop as long as an <expression> evaluates as true.

- ? Executes a <step assignment> at the end of each pass through the loop.

syntax : for (<initial assignment>; <expression>, <step assignment>)

<statement>

### Example :

for (i=0;i<=63;i=i+1) ram[i] <= 0; // Inialize the RAM with 0

### Continuous Assignment Statements

Continuous assignment statements drives nets (wire data type). They represent structural connections.

- ? They are used for modeling Tri-State buffers.

- ? They can be used for modeling combinational logic.

- ? They are outside the procedural blocks (always and initial blocks).

- ? The continuous assign overrides and procedural assignments.

- ? The left-hand side of a continuous assignment must be net data type.

syntax : assign (strength, strength) # delay net = expression;

### 💸 Example: 1-bit Adder

module adder (a,b,sum,carry);

input a, b;

output sum, carry;

assign #5 {carry,sum} = a+b;

endmodule

🗞 Example: Tri-State Buffer

module tri\_buf(a,b,enable); input a, enable; output b; assign b = (enable) ? a : 1'bz; endmodule

### Propagation Delay

Continuous Assignments may have a delay specified, Only one delay for all transitions may be specified. A minimum:typical:maximum delay range may be specified.

## 🚸 Example : Tri-State Buffer

module tri\_buf(a,b,enable); input a, enable; output b; assign #(1:2:3) b = (enable) ? a : 1'bz; endmodule

### Procedural Block Control

Procedural blocks become active at simulation time zero, Use level sensitive even controls to control the execution of a procedure.

always @ (d or enable) if (enable) q = d;

An event sensitive delay at the begining of a procedure, any change in either d or enable satisfies the even control and allows the execution of the statements in the procedure. The procedure is sensitive to any change in d or enable.

## 📀 Combo Logic using Procedural Coding

To model combinational logic, a procedure block must be sensitive to any change on the input.

Example : 1-bit Adder

```

module adder (a,b,sum,carry);

input a, b;

output sum, carry;

reg sum, carry;

always @ (a or b)

begin

{carry} = a + b;

end

endmodule

```

The statements within the procedural block work with entire vectors at a time.

```

Example : 4-bit Adder

```

```

module adder (a,b,sum,carry);

input [3:0] a, b;

output [3:0] sum;

output carry;

reg [3:0] sum;

reg carry;

always @ (a or b)

begin

{carry} = a + b;

end

endmodule

```

A procedure can't trigger itself

Once cannot trigger the block with the variable that block assigns value or drive's.

always @ (clk) #5 clk = !clk;

Procedural Block Concurrency

If we have multiple always blocks inside one module, then all the blocks ( i.e. all the always blocks) will start executing at time 0 and will continue to execute concurrently. Sometimes this is leads to race condition, if coding is not done proper.

```

module procedure (a,b,c,d);

input a,b;

output c,d;

always @ ( c)

a = c;

always @ (d or a)

b = a &d;

endmodule

```

🗞 Race condition

initial b = 0; initial b = 1;

In the above code it is difficult to say the value of b, as both the blocks are suppose to execute at same time. In Verilog if care is not taken, race condition is something that occurs very often.

Blocks can be named by adding : block\_name after the keyword begin. This block can be disabled using disable statement.

```

module named_block (a,b,c,d);

input a,b;

output c,d;

always @ ( c)

a = c;

always @ (d or a)

begin : my_block

b = a &d;

```

end

endmodule

In above example, my\_block is the named block. (Need to add more practical example)

# **Procedural Timing Control**

### Procedural blocks and timing controls.

- ? Delays controls.

- ? Edge-Sensitive Event controls

- ? Level-Sensitive Event controls-Wait statements

- ? Named Events

## Delay Controls

Delays the execution of a procedural statement by specific simulation time.

#<time> <statement>;

#### Example :

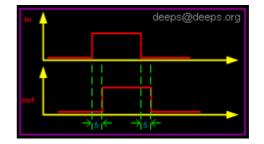

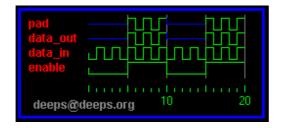

### 🔶 Waveform

## Edge sensitive Event Controls

Delays execution of the next statement until the specified transition on a signal.

@ (<posedge>|<negedge> signal) <statement>;

Example :

```

always @ (posedge enable)

begin

repeat (5) // Wait for 5 clock cycles

@ (posedge clk) ;

trigger = 1;

end

```

Waveform

| 10 20 30<br>deeps@deeps.org | enable<br>clk<br>trigger |    |    |    |

|-----------------------------|--------------------------|----|----|----|

|                             | deeps                    | 10 | 20 | 30 |

## Level-Sensitive Even Controls (Wait statements)

Delays execution of the next statement until the <expression> evaluates as true

syntax: wait (<expression>) <statement>;

## Example :

```

while (mem_read == 1'b1) begin

wait (data_ready) data = data_bus;

read_ack = 1;

end

```

## Intra-Assignment Timing Controls

Intra-assignment controls evaluate the right side expression right always

and assigns the result after the delay or event control.

In non-intra-assignment controls (delay or event control on the left side) right side expression evaluated after delay or event control.

Waveform

b = a; <mark>end</mark>

### Solution Notice Assignments Notice Assignments Notice Assignments

Whenever any signal changes on the right hand side, the entire right-hand side is re-evaluated and the result is assigned to the left hand side

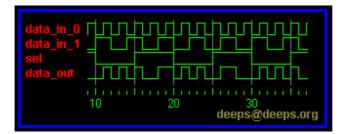

## Example : Tri-state buffer

module tri\_buf (data\_in,data\_out, pad,enable);

input data\_in, enable;

output data\_out;

inout pad;

wire pad, data\_out;

assign pad = (enable) ? data\_in : 1'bz;

assign data\_out = pad;

endmodule

# Example : 2:1 Mux

module mux2x1 (data\_in\_0,data\_in\_1, sel, data\_out);

input data\_in\_0, data\_in\_1;

output data\_out;

input sel;

wire data\_out;

assign data\_out = (sel) ? data\_in\_1 : data\_in\_0;

endmodule

## ♦ Waveform

# **Task and Function**

### Task

Tasks are used in all programming languages, generally known as Procedures or sub routines. Many lines of code are enclosed in task....end task brackets. Data is passed to the task, the processing done, and the result returned to a specified value. They have to be specifically called, with data in and outs, rather than just "wired in" to the general netlist. Included in the main body of code they can be called many times, reducing code repetition.

- ? task are defined in the module in which they are used. it is possible to define task in separate file and use compile directive 'include to include the task in the file which instantiates the task.

- ? task can include timing delays, like posedge, negedge, # delay.

- ? task can have any number of inputs and outputs.

- ? The variables declared within the task are local to that task. The order of declaration within the task defines how the variables passed to the task by the caller are used.

- ? task can take drive and source global variables, when no local variables are used. When local variables are used, it basically assigned output only at the end of task execution.

- ? task can call another task or function.

- ? task can be used for modeling both combinational and sequential logic.

- ? A task must be specifically called with a statement, it cannot be used within an expression as a function can.

## Syntax 🗞

- ? task begins with keyword task and end's with keyword endtask

- ? input and output are declared after the keyword task.