#### **Printed Circuit Boards**

ECE 188A Senior Electrical Engineering Capstone Project

> John Johnson November 5, 2014

#### **Schematics**

- Schematics Beginning the path to PCBs

- It all starts with the schematic

- Purpose of schematic

- Collection of parts (represented by logic symbols) and their interconnections (represented by nets)

- Both human and machine readable representations

- Schematics serve as a "design entry" format

- Often used as the primary view of a design

- With hierarchy, can highlight subsystems & structure

#### Schematics (continued)

- From schematic, generate netlist

- Netlist defines how to build it electrically (for simulation) and physically (for PCB routing)

- Netlist consists of an ASCII list of component pins that are shorted together

- Each such group constitutes a net

- Schematic "part" (logic symbol) is mapped onto (or associated with) a "model" for simulation and a "cell" for PCB routing

- Model can be SPICE, Verilog, VHDL, etc.

- Cell provides physical dimensions and pin ordering of the part at board level

#### Schematics (continued)

- With logic symbols mapped onto physical devices, we get a Bill of Materials (BOM)

- Ultimately, the netlist, together with the BOM, provides the basis for PCB layout and routing

- We will be using the Mentor Graphics® CAD Tools for schematic capture, PCB layout and library management

- DxDesigner® is the schematic capture tool

- Expedition® PCB is the PCB layout tool

- The Library manager provides the link between the two tools

- We will not be doing simulations of our complete designs

- Website tutorials demonstrate almost everything

http://www.ece.ucsb.edu/Faculty/Johnson/ECE189/Mentor2007/

#### **Printed Circuit Boards**

- Four layer board technology

- Top and bottom layers for signal routing

- Middle (inner) layers for power and ground planes

- Inner planes are (mostly) solid copper

- Top side referred to as "component side"

- Initially blank with component pads & traces added

- Bottom side referred to as "solder side"

- Initially blank with pads & traces added

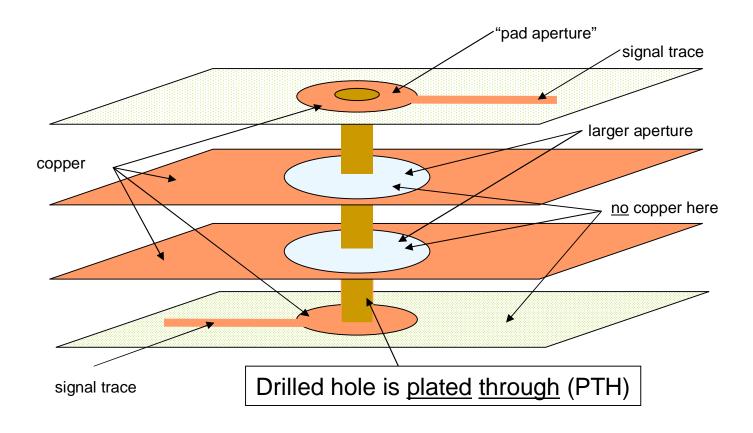

# Connection from Component Side to Solder Side (Via)

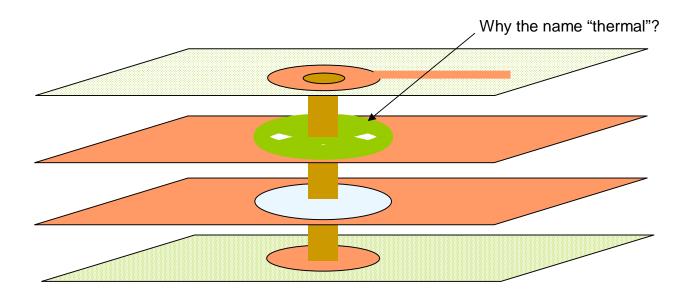

# Connection from Component Side to Power Plane (Thermal)

Thermal aperture shown highlighted ... actually it is copper (ORed-in with "+" plane)

#### **Thermals**

- Special consideration is required for making soldered connections between the power/ground layers and pins

- The term "thermal" refers to the portion of the foil layer of a power/ground plane where the connection is made to a pin

- Heat that is applied to a pin which is in contact with the copper layer will be drawn away by the relatively large thermal mass of the layer

- As a means to thermally (but not electrically) isolate the hole from the rest of the layer some of the copper outside the perimeter of the hole is etched away in the fabrication process leaving a few radial paths of copper to make the electrical connection from the pin to the foil layer

- If pins are connected to the power plane using thermals then the thermal must be able to carry the required current without excessive local heating

- Note that if heating is taking place at the connector between the pin and the board while the board is operating then there is probably an excessive voltage drop.

Electrical Design Standards for Electronics to be used in Experiment Apparatus at Fermilab, Revision 6.0 4/15/99

#### Pad Stacks

- Set of apertures appearing on the various layers to implement all flavors of via or through hole

- Surface-mount pad stacks also exist but they tend to only involve the mountside layer (though the concept of a "padstack" allows more general constructions)

- More complex structures are possible in multi-layer boards

- "Blind vias"

- vias going only between inner planes or just part of the way through a board ... not for us; too expensive

- Often we have several pad stacks defined

- Power connectors (larger diameter holes)

- Vias (smallest diameter holes)

- Mounting holes (special electrical details, e.g. non-plated thru, for isolation)

#### **Board Costs**

- Board size is a significant part of fab cost

- The smaller the board is, the cheaper it is

- In general, about \$150 per board after Sunstone Circuits 25% University sponsorship

- Most fab houses restrict the number of drill sizes or the number of drill holes

- Ours doesn't limit the number of holes but allows just 24 standard drill sizes

- Our fab house requires that boards be rectangular

#### 4-Layers (3 Days)

4-Layer Board + Soldermask + Silkscreen (LEAD-TIME - 3 days)

| Board Size in<br>Square Inches:   | 0-9   | 10 <b>-</b> 19 | 20-29 | 30-44 | 45-64 | 65 <b>-</b> 168 |  |  |

|-----------------------------------|-------|----------------|-------|-------|-------|-----------------|--|--|

| LOT QTY = \$USD per lot of boards |       |                |       |       |       |                 |  |  |

| 2                                 | \$210 | \$537          | \$569 | \$554 | \$583 | \$613           |  |  |

| 4                                 | \$389 | \$598          | \$651 | \$650 | \$701 | \$748           |  |  |

| 6                                 | \$519 | \$623          | \$690 | \$703 | \$768 | \$832           |  |  |

#### Sunstone Circuits PCBExpress® Quickturn PCB Pricing Table

http://www.sunstone.com/pcb-products/pcbquickturn/pcb-quickturn-pricing

#### **Board Costs**

- Cost increases with the number of layers

- But fewer layers often increases the size of the PCB.

- It takes time to drill the holes

- Too many vias on a net can cause electrical noise due to reflections

- Minimize the number of vias

- Buried vias are much more expensive than vias that go through all the layers ... we cannot use these(!)

- Buried vias require to drill each layer separately before they are laminated together.

- Like BGAs, buried vias are for production runs ....

- very difficult for debugging due to reduced access

## Surface Mount vs. Through Hole

- In Surface Mount Technology (SMT, utilizing Surface Mounted Devices or SMDs) components are soldered to the board on the same layer on which they are mounted

- i.e., if mounted on component side, soldered on component side

- In Through Hole Technology (THT, or Plated Through Hole, PTH) components are soldered to the board on the opposite side from which they are mounted

- Historically, components would be mounted on the "component" side and soldered on the "solder" side (hence the nomenclature)

- SMT also allows for much finer pin pitch on components

- SMT allows for more dense, and therefore smaller, PCBs than THT

- SMT is intended primarily for automated assembly but our assembly is done by hand

- Nearly all modern PCBs utilize Surface Mount Technology

#### PCB Assembly

- The assembly process consists of mounting and soldering the components onto the PCB

- Wave Soldering

- THT components are most often soldered in an automated process called wave soldering

- All components are soldered simultaneously

- Their legs are first cut near the board and slightly bent over to keep the component in place

- PCB is then moved over a wave of liquid flux, so that the bottom side strikes the flux

- This removes any oxide from the metal surfaces

- After heating, the PCB is moved over a wave of melted solder

- The solder attaches to the solder pads and component legs, and the soldering is complete

#### **PCB** Assembly

- The assembly process consists of mounting and soldering the components onto the PCB

- Reflow Soldering

- Common (automated) soldering of SMT components

- Solder paste (containing both flux and solder) is applied to the solder pads

- before the components are placed on the PCB

- solder paste application is a silkscreen-like process

- using solder paste (top or bottom) mask

- Components are placed

- often automatically with pick 'n place machine

- PCB then heated in an oven

- solder in the paste melts (i.e. it reflows)

- Cooling the PCB, then cleaning off excess flux completes this type of soldering

#### **PCB** Assembly

Our assembly is done by hand by Rapid Prototypes LLC in Ventura, CA

#### http://www.rprototypes.com/

- Even though we make extensive use of surface mount technology, limiting the pitch of our devices and not using BGAs etc. allows them to successfully (and at reasonable cost) assemble our boards

- The quote for the 2013/2014 assembly is shown below

#### **QUOTATION # 2773**

John Johnson UCSB ECE (9560) DEPARTMENT Santa Barbara, Ca.93106-9560

Ph: 805 893-4161

| Item # | Qty | Description                                               | Unit Price                   | Extended Price   |

|--------|-----|-----------------------------------------------------------|------------------------------|------------------|

| 001    | 5   | UCSB189- AUTOPONIX PCB ASSY<br>HAND PLACE SMT COMPONENT   | \$220.00<br>S WITH EPOXY, A  | , ,, , , , , , , |

| 002    | 5   | UCSB189- FRIDGENIUS PCB ASSY<br>HAND PLACE SMT COMPONENTS | \$164.00<br>S WITH EPOXY, AI | ,                |

| 003    | 5   | UCSB189-REMUTT CONTROL PC<br>HAND PLACE SMT COMPONENTS    |                              | ,                |

- Generally, it is best to place parts only on the top side of the board

- (Rare) Exceptions: resistors and small passive components that won't be needed as test points

- When placing components, use the snap-to-grid feature with a fairly course grid

- Generally 0.010" is a good setup for the grid

- Helps you get your chips lined up nicely

- First: place all the components that need to be in specific locations

- e.g. connectors, switches, LEDs, mounting holes, heat sinks or any other item that needs to be mounted in a particular location.

- Pay attention to orientation of each part placed

- Think in particular about cabling and enclosures, etc.

- Place parts above the power plane region to which they connect (or draw in the plane region later)

- Leave some space around each IC for bypass caps

- We want the bypass caps to be as close as possible to the component pins that connect to power and GND.

- Give careful thought when placing components to minimize trace lengths

- Put parts next to other parts they connect to

- a good job here makes routing the traces much easier.

- Of course, the orientation of each part matters too

- Arrange ICs in only one or two orientations: vertically or horizontally

- avoid placement at "odd" angles

- if possible, align each IC so that pin #1 is in the same place for each part, e.g. on the top and/or left sides.

- this greatly aids the assembler but it isn't always possible

- Position polarized parts (i.e. diodes, electrolytic caps, etc.) with the positive leads all having the same orientation ..... (guideline only)

- Use silkscreen layer to clearly identify the polarity

- mandatory to do this for the assembler

- Use a square pad or silkscreen "+" to mark the positive leads of these components

- Critical info for assembler. Unlabeled orientation will trigger a telephone call ..... to me

- or worse .... it may result in a part soldered on backwards

- Leave ample space (and then some more) between ICs for traces.

- At least 0.350" 0.500" between small-to-medium ICs

- Allow proportionally more for larger ICs

- Amount is based on number of pins and location

- Added space helps in routing and also in debug access

#### Placing Power and Ground Traces

- For designs with multiple supply voltages...

- After the components are placed, layout any nonplane power and ground traces

- essential to have solid power and ground connections, using wide traces that connect to common rails for each supply

- very important to avoid "snaking" or daisy chaining the power lines from part to part

#### Routing Power and Ground Traces

- Routing multiple voltages: Use planes if at all possible

- But if you must route power and ground, do it in this style

- Use air conditioning (ductwork) model

- Make traces as short and direct as possible

- Use vias (feedthrough holes) to move signals from one side to the other

- 2 or 3 vias per net is probably OK

- more may be required on larger nets

- too many is bad, however .... >5 ?

- think about net shape and overall net length

- Use net selection tool to highlight a net so you can see it!

- Generally, the best strategy is to...

- Put vertical traces on one side of board and horizontal traces on the other

- Usually not a good idea to put routing on power or GND planes

- Add vias where needed to connect a horizontal trace to a vertical trace on the opposite side.

- Avoid connections fully underneath a component

- Always make sure some part of each trace can be seen (& cut)

- A good trace width for low current digital and analog signals is 0.010" (10 mils)

- minimum width design rule in Expedition is 6 mils

- may even be too large for some dense processor parts(!)

- Traces that carry significant current must be much wider than signal traces

- Rough guidelines of how wide to make a trace for a given amount of current

```

0.010" 0.3 Amps

```

0.015" 0.4 Amps

0.020" 0.7 Amps

0.025" 1.0 Amps

0.050" 2.0 Amps

0.100" 4.0 Amps

0.150" 6.0 Amps

- Space between the trace and any adjacent traces (wires), pads, or vias.

- Minimum gap of 0.006" between items (wire, pad, via)

- □ 6 mils is the design rule; 0.010" is better.

- Leaving less blank space runs the risk of a short circuit developing in the board manufacturing process

- Note that we cannot afford to pay for testing so any board fab problems usually result in a shorted board (!)

- Necessary to leave larger gaps when working with higher voltages

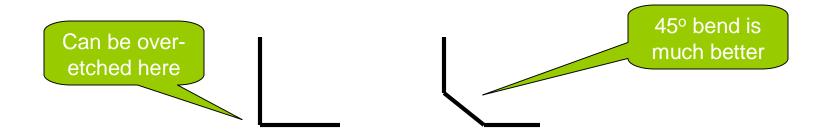

- Restrict the <u>direction</u> that traces run to horizontal, vertical, or 45° angles

- When placing narrow traces (≤ 0.012") avoid 90° turns

- In the manufacturing process, the outside corner can be overetched (becoming even narrower)

- Better to use two 45° bends with a short leg in between

# Checking Your Work

- Check the routing of every signal

- Verify that nothing is missing or incorrectly wired

- Trace through your schematic, one wire at a time

- Carefully follow the path of each trace on your PCB layout to verify that it is the same as specified on your schematic

- After each trace is confirmed, mark that signal on the schematic with a yellow highlighter

- Easiest to do this with another team member from your group

- Check for missing vias as well as shorted traces

- Use methods discussed in the ExpeditionPCB 'Analysis' section of our class tutorials

- run the DRC tool (and check its output!)

#### Some Sanity Checks

- Things to check

- Connections on power and GND planes (there should be some!)

- You should see pass thrus (N/C) as well as thermals (connections)

- It's OK if a via connects to a plane without a thermal ...

- Check carefully for region isolation when you have more than one voltage sharing the power plane

- Check that all connections to a given region are proper ones

- Planes are the first things I check when you submit a project to me

- Make a printout (1x) of top-side and bottom-side pads and trace

- Use it to check and re-check the fit of each of your packages

# Some Checks on your Sanity

#### NEVER EDIT THE GERBER FILES!!!

- Looking at the final Gerber is useful

- Try ViewMate from Pentalogix.com (free viewer)

- Usually not a good idea to try to edit the Gerber by hand

- Way too error prone

- Gerber editors are available

- usually one must buy these programs

# PCB Addendum: Gerber Plots

ECE 188A Senior Electrical Engineering Capstone Project

> John Johnson November 5, 2014

# Gerber Plots – Outputs from ExpeditionPCB

- Gerber plots needed for PCB fab (one per layer)

- Component side top (patterned copper interconnect)

- Solder side bottom (patterned copper interconnect)

- Power plane (inner power plane)

- Ground plane (inner ground plane)

- Component side solder mask (limits solder reflow)

- Solder side solder mask (limits solder reflow)

- Component side silkscreen (topside painted labels)

- Solder side silkscreen (optional, extra cost; only needed if components are placed on "solder side")

- Solder paste masks (both component and solder sides)

- Needed only for automated SMT assembly

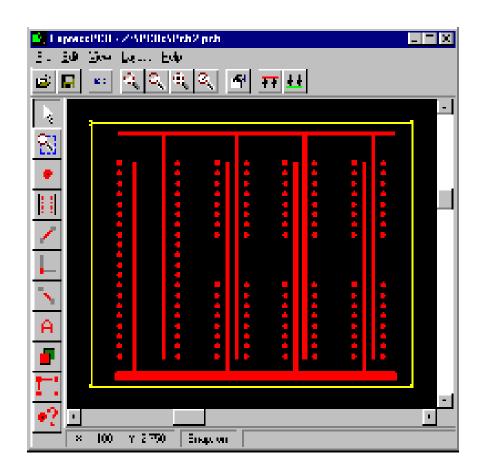

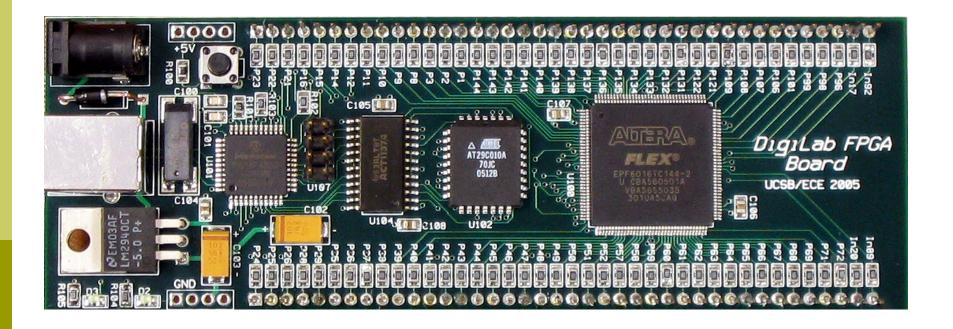

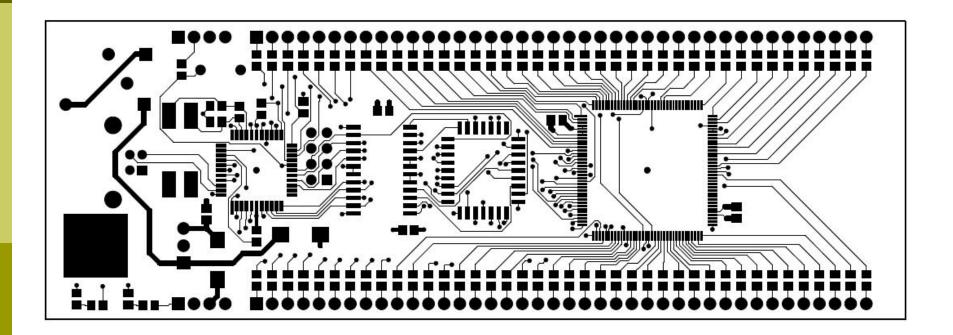

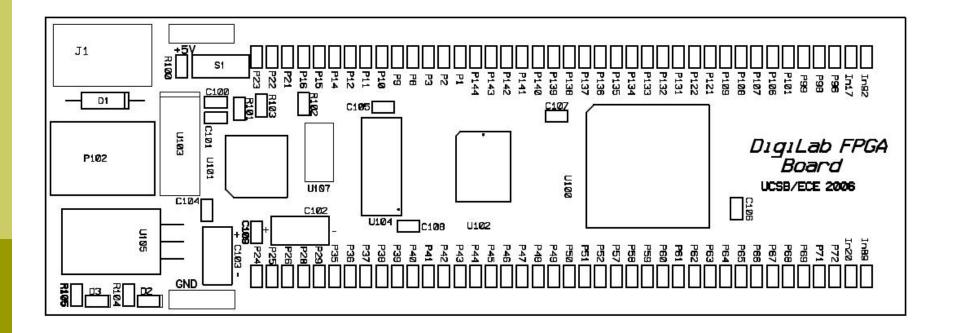

#### Example: Gerber Plots for Digilab-FPGA Board

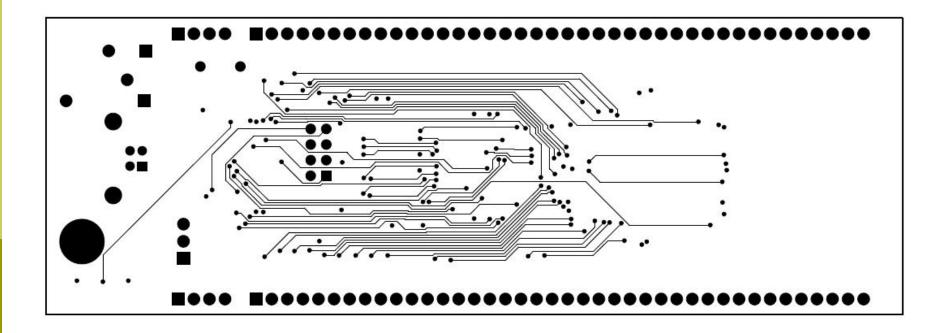

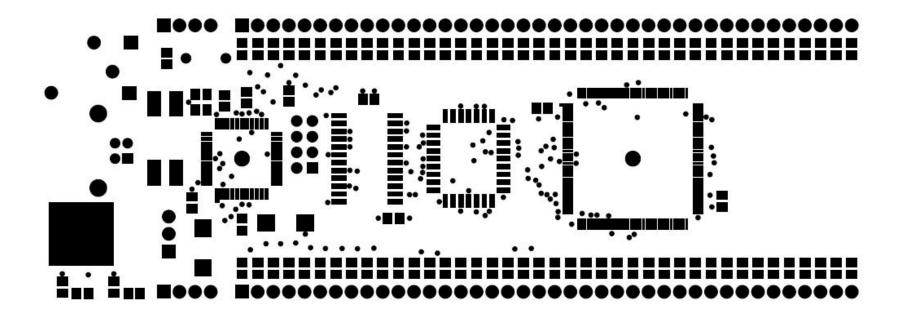

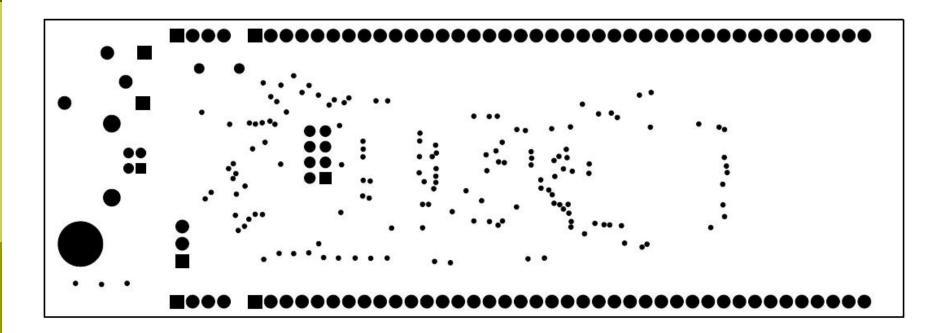

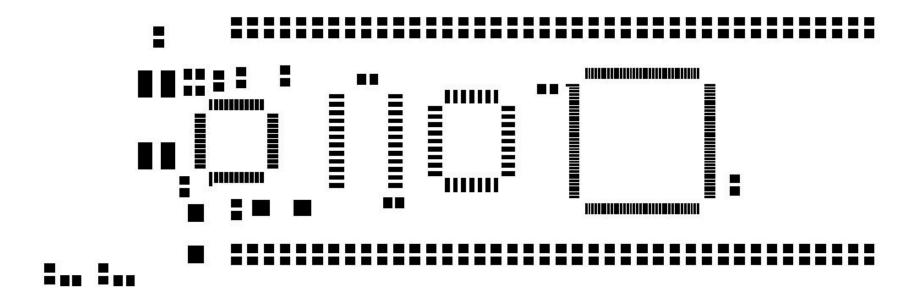

# Component Side (Layer1 "Top")

#### Component Side Silkscreen

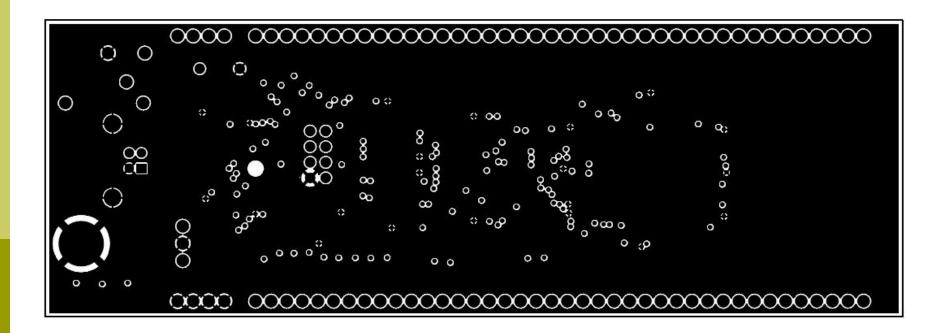

#### Inner Plane (Layer 2 ... GND)

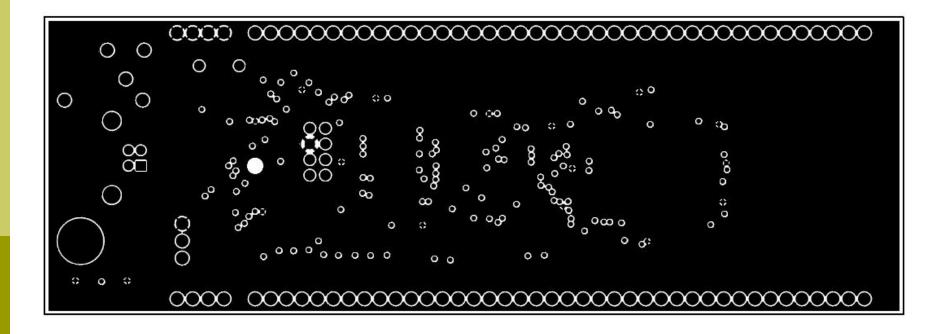

#### Inner Plane (Layer 3 ... Power)

#### Solder Side (Layer 4 ... Bottom)

### Solder Mask (Top side)

#### Solder Mask (Bottom side)

#### Solder Paste Mask (Top side)

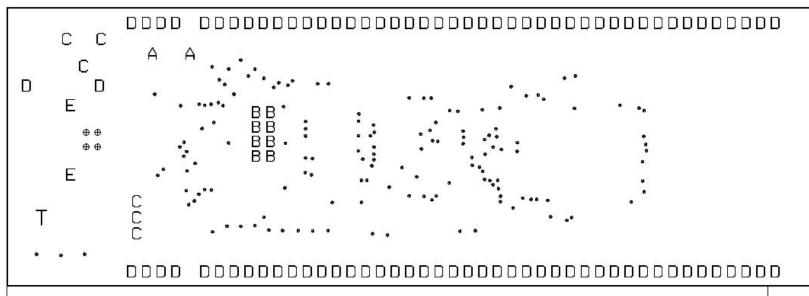

#### **Drill Drawing**

| Through Holes |               |                   |        |         |                       |          |

|---------------|---------------|-------------------|--------|---------|-----------------------|----------|

| Symbol        | Diameter (in) | Tolerance (in)    | Plated | Punched | Hole Name             | Quant:ty |

| Φ             | 0.0190        | +0.0000 / -0.0030 | Yes    | No      | Rnd 19 +Tol 0 -Tol -3 | 151      |

| В             | 0.0340        | +/- 0.0030        | Yes    | No      | 34th +/-3             | 8        |

| <b>⊕</b>      | 0.0390        |                   | Yes    | No      | HOLE_39               | 4        |

| D             | 0.0470        | +/- 0.0040        | Yes    | No      | 47th +/-4             | 90       |

| Α             | 0.0500        | +/- 0.0040        | Yes    | No      | 50th+/-4              | 2        |

| С             | 0.0600        | +/- 0.0040        | Yes    | No      | 60th+/-4              | 6        |

| E             | 0.0910        |                   | Yes    | No      | Rnd 91                | 2        |

| T             | 0.1500        | +/- 0.0080        | Yes    | No      | 150th +/-8            | 1        |

# PCB Addendum: Analog/Digital Isolation

ECE 188A Senior Electrical Engineering Capstone Project

> John Johnson November 5, 2014

#### Bypass & Decoupling Capacitors

- Decoupling capacitors are necessary on both the input side and the output side of all regulators

- In fact, throughout your board, the guideline is at least 1 bypass/decoupling capacitor per IC

- Nominal value is 0.1µF

- Smaller/faster vs. larger/slower is the tradeoff

- All IC's should have bypass/decoupling capacitors but reasons are different for analog and digital circuits

- In analog layouts, "bypass" capacitors redirect high frequency noise on power rail away from sensitive circuitry

- In digital layouts, "decoupling" capacitors serve as a charge reservoir, providing transient current when switching at high frequencies

#### Digital Decoupling Capacitors

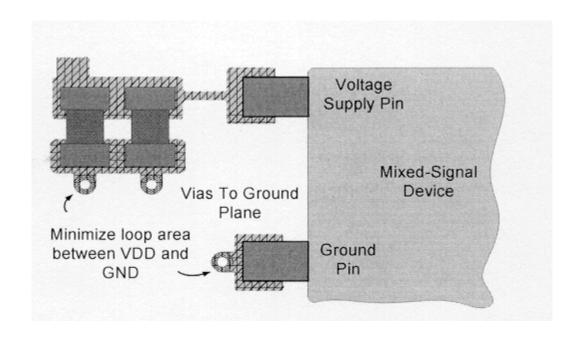

- The decoupling capacitor goes as close to the power pin as possible

- The supply side of the capacitor should be placed between the via (or trace) to the power supply and the IC's power pin

- The ground side of the capacitor should go directly through a via to the PCB ground plane

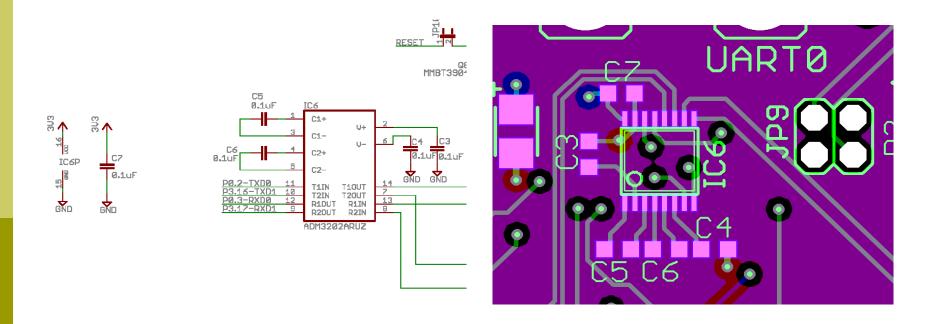

#### Digital Decoupling Capacitors

Sample schematic and layout

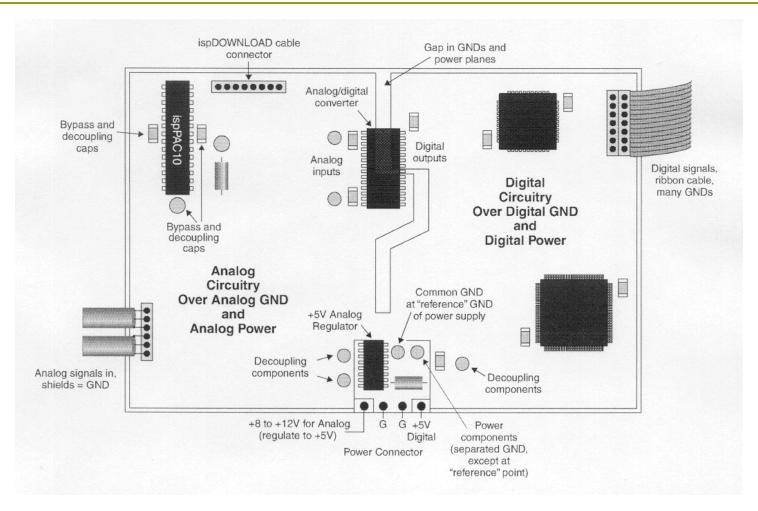

#### Analog / Digital Circuit Isolation

- In addition to multiple digital supply voltages, it is possible in many cases to have both analog and digital circuitry on the same board

- Switching noise from digital circuits cannot be allowed to disturb sensitive analog circuitry

- Analog and Digital Power, Ground and Circuitry need to be isolated from each other

- For example, the analog 3.3V supply needs to be completely disconnected from digital 3.3V supply

- However, the analog ground plane needs to be isolated (but still connected from a DC standpoint) from the digital ground plane

- There must be a single reference (GND) for the entire board

- A primary layout consideration is that the analog and digital ground planes should not overlap

- They should both be on the same PC board layer, separated by at least 0.1 inch

- The analog circuitry and the digital circuitry should likewise be separated over their respective ground planes

- Placing analog and digital circuitry at opposite ends of a circuit board is an excellent way to begin

- Do not surround the analog region with digital circuits or surround the digital region with analog circuits

- It will be impossible to route clean runs through the digital area to the analog circuitry or to keep the analog and digital runs separated

- Power supply circuits should be in a centralized area near the edge of the board so they can feed the digital and analog sections equally well

- A location near the edge of the board allows any return currents generated in this area to return directly to the main supply without passing through the rest of the board

- The analog and digital ground planes should be connected together at only one point

- Either at the local on-board power supply circuits or, preferably, where they leave the board to return to the main power supply

- When placing and routing the analog and digital circuitry over their respective ground planes, there should be no overlap between any of the analog areas (ground or power planes or circuitry) and any of the digital areas to minimize induced noise

- Do not cross signal runs between the planes unless absolutely necessary, for the same reason

- Return currents will not be able to jump the gap between the planes and will have to travel long distances to be reunited with the signal currents, usually picking up unwanted noise along the way.

- The best designs have analog power planes and an analog ground plane that exactly overlap, and digital power planes and a digital ground plane that exactly overlap

- The best performance is usually obtained when the ground plane is immediately underneath the power supply plane

- In our case, internal layers 2 and 3

#### Example Analog/Digital Layout

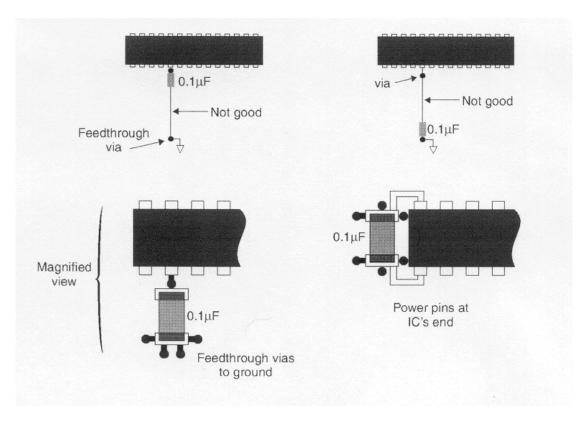

#### **Analog Bypass Capacitors**

- The capacitor should be placed as close to the IC as possible, on the same layer as the IC (to avoid the inductance of feed-through vias)

- The leads on these capacitors must be kept very short

- The best technique is to have the power feed from the power plane through a via to the capacitor and IC pins, with the capacitor between the via and the IC

- In precision analog applications, the ground connection is particularly important, and should be made with three to four vias connecting to the capacitor and thus to the IC pins

- The inductances of these vias are then effectively in parallel

- Surface-mount capacitors are best because their connection pads have almost no lead inductance

#### **Analog Bypass Capacitors**

#### Examples of bad and good layouts

## Mixed Signal Bypass/Decoupling Capacitors