#### Fabrication of NMOS Transistors DUE: Friday, Dec. 5, 2008

This lab will give you the chance to put together all the component processing knowledge you have been learning throughout the quarter, and carry out a multi-mask level process to produce an MOS Transistor. The principal processing steps are indicated below, and all of the critical procedures are provided in detailed documents that will be available on the class website.

It is up to you and your groups to design a plan and procedure that will *calibrate* and *verify* critical steps in the process. For example,

- Are you certain that the rate you assume for etching an oxide actually is the actual rate?

- Do you really know the thickness of the gate oxide you have formed?

- Are your metal interconnects really making contact to doped-semiconductor, or are they making contact to a thin oxide on top of the semiconductor?

You probably know by now that not every process step goes smoothly, and that *nominal* etch rates, deposition rates, oxidation rates, etc. may not be the *actual values* that you obtain for your samples. <u>Take that into account in the design of your lab procedures</u>, so that you have the best chance of measuring at least one good transistor.

The starting material will be a wafer of <u>p-type</u> <100> silicon with resistivity about 10-30 ohmcm. *Clean* your samples. Etch off the native oxide and measure the *resistivity* of the wafer, using a four point probe. Divide the wafer into the appropriate number of samples that will allow you to characterize the process, and that will give you some 'back-ups' for your devices.

## FORMING n-Si regions for SOURCE AND DRAIN

#### 1. Growth of oxide for a DIFFUSION mask.

- **a.** Prior to carrying out the oxidation, the samples must be given a **Piranha clean**. The instructions of this step are included in the documentation on **phosphorus diffusion**.

- **b.** The oxidation step is extremely sensitive to impurities: use the designated *boat* and *pushrod* for the silicon oxidation furnace. <u>Clean the boat and push rod</u> with HF prior to each oxidation.

- **c.** Grow at least 500 nm of wet oxide on your wafer. This forms the *field oxide*. Verify the thickness of the oxide.

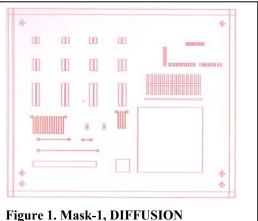

- 2. Photolithography using Mask-1 forms the DIFFUSION windows. Etch the oxide in buffered HF to form the windows in the oxide.

- 3. The oxide mask you've formed will define the regions of the wafer that are to be doped n-type by the PHOSPHORUS DIFFUSION PROCESS.

- **a.** Carry out *phosphorus predeposition*, at 950C for 15 minutes.

- **b.** Etch off the phosphorus glass in 10:1 DI H<sub>2</sub>O: HF, and measure the *resistivity* of the n-Si that you have formed.

- **c.** Load your samples into the oxidation furnace and *grow 350 nm of wet oxide*. This step serves two purposes: (a) driving in the dopant and (b) increasing the thickness of the field oxide.

## FORMING THE GATE REGONS

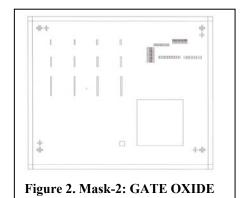

- 1. Photolithography using Mask-2 forms the regions where a thin GATE OXIDE will be grown. *The mask-2 patterns need to be aligned to <u>alignment marks</u> patterned from mask-1. After exposure and development of the gate oxide pattern, etch the field oxide in buffered HF until you reach the substrate surface.*

- 2. Carry out a *Piranha clean* on your samples, and grow a **dry oxide** of thickness 50 to 80 nm. Verify the thickness of the oxide.

#### FORMING VIAS TO SOURCE AND DRAIN

- 1. Photolithography using Mask-3 defines windows or vias that allow contact to the SOURCE and DRAIN regions, while masking the GATE region.

- 2. Using the pattern formed by Mask-3, form the **contact windows** by etching the samples in buffered HF. Again, take care to align mask-3 patterns to previous patterns. *It is essential to remove all the oxide in these regions.*

| 10-11         |     |       | п <sup>о</sup> | 100.000 | * |

|---------------|-----|-------|----------------|---------|---|

| 11            | 11  | 110   | 110            |         |   |

| -             | ∥°. |       | "              |         |   |

|               |     | s = = |                |         |   |

| ‡ aaaaaaaaaaa |     |       |                | ÷       |   |

# FORMING METAL CONTACTS TO SOURCE, DRAIN AND GATE

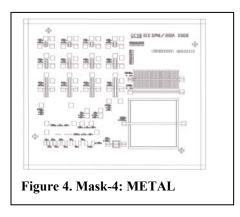

- 1. Photolithography using Mask-4 defines the metal lines, by *lift-off* that will make electrical contact to the device areas.

- 2. Using the pattern formed by Mask-4, evaporate 300 nm of Aluminum. Make sure that the Al is making contact to the silicon surface, rather than any *surface oxide*.

- **3.** Sinter the contacts for 10 minutes at 450C in the strip annealer.

# CHARACTERIZING THE OPERATION OF YOUR TRANSISTORS

Measure the CURRENT-VOLTAGE (I-V) characteristics of your transistors. (We will do a simple analysis of transistor behavior in class, so you will know the key features to look for.

#### FORMAT OF THE LAB REPORTS

A single lab report is to be prepared by each group: the designation of responsibilities in carrying out the lab, and in the completion of the lab report is to be made within each group. <u>Treat this laboratory report like a *Technical Memo*</u>, a real assessment and evaluation of the process that you are examining, a description of the final performance of the device, an analysis of key challenges in the process. A *suggested format* is:

A. Introduction: General statement of the goals of this work.

#### **B.** Technical Description:

- a. Give an accurate description of the experimental procedure, including a description of the starting material, and all the *relevant* processes that you have performed. Describe your procedures *concisely*, yet be sure to include any *critical features* in your procedure.

- The procedures you have been using are all thoroughly documented in various process documents (oxidation, lithography, etc.). *Please don't repeat all the details of the document in your report.*

- *Do* include relevant features, such as 'oxidation carried out at \_\_\_\_\_ oC for \_\_\_\_\_ minutes'.

- Please *do* mention when you apply/remove resist, when you *clean* or etch your samples, when and how you measure your samples.

- b. Include data in readable and 'enlightening' form, such as graphs and photographs.

- c. Discuss what critical problems arose during the experiment and your solutions to them. What special challenges were there for this <u>integrated process?</u>

- d. Set the discussion of the data within a *broad context*. Are the results you obtained reasonable ones? What were your expectations? If you didn't get 'reasonable' results, *what occurred in the experiment that led to those results*?

- e. Statistical Analysis and Error: learn the importance of *statistics and error evaluation* in your experiments. Learn which data points you can 'trust', what the variations in your measurements are. Try as much as possible to make measurements for several samples, or to make repeated measurements on a given sample. If you are generating graphs of data, do not connect-the-dots, but try to draw the 'best curve', using your data points, that describes the functional relationship of one parameter on another (for example, the resist thickness versus exposure time in your contrast curve).

- C. **Summary:** Summarize your experimental findings and draw your conclusions. Substantiate your conclusions with your data.