# ECE137AB: Writing Preliminary Design reports and Lab Reports

Mark Rodwell, ECE Dept, UCSB January 24, 2003

### **Background**

Engineering design is a balance of theory and testing. The IC design flow is as follows. The circuit is first designed on-paper and verified mathematically to the level of accuracy one can do hand calculations. Circuit designs are then verified by computer simulation, making certain that the design meets all specifications over all possible values of transistor parameters (Maximum and minimum values of beta, power supply voltage, temperature, resistor values, ...). At this point the design team will meet with supervision to verify the design process. Only then is the IC design committed to a mask and initial lots fabricated.

After initial lot fabrication, ICs are packaged, and the design engineer spends extensive time testing the IC to ensure that it functions over all conceivable variations of conditions...again supply voltage, process technology minimum and maximum values for transistor and passive element parameters, temperature, and perhaps drive voltage and loading conditions. Design failures have to be diagnosed, the circuit re-analyzed to understand the failure mode, and the design corrected. The fab/testing cycle then repeats.

In this class, design is being studied. Circuit designs should be fully verified by hand calculation before any circuit assembly takes place. Verification means that the DC bias conditions have been calculated over the allowable range of transistor parameters, and that a set of calculations has been performed proving that each specification has been met.

Format of the Preliminary Design reports and Lab Reports is therefore as follows:

#### Project design objectives

The objective is to design, build, and test a small audio power amplifier to drive a loudspeaker.

**Specifications**

- 1) The speaker is an 8 Ohm load.

- 2) A differential input is required.

- 3) Voltage Gain: 20, plus or minus 10%, measured at 1 kHz.

- 4) Variation in gain less than +/- 1 dB between 20 Hz and 20 kHz.

- 5) Peak-peak output swing before clipping: greater than 3 volts peak-peak.

- 6) Power supplies: Positive and negative 5 volts.

- 7) The input is to be differential, with a 75 dB CMRR at 1 KHz.

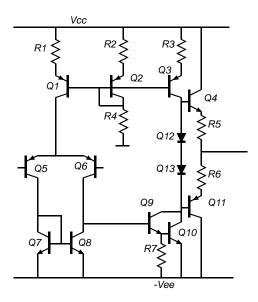

### Circuit diagram

Here is the circuit diagram of the reported design (component values should all be given)

# **Design Discussion**

On a multi-stage design, comment on the main features of the design, what function each stage performs, why the general topology was chosen, and any relevant design difficulties worth \*concise\* discussion.

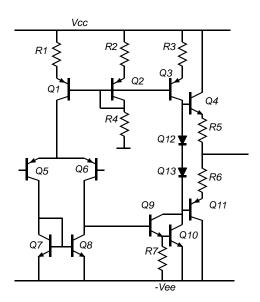

# Bias analysis

Circuit diagram with all DC bias conditions shown.

Calculations here show the how the DC bias conditions are found.

## **Performance Analysis**

(Several pages)

- 1) Calculations proving that the circuit meets specification #1

- 2) Calculations proving that the circuit meets specification #2 Etc.

Note that in some cases the calculations must be double-checked with minimum and maximum values of beta or power supply voltage.

-----this would be the end of the preliminary design report. The final report would repeat the above material (using the final design values, if changed from the initial design), but would also include the following------

#### **Performance Measurements**

(The TA-signed checkoff sheet goes here)

### **Performance Analysis**

Discuss here on any discrepancies between the performance predicted by your design analysis and the measurements. If the design did not work as expected, to the best of your ability, describe why. The more precise and analytic, the better.