# High Speed Bipolar Mixed Signal and Communication ICs Exercise in Running the Simulation Tools and Introductory Circuits

The exercises below are designed to \*\*complement\* your running the ADS tutorials (in ADS documentation), which are highly recommended.

| FIRST: MECHANICS OF ACCESSING THE PROGRAM         | 2  |

|---------------------------------------------------|----|

| DOWNLOADING THE ADS PROJECT DIRECTORY             | 2  |

| EXAMPLES OF ADS SIMULATIONS:                      | 2  |

| DIFFERENTIAL S-PARAMETER SIMULATION               |    |

| S-PARAMETER SIMULATION SINGLE-ENDED               |    |

| TRANSIENT SIMULATION AND EYE PATTERNSDIFFERENTIAL | 13 |

| Transient Simulation and Eye Patternssingle-ended |    |

| MODELING BIPOLAR TRANSISTORS:                     | 22 |

| SPICE MODEL                                       | 22 |

| SUBCIRCUIT MODEL WITH SPICE MODEL WITHIN          | 22 |

| S-parameter Data File                             | 29 |

| SMALL-SIGNAL MODELS                               | 29 |

| INTERCONNECTS                                     | 31 |

| PROCESS CROSS-SECTION                             | 31 |

| INTERCONNECT MODELS (ROUGHLY)                     | 32 |

| COMMENT: ADS MOMENTUM                             |    |

| EXERCISES                                         | 35 |

## First: Mechanics of Accessing the program.

I have set up some example ADS directories to aid in getting the tools running quickly.

## Downloading the ADS project directory

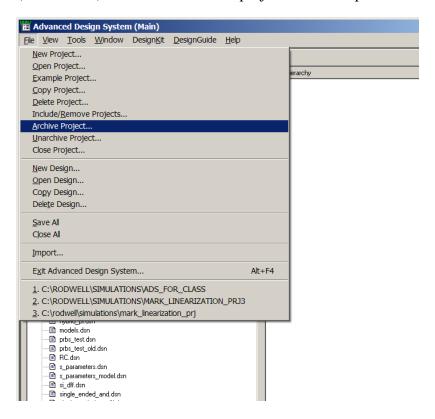

On my web page will be a compressed ADS project directory. This is in a ZAPPED format, which sounds like, but is not, a Zipped format. Download it using a web browser (save to disc) and then \*unarchive project\* to decompress it:

### **Examples of ADS simulations:**

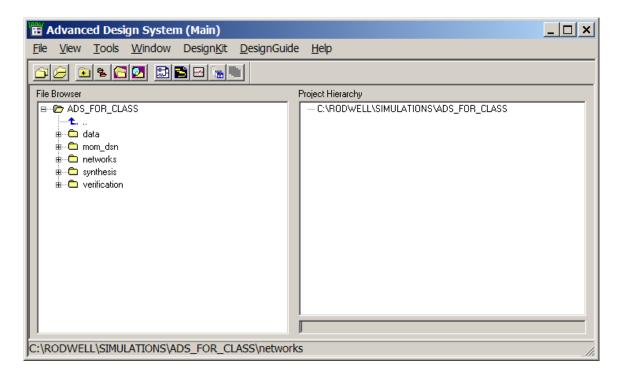

Download the project, Unarchive it as illustrated above, and open it. You should then see the following:

...you can open schematic editor window, by clicking on the button which looks like a schematic....but you may not need to: often the program opens itself in the state it was last saved.

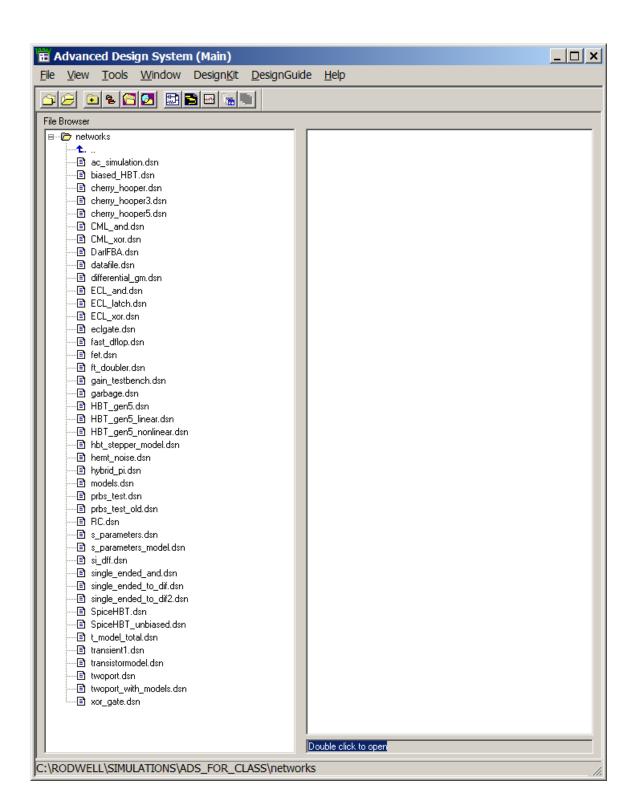

You can expand the file browser window to see available circuits (I have given you lots):

## <u>Differential S-parameter Simulation</u>

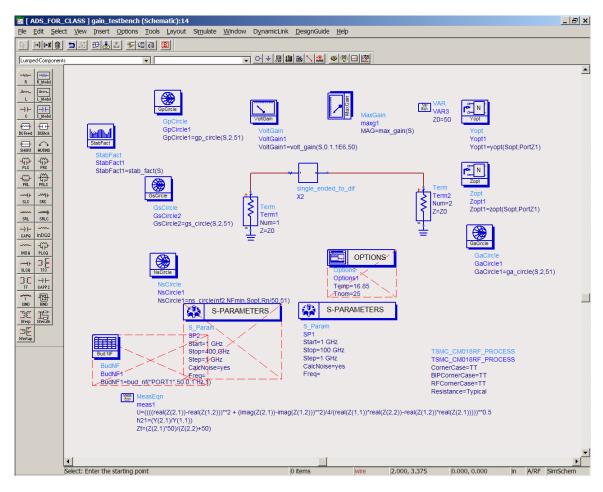

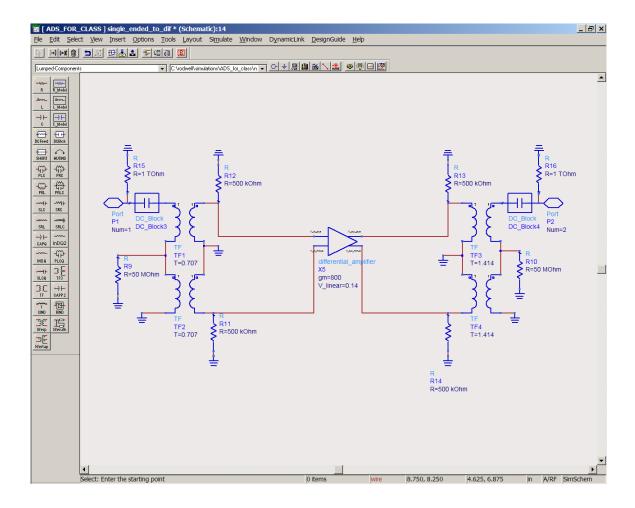

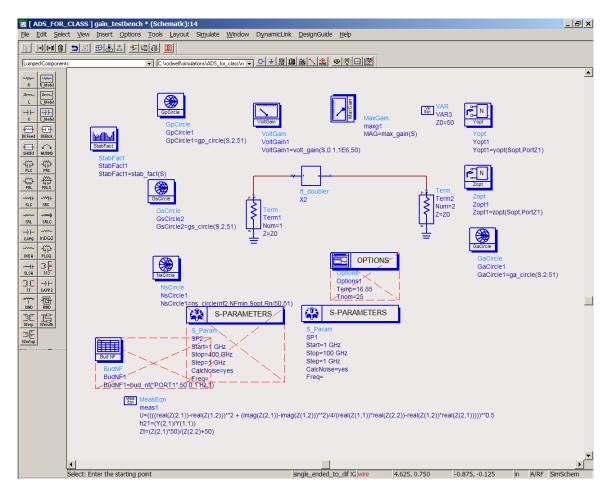

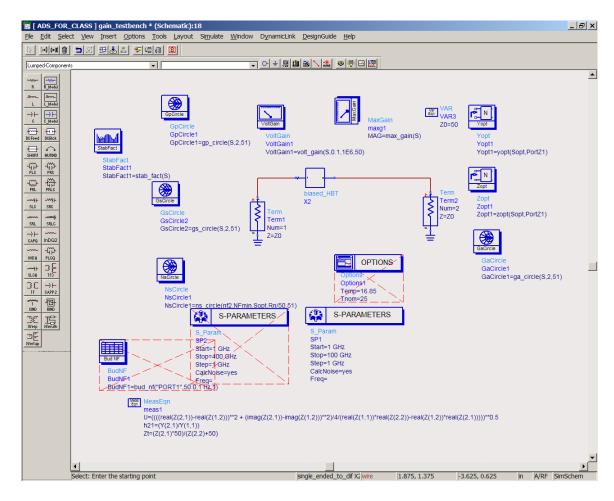

Open up the file gain\_testbench which I have created to calculate S-parameters:

This will test for Sparameters of the subcircuit "single\_ended\_to\_dif". You can type the name of other subcircuits there to test them instead.

You will see a "down arrow" button which is used to pop into the network hierarchy. Click on it, then on the "single\_ended\_to\_dif" subcircuit to move into the hierarchy.

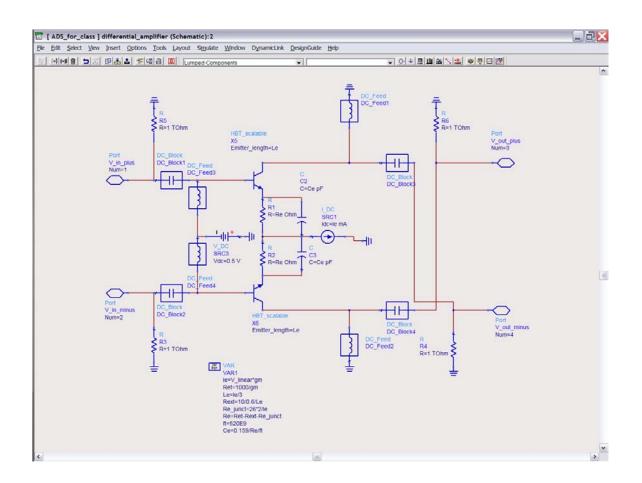

This is a utility block I created, which allows one to simulate for S parameters of a differential circuit (in this case the circuit is differential\_amplifier). This is a trick to overcome a shortcoming in ADS: it is otherwise hard to make it compute S parameters of differential circuits. Pop into it, and you see a common form of high frequency amplifier:

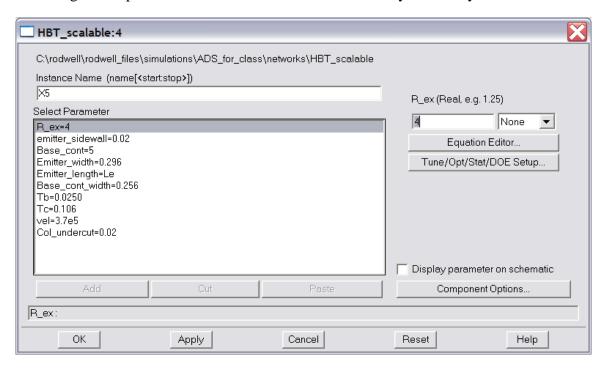

IMPORTANT: select the transistor, and double click on it and make sure that the following model parameters are set for \*all\* devices which you use in your circuit:

### In this list

Rex = 4 Ohm-micron^2 is the parasitic emitter resistance per unit area emitter\_sidewall=0.02 micron is the emitter sidewall thickness base cont = 5 Ohm-micron^2 is the base contact resistance per unit base contact resistance per un

**base\_cont= 5** Ohm-micron^2 is the base contact resistance per unit base contact area **emitter width=0.296** is the emitter junction width\*

\*the physical emitter junction width is 0.296-2\*(emitter sidewall)=0.256 um **emitter length,** here set = to the variable Le, is the emitter length in microns **base\_cont\_width=0.256** micron is the base contact width

**Tb=0.025** is the base thickness in microns

Tc=0.106 is the collector depletion layer thickness in microns vel=3.7e5 is the collector electron saturation drift velocity in m/s Col\_undercut =0.02 micron is the base-collector junction undercut the width of the base-collector

In all of your circuits, \*\*all\*\* of the parameters should be set to the above values, except the emitter length Le, which you may set to 1, 2, 4, or 8 microns. For convenience, and clarity in the circuit diagram, only the emitter length is shown by default. This has the danger that you may be inadvertently setting these transistor parameters to undesired values!

The device has a maximum operating current of  $\sim 3mA/micron* Le$ , and a maximum power dissipation of about  $4 \ mW/micron* Le$

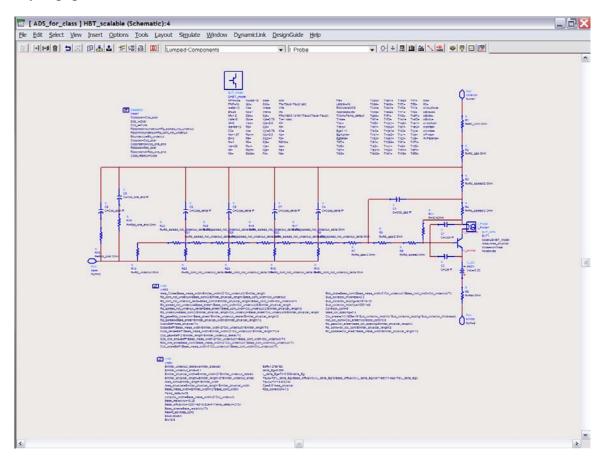

## If you pop into the transistor:

The transistor is defined as a SPICE model (DHBT model), with external parasitic resistances and capacitances which we have defined through equations from the transistor geometry. We do this at UCSB because it allows us to make fairly accurate predictions of performance of future transistors which we may not yet have built.

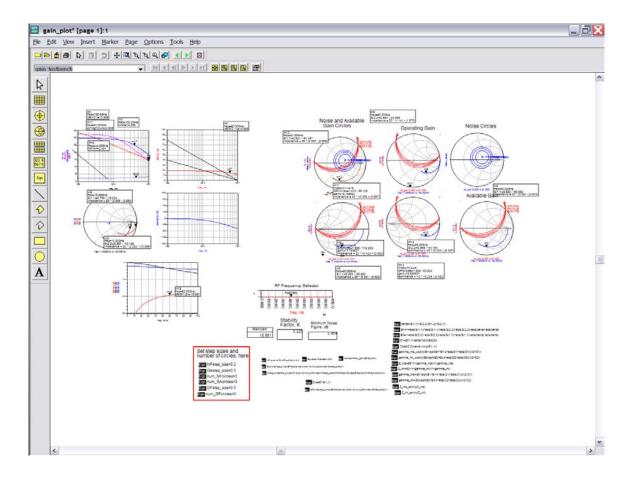

Now pop back up to the top level in the hierarchy and then "Simulate", and (if it does not happen automatically), open up a plot of results (window→open data display→"gain\_testbench") to open up a set of plots I have pre-created:

There are dB and polar plots of S-parameters, and plots of H21 and U (relevant for transistors, no relevant for the IC). There are also noise figure circles and gain circles, which are relevant to microwave tuned amplifier design.

If you change pages (push the green arrow buttons on the menu bar), there are also plots of Y and Z and S parameters, and plots of open-circuit voltage gains, etc.

Click on the toolbar on the left-hand side, and you can add other plots.

## S-parameter simulation single-ended

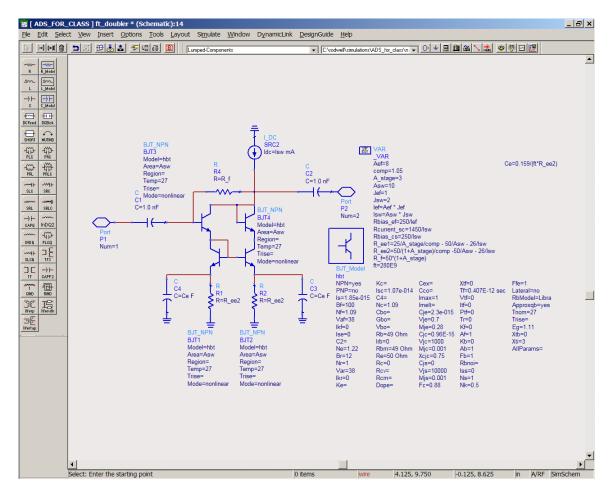

We can go back to the s\_parameters circuit and edit the circuit under test to ft\_doubler:

Pop into this (single\_ended) circuit and see the amplifier:

Note that a different transistor model is here used; there is no subcircuit with an associated set of equation-defined parasitics. This is the more common approach in IC design.

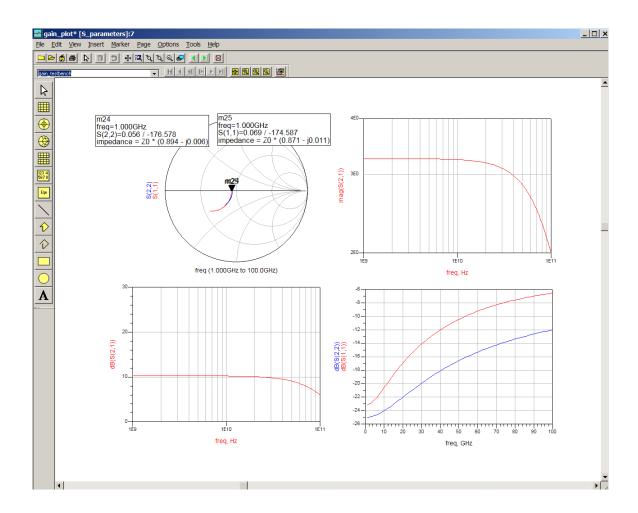

Pop back out, and hit simulate:

# Transient Simulation and Eye Patterns--differential.

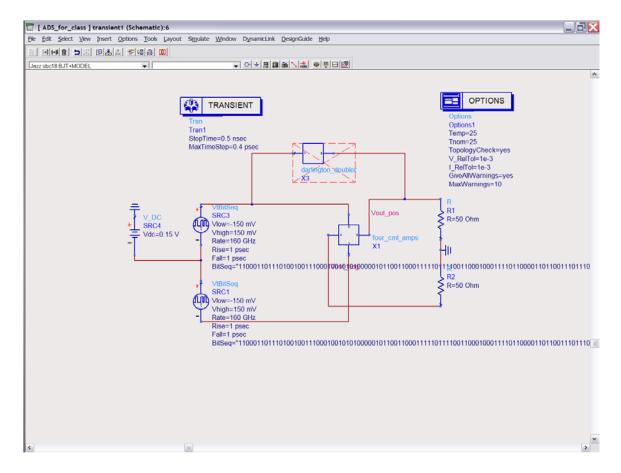

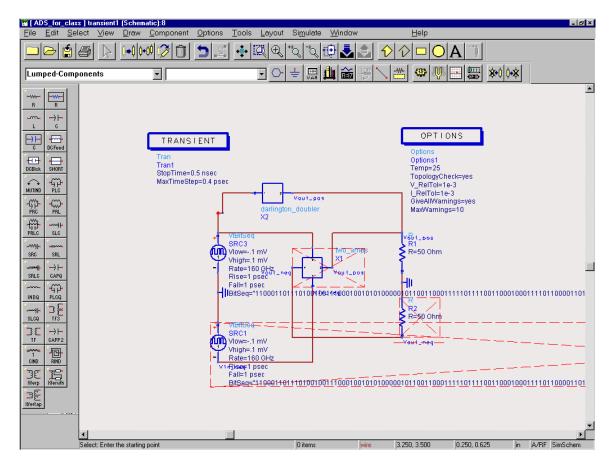

Now open up the test bench transient 1 (and zoom in a bit!)

You will see a couple of circuits. Darlington\_doubler is a single-ended circuit, and is currently "inactivated". There is a differential circuit, "four\_cml\_amps", which is active. There is a pair of (random) data string generators, which are logical complements of each other. For square-wave testing you could replace these with e.g. a square wave generator.

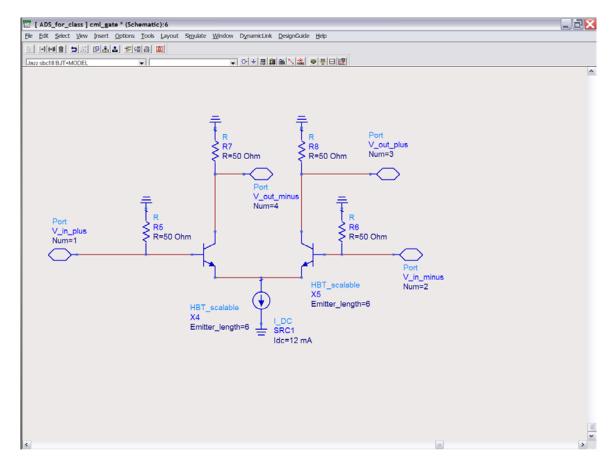

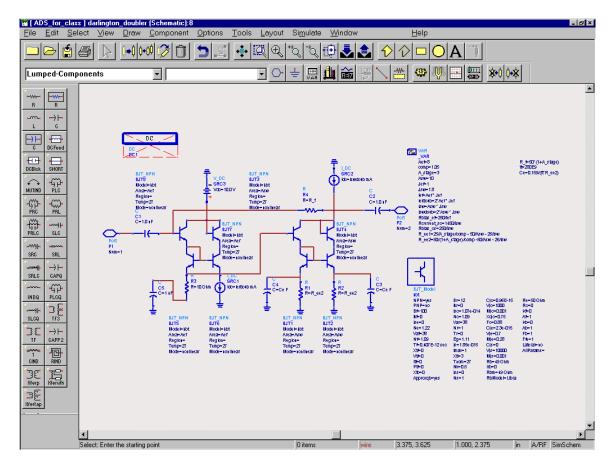

Pop into "four\_cml\_amps". It is a set of four cascaded amplifiers, each of which is a simple CML logic gate, which we are operating here as simple differential limiting amplifier.

You can pop in again to see the circuit:

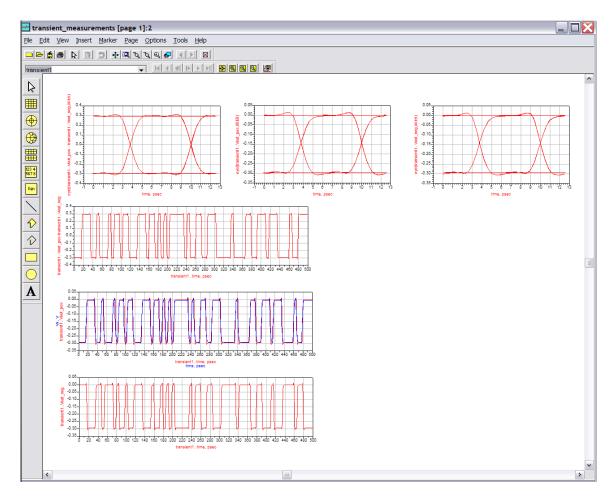

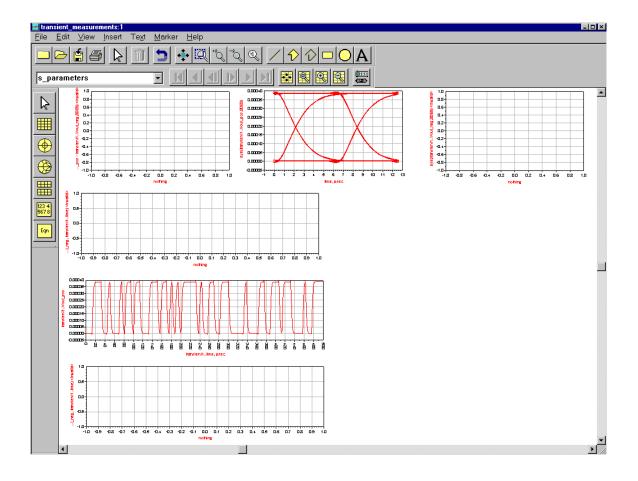

Pop back out to the highest level, and simulate. Then open up the graph window "transient measurements 1"

...and you can see the eye pattern and pulse response of Vout of the circuit:

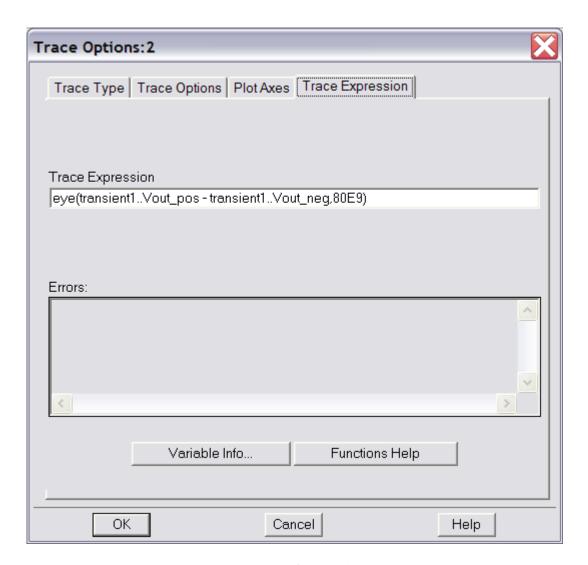

Clicking on the vertical axis of the eye pattern display reveals the syntax necessary to plot an eye pattern:

Note that the last number 80E9, is set at 1/2 the bit rate of the simulation.

## Transient Simulation and Eye Patterns--single-ended

To simulate a single-ended circuit, we activate and deactivate a few components:

Pop into Darlington\_doubler to take a look (a fairly exotic circuit block)

And pop back up and re simulate:

## **Modeling Bipolar Transistors:**

We can do this several ways:

## Spice MODEL

We have a model file, BJT\_MODEL, which we then invoke with an area statement. This is a large signal model which defaults to a small signal model (with bias-dependent parameters) when we do a S-parameter simulation.

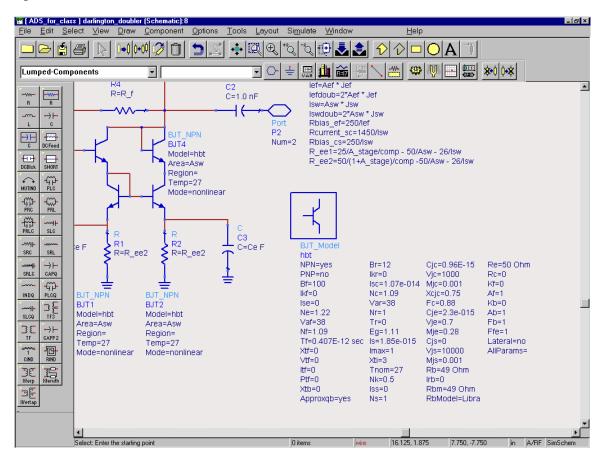

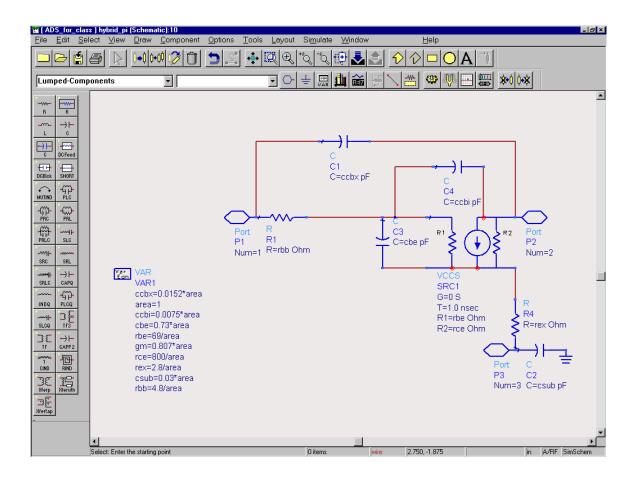

### Subcircuit model with SPICE MODEL within

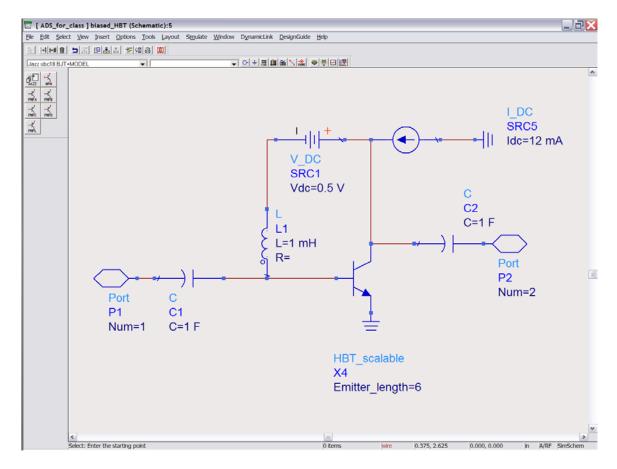

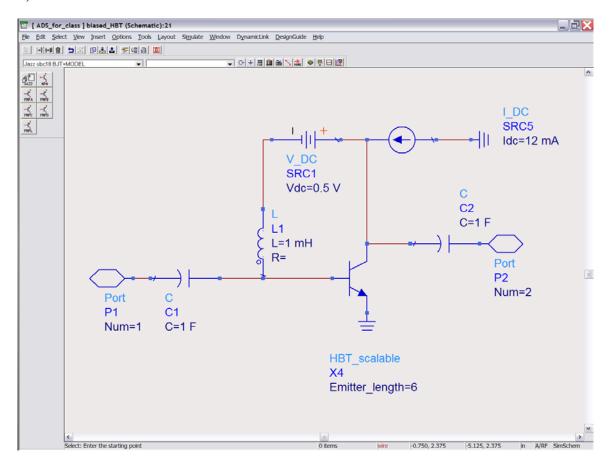

Here is a circuit (HBT under test)

HBT\_scalable is a subcircuit with PASSED parameters

Rex is the emitter resistance per unit area,

base\_cont is the base contact resistivity in ohm-micron^2,

emitter width and emitter length are the length and width of the emitter in microns,

base\_cont\_width is the base contact width in microns

Tb is the base thickness in microns

Tc is the collector thickness in microns.

vel is the collector electron velocity

col\_undercut is the undercut under the base contacts.

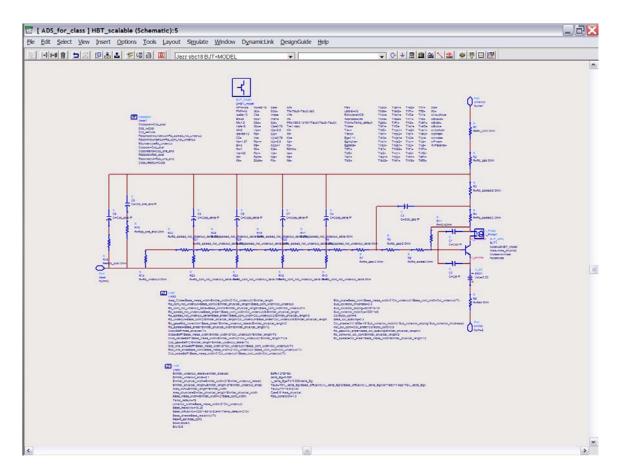

Popping into this model, as we did earlier, and you see the underlying definition based upon a SPICE model, with some additional parasitics and most of the device R's C's, and tau's defined in terms of the device physical dimensions:

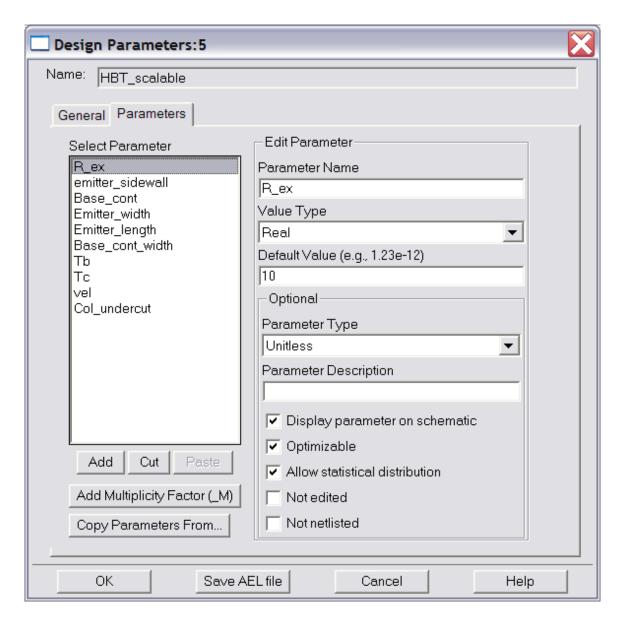

Go to file  $\rightarrow$  design parameters, and you will see how the passed parameters are defined (you should not need to play with this)

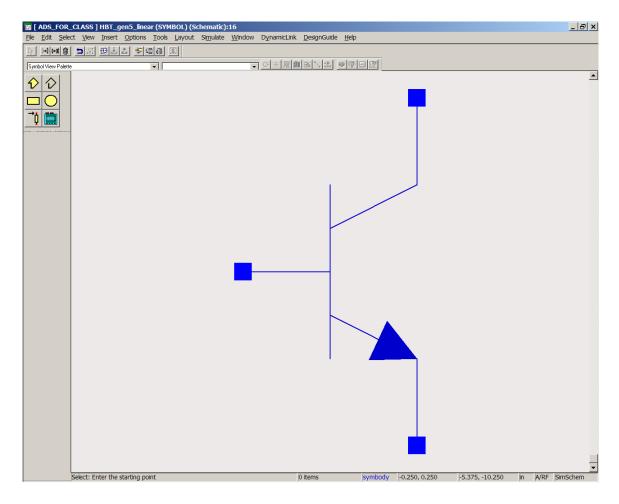

Go to view  $\rightarrow$  create/edit Schematic symbol and you will see how the subcircuit is given a pretty symbol:

You can edit such symbols, but do so for a backed-up file first, as the editor is somewhat hard to use.

Pop back out to biased\_HBT, then open the circuit gain\_testbench, and change the DUT to biased\_HBT:

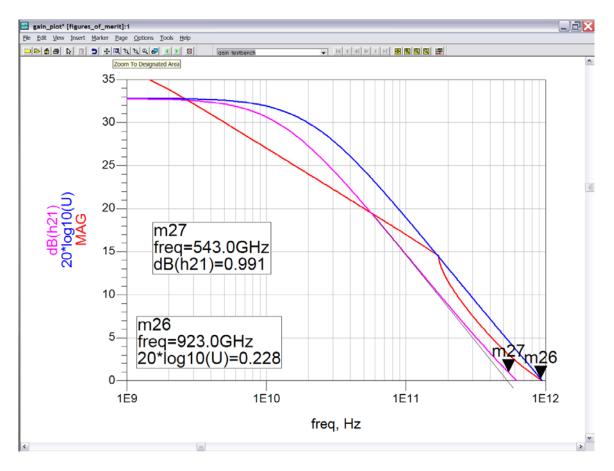

I have increased the frequency range to 1-1000 GHz, and on the figures\_of\_merit page of the gain plot we can now see the transistor high-frequency gains:

The device has an ft around 540 GHz and an fmax around 900 GHz.

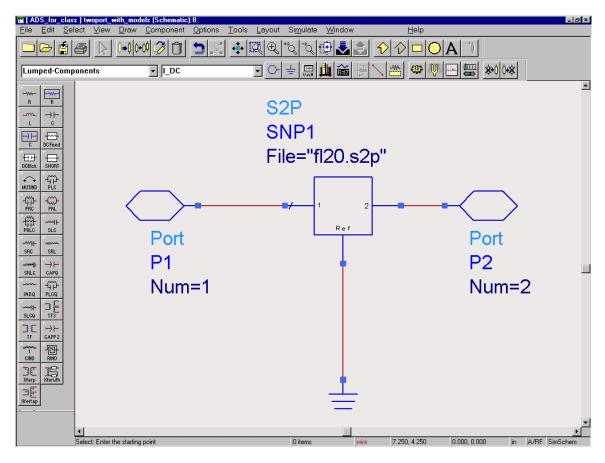

## S-parameter Data File

If you have measured data in tabular S parameter form, you can simulate from that

this is FYI only: I have not provided any such data set for you to use.

## Small-Signal Models

You can directly create hybrid pi models by method. Of course, there is no DC information being carried in this simulation model.

### **Interconnects**

## Process cross-section

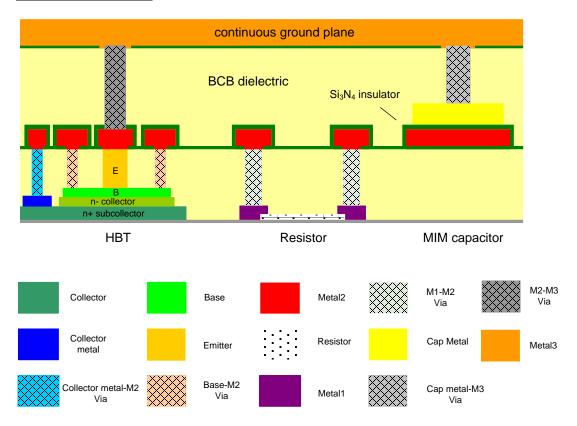

The process provides three metal layers, M1, M2, and M3. Normally, M3 will be used as a ground plane and M1 or M2 as signal lines.

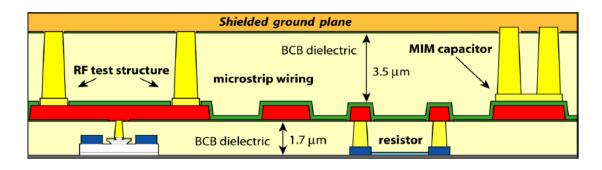

The cross-section below may also be helpful:

Note the thicknesses of the two BCB layers, and note that BCB has a dielectric constant of 3.8. Below the plane of the HBT subcollector, and below the resistors and metal 1, lies the semi-insulating InP substrate, having a dielectric constant of 13. We will approximate that M1 and M2 are each 1/2 micron thick.

### Interconnect models (roughly)

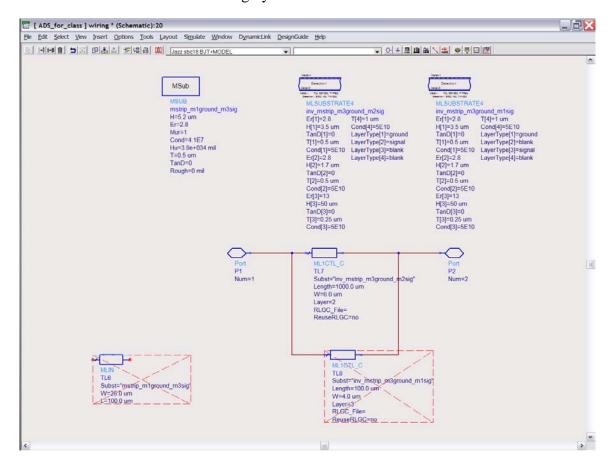

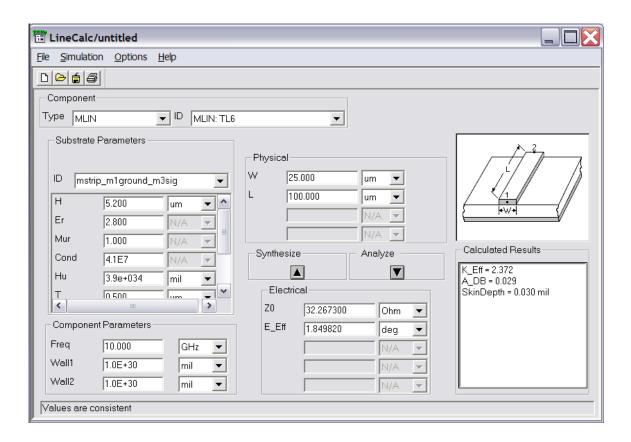

These interconnects can be \*\*\*roughly\*\*\* modeled as below:

The model "inv\_mstrip\_m3ground\_m2sig" is used for lines with an M3 ground plane and M2 signal line. The model "inv\_mstrip\_m3ground\_m1sig" is used for lines with an M3 ground plane and M1 signal line. There are limitations for this modeling strategy:

- a) I can't seem to make these models calculate metal line resistance correctly, so I have set the resistance to zero. This will be a serious error for long wires.

- b) the associated substrate models are not supported by LINECALC. More on linecalc below.

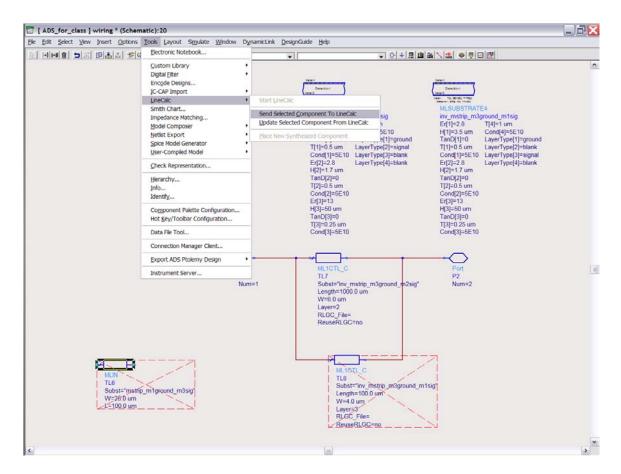

The model "mstrip\_m1ground\_m3\_sig" is a good and fairly accurate model for lines using metal 1 as the ground plane and m3 as the signal line. There are problems in using such lines; see the class notes. For lines of this type, we can select it, and then send its parameters to LINECALC:

...which allows very quick determination of line Zo, delay, and attenuation.

## Comment: ADS MOMENTUM

In reality, we use ADS MOMENTUM to model a short section of line, and from this determine its inductance, capacitance, and resistance per unit length. From this we usually can fit lines of a specified geometry to a ADS TLINP model. MOMENTUM is a fast, accurate, and powerful tool, but there is not time to learn it in this class.

### **Exercises**

1) first, please run all the above simulations. Make sure you can make them all work.

### 2) transistor simulation

Using the above model and the biased\_HBT test bench, set up a transistor with the above parameters, but adjust the bias to a current density of 1 mA *per linear micron of emitter length* and Vcb=0.5 Volts. Simulate and plot H21 and U. Determine ft and fmax.

### 3) S-parameter Circuit simulation

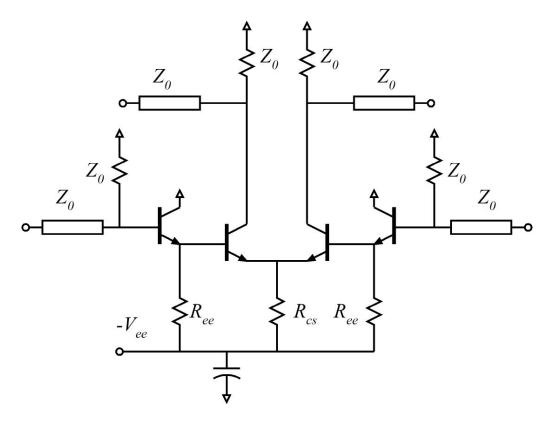

Create a Darlington differential pair amplifier with 2 DHBTs, each having parameters as above, except adjust the emitter length so that all transistors are biased at 1.2 mA *per linear micron of emitter length* when biased at 10 mA each. The basis circuit is as below, but you must think hard about the DC biasing. The resistors labeled Zo are 50 Ohms. The external load is 50 Ohms

Simulate this to determine the 4 S-parameters. Determine the gain and bandwidth of S21. Recall that S-parameters are equivalent to gains with 50 Ohm generator and load impedances.

## 4) Transient Circuit simulation.

Simulate the transient response of this circuit to a PRBS pattern with 1 mV pp input. Adjust the data rate to that which provides reasonable performance. Recall the need for external 50 Ohm generator and loads.

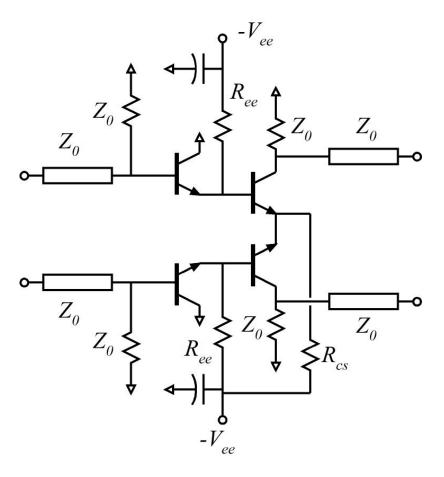

### 5) Mask layout

Using the available CML differential amplifier as a guide, generate an ADS mask layout for the amplifier. Hint: a floorplan like that below will facilitate layout.

# 6) Re-simulation:

Measure the lengths of wires in your mask layout. Add models for these wires to the circuit file and resimulate.