# High Speed Mixed Signal IC Design Notes set 5: Digital IC design at the Gate level

# Mark Rodwell University of California, Santa Barbara

rodwell@ece.ucsb.edu 805-893-3244, 805-893-3262 fax

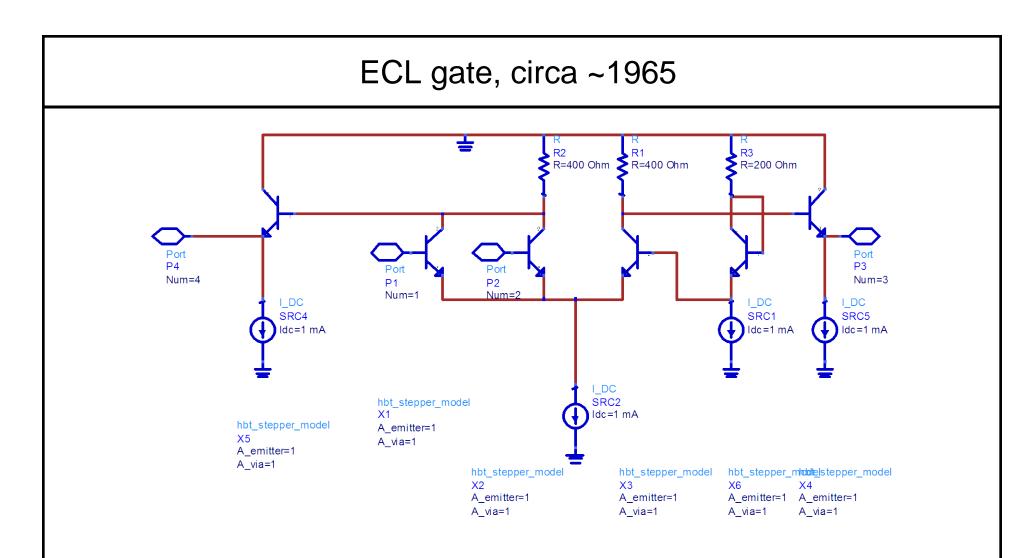

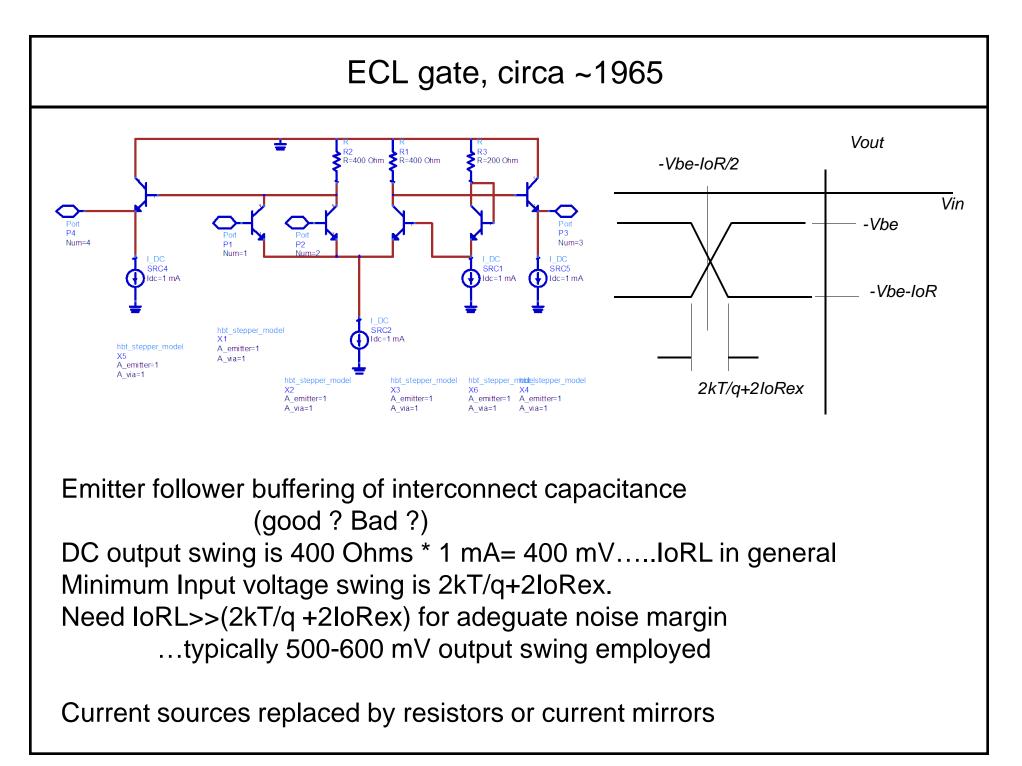

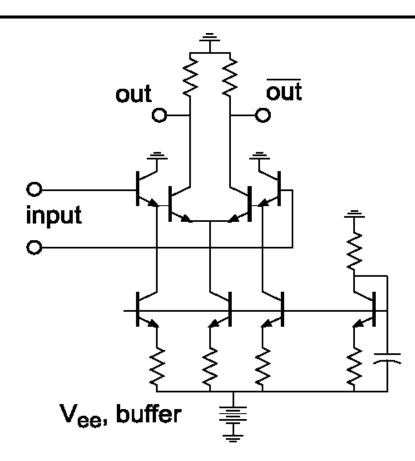

This is an \*OR/NOR gate....port 3 is high if ports 1 or 2 are high ...port 4 is the logical complement of port 3

Gate is single-ended....differential ckt generally preferred why? (standard reasons given are not so convincing...) one reason is 2:1 lower permissible logic swing, less power

Gate uses emitter followers on \*\*output\*\*....this can result in strong transmission-line ringing....  $\overline{\geq}$

Output impedance of emitter follower is  $Z_{out} \approx 1/g_m + R_L(jf/f_\tau)$ , which is inductive. Load on receivng end is capacitive.... Line can ring strongly.

Partial mitigation : EF biased by pull - down resistor on receving end of line, biased at e.g. - 2 Volts...this consumes substantial power

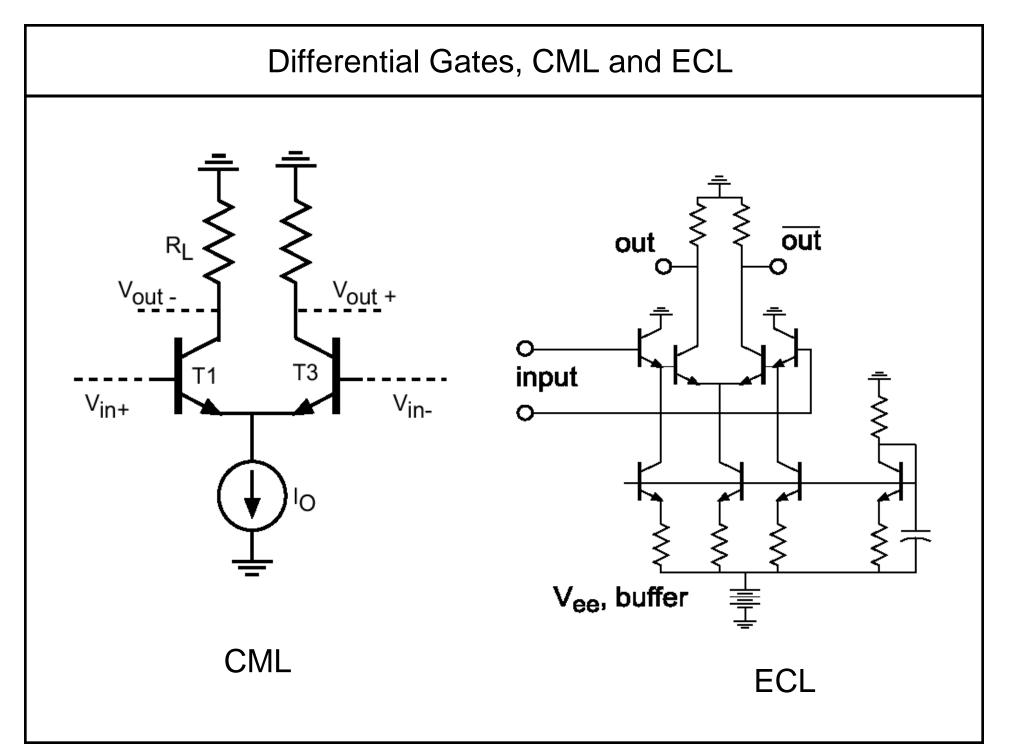

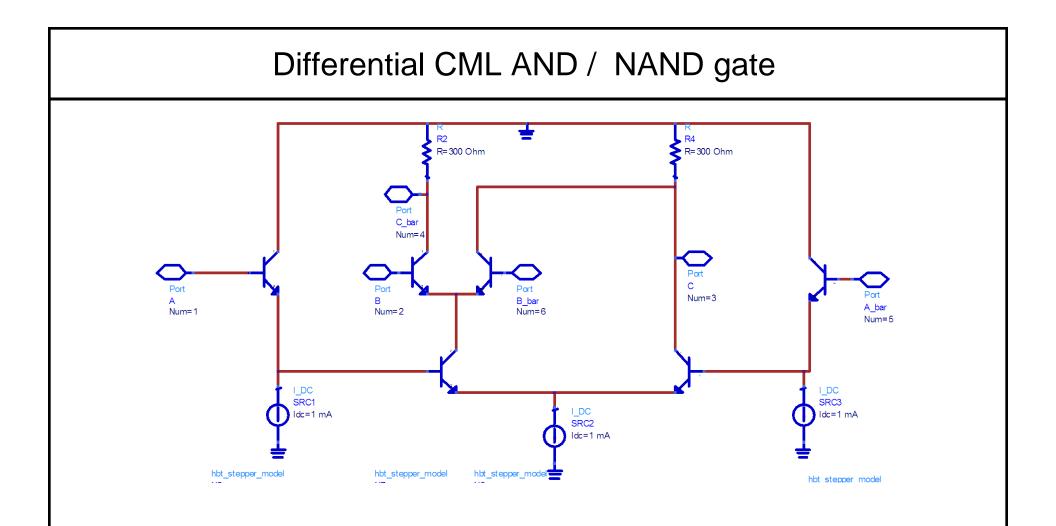

#### Differential CML gate, other attributes

Operates with complementary inputs and outputs Quite low power consumption, as not many pull-down current sources...

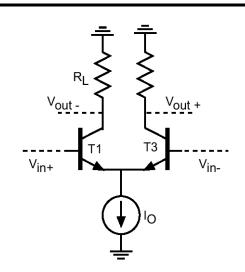

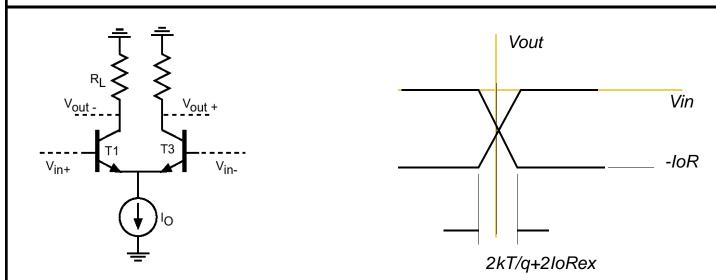

### Differential CML gate, DC operation.

DC output swing is  $\Delta V_{Logic} = I_o R_L$ DC linear input range is  $\Delta V_{in} = 2kT / q + 2I_o R_{ex}$ Transistor operates at  $V_{ce} = V_{be,on}$  when off Transistor operates at  $V_{ce} = V_{be,on} - I_o R_L$  when on Need HBT with LOW  $V_{ce,sat}$

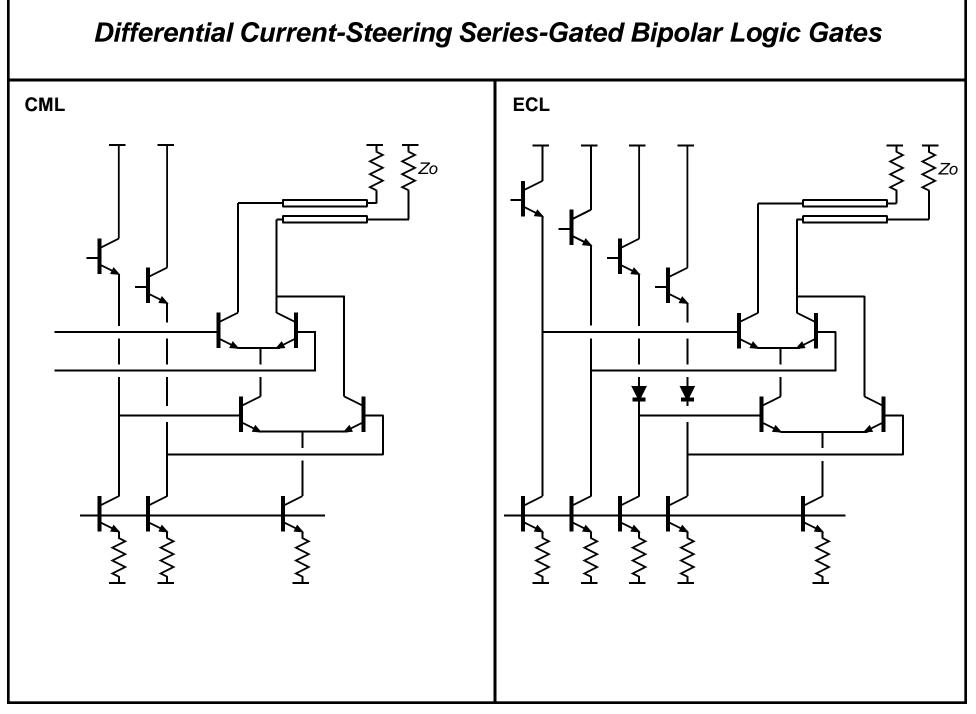

2-input logic gates must be implemented using *series gated current steering*. 3 input gates would require cascading 2-level gates, or 3-level series current steering. 3 level currrent steering is faster, but needs a more negative supply. OR/NOR gate is created by taking complements of both inputs and output.

#### **HEMT Logic Gates**

#### **Direct-coupled FET logic**

Need enhancement-mode and depletion-mode devices slow driving long wires single-ended...threshold problems with low  $\Delta V$

#### Source-Coupled FET logic:

Need a monolithic diode level-shift fairly high power due to source followers Source follows needed for level-shifting

#### FET equivalent of CML :

Need a monolithic diode level-shift need enhancement mode device would be best for fast / low-power

Logic family plays strong role in power Need diodes for SCFL

DCFL needs enhancement mode HEMTs:

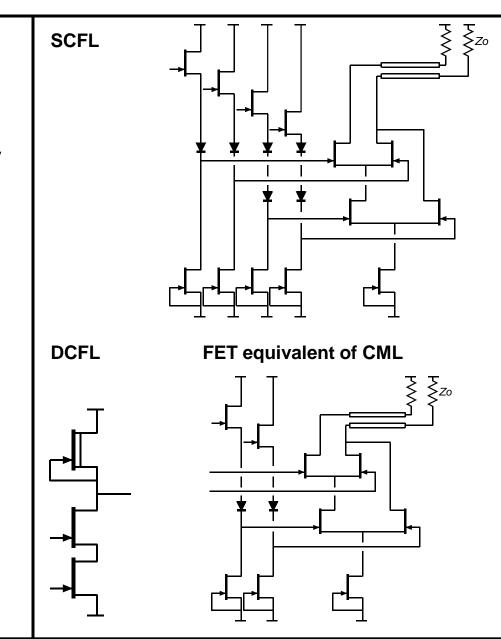

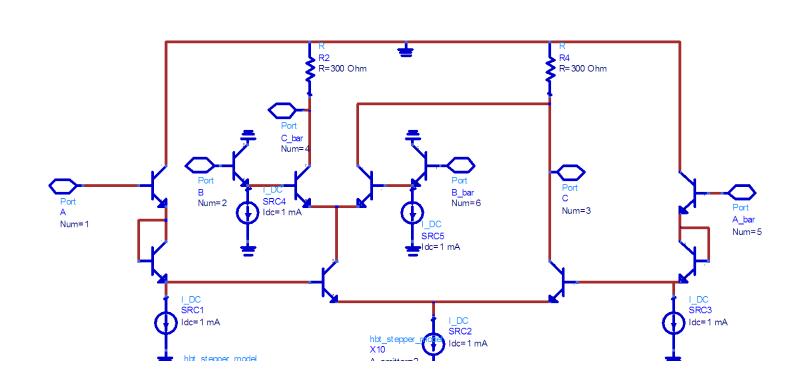

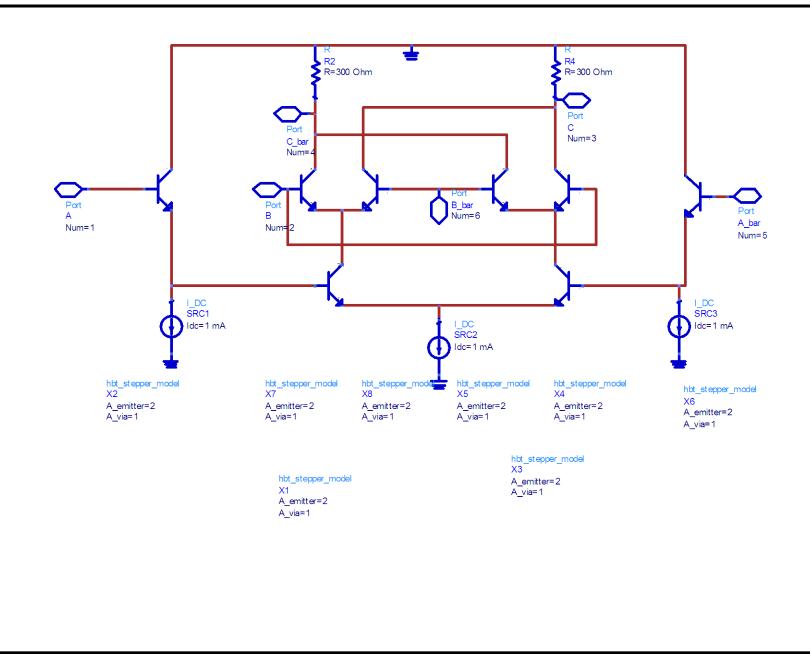

### Differential CML XOR gate

the 6-transistor cell is often referred to as a Gilbert cell (originating with his analog multipliers...). Note that the whole gate requires 3 pull down current sources

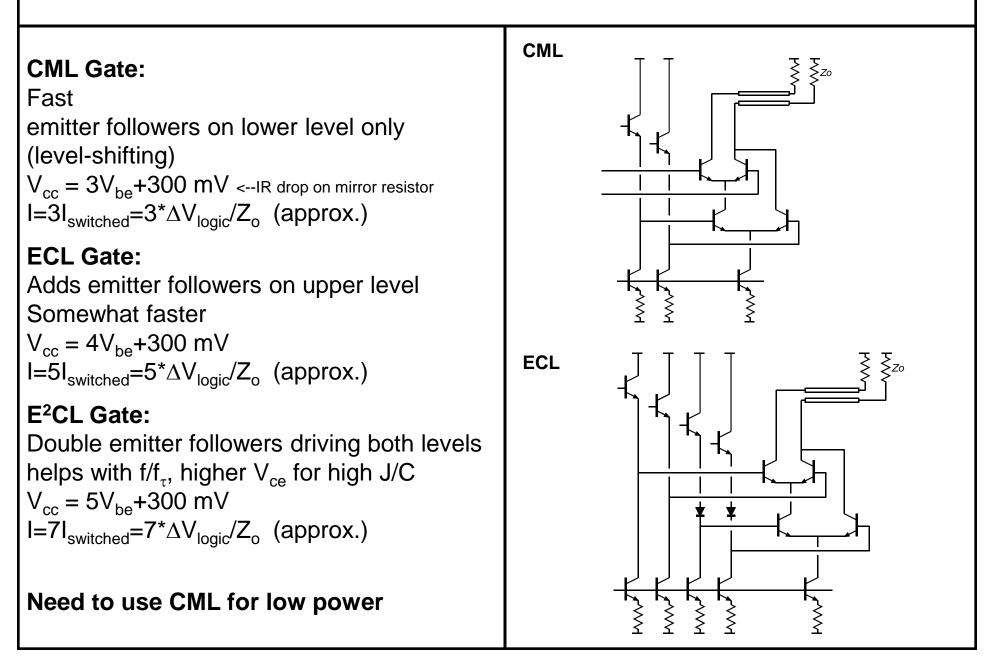

#### Differential ECL buffer / inverter

emitter followers on high "A-level" inputs result in faster gate operation and larger Vce across switching transistors, at expense of considerably higher current consumption. Emitter followers are usually assocaiated with gate inputs, not outputs.

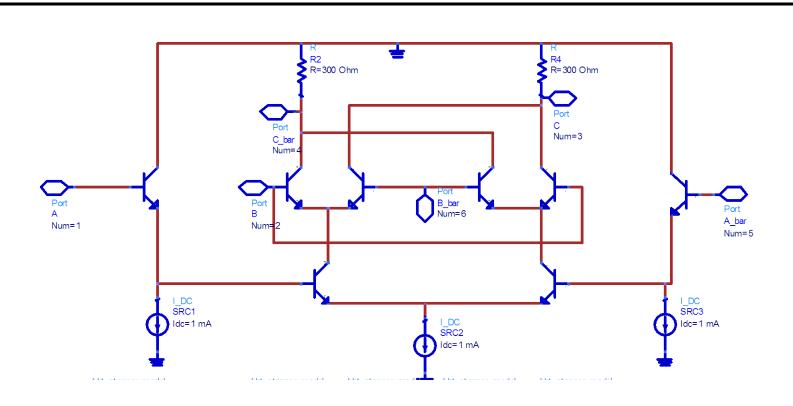

#### Differential ECL AND / NAND gate

Same circuit structure as CML gate, except note added emitter followers on B level inputs and added diode level shifts on A-level inputs

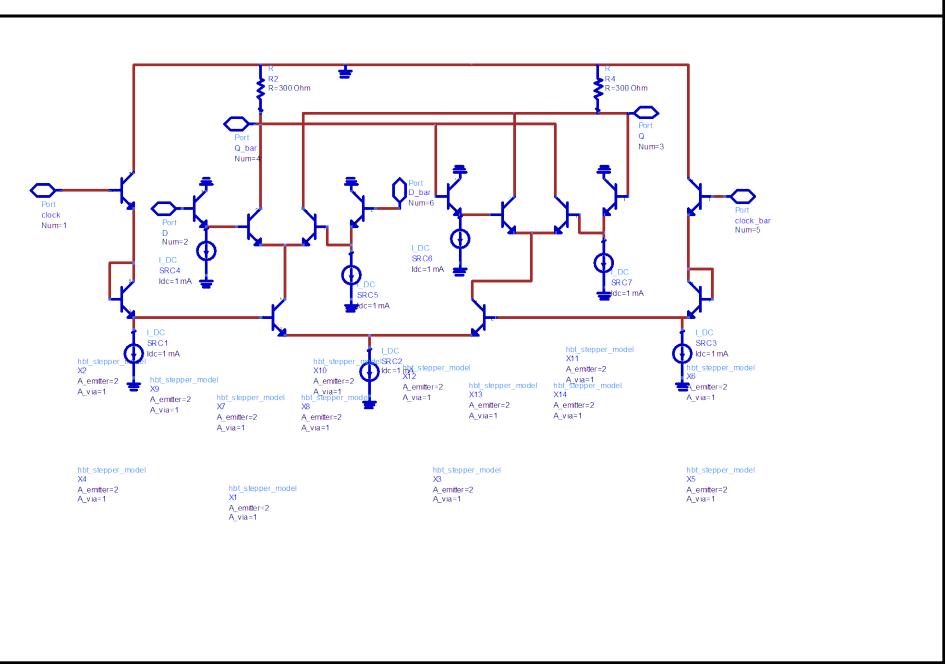

#### Differential ECL XOR gate ÷ R2 R4 R=300 Ohm 돈 R=300 Ohm С Port Num=3 C\_bar Port B\_bar Num=4 Num=6 Port В Num=2 Port А Ŧ A\_bar Num=1 L\_DC SRC4 Num=5 ldc=1mA SR C5 lc=1 mA I\_DC I\_DC SRC3 SRC1 Idc=1 mA I\_DC SRC2 hbt\_stepper X10 noon Idc=1 mA hbt\_stepper\_model X9 A\_emitter=2 A\_via=1 hbt\_stepper hbt\_stepper\_model A\_emitter=2 hbt\_stepper\_model X12 hbt\_stepper\_model X11 \_stepper\_model hbt\_stepper\_model X8 A\_via=1 **X**6 A\_emitter=2 A\_emitter=2 A\_emitter=2 A\_emitter=2 mitter=2 A A emitter=2 A\_via=1 А /ia=1 A\_via=1 A\_via=1 A\_via=1 A\_via=1 hbt\_stepper\_model hbt\_stepper\_model X4 X3 X5 hbt\_stepper\_model A\_emitter=2 A\_emitter=2 A\_emitter=2 X1 A\_via=1 A\_via=1 A\_via=1 . . .

- - - -

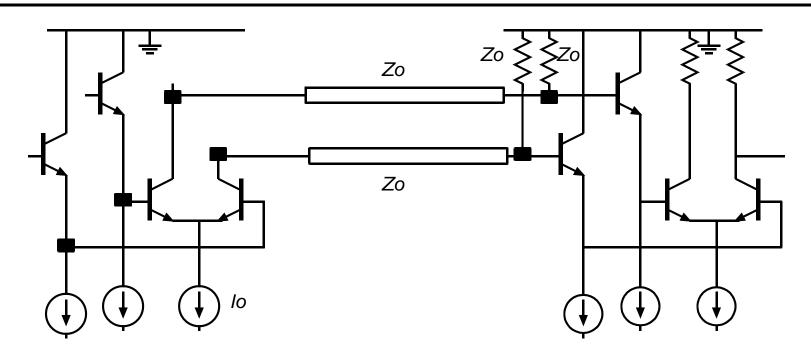

#### Driving Interconnects: EF associated with gate outputs

This can ring quite badly, due to inductive EF output impedance and capacitive CS input impedance.

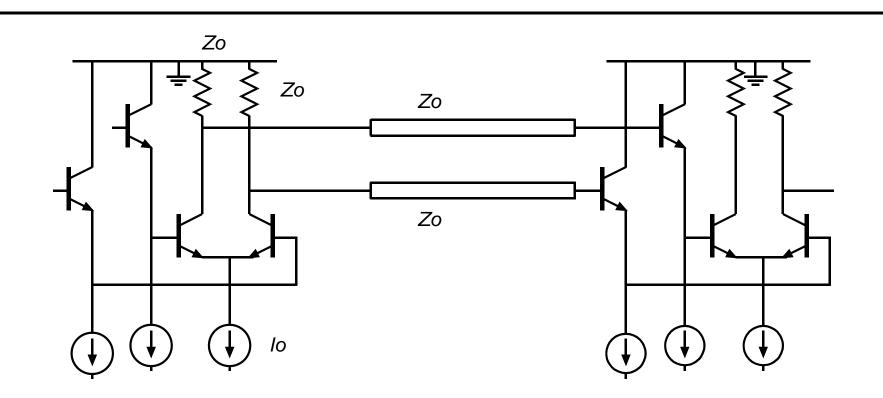

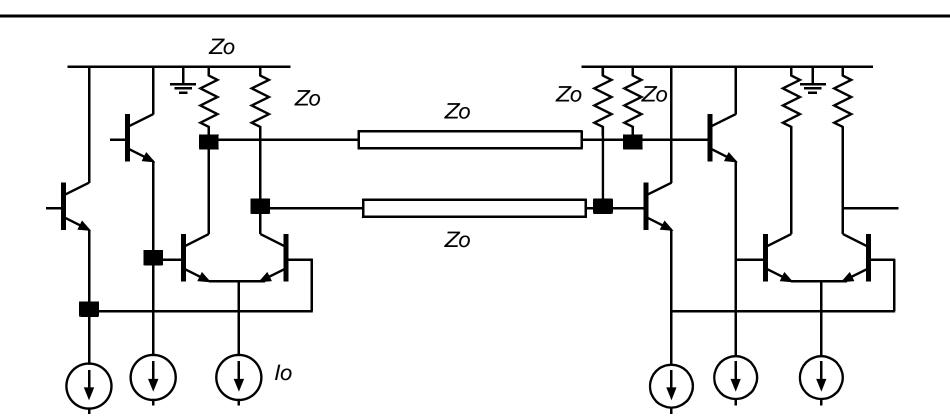

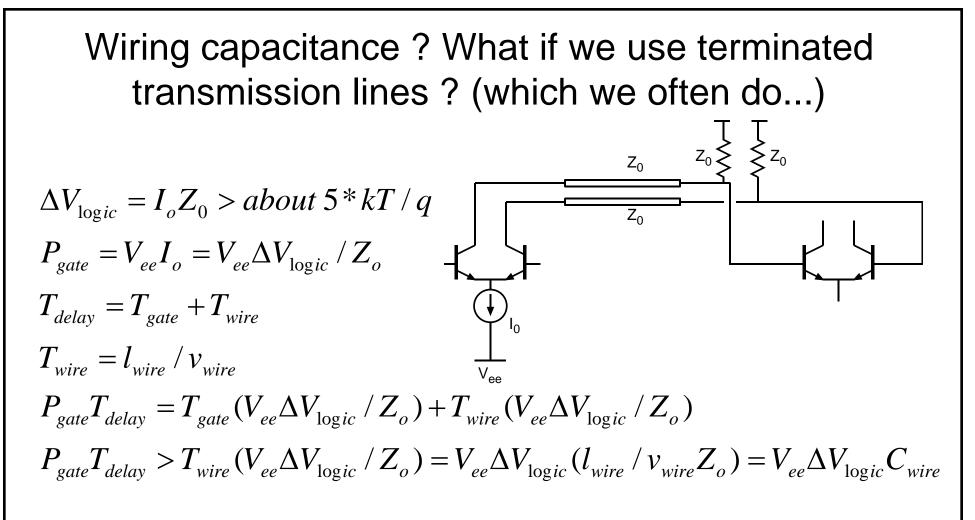

#### Driving Interconnects, and basic power-delay products

sending end termination....matched termination.... line should not (ideally) ring...actually does due to receiving end capacitive load... logic swing is lo\*Zo...with Zo of 100 Ohms typical, this requires 2 mA drive current for 200 mV logic swing in a 100 Ohm environment...

#### Driving Interconnects Receiving end termination

receving end termination....matched termination....

line should not (ideally) ring...actually does due to transistor capacitances ... logic swing is lo\*Zo...with Zo of 100 Ohms typical, this requires 2 mA drive current for 200 mV logic swing in a 100 Ohm environment...

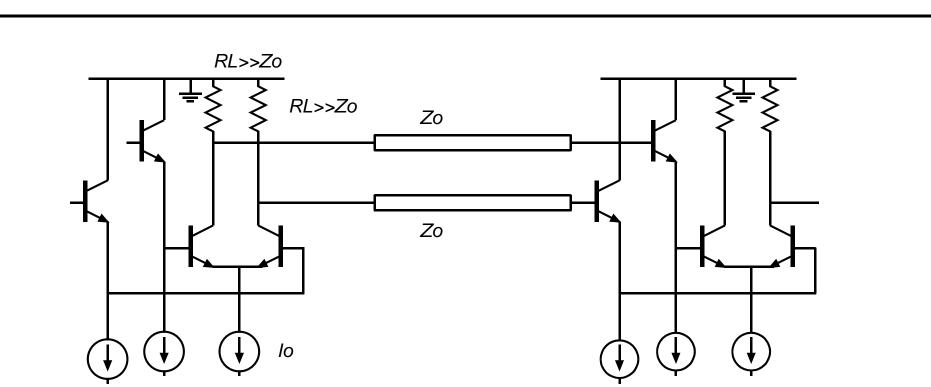

#### **Double line termination**

double matched termination....ringing more strongly suppressed, use where needed....

... logic swing is Io\*Zo/2...with Zo of 100 Ohms typical, this requires 4 mA drive current for 200 mV logic swing in a 100 Ohm environment...

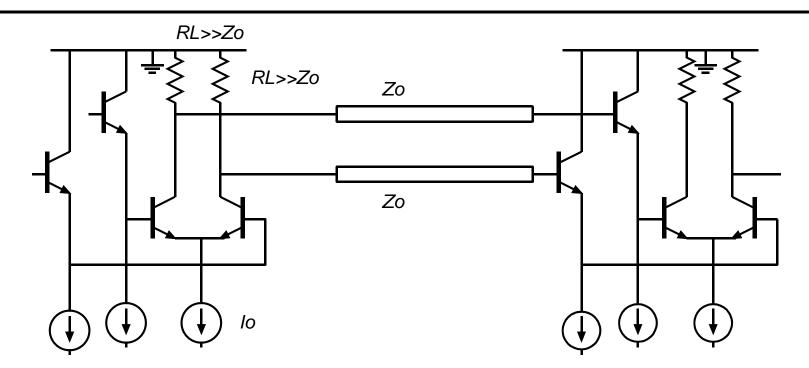

#### unterminated lines

here lines are not terminated. Acceptable only when line delay is short in comparison with risetimes of concern. A short unterminated line will act as a capacitive load; a long unterminated line will ring. More on this in a few slides.

... logic swing is lo\*RL...current consumption greatly reduced (and smaller HBTs used)....

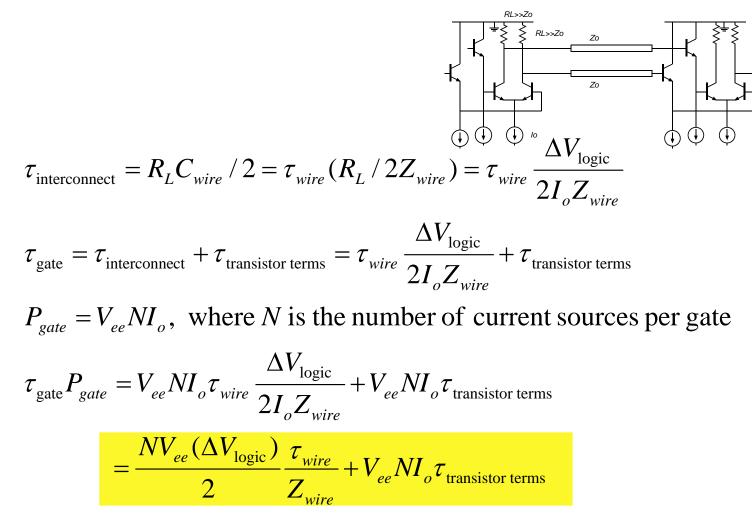

#### unterminated lines: delay due to wiring capacitance

If and only if  $\tau_{wire} \ll T_{rise/fall}$ , can treat as lumped interconnect. If and only if  $R_L \gg Z_{wire}$ , then  $L_{wire} / R_L \ll R_L C_{wire}$  & can ignore wiring inductance Then :

$$C_{wire} = l_{wire} / v_{wire} Z_{wire} = \tau_{wire} / Z_{wire}$$

Charging time constant :

$$\tau_{\text{interconnect}} = R_L C_{\text{wire}} = \tau_{\text{wire}} (R_L / Z_{\text{wire}}) = \tau_{\text{wire}} \frac{(\Delta V_{\text{logic}} / I_o)}{Z_{\text{wire}}}$$

#### Power Consumption in ECL and CML with singly-terminated Lines

# **Power and Power-Delay Products**

Device sized for 100  $\Omega$  load: (300 mV ECL logic swing) 0.25  $\mu$ m x 6  $\mu$ m emitter Jpeak=2 mA/um^2  $\rightarrow$  peak speed at 2 mA

Shorter stripe length device: 0.25 μm x 0.5 μm emitter *peak speed at 250 μA bias*

The smaller device consumes 12:1 less power but cannot use terminated lines. The lines then act as capacitive parasitics, and circuit speed is reduced due to the resuling RLCwire time constant.

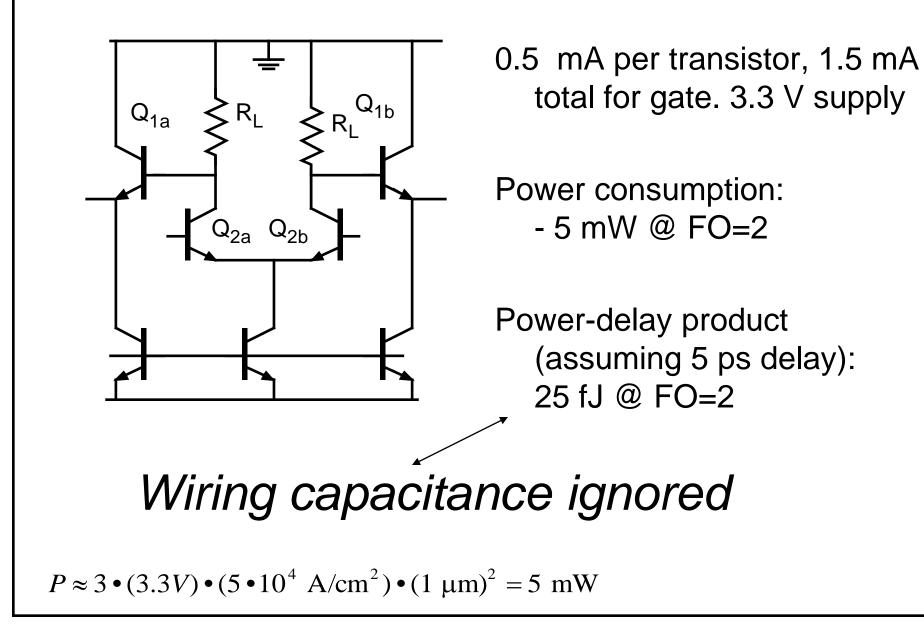

## Power-Delay Product for a "Baseline" Device 1 µm by 1 µm emitter

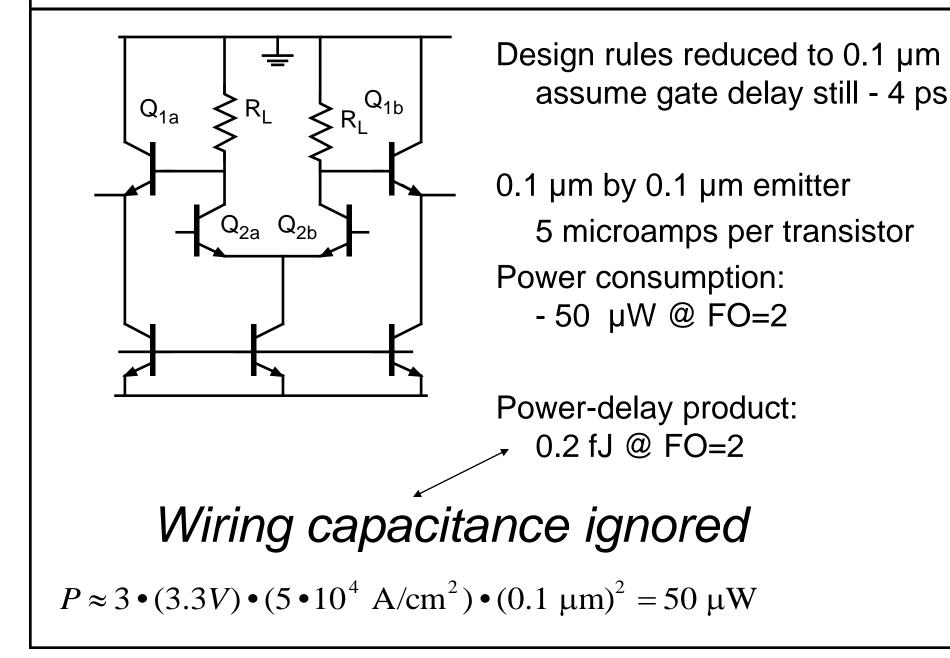

## Power-Delay Product for Scaled Device

#### Low-power gates have large delay from wiring capacitance

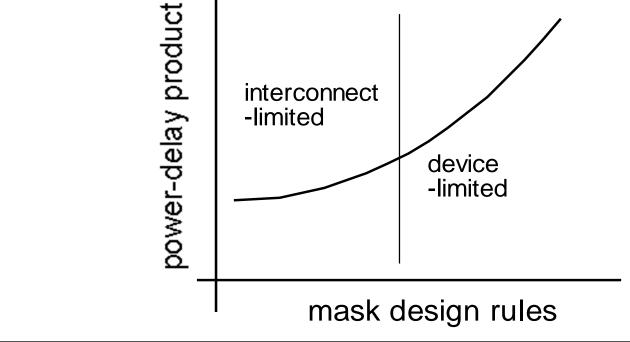

As transistors are scaled, becomes smaller, and power - delay product becomes interconnect - limited

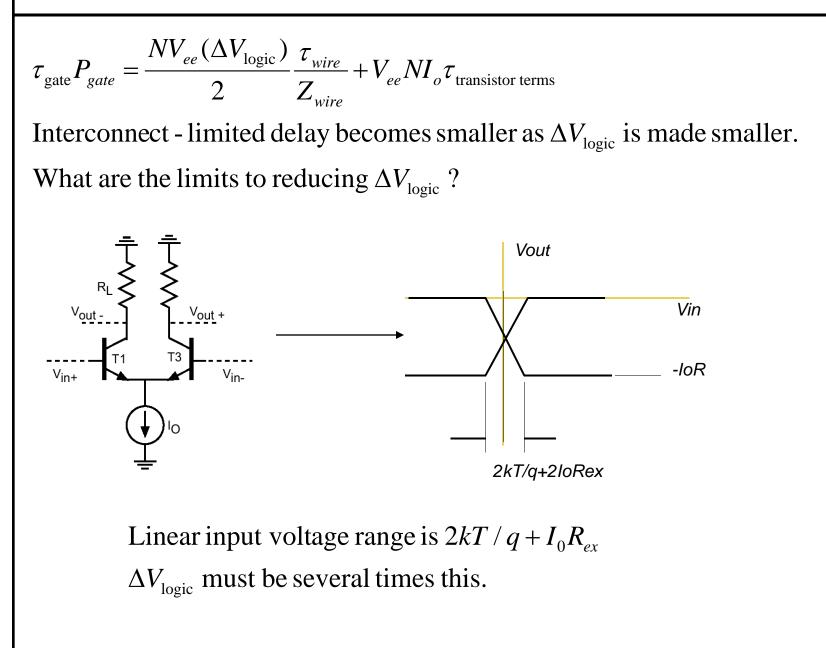

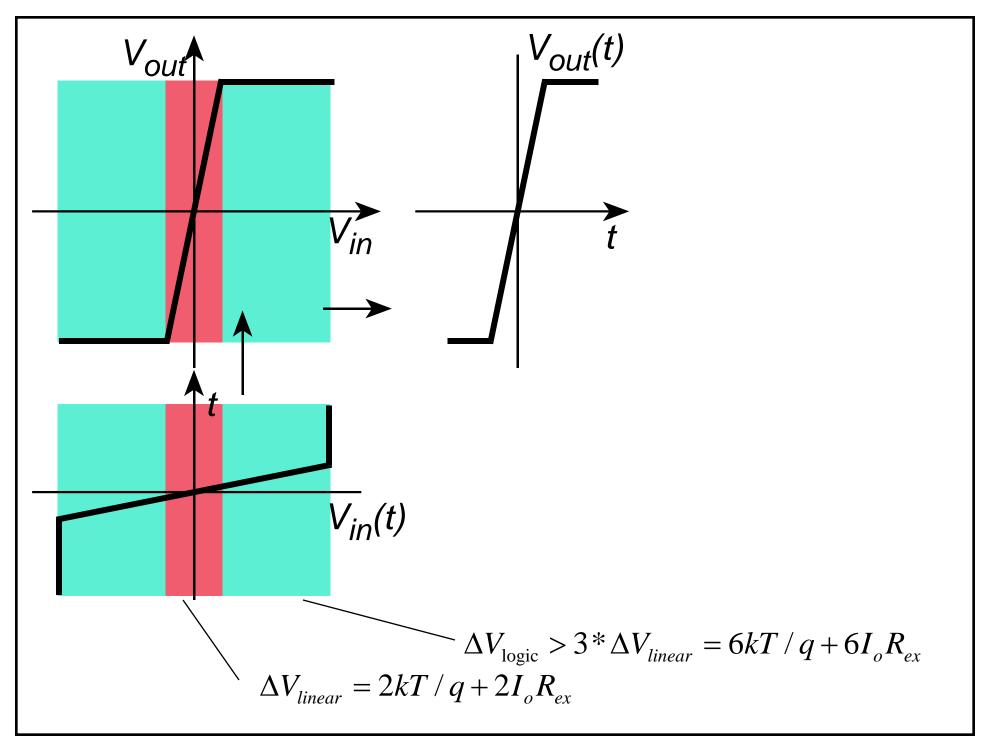

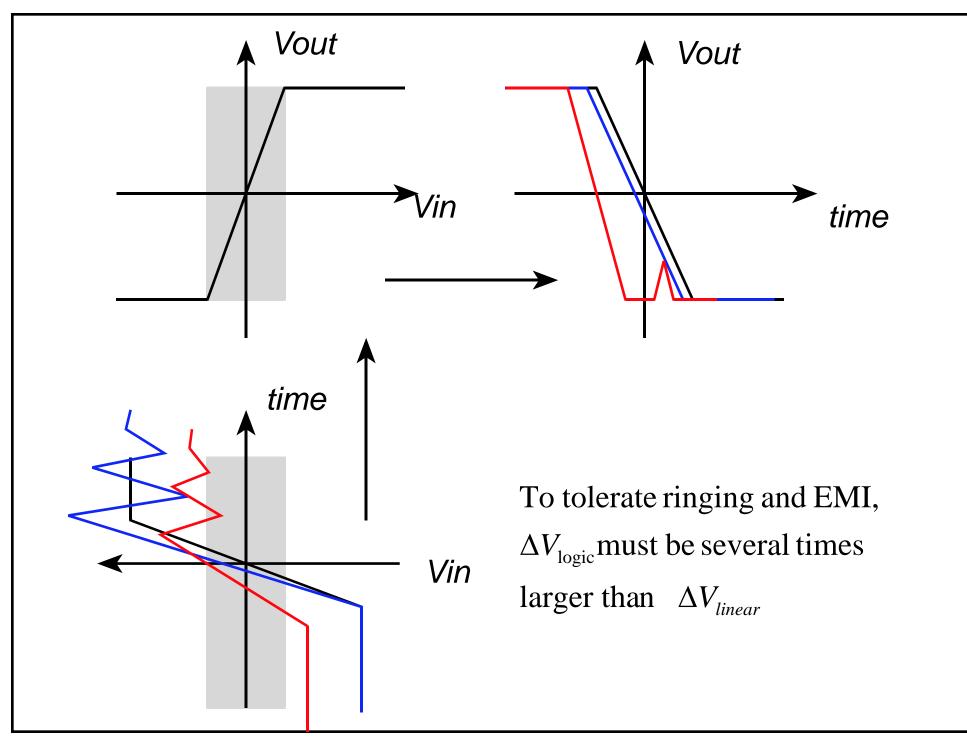

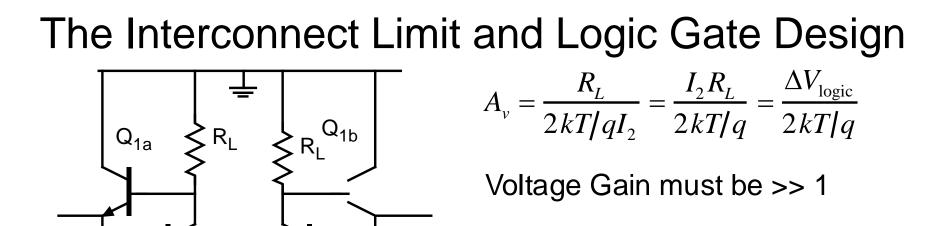

#### Minimum allowable logic voltage swing

## Minimum Logic Voltage Swing

The linear input voltage range of the gate is  $\Delta V_{linear} = 2kT / q + 2I_{o}R_{er}$ We need margin against signal degradation due to signal ringing (interconnects, circuit - level a2) gate - gate interference due to supply or ground coupling This safety margin is called "noise" margin has \*\*absolutely \*\* nothing to do with thermal noise  $\sqrt{4kTR\Delta f}$ should instead be called "EMI + ringing" margin In order to have adequate "noise" margin we need  $\Delta V_{\text{logic}} \sim 3 * \Delta V_{\text{linear}} = 6kT / q + 6I_o R_{ex} \sim 150 \text{ mV} + 6I_o R_{ex}$

## Power-delay product in interconnect limit

$$P_{gate}T_{prop} = (1/2)C_{wire}V_{cc}\Delta V_{logic}$$

bipolar logic (static power)  $P_{gate} / f_{clock} = (1/2)C_{wire}V_{cc}\Delta V_{logic}$

CMOS logic (dynamic power)

$(T_{prop}f_{clock})^{-1} \sim$  number gates between latches

For fast, low-power logic: reduce  $V_{cc}\Delta V_{logic}$

**So:**

$$\Delta V_{\text{logic}} = 10 \bullet (kT/q)$$

But:

$$P_{gate}T_{gate} > (1/2)V_{cc}\Delta V_{logic}C_{wire}$$

$$P_{gate}T_{gate} > (1/2)(1.5 \text{ Volt})(10 \bullet kT/q)C_{wire}$$

(power•delay) is constrained by interconnects

a fast transistor doesn't result in a fast IC

$\mathsf{Q}_{\mathsf{2b}}$

Q<sub>2a</sub>

conclusion: a better circuit design is needed

Similar derivation for CMOS (Meindl, Proc IEEE, 1995)

so, even though "wiring capacitance" is no longer an accurate description,  $CV_{cc}\Delta V_{logic}$  is still an accurate expression for the power-delay limit

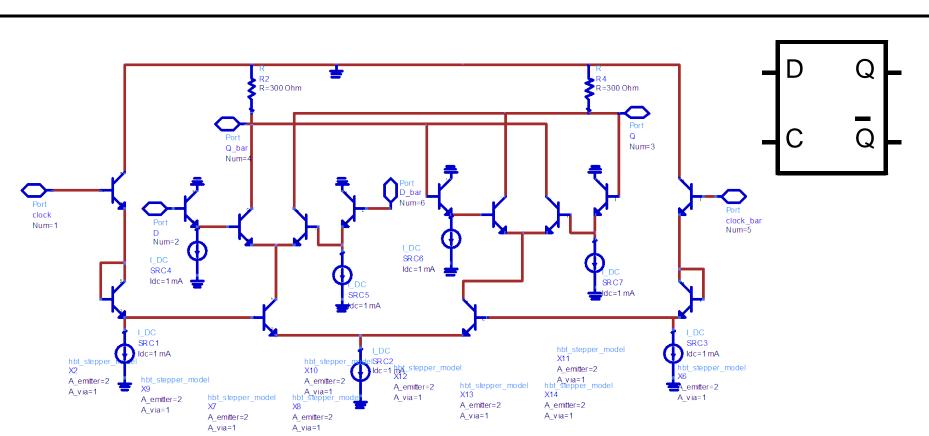

#### ECL Latch

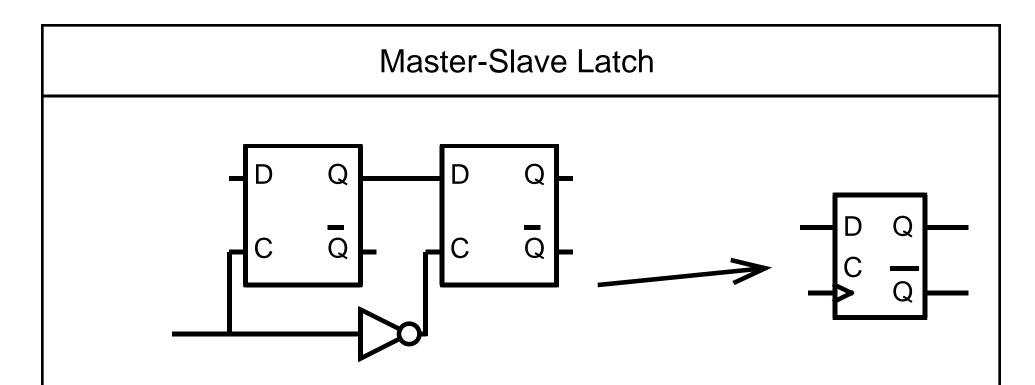

When clock is high, output = input. When clock is low, output = input at just before clock changed from high to low Note the positive feedback pair which holds the output level when clock\_bar is high

Cascading a pair of latches creates a circuit which reads the data input D, and outputs it as the value Q, *Only on a falling edge of clock....output is otherwise held constant*.... MS latch is used as timing control element...output is a version of the input, but sampled only at falling edge of clock

timing control in logic system, prop delays will be function of transititon & critical path. timing errors/fluctuations will accumulate...role of latch is to suppress this, restore timing.

decision element. in ADCs and in communcations receveviers, must decide whether a signal exceeds / does not exceed a critical threshold *at a particular set of points in time defined by a clock signal.*

# ECL M/S Latch connected as 2:1 static frequency divider ÷ ÷ ц р ğ -O data output О -vvv-Tr ൝൷ OCLK Ş Vee

## Fast ECL 2:1 static frequency divider keep-alive bias currents clock, clock Τ -^^-ΛΛ, n inductive load transmission-line bus ক short signal path emitter-follower damping clock clock

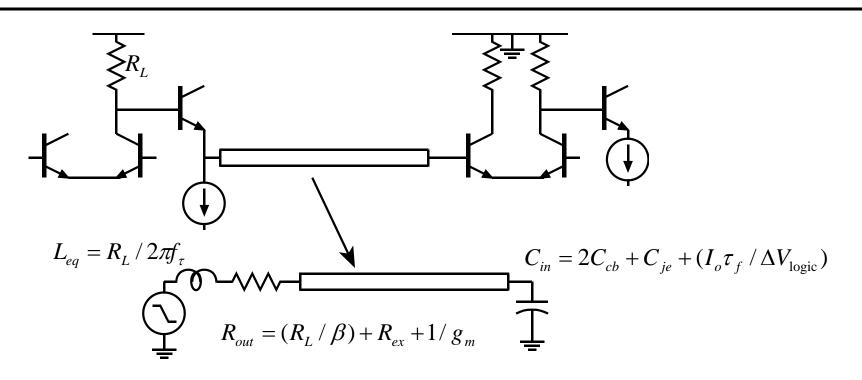

## Logic Propagation delay analysis: start with one-level CML gate

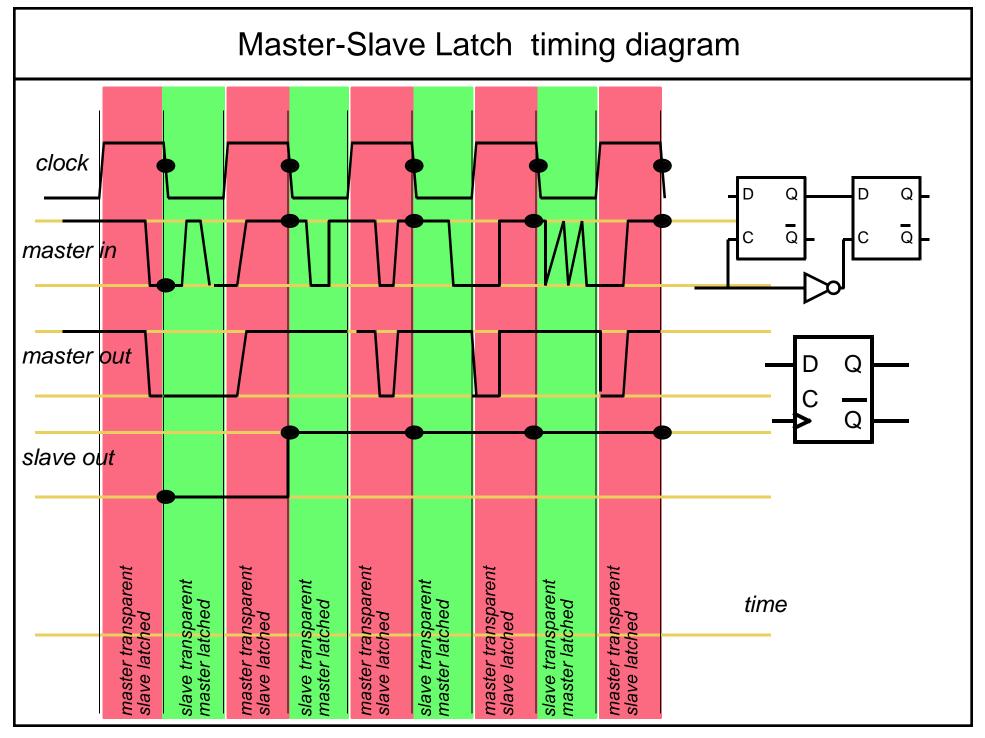

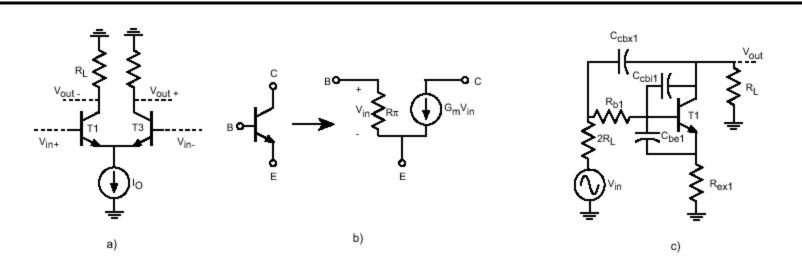

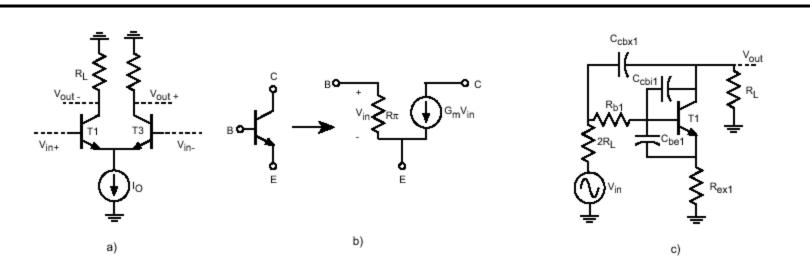

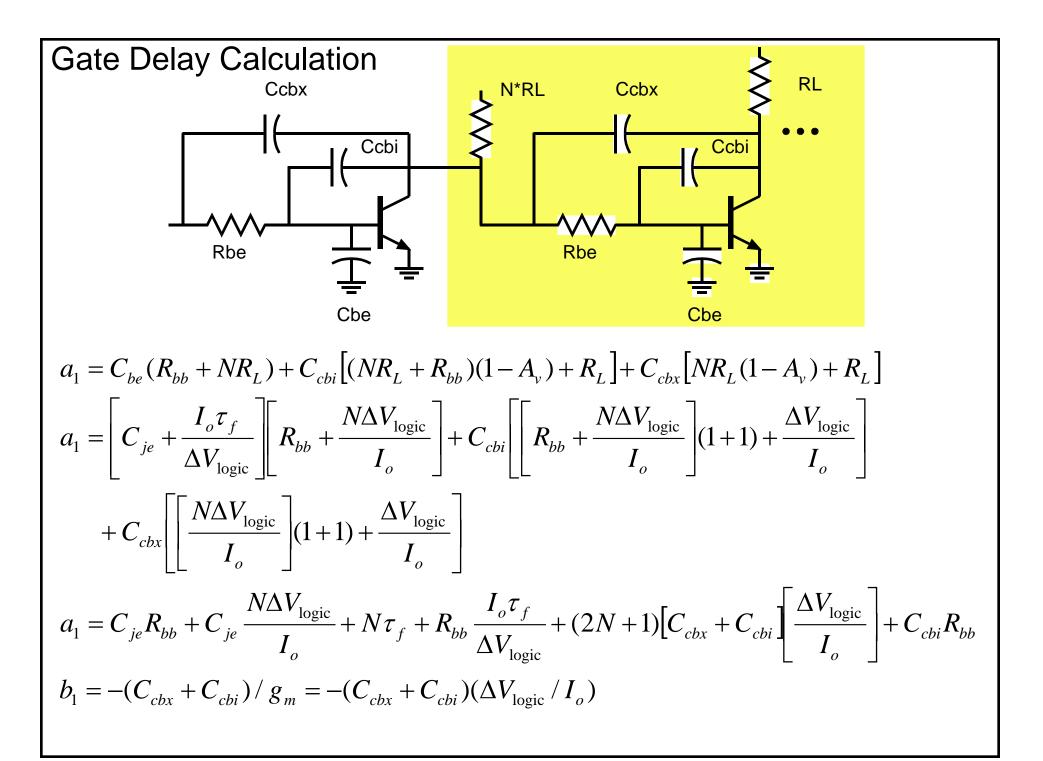

Figure 4.1: a) Basic CML gate. b) HBT without parasitics. c) CML equivalent circuit used for calculating propagation delay.

## First, basic assumptions: 2:1 fan-out, chain of identical gates

## Basic Assumptions for Propagation delay analysis

Figure 4.1: a) Basic CML gate. b) HBT without parasitics. c) CML equivalent circuit used for calculating propagation delay.

Transistor is nonlinear, how do we solve ? Small - signal analysis :  $C_{s.s.} \equiv dQ/dV$ ,  $g_m \equiv dI/dV$  etc. Large - signal analysis :  $C_{s.s.} \equiv \Delta Q/\Delta V$ ,  $g_m \equiv \Delta I/\Delta V$  etc. where  $\Delta V$  is the logic swing. Basic Assumptions for Propagation delay analysis

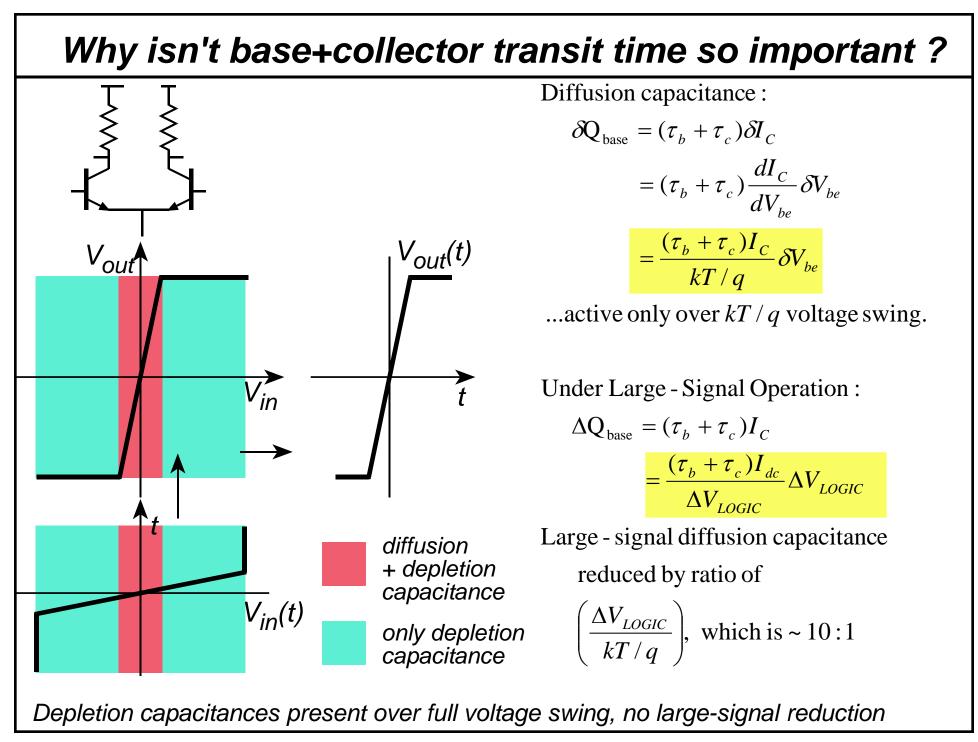

Large-signal analysis:  $C_{s,s} \equiv \Delta Q / \Delta V, g_m \equiv \Delta I / \Delta V$  etc. This implies :  $g_m = \Delta I / \Delta V = I_o / I_o R_L = 1 / R_L << qI_o / kT$  $C_{be.diffusion} = \Delta Q / \Delta V = I_o \tau_f / \Delta V = \tau_f / R_L \ll I_o \tau_f / (kT / q) = g_m \tau_f$  $A_{v} = \Delta V_{out} / \Delta V_{in} = -1$  $C_{je,l\,\mathrm{arg}\,e-signal} = \Delta Q / \Delta V = \left(\int_{V_{be,on}}^{V_{be,on}} C_{je}(v) dV\right) / \Delta V = C_{je,eff}$  $C_{cb,l\,arg\,e-signal} = \Delta Q / \Delta V = (C_{cb} \Delta V) / \Delta V = C_{cb}$ Note that large signal operation greatly reduces the effective values of gm and the diffusion capacitance...by roughly a factor of 10. Logic speed is much more controlled by deplection capacitances than it is by HBT base and collector stored charge

Gate Propagation delay analysis

We now solve for gate delay

Method : replace transistors with their \* large - signal \* models Circuit has transfer function of

$\begin{bmatrix} V_{out} \\ V_{in} \end{bmatrix} = \begin{bmatrix} V_{out} \\ V_{in} \end{bmatrix}_{mid-band} \frac{1+b_1s+b_2s^2+\dots}{1+a_1s+a_2s^2+\dots}$

It is elementary math to show that the \* mean delay \* of the transfer function is  $(a_1 - b_1)$ , hence 1/2 the mean delay (delay to the 50% switching points) is  $T_{gate} = (a_1 - b_1)/2$ Find  $a_1$  by the method of time constants Find  $b_1 = \sum C_{be} / g_m - \sum C_{cb} / g_{m,large-signal}$

common-emitter stages

emitter followers

Note that although the methods appear to be quite different, MOTC delay analysis on the linearized (large - signal) circuit, is identical to delay analysis by the charge - control method,

e.g.

$$T_{gate} = \frac{1}{2} \sum \frac{\Delta Q}{\Delta I} = \frac{1}{2} \sum \frac{1}{\Delta I} \int_{V_{low}}^{V_{high}} C(v) dV$$

In both cases it is important to note that 2nd - order effects  $a_2$ in the circuit transfer function are neglected. This means, specifically, that emitter - follower ringing is neglected, which is a serious limitation Taking  $T_{prop} = \tau \ln(2)$  is equivalent to assuming  $(1 - \exp(-t/\tau))$  charging behaviour. To the level of accuracy of the assumptions used, we have instead assumed linear node charging with time, which gives  $T_{prop} = \tau/2$ , e.g. (1/2) the mean delay

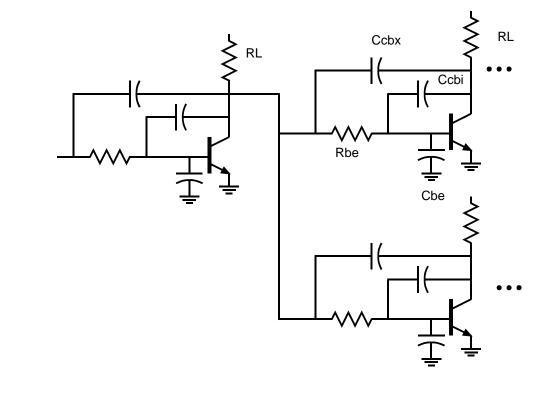

One-level CML Propagation delay analysis: fan-outs

Here we are analyzing a gate chain with a fan-out of 2:1

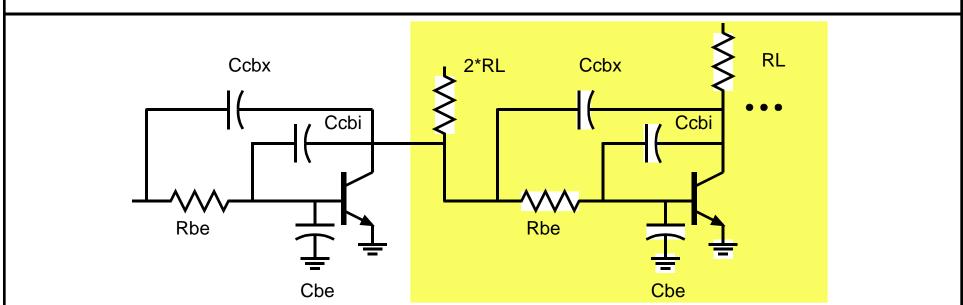

## Simplifying treatment of fan-outs

$R_L$  is replaced by  $2R_L$  by symmetry arguments. In order to count each parasitic capacitance ONCE per gate, we must consider only capacitors in the highlighted area

Gate Delay Calculation: Single-level CML gate at N:1 fanout

$$\begin{split} 2T_{gate} &= C_{je}R_{bb} + C_{cbi}R_{bb} + N\tau_{f} \\ &+ R_{bb}\frac{I_{o}\tau_{f}}{\Delta V_{logic}} \\ &+ (2N+2) \Big[C_{cbx} + C_{cbi} \Bigg[\frac{\Delta V_{logic}}{I_{o}}\Bigg] + C_{je}\frac{N\Delta V_{logic}}{I_{o}} \end{split}$$

Note that the  $C_{cb}(\Delta V_{logic}/I_o)$  and  $C_{je}(\Delta V_{logic}/I_o)$  terms usually dominate. This strongly favors the use of small logic swings and high current density

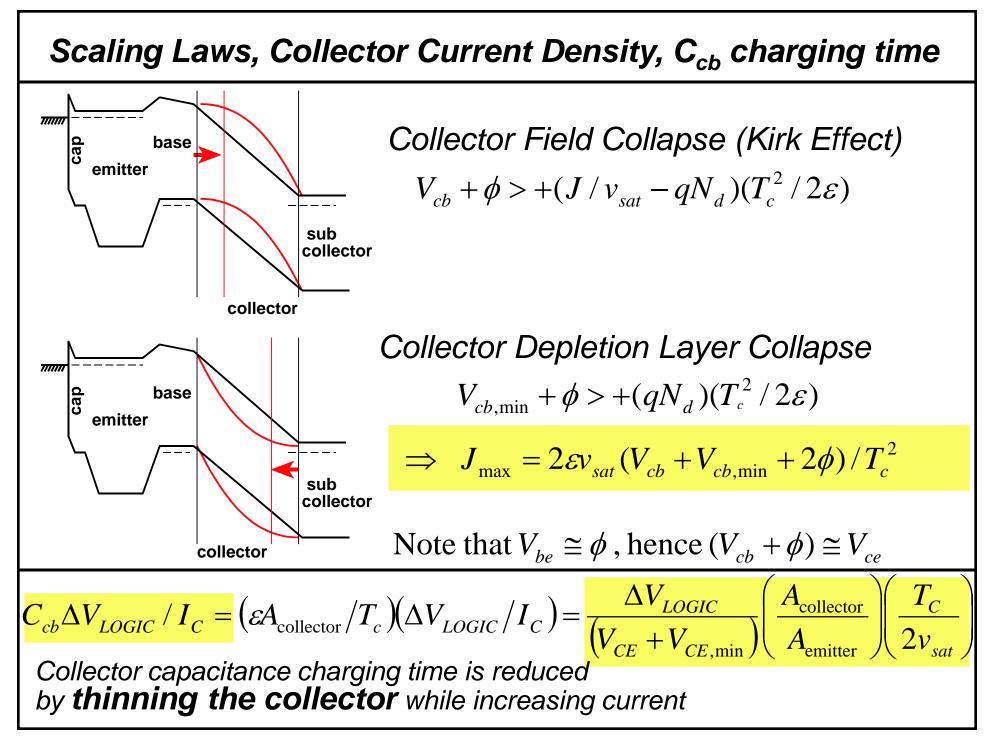

## Effect of Current Density

$$\begin{split} 2T_{gate} &= C_{je}R_{bb} + C_{cbi}R_{bb} + N\tau_{f} \\ &+ R_{bb}\frac{J_{o}A_{e}\tau_{f}}{\Delta V_{\text{logic}}} + (2N+2)\frac{\varepsilon A_{c}}{T_{c}}\left[\frac{\Delta V_{\text{logic}}}{A_{e}J_{o}}\right] + C_{je}\frac{N\Delta V_{\text{logic}}}{A_{e}J_{o}} \\ 2T_{gate} &= C_{je}R_{bb} + C_{cbi}R_{bb} + N\tau_{f} \\ &+ (R_{bb}A_{e})\frac{J_{o}\tau_{f}}{\Delta V_{\text{logic}}} + (2N+2)\frac{A_{c}}{A_{e}}\left[\frac{\varepsilon\Delta V_{\text{logic}}}{T_{c}J_{o}}\right] + \frac{C_{je}}{A_{e}J_{o}}N\Delta V_{\text{logic}} \end{split}$$

Effect of Logic Voltage Swing

$$\begin{aligned} 2T_{gate} &= C_{je}R_{bb} + C_{cbi}R_{bb} + N\tau_f + R_{bb} \left(I_o\tau_f / \Delta V_{logic}\right) \\ &+ (2N+2) [C_{cbx} + C_{cbi}] (\Delta V_{logic} / I_o) + NC_{je} (\Delta V_{logic} / I_o) \end{aligned}$$

Note that the linear input voltage range of the gate is

$$\Delta V_{linear} &= 2kT / q + 2I_o R_{ex}$$

Recall than we need

$$\Delta V_{logic} \sim > 3 * \Delta V_{linear} = 6kT / q + 6I_o R_{ex} \sim 150 \text{ mV} + 6I_o R_{ex}$$

Logic voltage swing should be as small as possible, consistent with this limit...the  $R_{bb} (I_o \tau_f / \Delta V_{logic})$  term usually being nondominant.

Effect of Logic Voltage Swing

$$2T_{gate} = C_{je}R_{bb} + C_{cbi}R_{bb} + N\tau_f + R_{bb}\left(I_o\tau_f/\Delta V_{logic}\right) + (2N+2)\left[C_{cbx} + C_{cbi}\right]\left(\Delta V_{logic}/I_o\right) + NC_{je}\left(\Delta V_{logic}/I_o\right)$$

#### But

$\Delta V_{\text{logic}} \sim 3 * \Delta V_{\text{linear}} = 6kT / q + 6I_o R_{ex} \sim 150 \text{ mV} + 6I_o R_{ex}$ Note that  $C_{cb} \left( \Delta V_{\text{logic}} / I_o \right) = \left( \varepsilon / T_c \right) \left( A_c / A_e \right) \left( \Delta V_{\text{logic}} / J_e \right)$ Note that  $I_0 R_{ex} = J_e / \left( R_{ex} / A_e \right)$

If we push up current density, we do reduce Ccb charging time, but we must reduce the emitter resistance per unit area. Otherwise, the voltage swing must increase, and no benefit is obtained

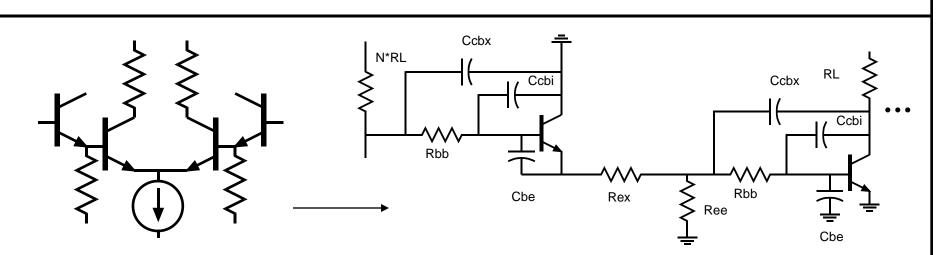

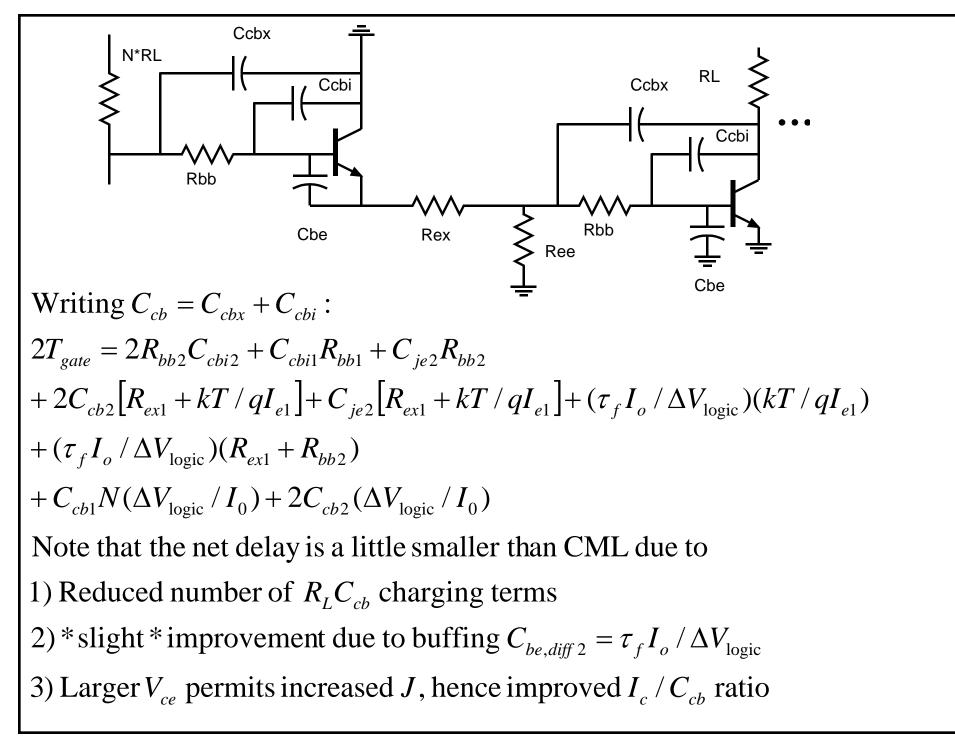

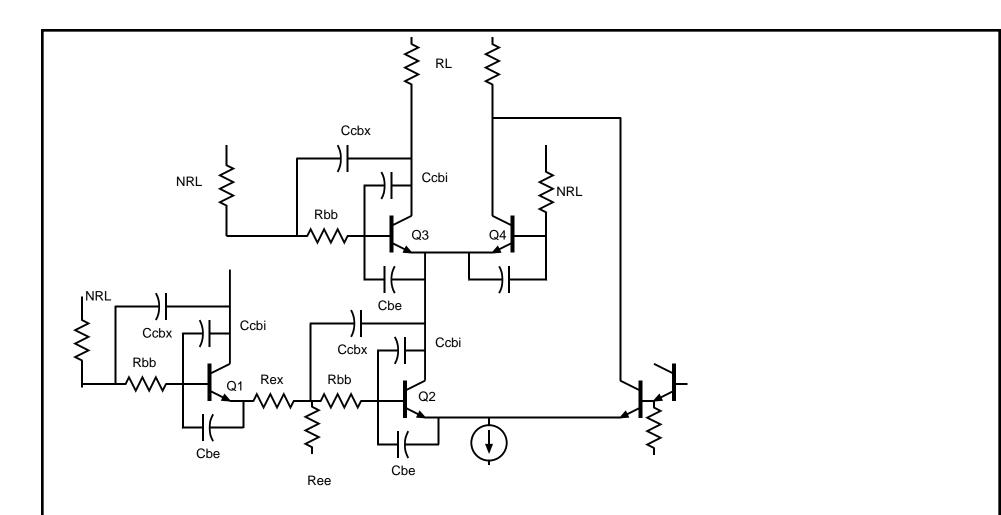

#### ECL Propagation delay: upper-level circuit

again assume a fan-out of N:1 Simplify by assuming beta>>1, Ree>>Re.

## ECL Propagation delay: upper-level circuit

Next key point:

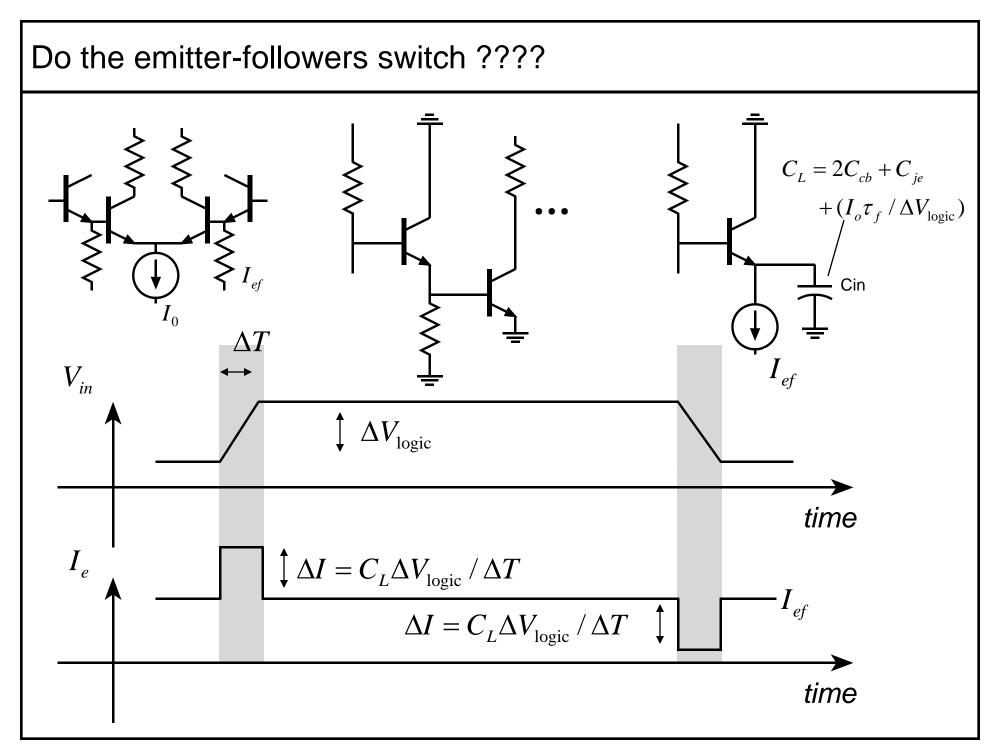

Depending upon the details of the IC design, the emitterfollowers may or may not switch.

For now, let us assuem they do not.

We consequently use small-signal quantities

for the EFs, and large-signal quantities for the CS transistors.

$$\begin{split} & \bigvee_{\text{Res}} \mathbb{C}_{\text{Cbb}} \xrightarrow{\text{Re}}_{\text{Res}} \mathbb{C}_{\text{Cb}} \xrightarrow{\text{Re}}_{\text{Reb}} \mathbb{C}_{\text{Cb}} \xrightarrow{\text{RL}}_{\text{Cb}} \cdots \\ & = a_1 \approx C_{cbx1} NR_L + C_{cbi1} (NR_L + R_{bb}) + (C_{je1} + \tau_f qI_{e1} / kT) (kT / qI_{e1}) \\ & + C_{cbx2} \Big[ (R_{ex1} + kT / qI_{e1}) (1+1) + \Delta V_{\log ic} / I_0 \Big] \\ & + C_{cbi2} \Big[ (R_{ex1} + kT / qI_{e1} + R_{bb2}) (1+1) + \Delta V_{\log ic} / I_0 \Big] \\ & + \Big[ C_{je2} + (\tau_f I_o / \Delta V_{\log ic}) \Big] R_{ex1} + kT / qI_{e1} + R_{bb2} \Big] \\ b_1 &= (C_{je1} + \tau_f qI_{e1} / kT) (kT / qI_{e1}) - (C_{cbx2} + C_{cbi2}) (\Delta V_{\log ic} / I_0) \\ & 2T_{gate} &= a_1 - b_1 = C_{cbx1} NR_L + C_{cbi1} (NR_L + R_{bb}) + (C_{cbx2} + C_{cbi2}) (\Delta V_{\log ic} / I_0) \\ & + C_{cbx2} \Big[ 2(R_{ex1} + kT / qI_{e1}) + \Delta V_{\log ic} / I_0 \Big] \\ & + C_{cbi2} \Big[ 2(R_{ex1} + kT / qI_{e1} + R_{bb2}) + \Delta V_{\log ic} / I_0 \Big] \\ & + \Big[ C_{je2} + (\tau_f I_o / \Delta V_{\log ic}) \Big] R_{ex1} + kT / qI_{e1} + R_{bb2} \Big] \end{split}$$

There are 2 dangers. First, on a rising pulse, the peak EF current is  $I_{ef,peak} = I_{ef} + \Delta I = I_{ef} + C_L \Delta V_{logic} / \Delta T$

We must ensure that this peak current is below Kirk - effect limits.

Second, on a falling pulse, the minimum EF current is zero :

$$I_{ef,\min} = 0 = I_{ef} - \Delta I = I_{ef} - C_L \Delta V_{logic} / \Delta T$$

From which

$$\Delta T_{\rm min} = C_L \Delta V_{\rm logic} \, / \, I_{\it ef}$$

This is slew - rate - limited discharging of  $C_L$ .

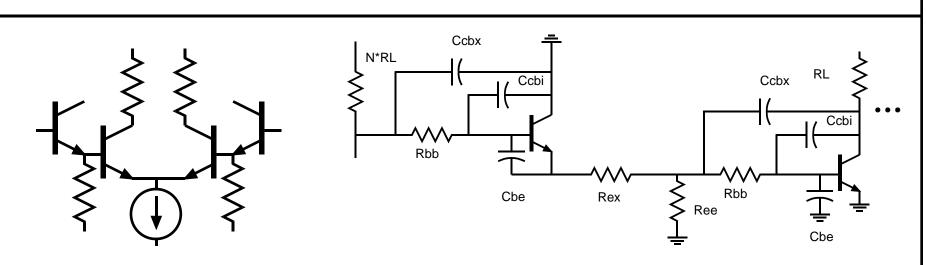

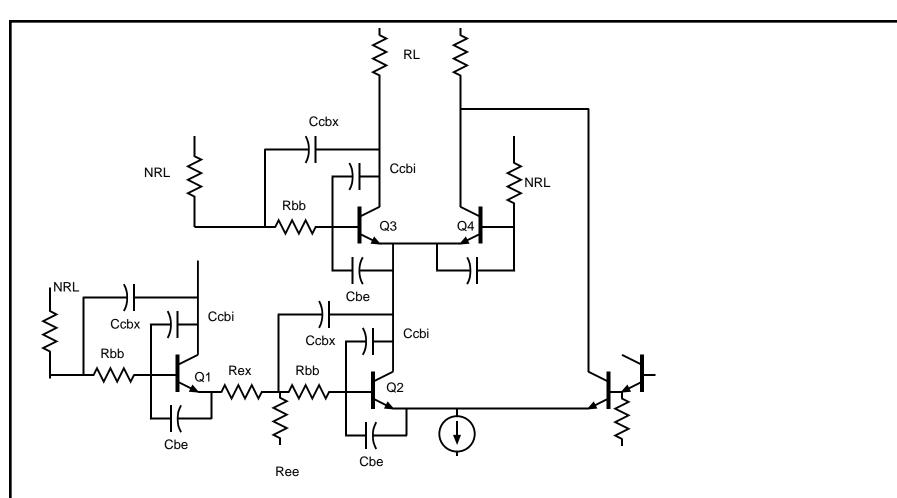

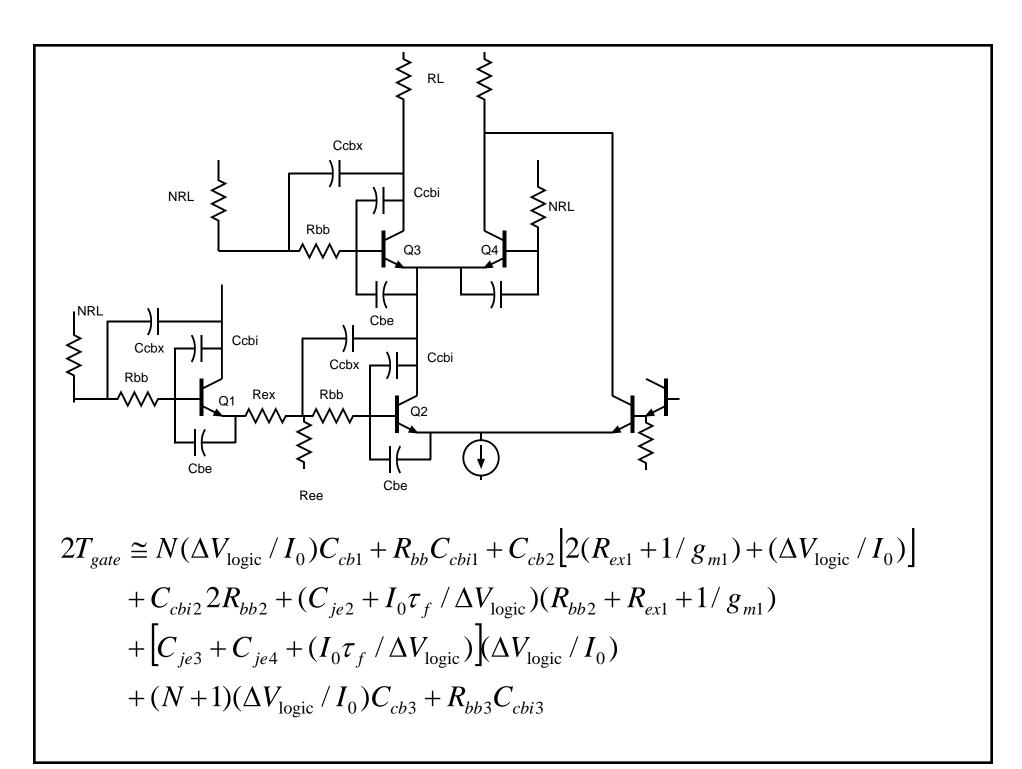

## CML Propagation delay: two-level circuit

The logic voltage swing on the collector of Q2 is also \* approximately \*  $\Delta V_{logic}$ . Justification of this is a long and somewhat messy discussion. Note that on the B level switching path that Q1 is an EF, Q2 is CE, and Q3 is CB. If the base of Q3 is high and Q4 is low, then Q4 remains off and simply loads the collector of Q3 in  $C_{je4}$

Also simplify the answer for clarity by assiming that  $\beta >> 1$ , & that the EF voltage gain is very close to 1. Note that Q3 operates in CB mode... please refer back to earlier notes to review  $a_1$  terms for CB stages.

## ECL Propagation delay: two-level circuit

| Logic Speed    |          |           |           |                       |  |  |  |  |  |

|----------------|----------|-----------|-----------|-----------------------|--|--|--|--|--|

|                |          |           |           |                       |  |  |  |  |  |

|                | $c_{je}$ | $c_{cbx}$ | $c_{cbi}$ | $\tau_f J/\Delta V_L$ |  |  |  |  |  |

| $\Delta V_L/J$ | 1        | 6         | 6         | 1                     |  |  |  |  |  |

| kT/qJ          | 0.5      | 1         | 1         | 0.5                   |  |  |  |  |  |

| $ ho_e$        | -0.25    | 0.5       | 0.5       | 0.5                   |  |  |  |  |  |

| $r_{bb}$       | 0.5      | 0         | 1         | 0.5                   |  |  |  |  |  |

Approximate delay coefficients  $a_{ij}$  for an ECL master - slave flip - flop, found by hand analysis. Gate delay is of the form  $T_{gate} = 1/2 f_{clock,max} = \sum a_{ij} r_i c_j$ , where  $f_{clock}$  is the maximum clock frequency. The minimum logic voltage swing is  $\Delta V_{LOGIC} > 6(kT/q + J\rho_{ex})$

Caveat: ignores interconnect capacitance and delay, which is very significant

# Logic Speed: definition of terms

- $c_{je}$ : emitter base depletion capacitance per unit emitter area

- $c_{cbi}$ : intrinsic collector base capacitance per unit emitter area

- $c_{cbx}$ : extrinsic collector base capacitance per unit emitter area

- $\tau_f$ : sum of base and collector transit times

- J: emitter current per unit emitter area

- $\Delta V_{LOGIC}$ : logic voltage swing

- $r_{bb}$ : base resistance times emitter area (e.g. "per area"  $R_{bb}$ )

- $\rho_{ex}$ : emitter resistance times emitter area (e.g. "per area"  $R_{ex}$ )

# What HBT parameters determine logic speed ?

|              | Cje   | Ccbx | Ccbi  | ( $\tau$ b+ $\tau$ c) ( $I/\Delta$ V) | total  |

|--------------|-------|------|-------|---------------------------------------|--------|

| $\Delta V/I$ | 33.5% | 6.7% | 27.8% |                                       | 68.4%  |

| $\Delta V/I$ |       |      |       | 12.3%                                 | 12.3%  |

| (kT/q) I     | 1.4%  | 0.1% | 0.4%  | 0.5%                                  | 2.5%   |

| Rex          | -1.3% | 0.1% | 0.3%  | 0.9%                                  | 0.1%   |

| Rbb          | 10.2% |      | 2.8%  | 3.7%                                  | 16.7%  |

| total        | 43.8% | 6.8% | 31.3% | 17.5%                                 | 100.0% |

|              |       | 3    | 8%    |                                       |        |

Sorting Delays by capacitances :

44% charging  $C_{je}$ , 38% charging  $C_{cb}$ , only 18% charging  $C_{diff}$  (e.g.  $\tau_b + \tau_c$ )

Sorting Delays by resistances and transit times :

68% from  $\Delta V_{\text{logic}} / I_c$ , 12% from  $(\tau_b + \tau_c)$ , 17% from  $R_{bb}$

$$R_{ex}$$

has very strong indirect effect, as  $\Delta V_{logic} > 6 \bullet (kT / q + I_C R_{ex})$

Caveats:

assumes a specific UCSB InP HBT (0.7 um emitter, 1.2 um collector 2kÅ thick, 400 Å base, 1.5E5 A/cm^2) ignores interconnect capacitance and delay, which is very significant