# Schottky-Collector Heterojunction Bipolar Transistors: Device Scaling Laws for $f_{max}$ beyond 500 GHz

U. Bhattacharya, M. J. Mondry, G. Hurtz, I. Tan

R. Pullela, M. Reddy, J. Guthrie,

M. J. W. Rodwell, and J. E. Bowers

Department of Electrical and Computer Engineering

University of California, Santa Barbara, CA 93106

805-893-8044, 805-893-3262 FAX

#### Introduction

Heterojunction bipolar transistors (HBTs) have high transconductance and extremely reproducible DC parameters. These attributes make HBTs the device of choice for high-speed precision analog and mixed analog-digital circuits. HBT cutoff frequencies are however considerably below that of high-electron-mobility field-effect-transistors (HEMTs).

Scaling laws are central to high-frequency semi-conductor device design. As the semiconductor layer thicknesses and Schottky contact widths of HEMTs and Schottky diodes are decreased, the device bandwidths increase. It is remarkable that power-gain cutoff frequencies  $f_{max}$  of normal HBTs do not significantly increase when the emitter dimensions are reduced below  $\sim 2~\mu{\rm m}$ . Consequently, HBTs are not normally fabricated with deep submicron dimensions.

Here we propose the Schottky-collector heterojunction bipolar transistor (SCHBT), a modified HBT whose scaling properties should result in increased cutoff frequencies. The SCHBT is derived from our prior work on Schottky-collector resonant-tunnel-diodes (SRTDs) [1, 2, 3]. The SCHBT, like the SRTD, should obtain a large reduction in a resistance-capacitance time constant, hence a large increase in  $f_{max}$ , by extreme scaling through the use of a submicron Schottky collector contact.

$f_{max}$  of the SCHBT increases as  $\lambda^{-1/2}$ , where  $\lambda$  is the process minimum feature size. An SCHBT processed at  $\lambda=0.2~\mu{\rm m}$  should attain  $f_{max}\sim600$  GHz. While fabrication of a such a device will require development of sophisticated dry etching and passivation technologies, it will be diffcult to obtain similar cutoff frequencies with the conventional HBT.

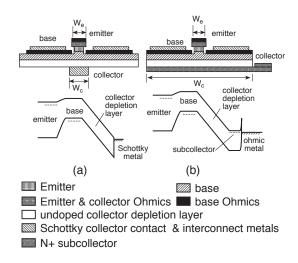

Figure 1: Layer structures and band diagrams comparing an SCHBT (a) to an HBT (b).

## Scaling Laws

With the SCHBT (fig. 1), two features should result in increased bandwidth during scaling. First, an epitaxial transfer process step inverts the transistor epitaxial layers during processing, allowing fabrication of aligned emitter and collector contacts with small widths  $W_e$  and  $W_c$ . Second, use of a Schottky collector contact in preference to a normal  $N^+$  semiconductor collector will permit scaling the collector contact to deep submicron dimensions. This scaling reduces  $r_{bb}C_{cb}$ , increasing  $f_{max}$ .

While the current-gain cutoff frequency  $f_{\tau} = 1/2\pi(\tau_b + \tau_c)$  at high current densities depends only on the base and collector transit times  $\tau_b \simeq T_b^2/2D_n + T_b/v_{sat}$  and  $\tau_c = T_c/2v_{sat}$ ,  $f_{max} \simeq \sqrt{f_{\tau}/8\pi r_{bb}C_{cb}}$  involves the base resistance  $r_{bb}$  and the collector- base capacitance  $C_{cb}$ .  $T_b$  is the base thickness,  $T_c$  the collector depletion layer thickness, and  $v_{sat}$  the electron velocity. Regardless of the value of  $f_{\tau}$ , transistors cannot provide power gain

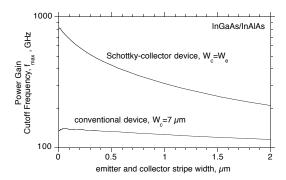

Figure 2: Calculated  $f_{max}$  of HBTs and SCHBTs versus emitter width  $W_e$  for InGaAs/InAlAs devices with  $T_c = 2000$  å,  $T_b = 800$  å, and material parameters taken from Hafizi et. al. [5]

above  $f_{max}$ .

In the normal HBT (fig. 1a) the collector junction width  $W_c$  is much larger than the emitter stripe width  $W_e$ , increasing  $C_{cb}$  and decreasing  $f_{max}$ . The collector-base capacitance  $C_{cb} = \epsilon W_c/T_c$  is proportional to the collector width  $W_c$  but is independent of the emitter width. The base resistance,  $r_{bb} = \sqrt{\rho_{bc}\rho_{bs}}/2l + W_e\rho_{bs}/12l$  is dominated by the base ohmic contact resistance term  $(\sqrt{\rho_{bc}\rho_{bs}}/2l)$ and is consequently independent of the emitter width for  $W_e < \sim 2\mu \text{m}$ .  $\rho_{bc}$  is the specific base contact resistivity, l the emitter stripe length,  $W_e$ the emitter width,  $\rho_{bs} = \rho_b/T_b$  the base sheet resistivity, and  $\rho_b$  the base bulk resistivity. Since  $f_{\tau}$ and  $r_{bb}C_{cb}$  are independent of the emitter width, so is  $f_{max}$ . For emitter stripe widths below  $\sim 2 \mu \text{m}$ ,  $f_{max}$  does not improve.

In contrast, SCHBTs (fig.1b) have  $W_c = W_e$ . This results in a smaller  $C_{cb}$  and a significant increase in  $f_{max}$ . Inclusive of fringing fields,  $C_{cb} \simeq \epsilon l(W_c + T_c)/T_c$ .  $C_{cb}$ , proportional to the collector width, is proportional to the emitter width since the widths are now equal. The base resistance is still independent of  $W_e$ , and hence  $r_{bb}C_{cb} \propto W_c + T_c$ . Consequently, with  $T_c$  and  $T_b$  fixed,  $f_{max} \propto (W_c + T_c)^{-1/2}$ . Bandwidth increases as the inverse square root of the process minimum feature size.

The Schottky collector also eliminates the collector contact resistance  $r_c$ , but  $r_c$  has significant impact on HBT bandwidth only when  $r_cC_{cb} \sim \tau_c$ , e.g. for collector space-charge-thicknesses  $T_c$  below 1000 å . In InGaAs/InAlAs SCHBTs the contact is to InGaAs. Schottky contacts to N-InGaAs result in very leaky junctions due to the small 0.2 eV conduction-band barrier, but it is the large 0.5

eV valence-band barrier which is relevant here; on base/Schottky-collector junctions with  $T_c = 2000$ å, we measure < 10A/cm<sup>2</sup> leakage at 4 V reverse bias.

Fig. 2 compares calculated HBT and SCHBT cutoff frequencies versus  $W_e$  for InAlAs/InGaAs devices, using measured HBT parameters ( $T_c = 2000$  å,  $T_b = 800$  å,  $\tau_b + \tau_c = 1.4$  ps,  $\rho_{bs} = 137$   $\Omega$ /square,  $\rho_{bc} = 70\Omega - \mu m^2$ ) taken from Hafizi et. al. [4]. Use of Hafizi's parameters, with fixed base and collector thicknesses, in calculation of the SCHBT scaling properties is conservative, in that it is beneficial here to reduce  $T_c$  and  $T_b$  as  $W_e$  is reduced. Even assuming fixed  $T_c$  and  $T_b$ , very high SCHBT cutoff frequencies are projected (fig. 2).

There are limits to emitter and collector scaling. As the emitter width is reduced, its periphery-area ratio increases and the current gain  $\beta$  drops due to surface recombination at the emitter-base mesa edge. In AlGaAs/GaAs, HBTs have attained very low surface recombination rates through use of depleted AlGaAs surface passivation layers [5]. In InGaAs/InAlAs, reduction of  $\beta$  for narrow emitters is much less severe because of the material's lower surface recombination velocities. An efficient Schottky collector must be as wide as the emitter, and alignment tolerances must be accommodated. With a projection mask aligner,  $0.5 \mu m$  features can be defined at 0.2  $\mu$ m alignment tolerance, resulting in  $W_e = 0.5 \mu \text{m}$ ,  $W_c = 0.9 \mu \text{m}$ , and  $f_{max} = 330 \text{ GHz}$ is calculated (fig. 2). With electron-beam lithography and reactive ion etching,  $W_e = W_c = 0.2 \mu \text{m}$ should be feasible, giving a projected 580 GHz  $f_{max}$

#### **Fabrication**

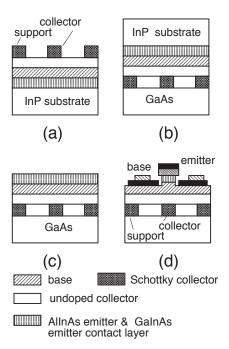

SCHBTs require processing of both sides of the transistor layers using epitaxial transfer (fig. 3) [6]. After a collector-up growth of the InAlAs/InGaAs HBT layers on a InP substrate, metal is deposited to form direct Schottky collector contacts to the undoped collector depletion layer. The wafer is then inverted and epoxied under vacuum to (e.g.) a GaAs substrate, whereupon the InP substrate is removed by an HCl selective etch. Alignment marks on the collector surface are then made visible using a recess etch. The remaining processes (emitter contact deposition, self-aligned base recess etch and base contact deposition, base mesa etch, and planarized emitter connections) then follow a normal HBT fabrication sequence [4].

There are two demanding steps in HBT fabrication; MBE growth with accurate positioning of

Figure 3: SCHBT fabrication process. Schottky collector contacts are deposited on MBE grown collector-up material (a). The wafer is inverted and epoxied under vacuum to a GaAs substrate (b). The InP substrate is removed by etching in HCl (c). Remaining process steps follow a normal HBT sequence (d).

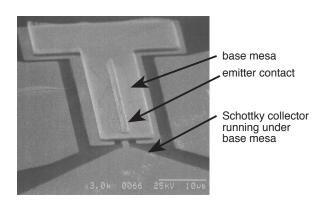

Figure 4: Electron micrograph of an SCHBT with  $W_c = W_e = 1 \mu \text{m}$  subsequent to epitaxial transfer, emitter and base ohmic contact deposition, and base mesa etching.

the base doping profile relative to the heterointerface, and control of the recess etch used in the self-aligned base process. SCHBT fabrication adds the additional step of epitaxial transfer [6]. These process steps can be integrated into a normal HBT process flow. We have performed extensive experiments on epitaxial transfer of HBT layers for SCHBT fabrication. Fig. 4 shows a sample with  $W_c = W_e = 1 \mu \text{m}$  after epitaxial transfer, the selfaligned emitter-base processes, and base mesa etching. The epoxy-bonded transferred epitaxial films are robust: experimental samples survive without degradation ohmic contact sintering (300° C), hot solvent cleaning, and the polyimide thermal curing cycles associated with the emitter planarization process.

### Conclusions

Cutoff frequencies of heterojunction bipolar transistors do not increase as process dimensions are reduced below 1  $\mu$ m. Schottky-collector HBTs should attain progressively increasing cutoff frequencies as the device dimensions are reduced. Successful realization of devices with cutoff frequecies above 500 GHz is dependent upon integration of an epitaxial transfer step into a normal HBT process, and development of dry etching and passivation technologies for fabrication of deep submicron emitters.

We acknowledge discussions with U. Mishra, W. Stanchina, P. Zampardi, and G. Sullivan. This work was supported by the AFOSR under grant F49620-92-J-0469.

#### References

- [1] Y. Konishi et. al., 1992 Engineering Foundation workshop on advanced heterostructure transistors, Kona, Hawaii, November.

- [2] Y. Konishi et. al., Solid-State Electronics, Vol. 36, No. 12, pp. 1673-1676, 1993

- [3] R.P. Smith et. al., IEEE Electron Device Letters, Vol. 15, No. 8, August 1994

- [4] M. Hafizi et. al., IEEE Trans. Elect. Dev., Vol. 40, No. 12, Dec. 1993.

- [5] C. Dai et. al., 1994 IEEE Device Research Conference, June 20-22, Boulder Co.

- [6] V. Abert-Engels et. al., 1994 IEEE Device Research Conference, June 20- 22, Boulder Co