# 48 GHz Digital ICs using Transferred-Substrate HBTs

Mark Rodwell, Q. Lee, D. Mensa, R. Pullela, J. Guthrie, S.C. Martin, R.P. Smith, S. Jaganathan, T. Mathew, B. Agarwal, S. Long.

Abstract—Using substrate transfer processes, we have fabricated heterojunction bipolar transistors with submicron emitter-base and collector-base junctions, minimizing RC parasitics and increasing  $f_{max}$  to 500 GHz. The process also provides a microstrip wiring environment on a low- $\epsilon_r$  dielectric substrate. First design iterations of ECL master-slave flip-flops exhibit 48 GHz maximum clock frequency when connected as static frequency dividers.

Keywords— heterojunction bipolar transistor, HBT, transferred-substrate, static frequency divider.

#### I. Introduction

A PPLICATIONS –present & potential– for heterojunction bipolar transistors (HBTs) include RF/ microwave analog-digital conversion, microwave direct digital frequency synthesis, and fiber-optic transmission in the range of 40–120 Gigabits/second.

The motivation for high circuit bandwidth varies with the application. In fiber-optic transmission, fast ICs will directly enable increased time-division-multiplexed transmission rates, complementing increases in channel capacity provided by wavelength-division-multiplexing. For oversampled  $(\Delta - \Sigma)$  analog-digital converters, in-band quantization noise power decreases in proportion to the  $5^{th}$  power of the oversampling ratio ( $2^{nd}$ -order modulators). Very high speed IC technologies offer the potential of  $\Delta - \Sigma$ ADCs with clock frequencies in the 10's of GHz, providing high dynamic range –and large instantaneous bandwidth– over radio-frequencies and lower microwave frequencies. In direct digital frequency synthesis (DDS), increases in logic IC clock rates and DAC bandwidths will result in increased synthesizer bandwidth. Used in radar transmitters, modulation bandwidths can then be increased and frequency agility improved.

A 100 GHz clock rate IC technology would permit significant advances in the performance of such signal conversion ICs. To permit clock rates exceeding 100 GHz, significant issues in transistor design, interconnects, packaging, and thermal design must be addressed. The transistor current gain  $(f_{\tau})$  and power gain  $(f_{max})$  cutoff frequencies must be several hundred GHz. Wiring parasitics must be minimized. The interconnects must have small inductance and capacitance per unit length, and the wire lengths, hence transistor spacings, must be small. Given that fast HBTs

Mark Rodwell, Q. Lee, D. Mensa, J. Guthrie, S. Jaganathan, T. Mathew, and S. Long are with the Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106, USA. R. Pullela is now with Lucent Technologies, Murray Hill, N.J. B. Agarwal is now with Rockwell Semiconductor Systems, Newport Beach, CA. S.C. Martin and R.P. Smith are with Jet Propulsion Labs, Caltech, Pasadena, CA.

operate at  $\sim 10^5~\rm A/cm^2$  current density, efficient heat sinking is then essential. To provide predictable performance, interconnects of more than a few ps length must have a controlled characteristic impedance. To prevent circuit-circuit interaction through ground-circuit common-lead inductance ("ground loops"), the IC technology must provide an integral ground plane for ground-return connection. Similarly, to prevent circuit-circuit interaction between the IC's input and output lines, common-lead inductance between the IC and package ground systems must be made vanishingly small.

Competing technologies for 100 GHz logic include submicron SiGe (and Si) bipolar transistors [1], InP/InGaAs [2] or InAlAs/InGaAs [4] HBTs, and InAlAs/InGaAs HEMTs. InAlAs/InGaAs HEMTs have extremely high bandwidths  $(200-300 \text{ GHz } f_{\tau}, 300-500 \text{ GHz } f_{max})$ , and have been used in quasi-dynamic ICs operating above 50 GHz [3]. Yet, circuit design is more difficult (level shifting due to the negative  $V_{qs}$ , large logics swing due to the low  $g_m/I_{dss}$  ratio), and present scales of integration with InAlAs/InGaAs HEMTs are well below the  $\sim 3000$  demonstrated with InPbased HBTs [4], most likely due to difficulties with 0.1  $\mu$ m lithography and gate recess etch control. Si/SiGe HBTs in standard planar processes offer  $\sim 100 \text{ GHz } f_{\tau}$  and  $f_{max}$ , very high yields, and 8" wafers. Further,  $\sim 10^6 \; \mathrm{A/cm^2 \; cur}$ rent densities in Si bipolars minimize  $C_{ie}$  and  $C_{cb}$  charging times, resulting in clock frequencies at a higher fraction of  $f_{\tau}$  than now obtained with III-V devices [1]. To win this competition, III-V HBT ICs must offer transistor bandwidths equal to -or better than- HEMTs, and 3-5 times that of Si. The technology must offer low inductance and low capacitance interconnects. IC's of  $\sim 1000-5000$  devices must be feasible.

# II. Transferred-Substrate HBTs

Transferred-substrate HBT ICs [5] offer high transistor bandwidth, low wiring capacitance, and low wiring inductance. In this process a substrate transfer step permits two-side processing of the device epitaxial layers, allowing definition of a transistor with narrow and aligned emitter-base and collector-base junctions.

In HBTs,  $f_{\tau}$  is primarily determined by the base transit time  $\tau_b$ , the collector transit time  $\tau_c$ , and the emitter charging time  $C_{je}(kT/qI_e)$ . Increases in  $f_{\tau}$  are obtained by thinning the collector, by thinning and grading the base, and by increasing the emitter current density. Unfortunately, thinning the base and collector epitaxial layers increases the collector capacitance  $C_{cb}$  and the base resistance  $R_{bb}$ ,

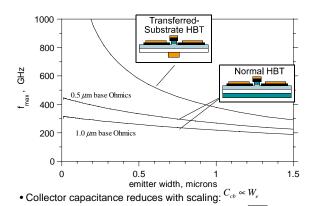

Fig. 1. Scaling of transferred-substrate and triple-mesa HBTs.

• Bandwidth increases rapidly with scaling:  $f_{\text{max}} \propto \sqrt{1/W_e}$

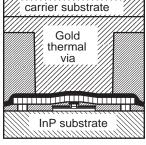

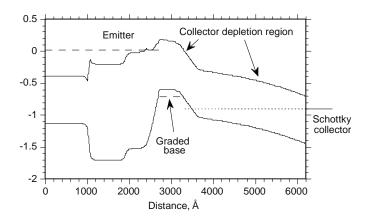

# 1) Normal emitter, base processes. Deposit silicon nitride insulator. 2) Coat with BCB polymer. Etch vias. 2) InP substrate 3) Electroplate with gold. Die attach to carrier substrate. 4) Invert wafer. Remove InP substrate.

3) Electroplate with gold.

Die attach to carrier substrate.

Fig. 2. Transferred-substrate HBT process flow.

decreasing  $f_{max} = (f_{\tau}/8\pi R_{bb}C_{cbi})^{1/2}$ . The base-collector junction is a distributed network and  $R_{bb}C_{cbi}$  represents an effective, weighted time constant [6]. For a fixed emitter stripe length, decreasing the width  $W_e$  of the emitter-base junction decreases the base spreading resistance, but does not decrease the base contact resistance. Scaling  $W_e$  reduces  $R_{bb}$  towards a minimum set by the contacts. Decreasing the width of the base-collector junction  $W_c$  decreases  $C_{cb}$ .

In normal double-mesa HBTs (fig. 1), the collector-base junction and base Ohmic contact are defined in a single process step. The Ohmic contacts must be at least one contact transfer length, setting a minimum collector junction width, and a minimum collector capacitance.  $R_{bb}C_{cb}$  has

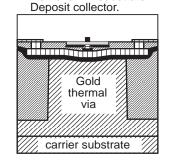

Fig. 3. Band diagram, under bias, of a typical device.

a minimum value, independent of lithographic limits, and  $f_{max}$  does not improve with scaling. In the transferred-substrate device, the collector width need only be larger than the emitter width. Reducing  $W_c$  and  $W_e$  progressively reduces  $R_{bb}C_{cb}$ , and  $f_{max}$  increases rapidly with scaling (fig. 1). With lateral scaling alone,  $f_{max}$  should approach 1 THz as dimensions are scaled to  $\sim 0.1 \ \mu m$ . Subsequently thinning the base and collector layers increases  $f_{\tau}$  at the expense of  $f_{max}$ . Simultaneous high values for both  $f_{\tau}$  and  $f_{max}$  are thus obtained.

# III. GROWTH AND FABRICATION

Fig. 3 shows the band diagram associated with a typical transferred-substrate HBT layer structure. The InGaAs base is nominally 400-500 Å thick, has kT-2kT bandgap grading, and is Be-doped at  $5\cdot10^{19}/\text{cm}^3$ . The InGaAs collector is 2500 Å thickness. A collector N<sup>+</sup> pulse-doped layer placed 400 Å from the base delays the onset of base pushout at high collector current densities. Devices typically use Schottky collector contacts [8], although HBTs with N+ subcollector layers (Ohmic-collector devices) have also been fabricated. While Ohmic-collector devices have non-zero collector series resistance, hence lower  $f_{max}$  [6], the 0.2 V barrier present in the Schottky-collector device increases the  $V_{ce}$  required to suppress base pushout at high current densities. Ohmic-collector devices thus show higher  $f_{max}$  under the low- $V_{ce}$  conditions associated with currentmode-logic (CML). Schottky-collector devices are used for emitter-coupled-logic (ECL), where the operating  $V_{ce}$  is higher.

Figure 2 shows the process flow. Standard fabrication processes [4] define the emitter-base junction, the base mesa, polyimide planarization, and the emitter contacts. The substrate transfer process commences with deposition of the PECVD  $\rm Si_3N_4$  insulator layer and the Benzocyclobutene (BCB) transmission-line dielectric (5  $\mu m$  thickness). Thermal and electrical vias are etched in the BCB. The wafer is electroplated to metalize the vias and to

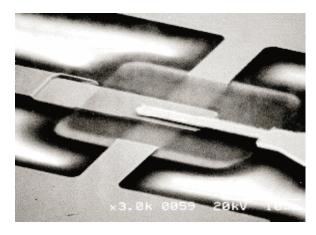

Fig. 4. Transferred-substrate HBT defined by contact lithography

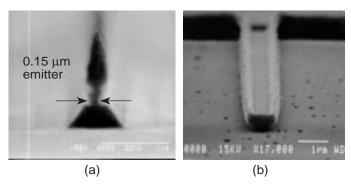

Fig. 5. E-beam HBT: test structure with 0.15  $\mu$ m emitter-base junction (a), and 0.4  $\mu$ m Schottky collector stripe (b)

form the ground plane. Subsequently, the wafer is Indiumbonded to a GaAs carrier substrate, and the InP substrate removed in HCl. Schottky collectors are then deposited, completing the process.

In addition to HBTs with narrow emitter and collector stripes, the process provides thermal vias for HBT heatsinking, NiCr resistors,  $\mathrm{Si_3N_4}$  MIM capacitors, and microstrip wiring on a  $\epsilon_r{=}2.7$  dielectric with vias, ground plane, and 3 levels of interconnects. To tolerate high power densities, the NiCr resistors must have thermal vias, which results in significant parasitic capacitance. Pull-up resistors in ECL do not require the thermal via.

A significant missing feature is in packaging. In the present process the microstrip ground plane is isolated from the wafer back surface by the GaAs transfer substrate, increasing thermal resistance and preventing low-inductance connections between the IC and package ground. A modified process with a fully metallic electroplated copper substrate is in development [7]. This will provide highly effective heatsinking (395 W/M · K for Cu vs. 74 for InP) and, with a package-IC ground interface over the full IC back surface, very low package-chip ground inductance.

# IV. DEVICE PERFORMANCE

Devices have been fabricated using contact lithography at 1–2  $\mu$ m resolution, using a 0.5  $\mu$ m stepper, and using electron-beam lithography. Fig. 4 shows a device with

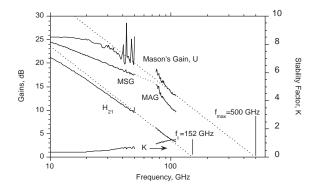

Fig. 6. W-band gains of device with a 0.4  $\mu$ m  $\times$  25  $\mu$ m emitter and a 1.0  $\mu$ m  $\times$  29  $\mu$ m collector.

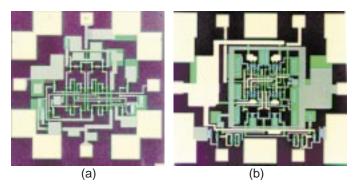

Fig. 7. CML (a) and ECL (b) master-slave D-flip-flops.

a  $0.6\mu\mathrm{m}$  by  $8\mu\mathrm{m}$  emitter and a  $1.6\mu\mathrm{m}$  by  $12\mu\mathrm{m}$  collector. The device exhibits 215 GHz peak  $f_{\tau}$ , and peak  $f_{max}$  above 400 GHz. Figure 5 shows HBT emitter-base and collector-base junctions defined by electron-beam lithography. Submicron devices fabricated by E-beam lithography (fig. 6) exhibit 500 GHz.  $f_{max}$  [9]. Neither contact lithography nor electron-beam lithography is suitable for fabrication of large ICs. We have recently fabricated HBT ICs using a  $0.5~\mu\mathrm{m}$  projection lithography system, and have obtained microwave gains (and  $f_{max}$ ) somewhat higher than that shown in fig. 6.

Device scaling also reduces D.C. current gain and breakdown voltage. Base current in narrow-emitter In-AlAs/InGaAs HBTs is predominantly due to conduction on the exposed InGaAs base surface between the emitter mesa and the base Ohmic contact.  $\beta$  decreases with emitter width, but increases as the base is thinned, as base bandgap grading is increased, and (at the expense of  $f_{max}$ ) as the emitter-base spacing is increased.  $\beta > 50$  has been obtained with 0.2  $\mu$ m emitters. The 2500 Å InGaAs collectors have very low breakdown, 1.5 V BV<sub>ceo</sub>, 2 V BV<sub>cbo</sub> at 1–2 ·10<sup>5</sup> A/cm<sup>2</sup> current density. Clearly, InP collectors should be used for highly scaled devices.

# V. DIGITAL IC DEMONSTRATION

As first digital ICs demonstrations, we fabricated ECL and CML master-slave D flip-flops, configured as 2:1 static frequency dividers [10]. Circuits were fabricated using contact lithography, producing devices with 0.6  $\mu$ m × 8 $\mu$ m

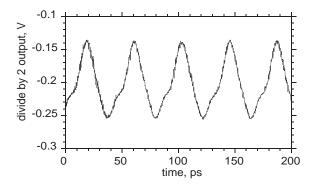

Fig. 8. CML static frequency divider output for 47 GHz input.

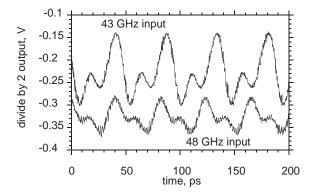

Fig. 9. ECL static divider output for 48 GHz and 43 GHz inputs...

emitters and 1.6  $\mu m \times 12~\mu m$  collectors. The devices operate at 1.25 mA/ $\mu m^2$ . The differential logic swing is 600 mV. The collector pull-up resistors are 50  $\Omega$ , hence the divider outputs directly drive 50  $\Omega$  output lines without buffering. Circuit design is entirely standard. The CML divider uses series-gated master and slave latches. Emitterfollower buffers are added to the CML clock and data ports to form the ECL divider. The ICs are shown in fig. 7

Measurement results are shown in figs. 8 and 9. The CML and ECL static frequency dividers operated at maximum clock frequencies of 47 and 48 GHz. The circuits dissipate 380 mW (ECL) or 75 mW (CML) from a -5 V supply, and have pad-limited 0.6 mm  $\times$  0.6 mm die areas. The peak ECL clock speed of 70 GHz predicted from SPICE simulation (in which efforts were made to model all significant device and interconnect parasitics) does not correlate with the measured 48 GHz. We suspect this discrepancy arises from strong emitter-follower gain peaking at 50 GHz. We have observed very strong  $\sim 50$  GHz gain peaking –inconsistent with SPICE simulation– in resistive feedback amplifiers [11], [12], and have suppressed it with shunt resistive loading at the emitter-follower output [13]. Design studies now in progress suggest the feasibility of 100 GHz clock rates with the present HBTs, but the device models –and the circuits– remain to be validated.

## VI. Conclusions

100 GHz digital ICs require a high-bandwidth transistor, low-parasitic interconnects, and effective heatsinking. Us-

ing substrate transfer processes, HBTs can be fabricated with highly scaled lithographic and epitaxial dimensions, giving both high  $f_{\tau}$  and high  $f_{max}$ . Initial designs yielded 48 GHz digital ICs [10] and 50-80 GHz amplifiers [11], [12], [14]. With further scaling and improved circuit design, 100 GHz digital ICs will be feasible.

## ACKNOWLEDGMENTS

Work at UCSB supported by the ONR under grants N00014-95-1-0688 and N00014-98-1-0068 (J. Zolper, M. Yoder), and by the AFOSR under grant F4962096-1-0019 (H. Schlossberg). JPL work was performed at the Center for Space Microelectronics Technology, JPL, Caltech, and sponsored by the NASA office of Space Science

#### References

- [1] M. Wurtzer et. al. "42 GHz static frequency divider in a Si-SiGe bipolar technology" *IEEE International Solid-State Cir*cuits Conference, Digest of Technical Papers, 1997

- [2] Y. Matsuoka, S. Yamahata, K. Kurishima and H. Ito, Ultrahigh-Speed InP/InGaAs Double-Heterostructure Bipolar Transistors and Analyses of Their Operation", in J. of Appl. Phys., vol. 35, pp. 5646-5654, 1996.

- [3] Yoneyama, M.; Otsuji, T.; Imai, Y.; Yamaguchi, S.; Enoki, T.; Umeda, Y.; Hagimoto, K.,, "46 Gbit/s super-dynamic decision circuit module using InAlAs/InGaAs HEMTs". Electronics Letters, vol.33, (no.17), IEE, 14 Aug. 1997. p.1472-1474.

- [4] W. E. Stanchina, J.F. Jensen, R.H. Walden, M. Hafizi, H.-C. Sun, T. Liu, G. Raghavan, K.E. Elliot, M. Kardos, A.E. Schmitz, Y.K. Brown, M.E. Montes, and M. Yung, "An InP-based HBT fab for High-Speed Digital, Analog, Mixed-Signal, and Optoelectronic ICs" GaAs IC Symp. Tech. Dig., 1995, pp. 31-34

[5] Q. Lee, B. Agarwal, D. Mensa, R. Pullela, J. Guthrie, L.

- [5] Q. Lee, B. Agarwal, D. Mensa, R. Pullela, J. Guthrie, L. Samoska and M. J. W. Rodwell, "A > 400 GHz f<sub>max</sub> transferred-substrate heterojunction bipolar transistor IC technology", IEEE Electron Dev. Lett., vol. 19, pp. 77-79, 1998.

- [6] M. Vaidyanathan and D. L. Pulfrey, "Extrapolated f<sub>max</sub> of heterojunction bipolar transistors", Submitted to IEEE Transactions on Electron Devices.

- [7] J. Guthrie, D. Mensa, B. Agarwal, Q.Lee, R. Pullela, M. Rodwell, "HBT IC process with a Copper Substrate" IEE Electronics Letters, Vol. 34, No. 5, pp. 467-468, 5 March, 1998

- [8] R.P. Smith, S.T. Allen, M. Reddy, S.C. Martin, J. Liu, R.E. Muller, and M.J.W. Rodwell, "0.1 μm Schottky-Collector AlAs/GaAs Resonant Tunneling Diodes", *IEEE Electron Device Letters*, Vol. 15, No. 8, August 1994.

- [9] Q. Lee, S.C. Martin, D. Mensa, R. Pullela, R.P.Smith, B. Agarwal, J. Guthrie, M. Rodwell "Deep Submicron transferred-substrate heterojunction bipolar transistors" 1998 Device Research Conference, June Charlottesville, VA, June.

- [10] R. Pullela, D. Mensa, B. Agarwal, J. Guthrie, M. Rodwell, "47 GHz static frequency divider in Ultrafast transferred-substrate heterojunction bipolar transistor technology" 1998 Conference on InP and Related Materials, May, Tsukuba, Japan

- [11] B. Agarwal, D. Mensa, Q. Lee, R. Pullela, J. Guthrie, L. Samoska and M. J. W. Rodwell, "A 13 dB, 50 GHz Feedback Amplifier with AlInAs/GaInAs Transferred-substrate HBT", 1997 IEEE International Electron Device Meeting, December, Washington, DC

- [12] B. Agarwal, Q. Lee, R. Pullela, D. Mensa, J. Guthrie, M. J.W. Rodwell, "A transferred-substrate HBT wideband differential Amplifier to 50 GHz" IEEE Microwave and Guided Wave Letters, June 1998.

- [13] D. Mensa, et. al.. "Baseband amplifiers in the transferredsubstrate HBT technology". This conference.

- [14] B. Agarwal, R. Pullela, Q. Lee, D. Mensa, J. Guthrie, M. J.W. Rodwell, "80 GHz Distributed Amplifiers with transferred-substrate heterojunction bipolar transistors" 1998 IEEE MTT Microwave Symposium, June, Baltimore Md.