InP-based HBTs: Devices and GHz mixed-signal ICs

Mark Rodwell

University of California, Santa Barbara

rodwell@ece.ucsb.edu 805-893-3244, 805-893-3262 fax

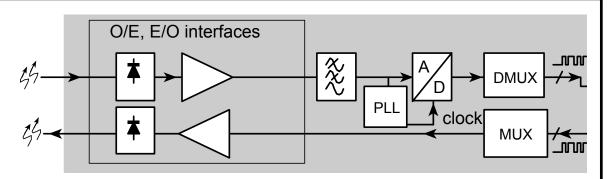

# Applications:

#### Applications: optical fiber transceivers at 40 Gb/s and higher

Key advantages for:

TIA, LIA, Modulator driver

Closer competition with SiGe:

MUX/CMU, DMUX/CDR

lower power

problems with integration scale

"40 Gb" is often 44, 48, or 52... increases InP leverage over SiGe

80 & 160 Gb may come in time world may not need capacity for some time WDM might be better use of fiber bandwidth

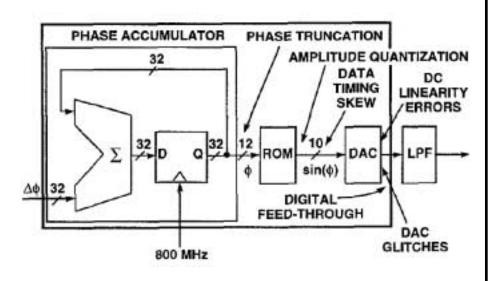

#### Applications: military mixed-signal ICs

Radar/Comms transmitter electronics direct digital frequency synthesis accumulator, sine ROM, DAC

Radar/Comms receiver electronics high resolution ADC

#### **Technology requirements**

3,000 to 30,000 transistors Few GHz IF (operating ) bandwidths ~160 dB/Hz dynamic range

high resolution drives technology speed far beyond signal bandwidth

50-100 GHz clock rate digital technologies sought

#### Applications: wireless / RF

#### **Present Wireless/RF ICs**

GaAs HBTs at lower frequencies InGaAs PHEMTs in higher bands

#### **Opportunities for InP**

33 GHz LMDS and 60 GHz metropolitan area networks (IEEE 802.16) cheap GaAs HBT processes  $\rightarrow$  cheap InP HBT processes 200 GHz  $f_t$  and  $f_{max}$ , 8 V BVCEO quick migration to 6" wafers enabled by metamorphic growth on GaAs

#### Longer-term opportunities for InP

wider range of RF/wireless applications ...IF SiGe-like integration scales can be reached.

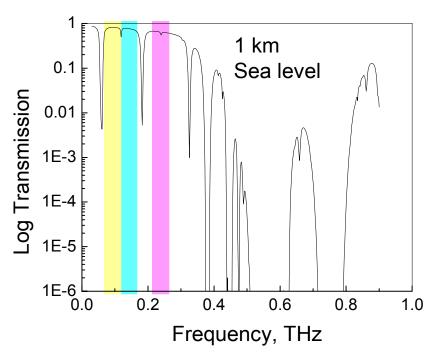

#### mmWave Transmission

**UCSB**

Atmospheric attenuation is LOW (~4 dB/km) at bands of interest 60-80 GHz, 120-160 GHz, 220-300 GHz

(Weather permitting)

Geometric path losses are LOW due to short wavelengths.

55 mW transmitter power sufficient for 10 Gb/s transmission over 500 meters range.

| Bit rate          | 1.00E+10 | 1/sec     |                                 |  |

|-------------------|----------|-----------|---------------------------------|--|

| carrier frequency | 1.50E+11 | Hz        |                                 |  |

| F                 | 10       | dB        | receiver noise figure           |  |

| Distance          | 5.00E+02 | m         | trans mis s ion range           |  |

| atmospheric loss  | 4.00E-03 | dB/m      | dB loss per unit distance       |  |

| Dant, trans       | 0.1      | m         | transmit antenna diameter       |  |

| Dant, revr        | 0.1      | m         | receive antenna diameter        |  |

| bits/symbol       | 1        |           |                                 |  |

| kT                | -173.83  | dBm (1Hz) |                                 |  |

| Prec              | -48.27   | dBm       | received power at 10^{-9} B.E.R |  |

| $\Delta f$        | 1.00E+10 | Hz        | RF channel bandwidth required   |  |

| trans mis s ion   | -63.68   |           | geometric path loss, dB         |  |

| atmospheric loss  | 2        | dB        | total atmospheric loss, dB      |  |

| P trans mitte r   | 55.1     | mW        | required transmitter power      |  |

# Transistor Figures of Merit

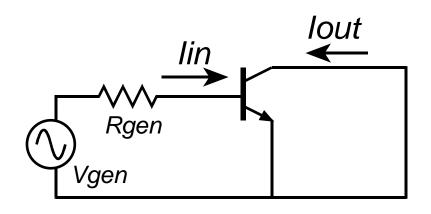

#### Short-circuit current gain cutoff frequency

short-circuit current gain: drive input, short output, measure  $H_{21}=I_{out}/I_{in}$

$$H_{21}(f) \approx \frac{1}{(1/\beta) + (jf/f_{\tau})}$$

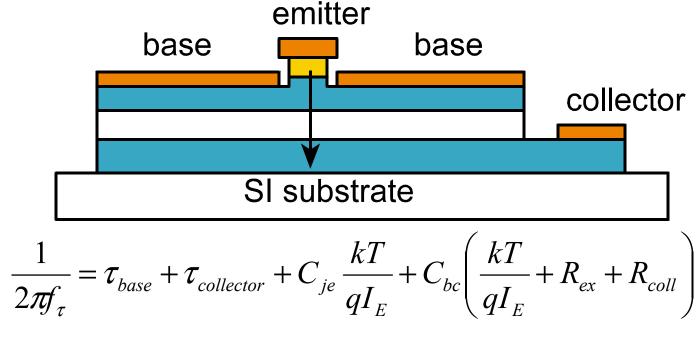

# Current-gain cutoff frequency in HBTs

$$\tau_{base} \approx T_b^2 / 2D_n$$

$\tau_{collector} \approx T_c / 2v_{sat}$

RC terms are quite important for > 200 GHz  $f_{\tau}$  devices  $f_{\tau}$  is a questionable metric for high speed digital logic ...where capacitance charging has proportionally larger role

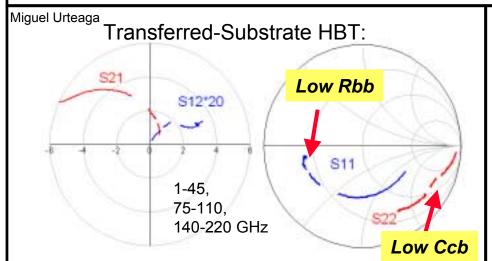

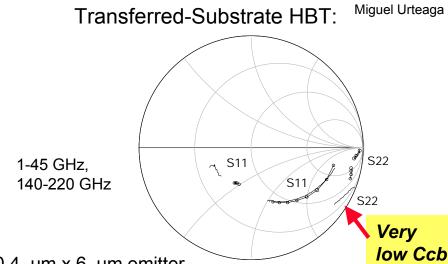

Miguel Urteaga

# Measurement of power gains and $f_{max}$

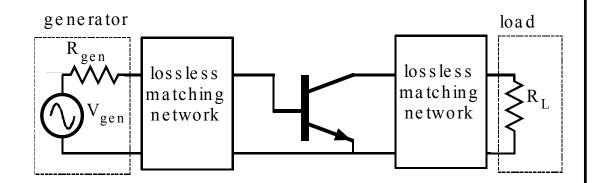

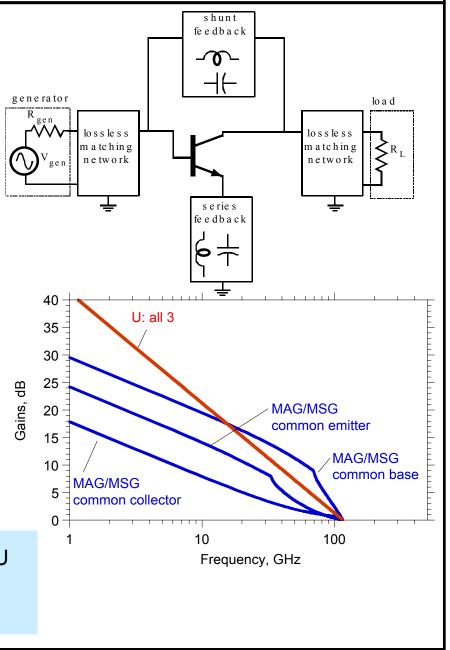

#### **Maximum Available Gain**

Simultaneously match input and output of device

$$\mathbf{MAG} = \frac{|S_{21}|}{|S_{12}|} (K - \sqrt{K^2 - 1})$$

K = Rollet stability factor

Transistor must be unconditionally stable or MAG does not exist

#### **Maximum Stable Gain**

Stabilize transistor and simultaneously match input and output of device

$$\mathbf{MSG} = \frac{|S_{21}|}{|S_{12}|} = \frac{|Y_{21}|}{|Y_{12}|} \approx \frac{1}{\omega C_{cb} \left(R_{ex} + kT/qI_{c}\right)}$$

Approximate value for hybrid- $\pi$  model

To first order MSG does not depend on  $f_{\tau}$  or  $R_{bb}$

For Hybrid-  $\pi$  model, MSG rolls off at 10 dB/decade, MAG has no fixed slope. So, NEITHER can be used to accurately extrapolate  $f_{max}$

MSG/MAG is however of direct relevance in tuned RF amplifier design

Miguel Urteaga

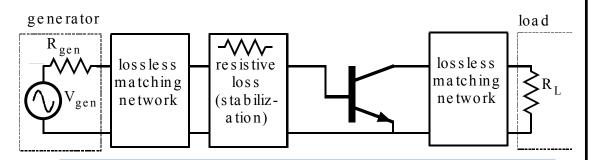

#### **Unilateral Power Gain**

#### **Mason's Unilateral Power Gain**

Use lossless reactive feedback to cancel device feedback and stabilize the device, then match input/output.

$$\mathbf{U} = \frac{\left| \mathbf{Y}_{21} - \mathbf{Y}_{12} \right|^2}{4 \left( \mathbf{G}_{11} \mathbf{G}_{22} - \mathbf{G}_{21} \mathbf{G}_{12} \right)}$$

U is not changed by pad reactances

#### For Hybrid- $\pi$ model, U rolls off at 20 dB/decade

ALL Power Gains must be unity at  $f_{max}$

Monolithic amplifiers not easily made unilateral, so U of only historical relevance to IC design.

U is *usually* valuable for f<sub>max</sub> extrapolation

#### **Excess Collector Capacitance, Fmax, and Device Utility**

The partitioning between  $C_{cbi}$  and  $C_{cbx}$  will be discussed later.

$C_{cbx}$  has no effect upon  $f_{max}$  or U.

$C_{cbx}$  has a large impact upon common - emitter MSG,

hence has large impact on usable gain in mm - wave circuits.

$C_{cbx}$  has a large impact upon digital logic speed.

# high f<sub>max</sub> does not mean low C<sub>cb</sub> or fast logic

# What do we need: $f_{\tau}$ , $f_{max}$ , or ...?

#### Tuned ICs (MIMICs, RF):

fmax sets gain, & max frequency, not ft. ...low ft/fmax ratio makes tuning design hard (high Q) high C<sub>cbx</sub> reduces MSG

#### **Lumped analog circuits**

need high & comparable ft and fmax.

C<sub>cb</sub>/I<sub>c</sub> has major impact upon bandwidth

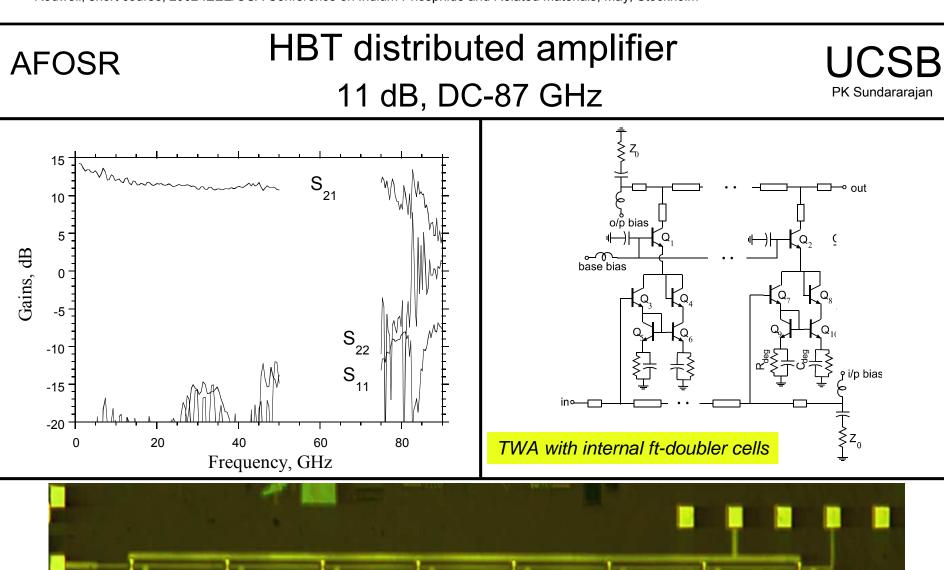

#### **Distributed Amplifiers**

in principle, fmax-limited, ft not relevant....

(low ft makes design hard)

digital ICs will be discussed in detail later

# transistor layer structures

#### SHBT layer structure

| Layer                  | Material                                                       | Doping                                                                                    | Thickness (Å) |

|------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------|

| Emitter cap            | In <sub>0.53</sub> Ga <sub>0.47</sub> As                       | $2 \times 10^{19} \text{ cm}^{-3}$ : Si                                                   | 300           |

| N <sup>+</sup> emitter | InP                                                            | $2 \times 10^{19} \text{ cm}^{-3}$ : Si                                                   | 700           |

| N⁻ emitter             | InP                                                            | $8 \times 10^{17} \text{ cm}^{-3}$ : Si                                                   | 500           |

| Emitter-base grade     | $In_{0.53}Ga_{0.26}Al_{0.21}As$<br>to $In_{0.455}Ga_{0.545}As$ | P: $4 \times 10^{17}$ cm <sup>-3</sup> : Si<br>N: $8 \times 10^{17}$ cm <sup>-3</sup> : C | 233<br>47     |

| Base                   | $In_{0.53}Ga_{0.47}As$                                         | N: $4 \times 10^{19}$ cm <sup>-3</sup> : C                                                | 400           |

| Collector              | In <sub>0.53</sub> Ga <sub>0.47</sub> As                       | N: $2 \times 10^{16} \text{ cm}^{-3}$ : Si                                                | 2000          |

| Subcollector           | InP                                                            | N: $1 \times 10^{19}$ cm <sup>-3</sup> : Si                                               | ~1000 Å       |

very low breakdown: scaling beyond ~75 GHz digital clock rate very difficult

high collector-base leakage particularly at elevated temperatures. Serious difficulties in real applications

very high thermal resistance InGaAs collector and subcollector

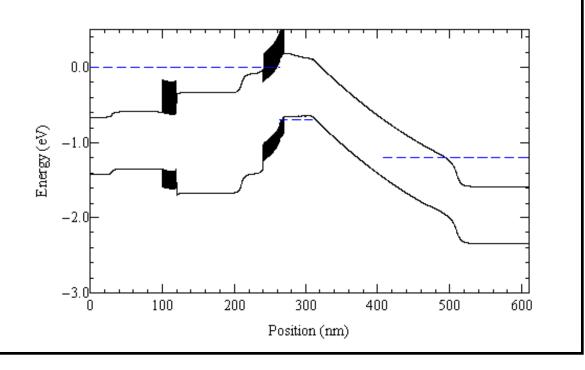

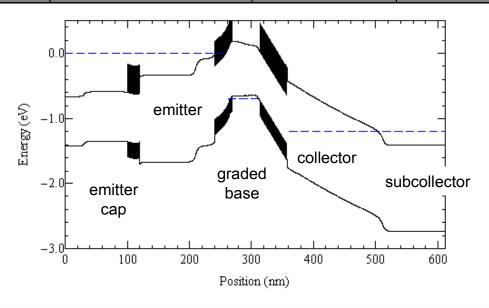

#### **DHBT** Layer structure

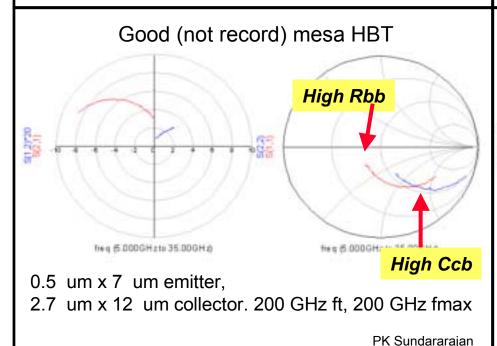

PK Sundararajan

B-C grade design is critical

InGaAs or GaAsSb bases GaAsSb more easily passivated otherwise comparable

#### high breakdown

important for microwave power important for logic

#### low thermal resistance

essential for high power density important for microwave power important for logic

#### **Performance**

ft and fmax good or better than SHBTs

| Layer                       | Material                                                                                                   | Doping                                                                                    | Thickness (Å) |

|-----------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------|

| Emitter cap                 | In <sub>0.53</sub> Ga <sub>0.47</sub> As                                                                   | $2 \times 10^{19} \text{ cm}^{-3}$ : Si                                                   | 300           |

| N <sup>+</sup> emitter      | InP                                                                                                        | $2 \times 10^{19} \text{ cm}^{-3}$ : Si                                                   | 700           |

| N⁻ emitter                  | InP                                                                                                        | $8 \times 10^{17} \text{ cm}^{-3}$ : Si                                                   | 500           |

| Emitter-base grade          | $In_{0.53}Ga_{0.26}Al_{0.21}As$<br>to $In_{0.455}Ga_{0.545}As$                                             | P: $4 \times 10^{17}$ cm <sup>-3</sup> : Si<br>N: $8 \times 10^{17}$ cm <sup>-3</sup> : C | 233<br>47     |

| Base                        | $In_{0.53}Ga_{0.47}As$                                                                                     | N: $4 \times 10^{19}$ cm <sup>-3</sup> : C                                                | 400           |

| Base-<br>collector<br>grade | In <sub>0.53</sub> Ga <sub>0.47</sub> As<br>to In <sub>0.53</sub> Ga <sub>0.26</sub> Al <sub>0.21</sub> As | N: $2 \times 10^{16}$ cm <sup>-3</sup> : Si                                               | 240           |

| Pulse doping                | InP                                                                                                        | $5.6 \times 10^{18} \text{ cm}^{-3}$ : Si                                                 | 30            |

| Collector                   | InP                                                                                                        | N: $2 \times 10^{16} \text{ cm}^{-3}$ : Si                                                | 1,630         |

| Subcollector                | InP                                                                                                        | N: $1 \times 10^{19}$ cm <sup>-3</sup> : Si                                               | ~1000 Å       |

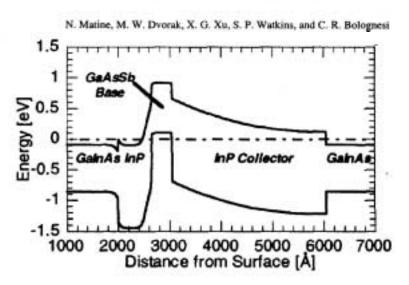

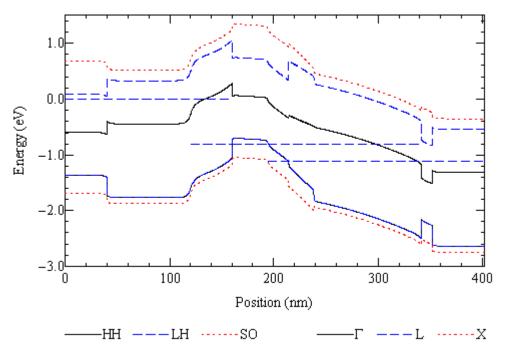

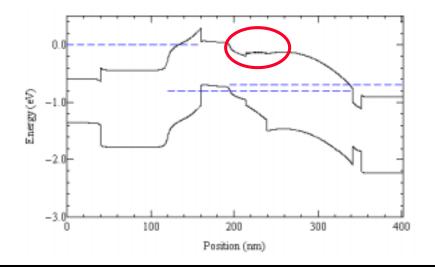

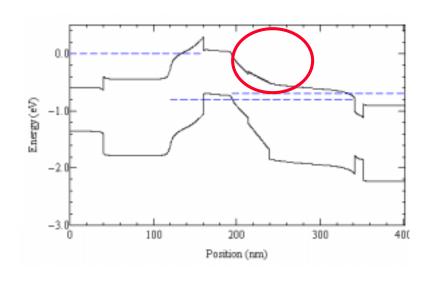

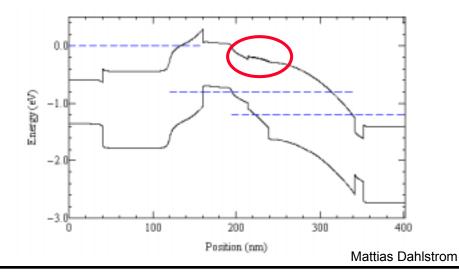

#### Alternative InP DHBT base-collector junction designs

#### Several layer alternatives exist for DHBTs with:

high ft high current density negligible current blocking low base sheet and contact resistivity

InAlAs/ InGaAs superlattice

UCSB: InGaAs base, MBE

InP collector

InGaAs

InGaAs setback

base

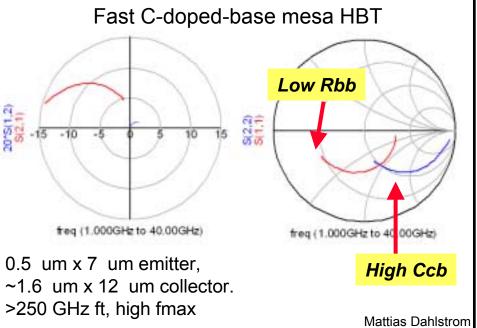

Mattias Dahlstrom

200

Position (nm)

300

11th International Conference on Indiam Phosphide and Related Materials 16-20 May 1999 Davis, Switzerland TuA1-3

#### InP/GaAsSb/InP DOUBLE HETEROJUNCTION BIPOLAR TRANSISTORS WITH HIGH CUT-OFF FREQUENCIES AND BREAKDOWN VOLTAGES

InP/InGaAs DHBTs with 341-GHz f at high current density of over 800 kA/cm2

100

Minoru Ida, Kenji Kurishima, Noriyuki Watanabe, and Takatomo Enoki

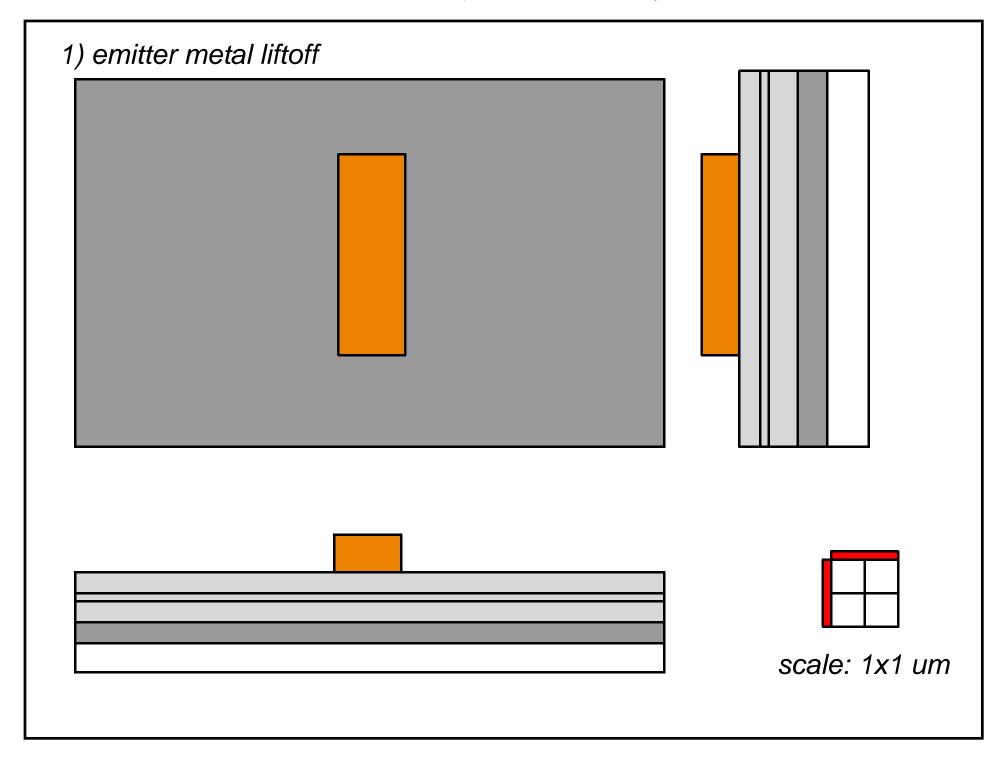

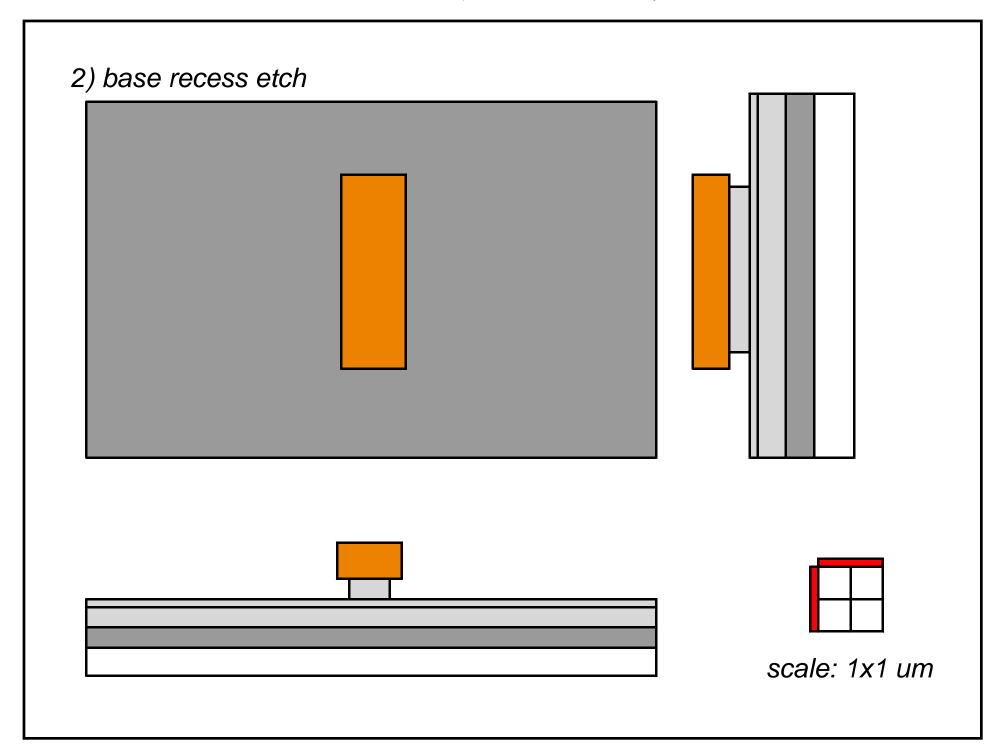

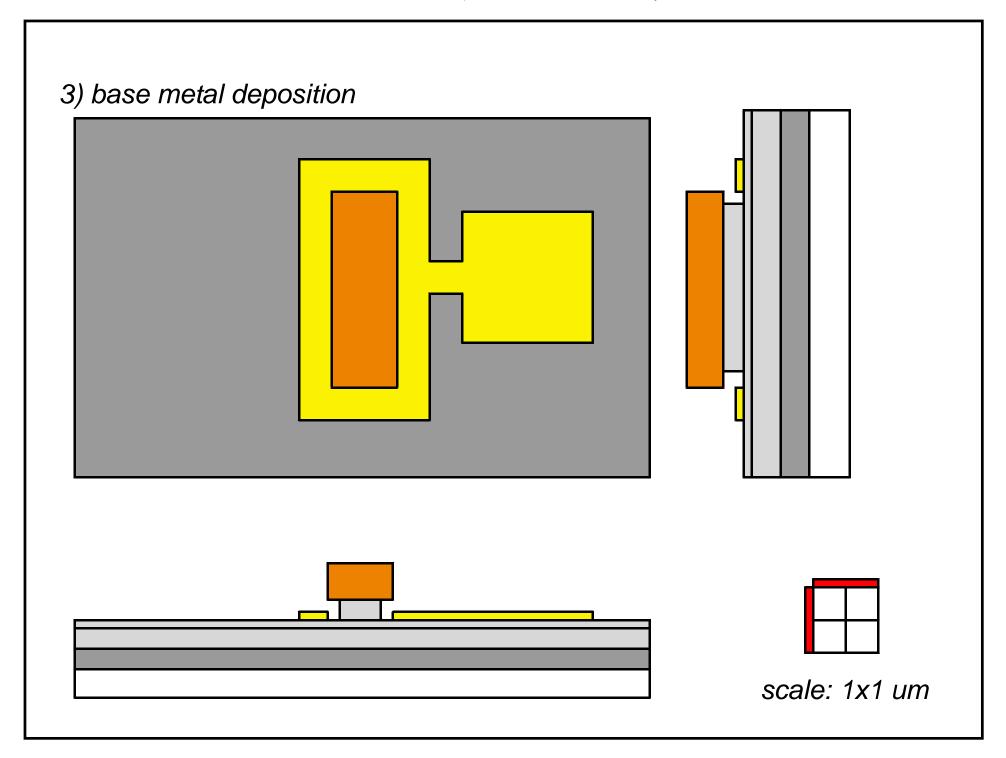

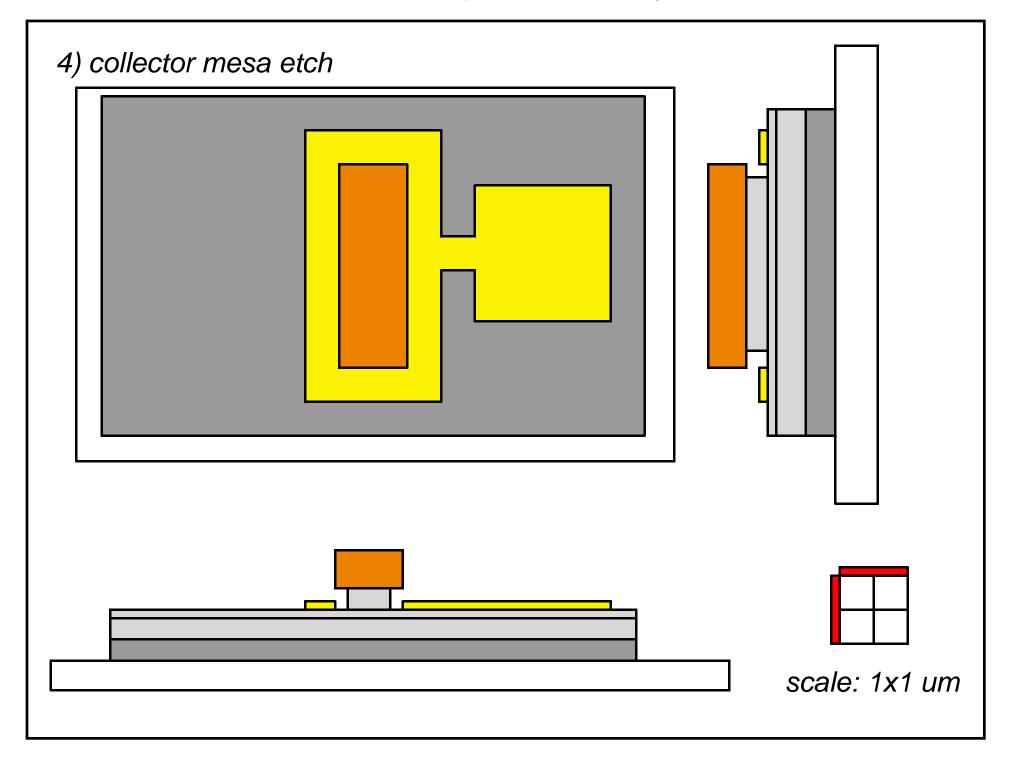

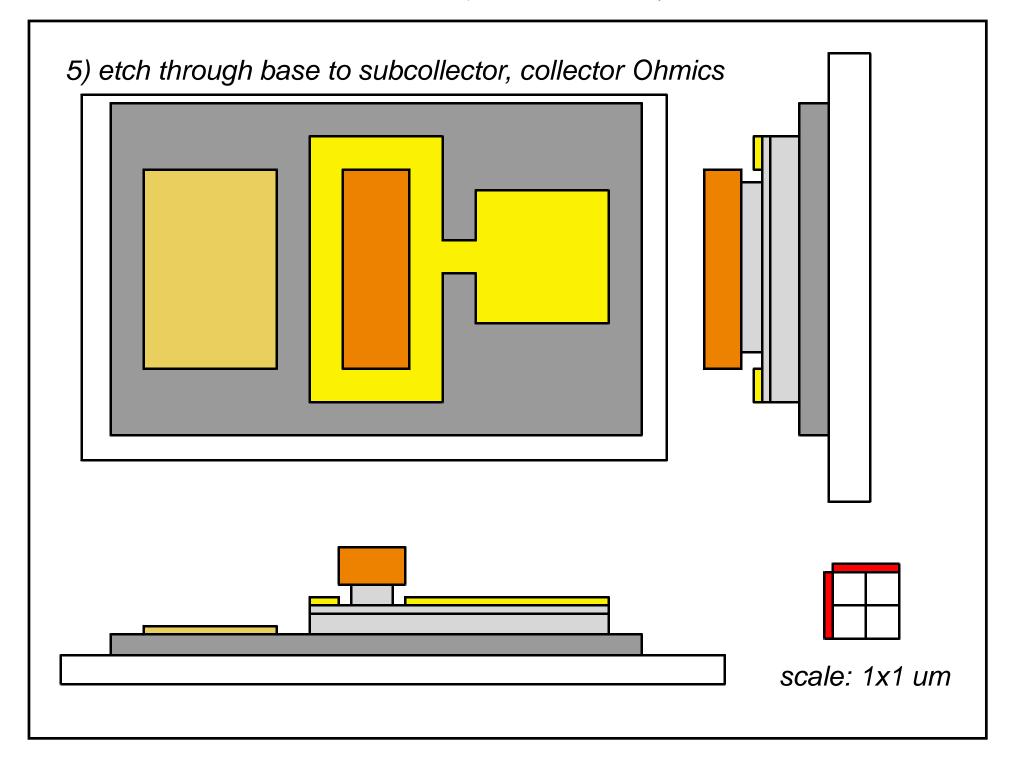

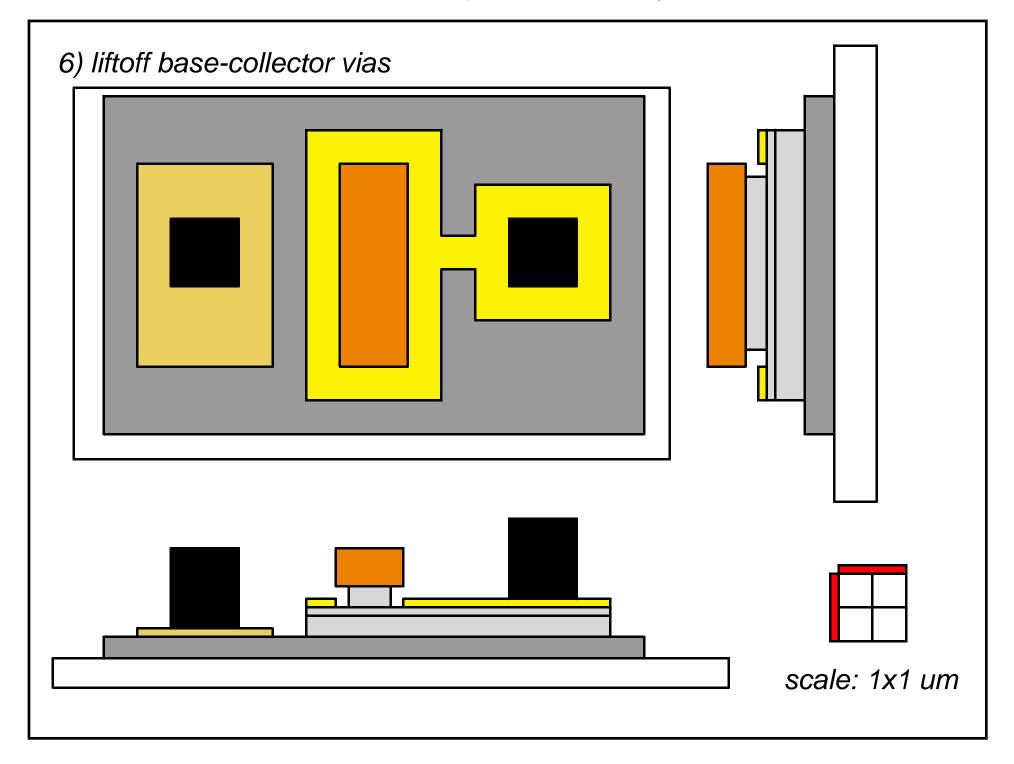

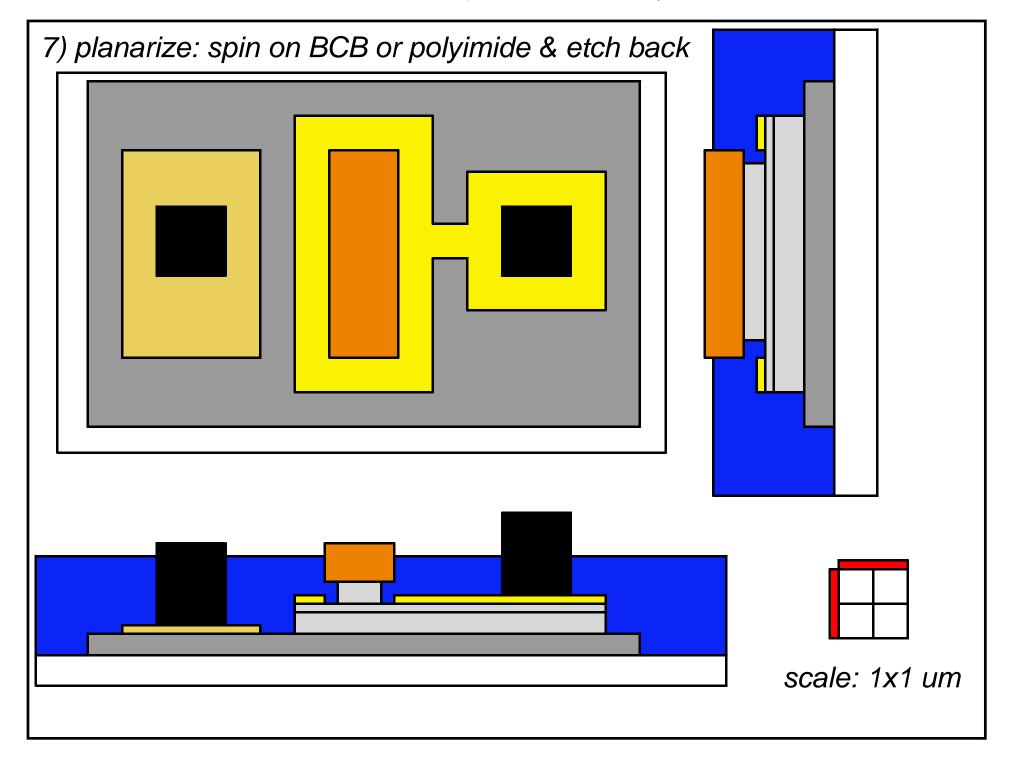

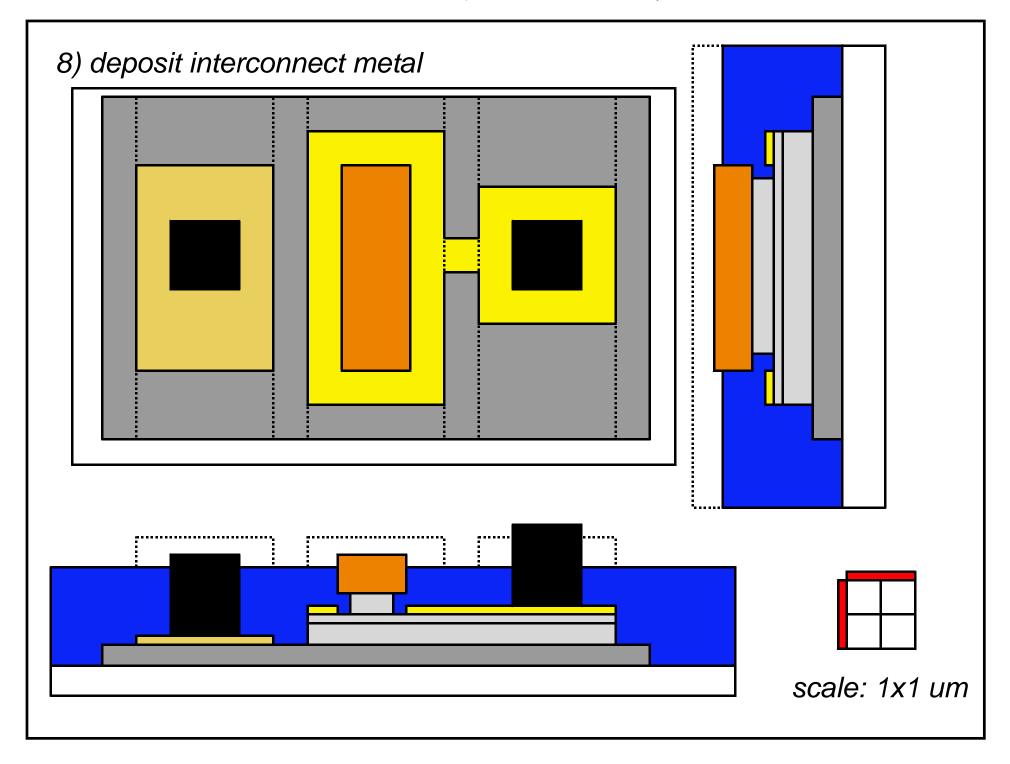

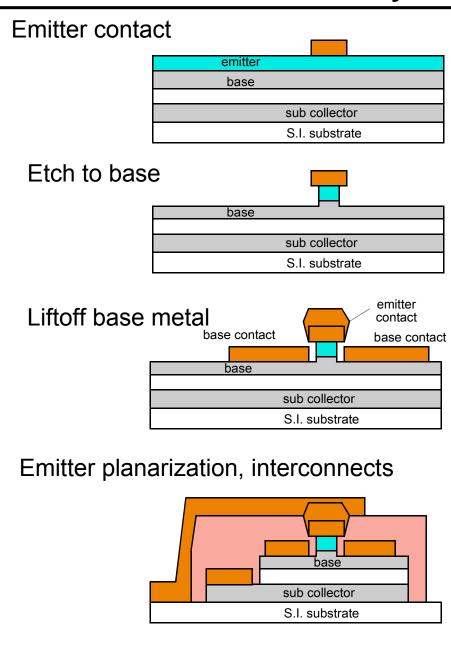

# transistor process flow

(research-lab-like)

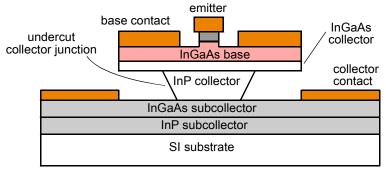

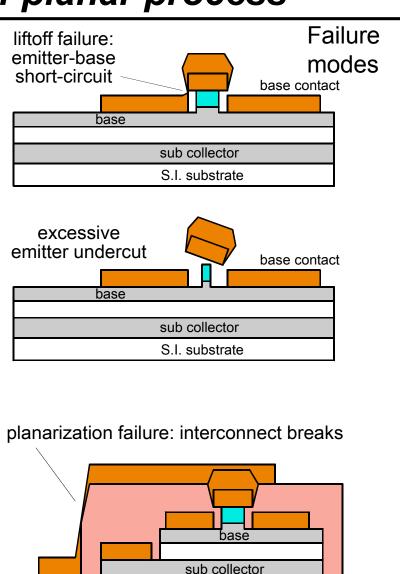

# Problems with mesa process flow

#### Large Parasitic Collector Junction, Large Excess Ccb

resembles Si bipolar processes of 1960's!

parasitic collector junction lies under base contacts

base contacts must be nonzero size: nonzero resistivity

base contacts must be nonzero size: lithographic impact on yield

#### Self-aligned emitter-base process flow

base-emitter short-circuits problems with wet-etch undercut control problems with dry-etch reproducibility

#### Nonplanar process

loss of yield in back-end process

# Problems with mesa process flow

emitter-base junction is 3 um^2 collector-base junction is 12 um^2

collector/emitter area ratio even worse in non-self-aligned processes...

While research-lab processes have moderate Ccb, processes aimed at high yield at >3000 HBTs have very large collector junctions

Ccb then the dominant circuit parasitic, regardless of impact on  $f_{\tau}$  &  $f_{max}$ .

# transistor key parasitics and model

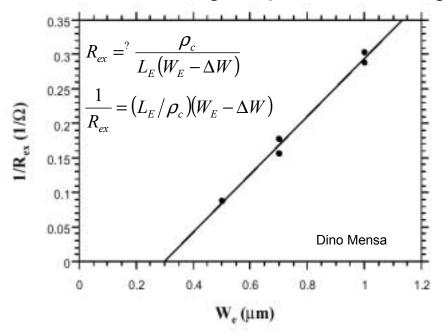

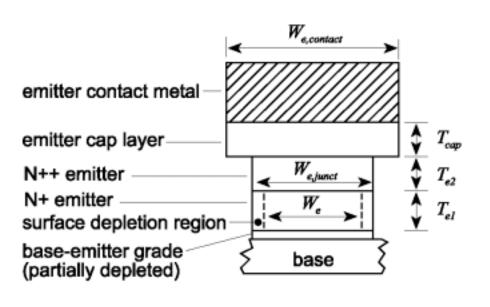

#### **Emitter Resistance**

Emitter resistance: one limiting factor in scaling for speed high speed devices: high  $J \to \text{low}\left(C_{cb}/I_c\right)$  but high  $J \to \text{excessive}\left(I_E R_{ex}\right)$  voltage drop

evidence of edge depletion or damage

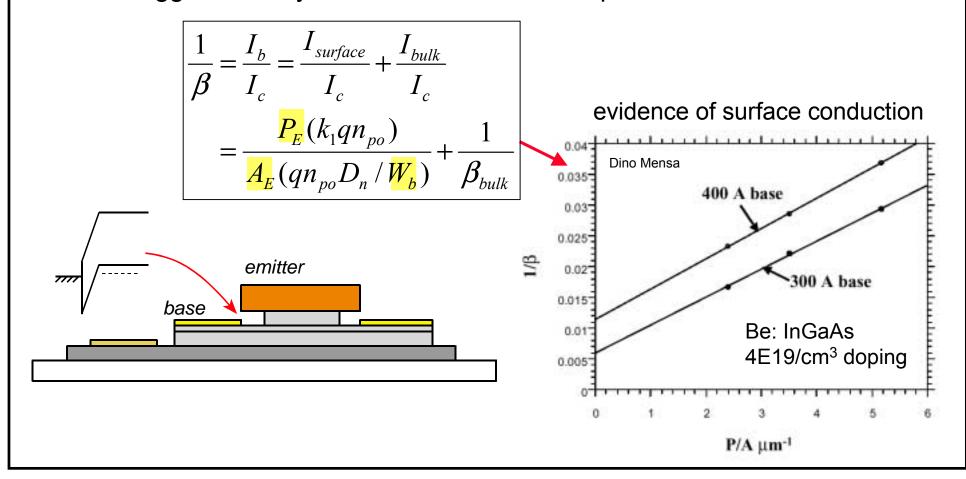

# Current Gain: surface leakage

#### **Surface Conduction:**

InGaAs has low surface recombination velocity.

InGaAs has surface pinning near conduction band.

→ weak surface inversion layer on base, surface conduction to base contact Problem aggravated by InP emitter, as this also pins near conduction band

# **Current Gain: Auger recombination**

Carbon base doping: above  $10^{20}$  / cm<sup>2</sup> feasible

Bulk recombination dominated by Auger

$$\tau_{\rm Auger} \propto 1/N_A^2$$

Since

$$\tau_{\rm base} \propto 1/T_B^2$$

..

$$\beta \propto 1/(N_A T_B)^2 \propto 1/\rho_{sheet}^2$$

This constrains  $\rho_{sheet}$  reduction through high base doping

But, high base doping + thin base

⇒ low base contact resistivity, low transit time

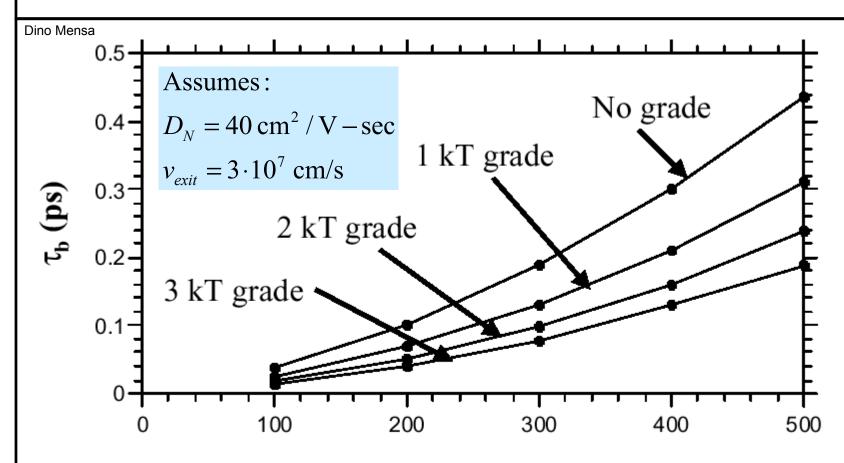

#### **Base Transit Time**

#### **Base Thickness (Angstroms)**

$$\tau_b = W_b L_g / D_n - (L_g^2 / D_n - L_g / v_{sat}) (1 - e^{-W_b / L_g})$$

where  $L_g$  is the grading length:

$$L_g = W_b \left( kT / \Delta E_g \right)$$

Drift - diffusion model correct if

$$\tau_b >> \tau_m \approx D_n m^* / kT \approx 35 \text{ fs}$$

# Base Bandgap vs. Doping Grading

Objective: introduce a 52 meV potential drop across base.

Case 1: base bandgap grading.

Vary In : Ga ratio :  $In_{0.455}Ga_{0.545}As \leftrightarrow In_{0.53}Ga_{0.47}As$  (strained)

Case 2: base doping grading, non - degenerate base

Base doping near emitter side constrained by growth / reliability

Reduce doping at collector side of base by  $e^{-2}:1=0.12:1$

- ⇒ greatly increased base sheet resistance

- ⇒ Contact resistance increased : contacts land somewhere in middle of base

Case 3: base doping grading, degenerate base

Degenerate doping statistics: small doping change induces big field

With heavy doping, Auger-induced  $\beta$  collapse sets maximum  $\int_0^{T_b} p(x) dx$

Can introduce built - in field without degrading sheet resistance.

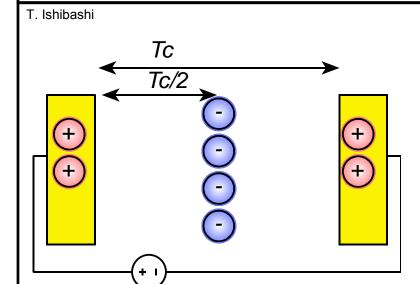

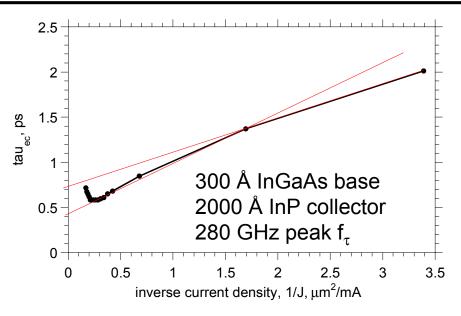

#### **Collector Transit Time**

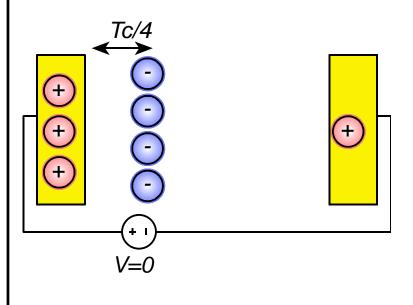

V=0

From elementary electrostatics (refer to sketch)

$$\tau_{\rm c} = \int_{0}^{T_c} \frac{(1 - x / T_c)}{v(x)} dx \equiv \frac{T_c}{2v_{eff}}$$

$\tau_{\rm c}$  is more sensitive to velocity near base.

Fortuitous, as initial velocity is high, then decreases due to  $\Gamma$ -L scattering.

#### **Collector Transit Time**

...from best fit to RF data

Velocities in InGaAs collectors

$3-5\cdot10^7$  cm/s for  $\sim 2000$  Å layers

Velocities in InP collectors

also  $3 - 5 \cdot 10^7$  cm/s for  $\sim 2000$  Å layers

#### **Current-induced Collector Velocity Overshoot (?)**

Effect predicted by Ishibashi

$\tau_{\rm ec}$  data \*does \* show predicted trend.

BUT:  $\tau_{\rm ec}$  variation may also be due to modulation in emitter ideality factor with bias current  $(1/g_m$  often does not vary as  $R_{\rm ex} + kT/qI_E$ ).  $C_{\rm ie}$  also varies with bias.

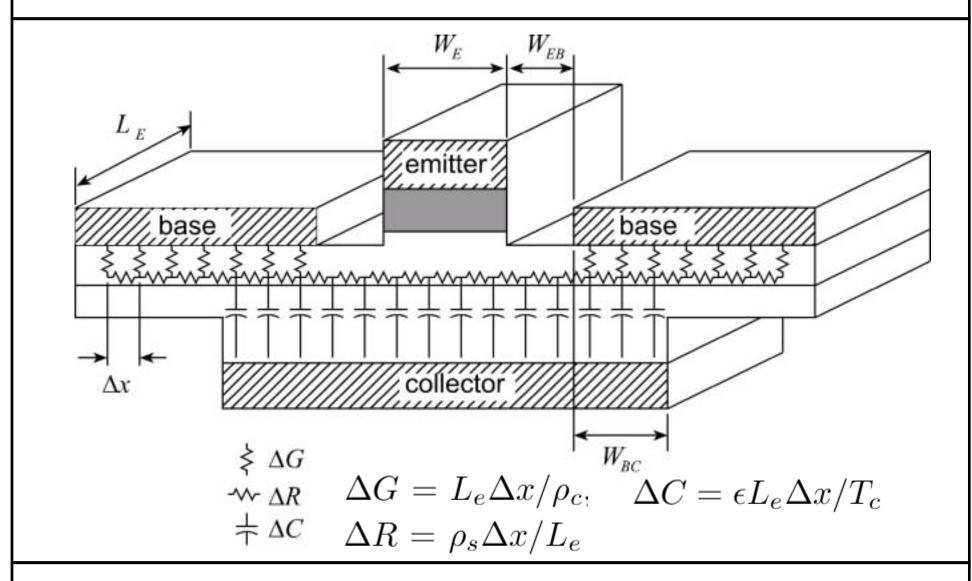

#### **Base-Collector Distributed Model: exact**

This "mesh model" can be entered into a microwave circuit simulator (e.g. Agilent ADS) to predict  $f_{\text{max}}$ , etc.

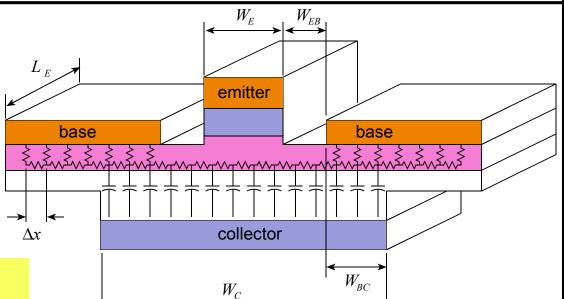

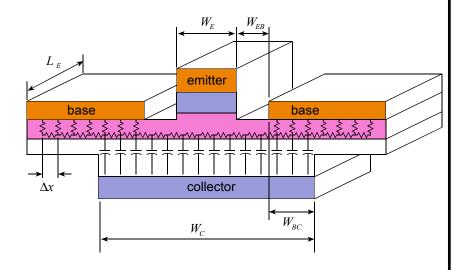

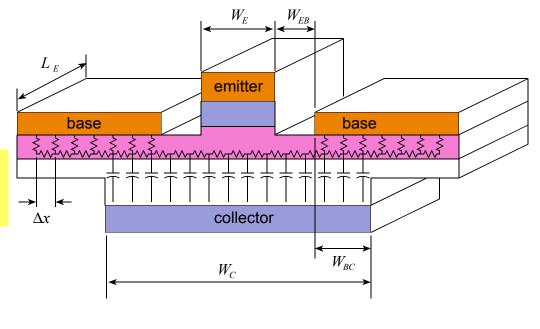

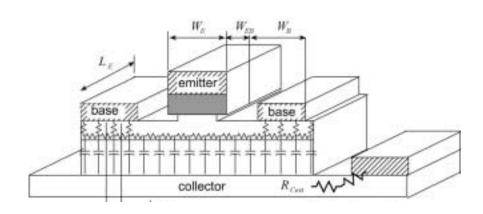

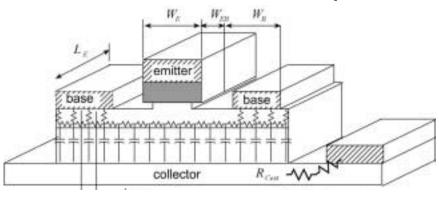

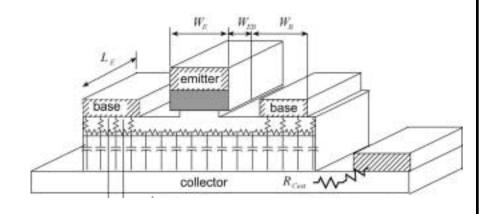

#### Components of Rbb and Ccb

#### Components of base spreading resistance

$$R_{bb} = R_{cont} + R_{gap} + R_{spread}$$

$$R_{cont} = \sqrt{\rho_s \rho_v} / 2L_e$$

$$R_{gap} = \rho_s W_{eb} / 2L_e$$

$$R_{spread} = \rho_s W_e / 12L_e.$$

With submicron emitters (or with  $\sim$  1E20 base doping)  $R_{bb}$  is dominated by  $R_{contact}$  and  $R_{gap}$ .

Given that emitter area  $A_E = L_E W_E$  is fixed:

decreased emitter width  $W_E$  results in increased emitter length  $L_E$ .

$\Rightarrow$  Low  $R_{bb}$  is obtained with narrow emitters, even with negligible  $R_{spread}$ .

#### Typical base parameters

4·10<sup>19</sup>/cm<sup>3</sup> Be - doped InGaAs base, 52 meV grading, 400 A thickness

$$\rho_{\rm s} = 750 \, {\rm Ohms/square}$$

,  $\rho_{\rm c} = 100 \, {\rm Ohm} - \mu {\rm m}^2$ ,  $\tau_b \approx 170 \, {\rm fs}$ ,  $D_n \approx 40 \, {\rm cm}^2 / {\rm s}$

7·10<sup>19</sup>/cm<sup>3</sup> C-doped InGaAs base, 52 meV (doping) grading, 300 A thickness

$$\rho_{\rm s} = 700 \, {\rm Ohms/square}$$

,  $\rho_{\rm c} < 10 \, {\rm Ohm} - \mu {\rm m}^2$ ,  $\tau_b \approx 100 \, {\rm fs}$ ,  $D_n \approx 40 \, {\rm cm}^2 \, / \, {\rm s}$

8·10<sup>19</sup>/cm<sup>3</sup> C-doped GaAsSb base, ?? meV grading, 250 A thickness

$$\rho_s = 1000 \text{ Ohms/square}$$

,  $\rho_c \approx 20 \text{ Ohm} - \mu \text{m}^2$ ,  $\tau_b \approx 150 - 200 \text{ fs}$ ,  $D_n \approx 20 \text{ cm}^2 / \text{s}$  (Dvorak)

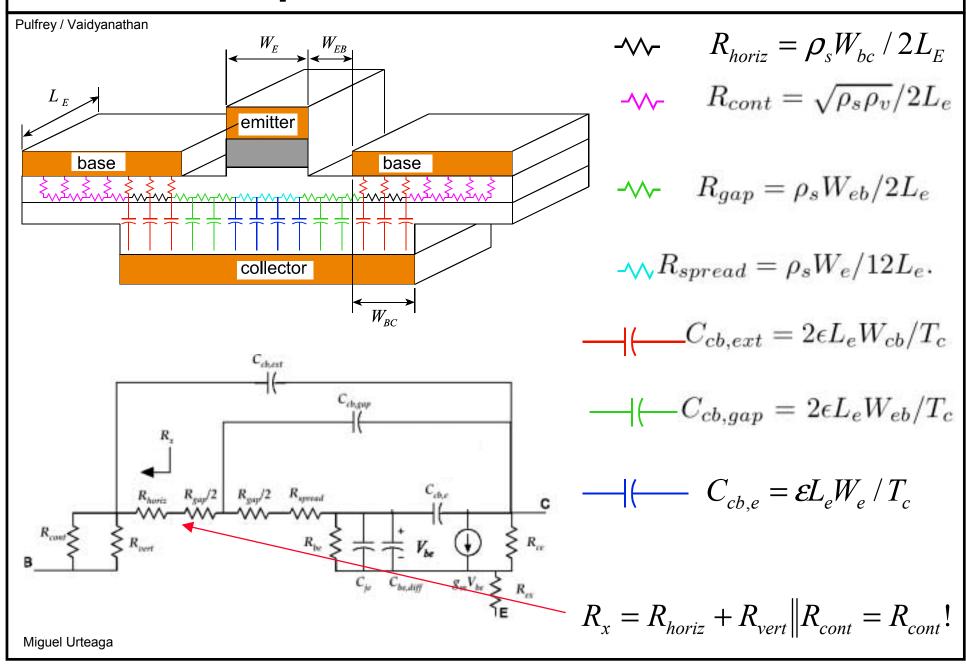

#### Pulfrey / Vaidyanathan fmax model

Pulfrey / Vaidyanathan

$$f_{max} = \sqrt{\frac{f_{\tau}'}{8\pi\tau_{cb}}},$$

$$\frac{1}{2\pi f_{\tau}'} = \tau_b + \tau_c + \frac{kT}{qI_c} (C_{je} + C_{cb}),$$

$$\tau_{cb} = C_{cb,e} \left( R_{cont} + R_{gap} + R_{spread} \right)$$

$$+ C_{cb,gap} \left( R_{cont} + R_{gap} / 2 \right)$$

$$+ \left( R_{cont} || R_{vert} \right) C_{cb,ext}$$

Note that the external capacitance  $C_{cb,ext}$  is charged through a relatively low resistance, less than  $R_{vert}$ .

$$C_{cb,ext}(R_{cont}||R_{vert}) < C_{cb,ext}R_{vert}$$

$$= \frac{\mathcal{E}}{T_c} \frac{1}{\rho_{contact}}$$

...the associated charging time is relatively small

$C_{cb,ext}$  has moderate effect upon  $f_{\max}$  , but big impact upon digital and analog speed

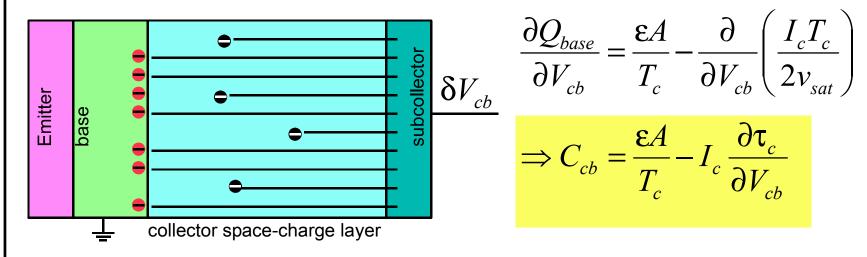

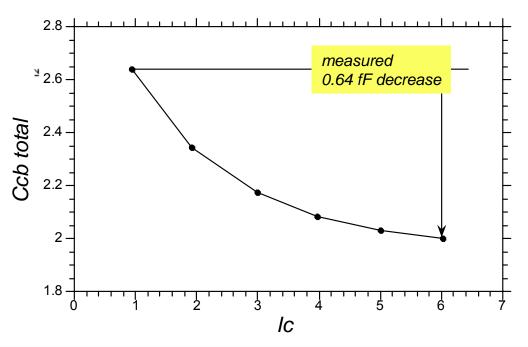

#### C<sub>cb</sub> Cancellation by Collector Space-Charge

Moll & Camnitz, Betser and Ritter

Collector space charge screens field, Increasing voltage decreases velocity,

- → modulates collector space-charge

- → offsets modulation of base charge

- → Ccb is reduced

Even if you don't care about fmax, the effect can confuse HBT model extraction

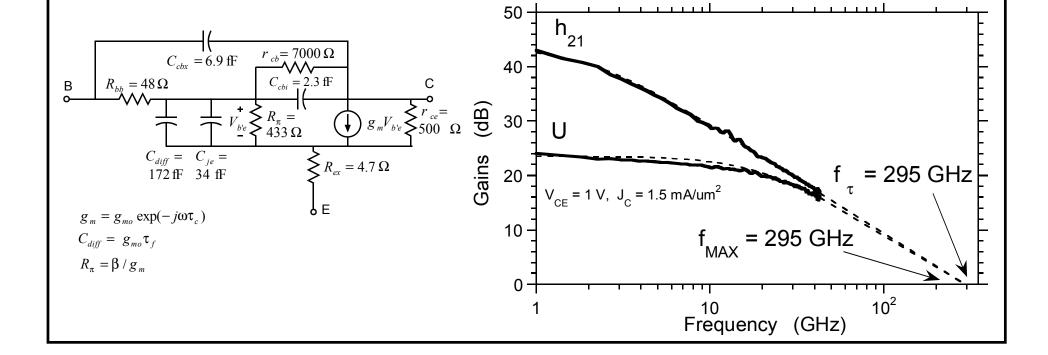

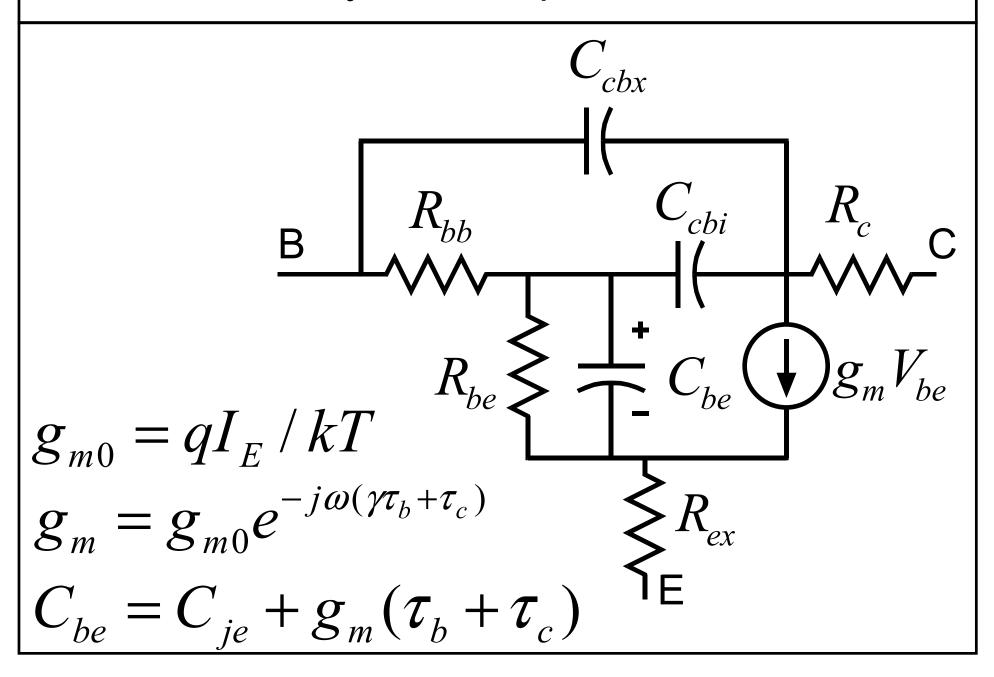

# equivalent circuit model

#### Transistor Hybrid-Pi equivalent circuit model

#### Comments regarding the Hybrid-Pi model

The common - base (T) model directly models frequency - dependent transport

The hybrid - pi model results from a fit to the T to first order in  $\omega$ .

The capacitance  $C_{be,diff}$  models the effect of  $(\tau_b + \tau_c)$  on input impedance

The  $g_m$  generator nevertheless also requires an associated  $\sim (0.2 \cdot \tau_b + \tau_c)$  delay (important in fast IC design)

$R_{bb}C_{cbi}$  and  $C_{cbx}$  represent fits to the distributed RC base - collector network

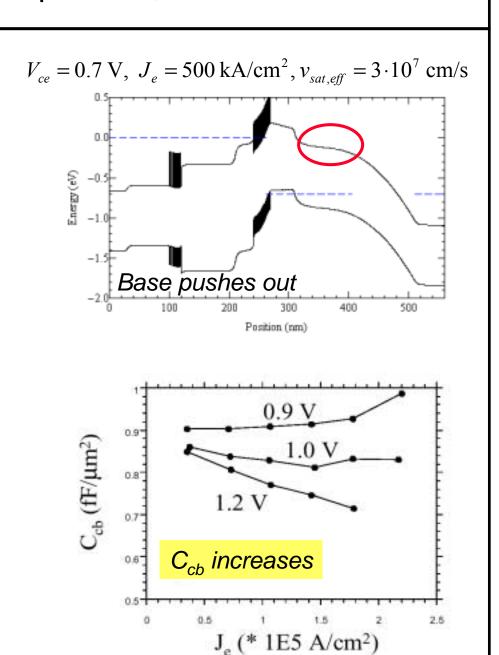

## Collector field-screening (Kirk Effect)

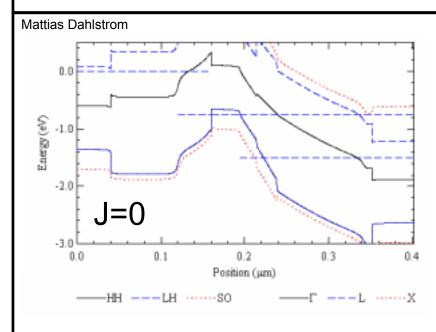

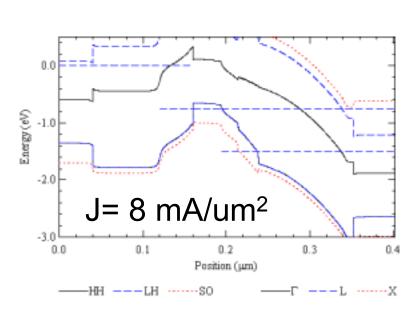

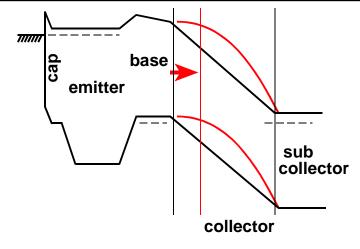

#### Kirk effect in DHBTs: not base pushout, but current-blocking

$$\frac{d^2\phi}{dx^2} = \frac{\rho}{\varepsilon} = \frac{qN_d - J/v}{\varepsilon}$$

Bandbending under high J and low  $V_{ce}$  results in current blocking

$\Rightarrow$  decrease in  $\beta$  and  $f_{\tau}$

$$V_{ce} = 0.7 \text{ V}, J_e = 1000 \text{ kA/cm}^2, v_{sat,eff} = 4 \cdot 10^7 \text{ cm/s}$$

$V_{ce} = 1.2 \text{ V}, J_e = 1000 \text{ kA/cm}^2, v_{sat,eff} = 4 \cdot 10^7 \text{ cm/s}$

$$V_{ce} = 0.7 \text{ V}, J_e = 0 \text{ kA/cm}^2, v_{sat,eff} = 4.10^7 \text{ cm/s}$$

$$V_{ce} = 1.2 \text{ V}, J_e = 1000 \text{ kA/cm}^2, v_{sat,eff} = 4.10^7 \text{ cm/s}$$

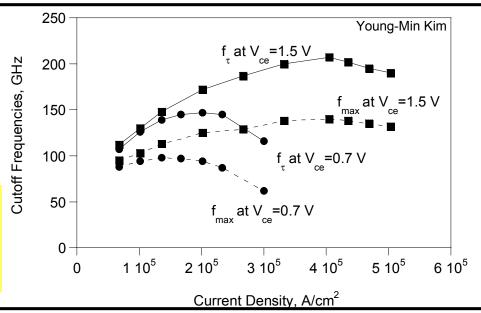

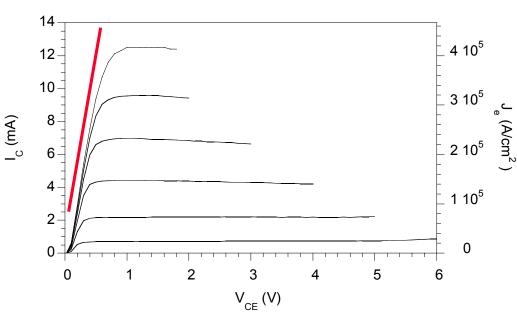

#### Kirk effect in DHBTs

Decrease in  $f_{\tau}$  and  $f_{\text{max}}$  at lower JKirk - effect threshold increases with increased  $V_{ce}$

$$J_{\text{max}} = 2\varepsilon v_{sat} (V_{cb} + V_{cb,\text{min}} + 2\phi) / T_c^2$$

$$\cong 2\varepsilon v_{sat} (V_{ce} + V_{ce,\text{min}}) / T_c^2$$

Increase in  $V_{ce,sat}$  with increased J

$$\frac{dV_{ce}}{dI_c} = R_{\text{space-charge}} = \frac{T_c^2}{2\varepsilon v_{sat} A_{\text{effective}}}$$

where the effective collector current flux area is

$$A_{effective} \approx L_E (W_E + 2T_C)$$

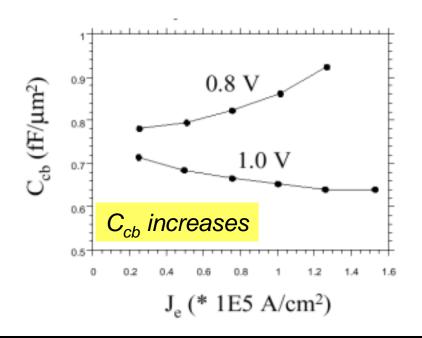

#### Kirk effect in SHBTs: base pushout, increased Ccb

Base pushes out.

Holes compensate electrons

$C_{cb}$  increases.

#### Kirk effect with Nonuniform Collector Electron Velocity

From transit time analysis,

$$\tau_{\rm c} = \int_{0}^{T_c} \frac{(1 - x / T_c)}{v(x)} dx \equiv \frac{T_c}{2v_{eff}}$$

$\tau_{\rm c}$  and  $v_{\it eff}$  are more sensitive to velocity near base.

Kirk effect with uniform collector velocity:

$$J_{\text{max}} = 2\varepsilon v_{sat} (V_{cb} + V_{cb,\text{min}} + 2\phi) / T_c^2$$

$$\approx 2\varepsilon v_{sat} (V_{ce} + V_{ce,\text{min}}) / T_c^2$$

Kirk effect with NONuniform collector velocity:

$$J_{\text{max}} = 2\varepsilon v_{\text{eff}} (V_{cb} + V_{cb,\text{min}} + 2\phi) / T_c^2$$

$$\approx 2\varepsilon v_{\text{eff}} (V_{ce} + V_{ce,\text{min}}) / T_c^2$$

Nonuniform collector electron velocity doesn't profoundly change Kirk effect...

## transistor scaling theory

Rodwell

#### HBT scaling: layer thicknesses

2:1 improved device speed: keep G's, R's, I's, V's constant, reduce 2:1 all C's,  $\mathcal{T}$  's

reduce  $T_b$  by  $\sqrt{2:1}$

$\rightarrow \tau_{\rm b}$  improved 2:1

reduce  $T_c$  by 2:1

$\rightarrow \tau_{\rm c}$  improved 2:1

note that Ccb has been doubled ..we had wanted it 2:1 smaller

$$\tau_b \cong T_b^2 / 2D_n$$

$$au_b \cong T_c / 2v_{sat}$$

Assume

$$W_C \sim W_E$$

Rodwell

#### HBT scaling: lithographic dimensions

2:1 improved device speed: keep G's, R's, I's, V's constant, reduce 2:1 all C's,  $\mathcal{T}$  's

Base Resistance  $R_{bb}$  must remain constant  $\rightarrow L_e$  must remain  $\sim$  constant

$$R_{bb} = R_{gap} + R_{spread} + R_{contact}$$

$$\cong R_{contact}$$

$$= \sqrt{\rho_{sheet} \rho_{c,vertical}} / 2L_{E}$$

Ccb/Area has been doubled

..we had wanted it 2:1 smaller

...must make area=L<sub>e</sub>W<sub>e</sub> 4:1 smaller

$\rightarrow$  must make  $W_e$  &  $W_c$  4:1 smaller

reduce collector width 4:1 reduce emitter width 4:1 keep emitter length constant

Assume  $W_C \sim W_E$

#### HBT scaling: emitter resistivity, current density

2:1 improved device speed: keep G's, R's, I's, V's constant, reduce 2:1 all C's,  $\mathcal T$  's

Rodwell

Emitter Resistance  $R_{\rm ex}$  must remain constant but emitter area= $L_{\rm e}W_{\rm e}$  is 4:1 smaller resistance per unit area must be 4:1 smaller

Assume  $W_C \sim W_E$

Collector current must remain constant but emitter area= $L_eW_e$  is 4:1 smaller and collector area= $L_cW_c$  is 4:1 smaller current density must be 4:1 larger

increase current density 4:1 reduce emitter resistivity 4:1

Rodwell

#### Scaling Laws, Collector Current Density, C<sub>cb</sub> charging time

Collector Field Collapse (Kirk Effect)

$$V_{cb} + \phi > + (J/v_{sat} - qN_d)(T_c^2/2\varepsilon)$$

Collector Depletion Layer Collapse

$$V_{cb,\text{min}} + \phi > +(qN_d)(T_c^2/2\varepsilon)$$

$$\Rightarrow J_{\text{max}} = 2\varepsilon v_{sat} (V_{cb} + V_{cb,\text{min}} + 2\phi) / T_c^2$$

Note that  $V_{be} \cong \phi$ , hence  $(V_{cb} + \phi) \cong V_{ce}$

$$\frac{C_{cb}\Delta V_{LOGIC}/I_{C}}{(V_{CE}+V_{CE,min})} \left(\frac{A_{collector}}{A_{emitter}}\right) \left(\frac{T_{C}}{2v_{sat}}\right)$$

Collector capacitance charging time is reduced by **thinning the collector** while increasing current

#### Scaling Laws for fast HBTs

#### for x 2 improvement of all parasitics:

f<sub>t</sub>, f<sub>max</sub>, logic speed...

base √2: 1 thinner

collector 2:1 thinner

emitter, collector junctions 4:1 narrower

current density 4:1 higher

emitter Ohmic 4:1 less resistive

#### Challenges with Scaling:

#### Collector

mesa HBT: collector under base Ohmics.

Base Ohmics must be one transfer length

sets minimum size for collector

#### **Emitter Ohmic:**

hard to improve...how?

#### **Current Density:**

dissipation, reliability

#### Loss of breakdown

avalanche Vbr never less than collector Egap

(1.12 V for Si, 1.4 V for InP)

....sufficient for logic, insufficient for power

## digital circuit speed

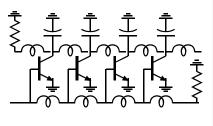

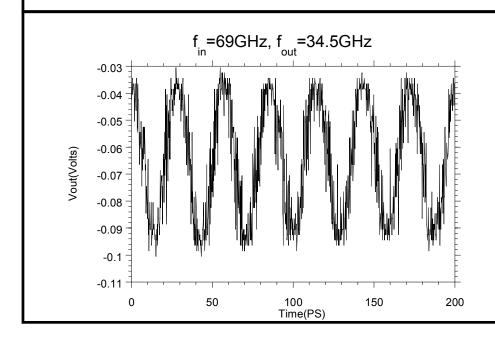

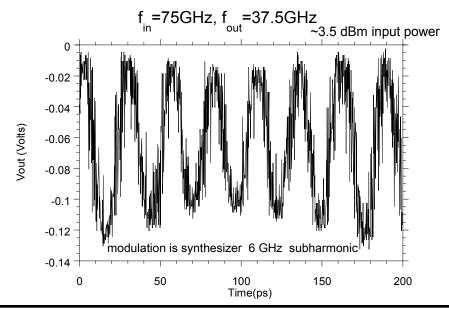

### 75 GHz HBT master-slave latch connected as Static frequency divider

JCSB

Thomas Mathew

Michelle Lee

Hwe-Jong Kim

#### technology:

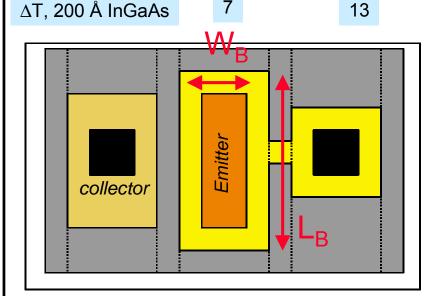

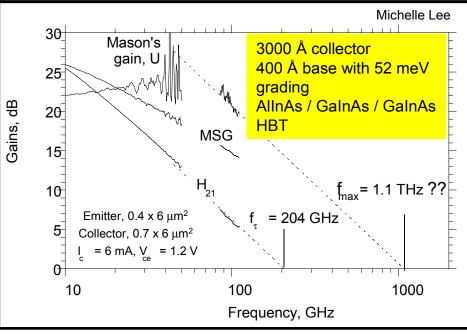

400 Å base, 2000 Å collector HBT

- 0.7 um mask (0.6 um junction) x 12 um emitters

- 1.5 um mask (1.4 um junction) x 14 um collectors

#### transistor performance:

1.8×10<sup>5</sup> A/cm<sup>2</sup> operation, 180 GHz ft, 260 GHz fmax collector/ emitter junction area ratio: 2.7:1 (low)

Ccb/lc: 0.9 ps/V Rex\*I=54 mV

simulations: 95 GHz clock rate in SPICE

#### What do we need for fast logic?

#### Gate Delay Determined by:

Depletion capacitance charging through the logic swing

$$\left(\frac{\Delta V_{LOGIC}}{I_{C}}\right) \left(C_{cb} + C_{be, \text{depletion}}\right)$$

Depletion capacitance charging through the base resistance

$$R_{\rm bb} \left( C_{cb} + C_{be, \rm depletion} \right)$$

Supplying base + collector stored charge through the base resistance

$$R_{\rm bb} ( au_b + au_c) \left( rac{I_C}{\Delta V_{LOGIC}}

ight)$$

The logic swing must be at least

$$\Delta V_{LOGIC} > 6 \left( \frac{kT}{q} + R_{ex} I_c \right)$$

Neither  $f_{\tau}$  nor  $f_{max}$  predicts digital speed

$C_{cb}\Delta V_{logic}/I_c$  is very important

- → collector capacitance reduction is critical

- → increased III-V current density is critical

$\rm R_{\rm ex}~$  must be very low for low  $\Delta \rm V_{\rm logic}$  at high  $\rm J_{c}$

InP:  $R_{bb}$ ,  $(\tau_b + \tau_c)$ , are already low, must remain so

#### What HBT parameters determine logic speed?

|          | Cje   | Ccbx | Cebi  | (τb+τc) ( I/ΔV) | total  |

|----------|-------|------|-------|-----------------|--------|

| ΔV/ I    | 33.5% | 6.7% | 27.8% |                 | 68.4%  |

| ΔV/ I    |       |      |       | 12.3%           | 12.3%  |

| (kT/q) I | 1.4%  | 0.1% | 0.4%  | 0.5%            | 2.5%   |

| Rex      | -1.3% | 0.1% | 0.3%  | 0.9%            | 0.1%   |

| Rbb      | 10.2% |      | 2.8%  | 3.7%            | 16.7%  |

| total    | 43.8% | 6.8% | 31.3% | 17.5%           | 100.0% |

|          |       | 3    | 8%    |                 |        |

Sorting Delays by capacitances:

44% charging  $C_{je}$ , 38% charging  $C_{cb}$ , only 18% charging  $C_{diff}$  (e.g.  $\tau_b + \tau_c$ )

Sorting Delays by resistances and transit times:

68% from

$$\Delta V_{\text{logic}} / I_c$$

, 12% from  $(\tau_b + \tau_c)$ , 17% from  $R_{bb}$

$R_{ex}$  has very strong indirect effect, as  $\Delta V_{logic} > 6 \bullet (kT/q + I_C R_{ex})$

#### Caveats:

assumes a specific UCSB InP HBT (0.7 um emitter, 1.2 um collector 2kÅ thick, 400 Å base, 1.5E5 A/cm^2) ignores interconnect capacitance and delay, which is very significant

#### Logic Speed

| • •            | $c_{je}$ | $c_{cbx}$ | $c_{cbi}$ | $	au_f J/\Delta V_L$ |

|----------------|----------|-----------|-----------|----------------------|

| $\Delta V_L/J$ | 1        | 6         | 6         | 1                    |

| kT/qJ          | 0.5      | 1         | 1         | 0.5                  |

| $ ho_e$        | -0.25    | 0.5       | 0.5       | 0.5                  |

| $r_{bb}$       | 0.5      | 0         | 1         | 0.5                  |

Approximate delay coefficients  $a_{ij}$  for an ECL master-slave flip-flop, found by hand analysis. Gate delay is of the form  $T_{gate} = 1/2 f_{clock,max} = \sum a_{ij} r_i c_j$ , where  $f_{clock}$  is the maximum clock frequency. The minimum logic voltage swing is  $\Delta V_{LOGIC} > 6(kT/q + J\rho_{ex})$

Caveat: ignores interconnect capacitance and delay, which is very significant

#### Logic Speed: definition of terms

$c_{ie}$ : emitter base depletion capacitance per unit emitter area

$c_{cbi}$ : intrinsic collector base capacitance per unit emitter area

$c_{cbx}$ : extrinsic collector base capacitance per unit emitter area

$\tau_f$ : sum of base and collector transit times

J: emitter current per unit emitter area

$\Delta V_{LOGIC}$ : logic voltage swing

$r_{bb}$ : base resistance times emitter area (e.g. "per - area"  $R_{bb}$ )

$\rho_{ex}$ : emitter resistance times emitter area (e.g. "per - area"  $R_{ex}$ )

#### Why isn't base+collector transit time so important?

**Under Small-Signal Operation:**

$$\delta Q_{\text{base}} = (\tau_b + \tau_c) \delta I_C = (\tau_b + \tau_c) \frac{dI_C}{dV_{be}} \delta V_{be} = \frac{(\tau_b + \tau_c)I_C}{kT/q} \delta V_{be}$$

Under Large - Signal Operation:

$$\Delta Q_{\text{base}} = (\tau_b + \tau_c)I_C = \frac{(\tau_b + \tau_c)I_{dc}}{\Delta V_{LOGIC}} \Delta V_{LOGIC}$$

Large-signal diffusion capacitance reduced by ratio of

$$\left(\frac{\Delta V_{LOGIC}}{kT/q}\right)$$

, which is ~ 10:1

Depletion capacitances see no such reduction

## roadmap

#### Technology Roadmaps for 40 / 80 / 160 Gb/s

| Parameter                                             | Transferred-                        | Mesa HBT                            | Mesa HBT                            | Mesa HBT                            |

|-------------------------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

|                                                       | Substrate HBT                       | Generation 1                        | Generation 2                        | Generation 3                        |

| Predicted MS-DFF                                      | 93 GHz                              | 62 GHz                              | 125 GHz                             | 237 GHz                             |

| speed (no interconnects)                              |                                     |                                     |                                     |                                     |

| Observed speed                                        | 75 GHz                              |                                     |                                     |                                     |

| Emitter Junction Width                                | 0.6 μm                              | 1 μm                                | 0.8 μm                              | 0.2 μm                              |

| Parasitic Resistivity                                 | 30 Ω-μm²                            | 50 Ω-μm²                            | 20 Ω-μm²                            | 5 Ω-μm²                             |

| Base Thickness                                        | 400 Å                               | 400Å                                | 300Å                                | 250Å                                |

| Doping                                                | 4 10 <sup>19</sup> /cm <sup>2</sup> | 5 10 <sup>19</sup> /cm <sup>2</sup> | 5 10 <sup>19</sup> /cm <sup>2</sup> | 5 10 <sup>19</sup> /cm <sup>2</sup> |

| Sheet resistance                                      | 750 Ω                               | 750 Ω                               | 700 Ω                               | 700 Ω                               |

| Contact resistance                                    | 150 Ω-μm <sup>2</sup>               | 150 Ω-μm <sup>2</sup>               | 20 Ω-μm²                            | 10 Ω-μm²                            |

| Collector Width                                       | 1.5 μm                              | 3 μm                                | 1.6 μm                              | 0.4 μm                              |

| Collector Thickness                                   | 2000 Å                              | 3000 Å                              | 2000 Å                              | 1000 Å                              |

| Current Density                                       | 1.8 mA/μm <sup>2</sup>              | 1 mA/μm <sup>2</sup>                | $2.3 \text{ mA/}\mu\text{m}^2$      | 9.3 mA/μm <sup>2</sup>              |

| A <sub>collector</sub> /A <sub>emitter</sub>          | 2.5                                 | 4.55                                | 2.6                                 | 2.6                                 |

| $f_{\tau}$                                            | 180                                 | 170                                 | 260                                 | 500                                 |

| $f_{	ext{max}}$                                       | 220                                 | 170                                 | 440                                 | 1000                                |

| $C_{cb}$ / $I_c$                                      | 0.8 ps/V                            | 1.7 ps/V                            | 0.63 ps/V                           | 0.31 ps/V                           |

| $C_{cb}\Delta V_{\mathrm{logic}}$ / $I_{c}$           | 0.24 ps                             | 0.5 ps                              | 0.19 ps                             | 0.093 ps                            |

| $R_{bb}$ /( $\Delta V_{ m logic}$ / $I_c$ )           | 0.9                                 | 0.8                                 | 0.65                                | 0.52                                |

| $C_{je} \left( \Delta V_{	ext{logic}} / I_{C}  ight)$ | 0.9 ps                              | 1.7 ps                              | 0.72 ps                             | 0.18 ps                             |

| $R_{ex} / (\Delta V_{	ext{logic}} / I_c)$             | 0.12                                | 0.1                                 | 0.15                                | 0.15                                |

#### Technology Roadmaps for 40 / 80 / 160 Gb/s

#### 80 Gb/s technology node:

Change from 40 Gb/s does not fully follow scaling laws. Why? Lithographic scaling eased by carbon base doping. Current density scaling eased by reduced excess collector area.

#### 160 Gb/s technology node:

Direct application of scaling laws.

Aggressive current density and lithographic scaling required.

If further improved base contact resistance  $\rightarrow$  relax lithographic scaling

Further reduce  $A_{collector}/A_{emitter}$  ratio  $\rightarrow$  relax current density scaling

...note that  $A_{collector}/A_{emitter}$  < 2.5 looks hard at deep submicron.

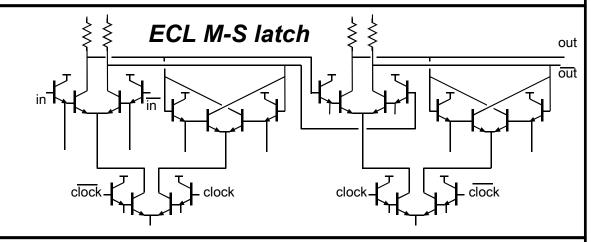

## device structures

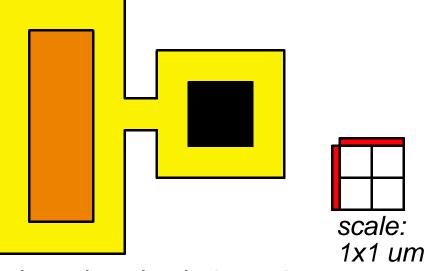

#### Narrow-Mesa HBTs: high $f_{\tau}$ & $f_{max}$ if high base doping

#### Low Ccb HBT structures

Extremely high demonstrated fmax 75 GHz (record) static frequency dividers

Too low yield for manufacturing (?)

#### undercut-collector

Pursued by several research groups

Also has uncertain yield at submicron geometries

#### Narrow-mesa with ~1E20 carbon-doped base

The conservative device structure

Yet, I assert that even this device is not viable of mass manufacturing if > 3000 transistors per IC are sought

## yield and fabrication

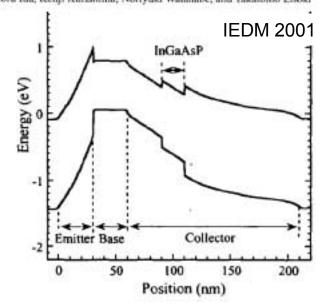

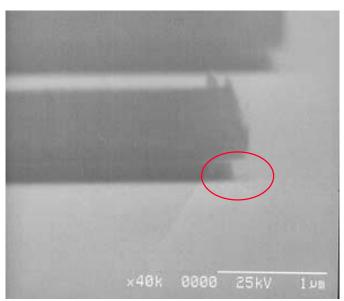

## InP HBT limits to yield: non-planar process

S.I. substrate

Yield degrades as emitters are scaled to submicron dimensions

InP

Front and side views

InAlAs

Front and side views

Smaller emitters  $\rightarrow$  lower yield. Need better fabrication process

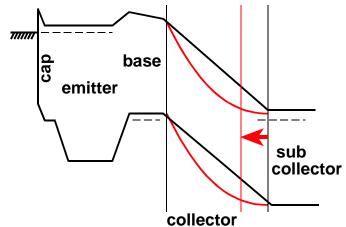

## InP vs. SiGe

## **Digital**

InP has slightly higher speed, much less power InP can't meet integration scales of many complex fast ICs

## Analog:

Combined InP speed and breakdown are key advantages

mm-wave wireless / RF (60 GHz, etc)

No significant market yet

InP HBT could be strong contender (fast and cheap)

Fast, high-yield InP HBT IC processes are critically needed

## InP vs. SiGe

III-V literature, III-V research community: large inherent advantages in transport parameters over Si research focused on transport physics, poorly tied to circuit design

- → devices not well-tuned for circuits, poor parasitic reduction

- → university-like fabrication, low yield, low scales of integration

Silicon research community focused on **SCALING**, closely tied to **circuit** design, focus on **YEILD** strong **extrinsic parasitic reduction** result: very good SiGe HBT digital circuit speed, large fast ICs

InP HBT has fundamental advantages which will allow it to scale beyond SiGe HBT scaling limits, but must address:

yield: Silicon-like planar implanted / regrowth processes speed: device scaling informed by understanding of circuit design

## InP vs. Si/SiGe HBTs: materials vs. scaling advantages

Good:

Narrow emitter: 0.18 um

High current density: 10 mA/um<sup>2</sup>

Large emitter contact: low resistance

Polysilicon base contact: low resistance

SiO2 trenches: small collector capacitance

Planar device: high yield

Bad:

High base sheet resistance,

Low electron velocity, low breakdown limits scaling.

Equal speed at 5x smaller scaling.

Loss of breakdown may soon slow scaling

### Good:

20x lower base sheet resistance,5 x higher electron velocity,4x higher breakdown-at same ft.

### Bad:

Presently only scaled to ~ 1 um Archaic mesa fabrication process:

large emitters, poor emitter contact:

low current density: 2 mA/um<sup>2</sup> high collector capacitance

nonplanar device : low yield

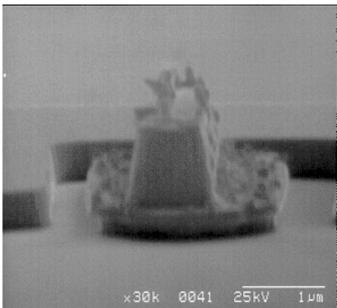

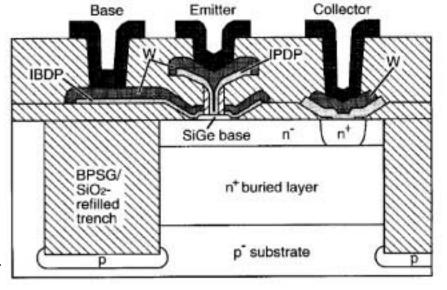

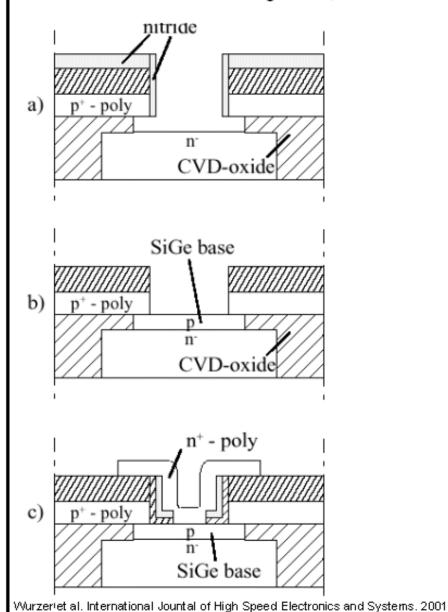

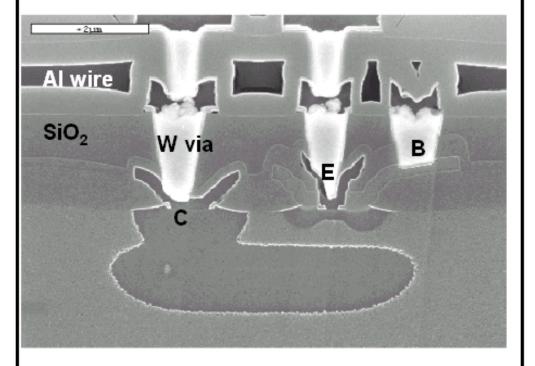

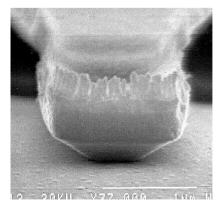

## SiGe HBTs high yield: regrown emitter, planar process, VLSI interconnects

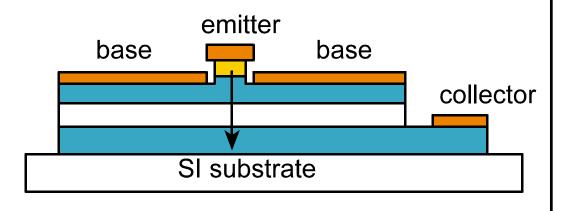

## 0.2 um emitters are regrown, not etched

Transistor is planar, interconnects are standard for VLSI (W/ Al with SiO<sub>2</sub>)

Wurzer et al. International Jountal of High Speed Electronics and Systems, 2001

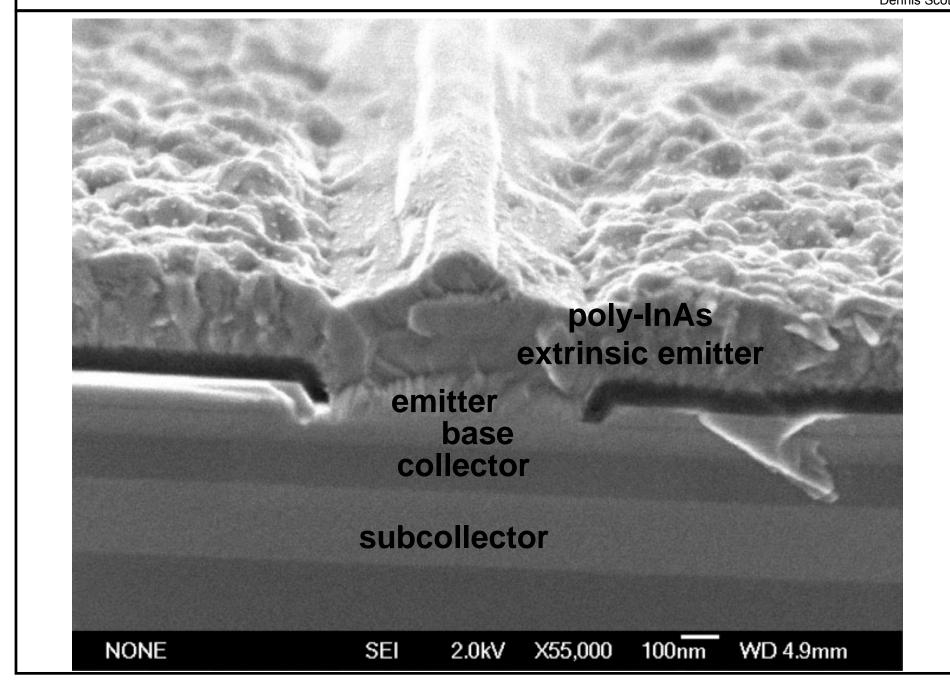

ONR InAlAs/InGaAs/InP DHBT with polycrystalline extrinsic emitter regrowth.

UCSB

Dennis Scott

## thermal resistance and thermal runaway

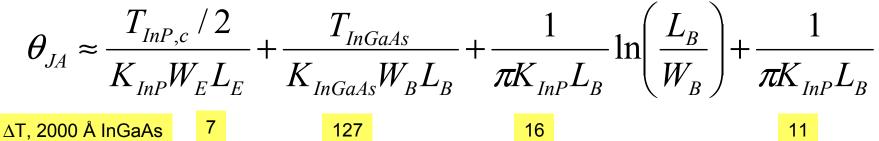

## Thermal resistance and effect of subcollector

## Approximation:

InGaAs dominates thermal resistance → heat flows through InGaAs in area equal base mesa (excluding pad)

InGaAs subcollector

$W_E = 0.5 \,\mu\text{m}, L_E = 3 \,\mu\text{m}, W_B = 0.7 \,\mu\text{m}, L_E = 3.25 \,\mu\text{m},$  $J_E = 4 \text{ mA}/\mu\text{m}^2$ ,  $V_{CE} = 1.2 \text{ V}$  $K_{InGaAs} = 5 \text{ W/k} - \text{m}$   $K_{InP} = 68 \text{ W/k} - \text{m}$

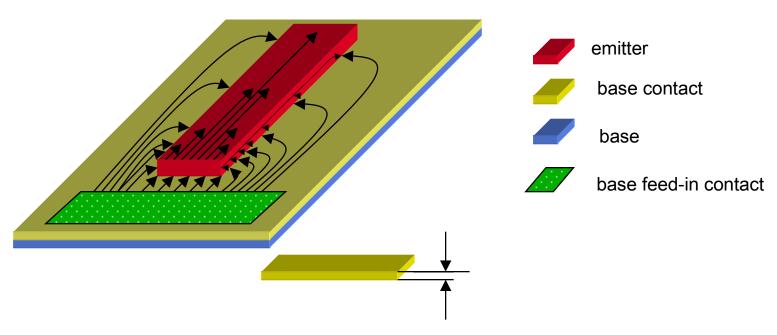

## Poor performance observed in multi-finger DHBT

Yun Wei

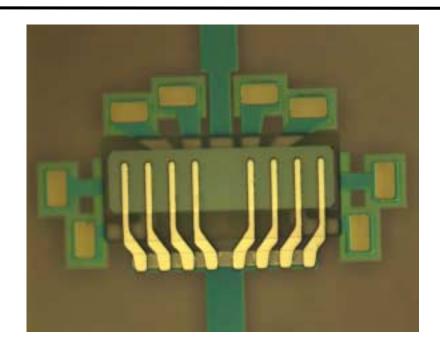

8 finger common emitter DHBT Emitter size: 16 um x 1 um Ballast resistor (design):9 Ohm/finger

current hogging observed fmax also low due to high base feed resistance

## Restrictions on DHBT sizing: distributed base feed resistance

Yun Wei

Self-aligned base contact thickness= $0.08 \mu m$  Leads to feed sheet resistance:

$$\rho$$

= 0.3 Ω/ $\square$  restricts emitter length to ~15 μm

Excess Rbb, hence reduced  $f_{max}$  (big HBT has big  $C_{cb}$ , small  $R_{bb}$ , hence even small excess  $R_{bb}$  reduces  $f_{max}$ )

## DHBT thermal stability: multiple emitter fingers

Yun Wei

Assume initial temperature difference  $\delta T$  between 2 fingers

$$\frac{dV_{be}}{dT} = -1.1 \,\text{mV/K} \text{ at constant } I_c$$

$$\delta T \Rightarrow \delta V_{be} = \frac{dV_{be}}{dT} \delta T \Rightarrow \delta I_{C} = \frac{1}{R_{ex} + R_{ballast} + kT/qI_{E}} \delta V_{be}$$

$$\Rightarrow \delta P = V_{CE} \delta I_{C} \Rightarrow \delta T = \theta_{JA} \delta P$$

Unstable unless

$$K_{\text{thermal stability}} = \left| \frac{dV_{be}}{dT} \right| \frac{V_{CE}\theta_{JA}}{R_{ex} + R_{ballast} + kT/qI_E} < 1$$

**ARO** Thermal runaway within a finger **MURI** Yun Wei emitter emperature With long emitter finger, current-crowding can occur within finger • Long finger: temperature can vary along length of emitter finger loss of strong thermal coupling •Temperature gradients along finger results in nonuniform current distribution center of stripe gets hotter  $\rightarrow$  carries more current  $\rightarrow$  gets hotter  $\rightarrow \dots$ Premature Kirk-effect-induced collapse in f<sub>t</sub>.

## **ARO** Current hogging observation: multi-finger DHBT UCSB **MURI** V\_DC SRC2 \_Probe \_Probe Probe2 \_Probe1 BJT\_NPN BJT\_NPN BJT\_NPN BJT\_NPN BJT1 BJT2 BJT3 BJT4 $I_DC$ 0.05 SRC1 0.04 0.03 0.02 0.01 0 0.5 2 1.5

W. Liu, H-F Chau, E. Beam III, "Thermal properties and thermal instabilities of InP-based heterojunction bipolar transistors", IEEE Transactions on Electron Devices, vol.43, (no.3), IEEE, March 1996. p.388-95.

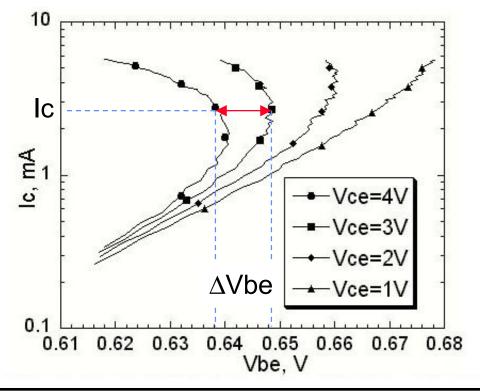

## Measuring DHBT thermal resistance

Yun Wei

$$\left. \delta V_{be} \right|_{\text{fixed } I_c} = \frac{dV_{be}}{dT} \frac{dT}{dP} \frac{dP}{dV_{CE}} \delta V_{CE} = \left( -1.1 \,\text{mV/K} \right) \cdot \theta_{JA} I_C \delta V_{CE}$$

$$\Rightarrow \theta_{JA} = \frac{dV_{be}}{dV_{CE}} \bigg|_{\text{fixed } I_c} \times \frac{1}{I_C(-1.1 \,\text{mV/K})}$$

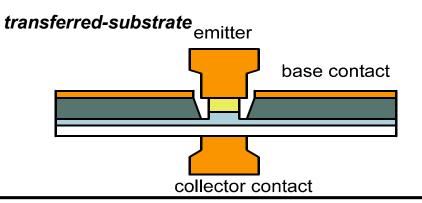

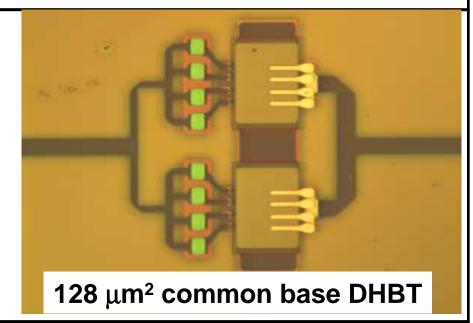

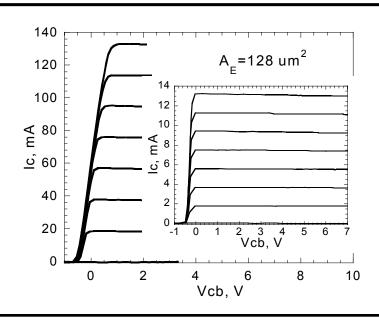

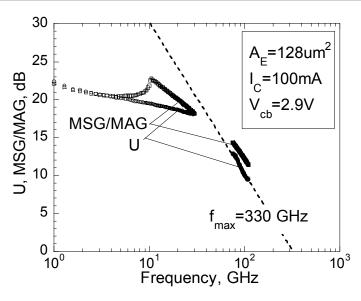

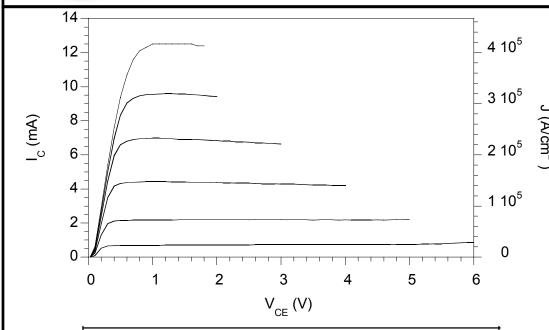

## Large current high breakdown voltage broadband InP DHBT

UCSB

Yun Wei

**Objectives:**  $f_{max}$ >300 GHz, *BVCEO*>6 V,

$J_{max}$ ~1x10<sup>5</sup> A/cm<sup>2</sup>

**Approach:** transferred-substrate multi-finger

InP DHBTs, HBT thermal analysis

Simulations: large signal HBT spice model

**Accomplishments:**

$f_{max}$ >330 GHz,  $Bv_{ce}$ >7 V,  $J_{max}$ >1x10<sup>5</sup> A/cm<sup>2</sup>

# On-wafer characterization of HBTs

accurate and otherwise

Miguel Urteaga

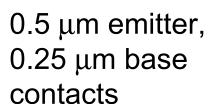

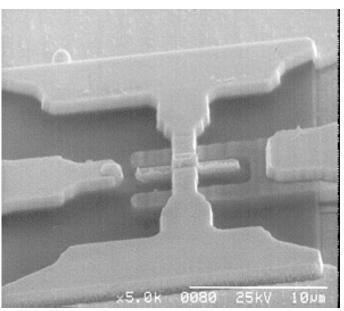

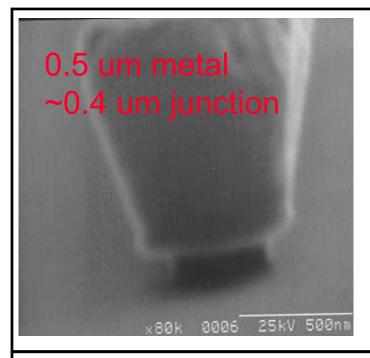

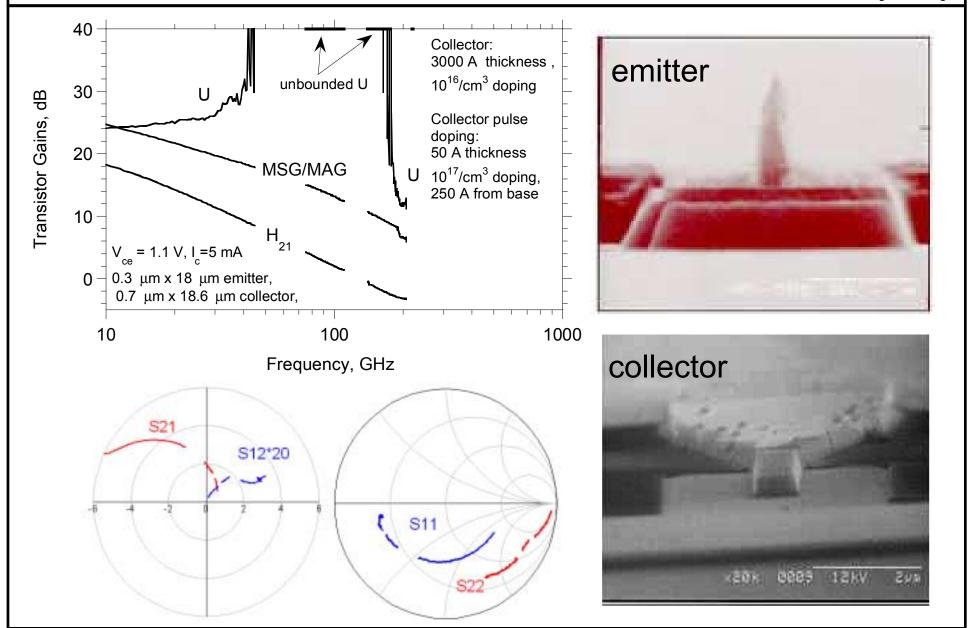

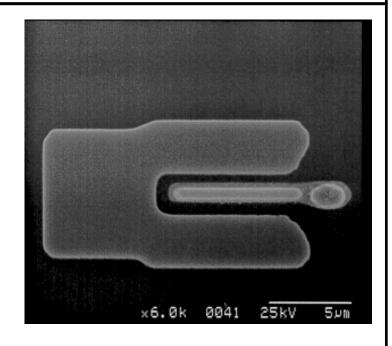

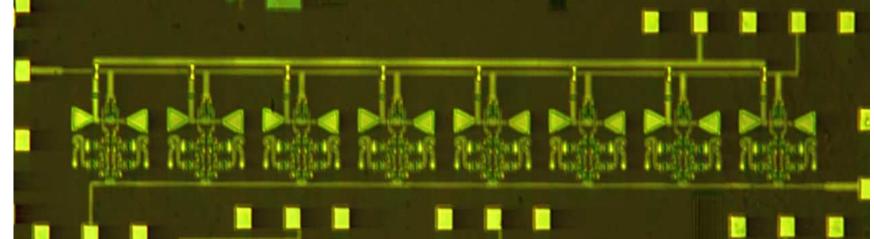

## Ultra-high $f_{max}$ Submicron HBTs

- Electron beam lithography used to define submicron emitters and collectors

- Minimum feature sizes

- $\Rightarrow$  0.2  $\mu$ m emitter stripe widths

- $\Rightarrow$  0.3 µm collector stripe widths

- Improved collector-to-emitter alignment using local alignment marks

- Aggressive scaling of transistor dimensions predicts progressive improvement of  $f_{max}$

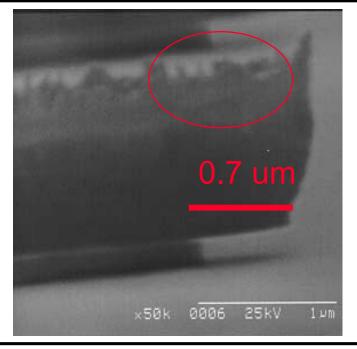

As we scale HBT to <0.4 um,  $f_{max}$  keeps increasing, measurements become *very* difficult

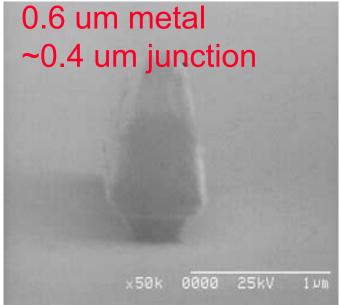

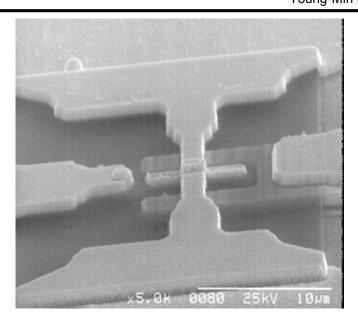

<mark>0.3 μm Emitter before polyimide planarization</mark>

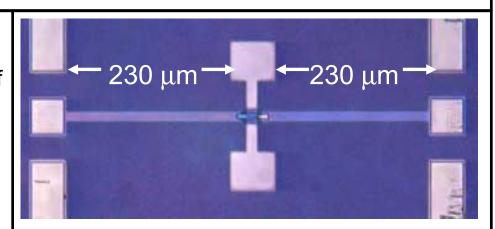

Submicron Collector Stripes (typical: 0.7 um collector)

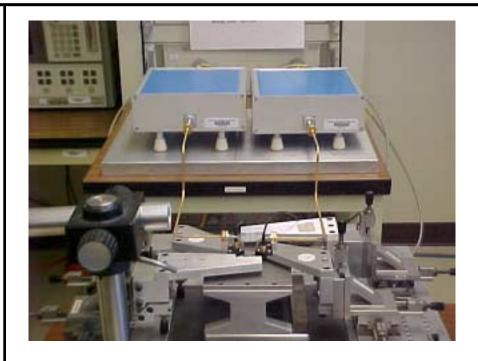

## 140-220 GHz On-Wafer Network Analysis

- HP8510C VNA,

Oleson Microwave Lab mm-wave

Extenders

- GGB Industries coplanar wafer probes

- •connection via short length of WR-5 waveguide

- Internal bias Tee's in probes for biasing active devices

- 75-110 GHz set-up is similar

UCSB 140-220 GHz VNA Measurement Set-up

Miguel Urteaga

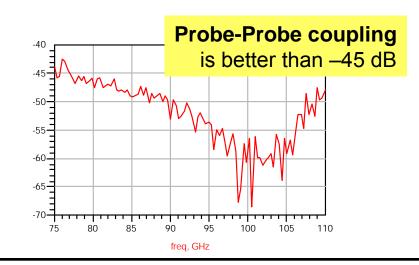

## Accurate Transistor Measurements Are Not Easy

- Submicron HBTs have very low C<sub>cb</sub> (< 3 fF)</li>

- Characterization requires accurate measure of very small S12

- Standard 12-term VNA calibrations do not correct S12 background error due to probe-to-probe coupling

## Solution

Embed transistors in sufficient length of transmission line to reduce coupling

Place calibration reference planes at transistor terminals

## **Line-Reflect-Line Calibration**

Standards easily realized on-wafer

Does not require accurate characterization of reflect standards

Characteristics of Line Standards are well controlled in transferred-substrate microstrip wiring environment

### Transistor in Embedded in LRL Test Structure

Corrupted 75-110 GHz measurements due to excessive probe-to-probe coupling

Miguel Urteaga

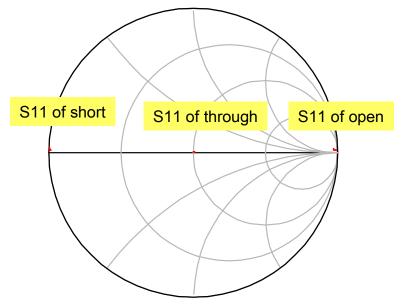

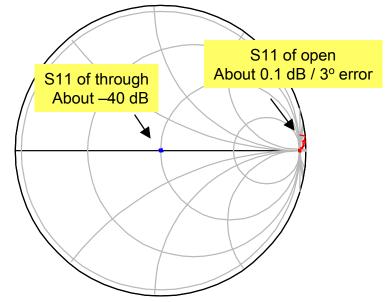

## Can we trust the calibration?

## 75-110 GHz calibration looks *Great*

freq (75.00GHz to 110.0GHz)

## 140-220 GHz calibration looks OK

freq (140.0GHz to 220.0GHz)

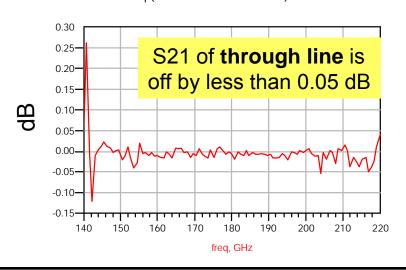

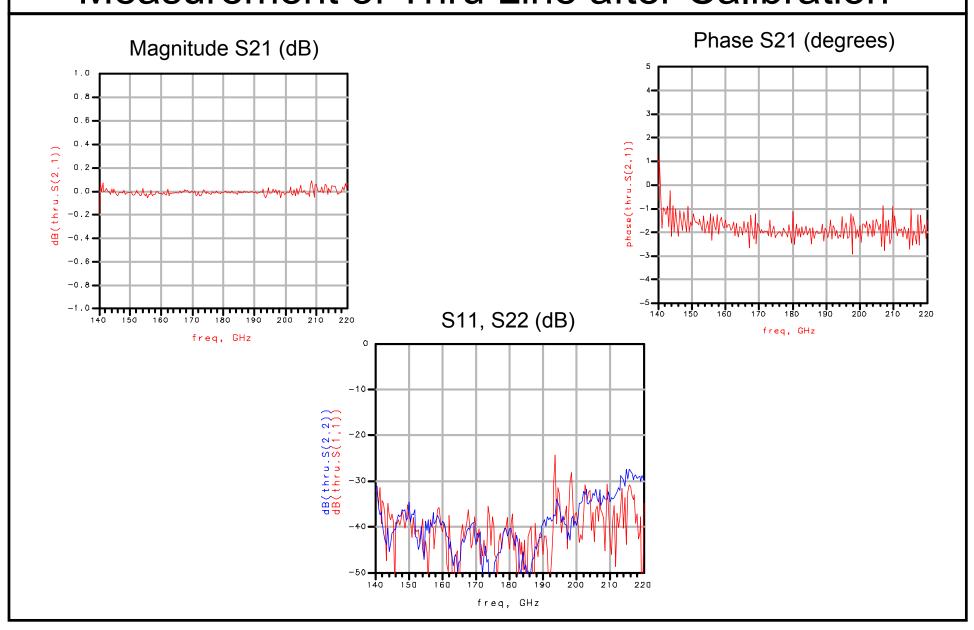

140-220 GHz Calibration Verification:

Measurement of Thru Line after Calibration

## transistor results

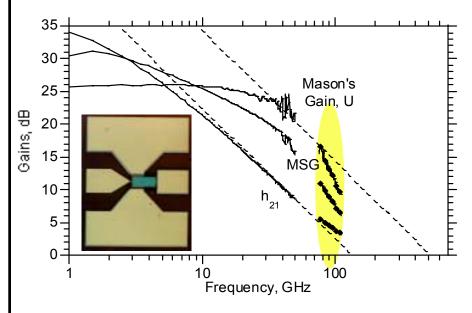

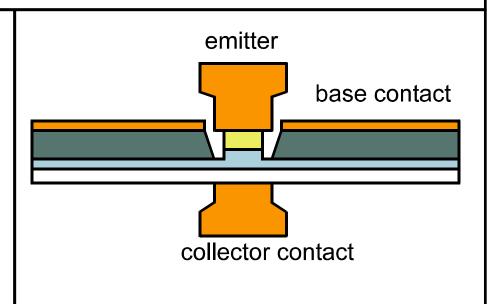

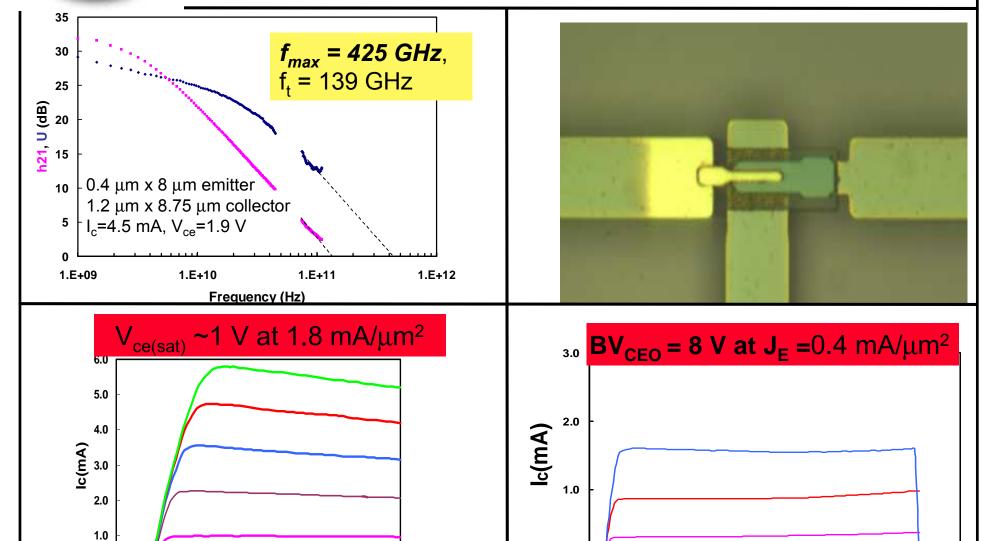

## **Ultra-high f**<sub>max</sub> **Transferred-Substrate HBTs**

- Substrate transfer provides access to both sides of device epitaxy

- Permits simultaneous scaling of emitter and collector widths

- Maximum frequency of oscillation

$$\Rightarrow f_{\text{max}} \cong \sqrt{f_{\tau} / 8\pi R_{bb} C_{cb}}$$

- Sub-micron scaling of emitter and collector widths has resulted in record values of **extrapolated**  $f_{max}$

- Extrapolation begins where measurements end

- New 140-220 GHz Vector Network Analyzer (VNA) extends device measurement range

## Submicron InAIAs/InGaAs HBTs: Unbounded Unilateral power gain 45-170 GHz

UCSB ONR Miguel Urteaga

Miguel Urteaga

## **Negative Unilateral Power Gain ???**

## Can U be Negative?

YES, if denominator is negative

This may occur for device with a negative output conductance  $(G_{22})$  or some positive feedback  $(G_{12})$

$$\mathbf{U} = \frac{\left| \mathbf{Y}_{21} - \mathbf{Y}_{12} \right|^2}{4 \left( \mathbf{G}_{11} \mathbf{G}_{22} - \mathbf{G}_{21} \mathbf{G}_{12} \right)}$$

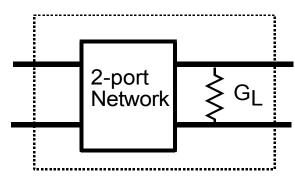

## What Does Negative U Mean?

Device with negative U will have infinite Unilateral Power Gain with the addition of a proper source or load impedance

## **AFTER Unilateralization**

- Network would have negative output resistance

- Can support one-port oscillation

- Can provide infinite two-port power gain

$$\mathbf{U} = \frac{\left| \mathbf{Y}_{21} - \mathbf{Y}_{12} \right|^2}{4 \left[ \mathbf{G}_{11} \left( \mathbf{G}_{22} + \mathbf{G}_{L} \right) - \mathbf{G}_{21} \mathbf{G}_{12} \right]}$$

Select G<sub>L</sub> such that denominator is zero:

$$\mathbf{U} = \infty$$

Simple Hybrid-  $\pi$  HBT model will NOT show negative U

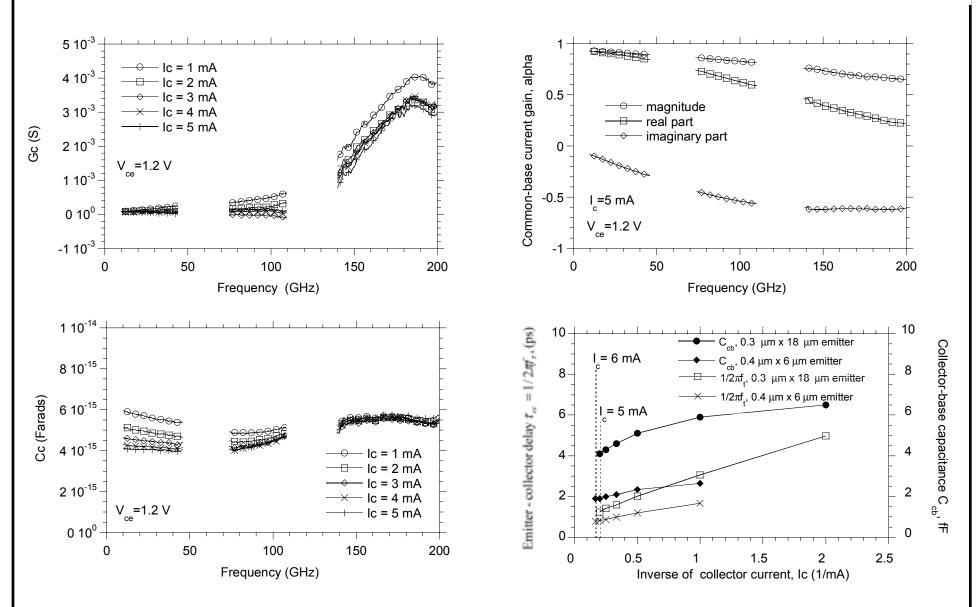

## DC-200 GHz parameters of 0.3 $\mu$ m Emitter / 0.7 $\mu$ m Collector HBTs:

Miguel Urteaga

No evidence whatsoever of the postulated base pushout phenomenon of Jäckel et al (this theory also uses an erroneous hole mobility, error due to calculus derivatives chain rule error)

0

0.5

1.5

Vce(V)

2

2.5

## transferred-substrate DHBTs

much wider bandwidth devices coming soon (we hope...)

0.0

$V_{ce}(V)$

UCSB IQE

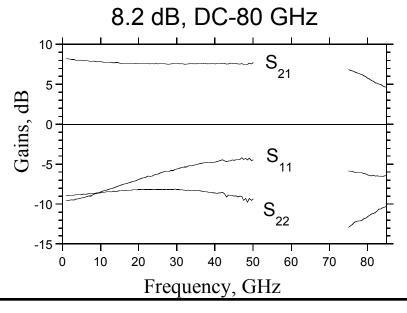

## Wideband Mesa InP/InGaAs/InP DHBTs

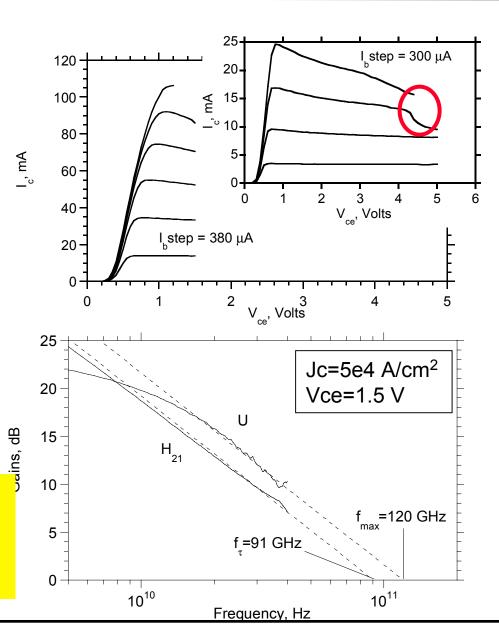

Walsin ONR

Mattias Dahlstrom / Amy Liu

We have obtained high  $f_t$  and very high  $f_{max}$  in mesa DHBTs with C-doped InGaAs bases

Devices have very narrow base mesas and extremely low base contact resistivity

Unlike transferred-substrate HBTs, which have very low  $C_{\rm cbx}$ , these devices have significant extrinsic collector-base junction areas.

→ further effort needed in excess Ccb reduction for >100 GHz digital ICs

Results to be presented soon

## Comparing High-f<sub>max</sub> HBTs

- 0.3 um x 18 um emitter,

- 0.7 um x 19 um collector. 130 GHz ft, fmax very high

- 0.4 um x 6 um emitter,

- 0.7 um x 6.4 um collector. 130 GHz ft, fmax very high

100

0.1

## InP/InGaAs/InP *Metamorphic* DHBT on *GaAs substrate*

UCSB Young-Min Kim

# 40 - h<sub>21</sub> 30 - U 30 - triple-mesa device (not transferred-substrate) f = 207 GHz f = 140 GHz

frequency (GHz)

## Growth:

400 Å base, 2000 Å collector GaAs substrate InP metamorphic buffer layer (high thermal conductivity)

## **Processing**

conventional mesa HBT narrow 2 um base mesa, 0.4 um emitter

### **Results**

1000

207 GHz  $f_t$ , 140 GHz  $f_{max}$ , >6 Volt BVCEO,  $\beta$ =76

## IC results

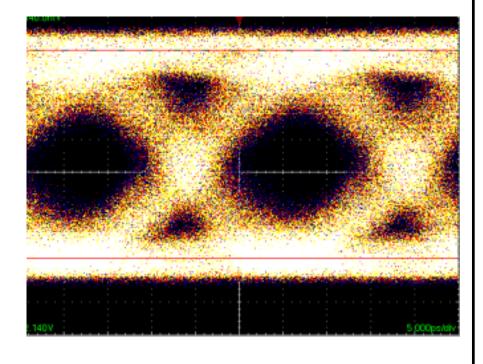

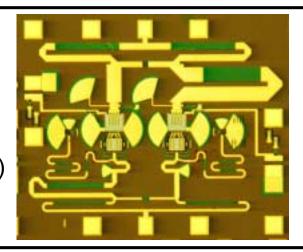

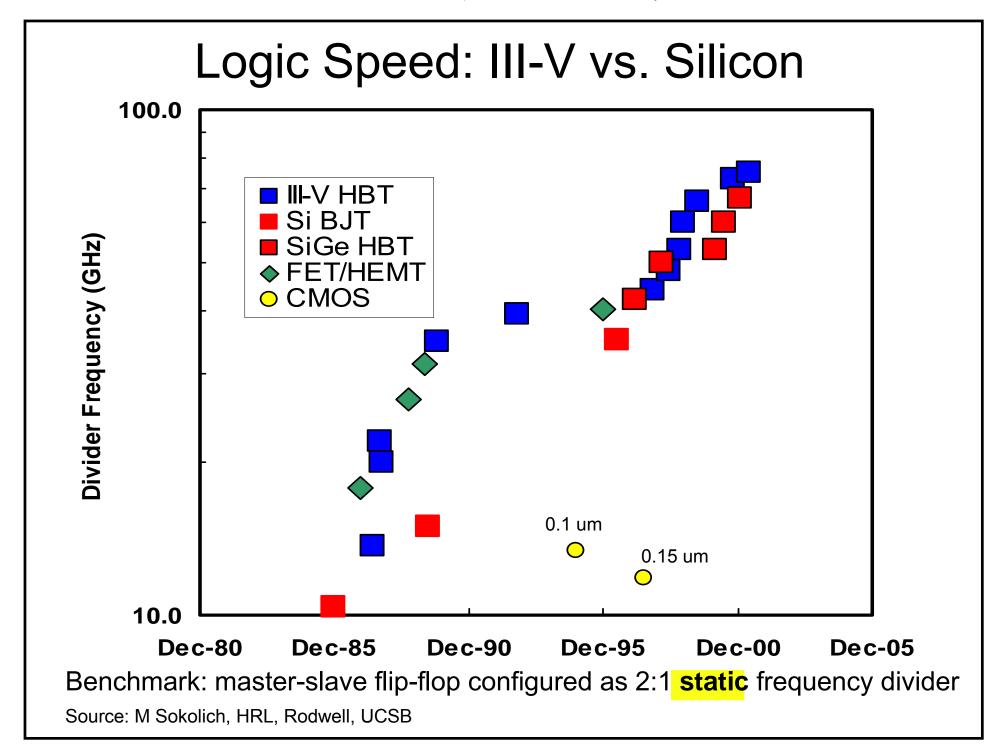

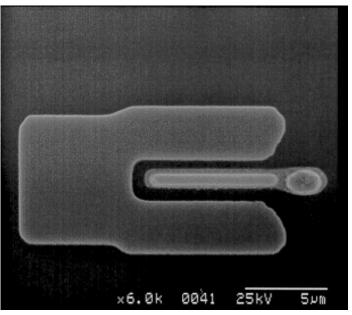

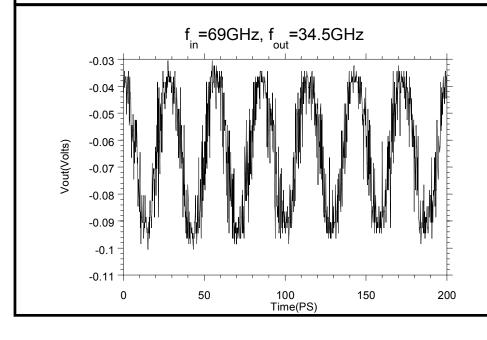

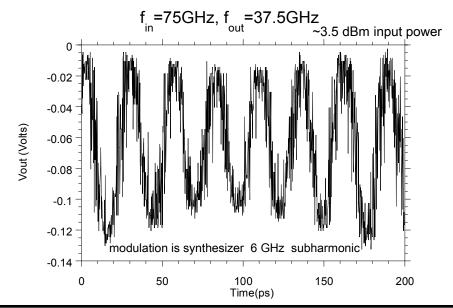

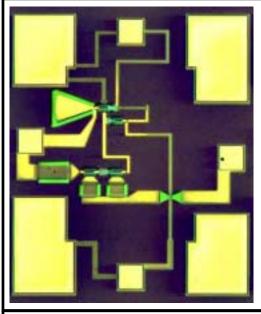

## 75 GHz HBT master-slave latch connected as Static frequency divider

Thomas Mathew

Michelle Lee

Hwe-Jong Kim

### technology:

400 Å base, 2000 Å collector HBT

0.7 um mask (0.6 um junction) x 12 um emitters

1.5 um mask (1.4 um junction) x 14 um collectors

1.8×10<sup>5</sup> A/cm<sup>2</sup> operation, 180 GHz ft, 260 GHz fmax

simulations: 95 GHz clock rate in SPICE

test data to date:

tested, works over full 26-40 and 50-75 GHz bands

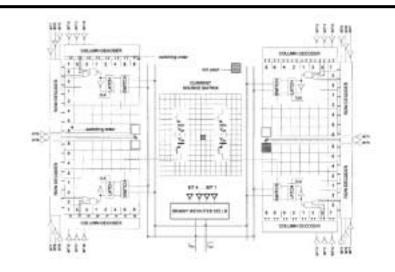

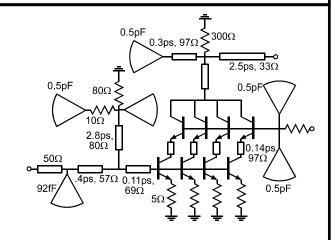

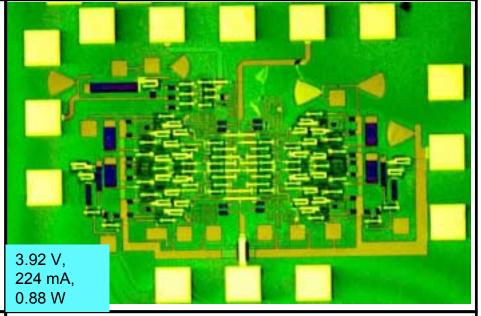

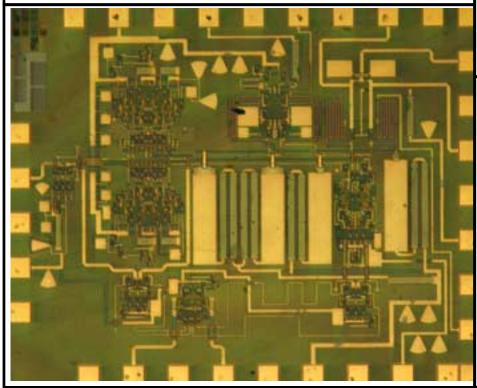

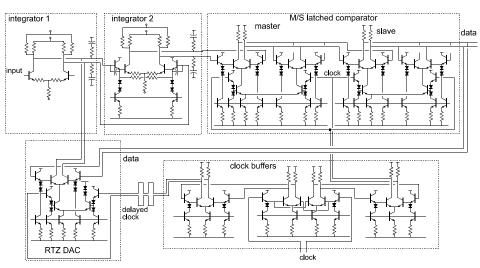

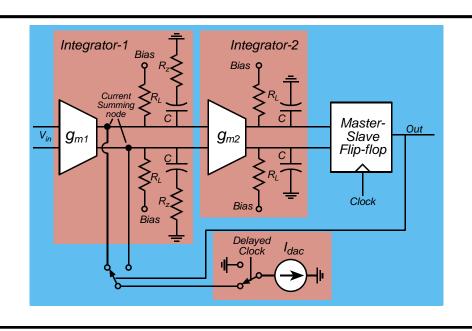

## 18 GHz $\Sigma$ - $\Delta$ ADC

UCSB

S Jaganathan

## Design

comparator is 75 GHz flip flop DC bias provided through 1 K $\Omega$  resistors Integration obtained with 3 pF capacitors RTZ gated DAC

## **Integrated Circuit**

150 HBTs, 1.2 x 1.5 mm, 1.5 W

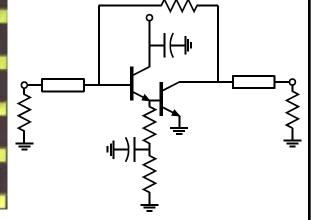

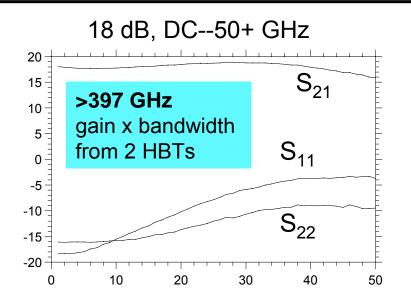

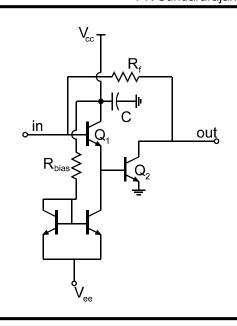

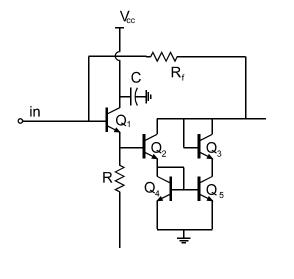

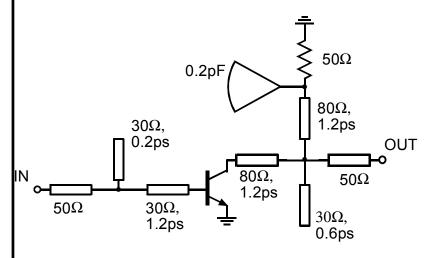

## **High Speed Amplifiers**

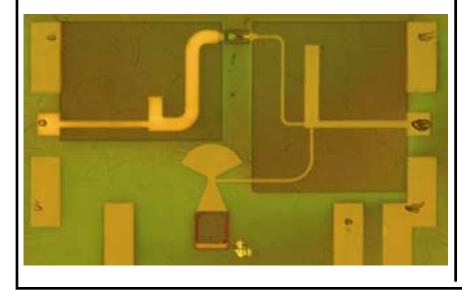

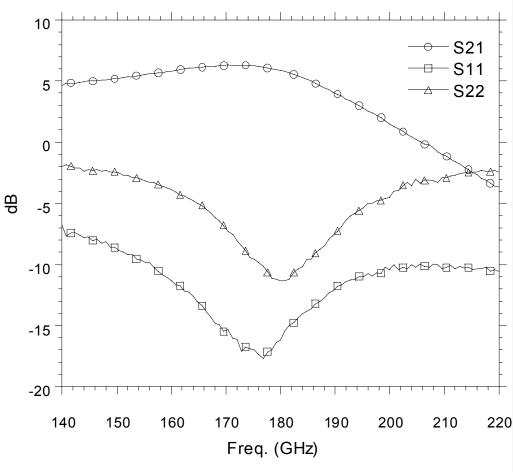

## 175 GHz Single-Stage Amplifier

**UCSB**

Miguel Urteaga

Submicron HBT Program

6.3 dB gain at 175 GHz

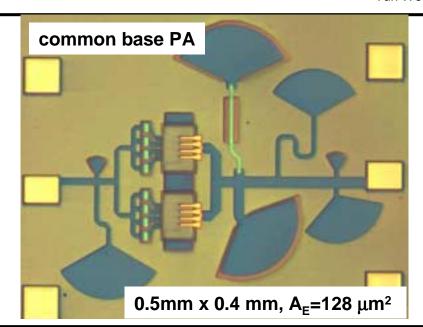

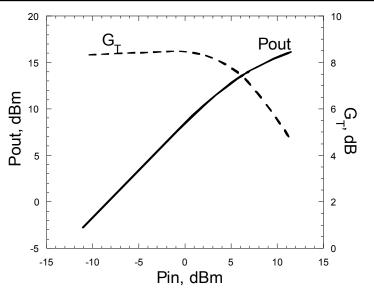

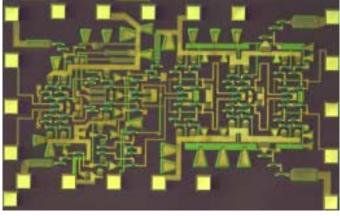

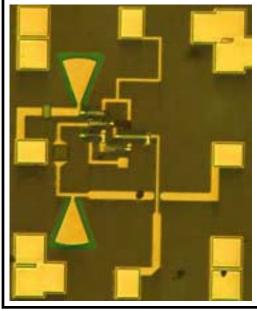

## 40 mW, W-band InP DHBT power amplifiers

Yun Wei

**Objectives:** W band, P<sub>1dB</sub>>9 dBm, P<sub>sat</sub>>12 dBm

**Approach:** transferred-substrate InP DHBTs,

microwave amplifier design

Simulations: S-parameter and harmonic

simulation in ADS

## **Accomplishments:**

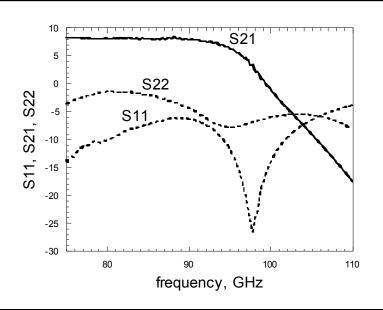

$f_0$ =85 GHz, BW<sub>3dB</sub>=28 GHz,

$G_T$ =8.5 dB,  $P_{1dB}$ =14.5 dBm,  $P_{sat}$ =16dBm