## Improved Migration-Enhanced Epitaxy for Self-Aligned InGaAs Devices

Mark A. Wistey, Uttam Singisetti, Ashish K. Baraskar, Greg J. Burek, Arthur C. Gossard, and Mark J. W. Rodwell

University of California, Santa Barbara, Santa Barbara, CA 93105

Parasitic contact and access resistances limit the bandwidth of high speed electronic and optoelectronic devices. Molecular beam epitaxy can provide very highly doped layers and in-situ Mo deposition for low resistance contacts [1]. But regrowth of contacts next to a finished device often results in undesirable gaps. On the other hand, self-aligned contacts provide the shortest electrical path from external contacts to a device, and they require no critical lithography.

In this study, we examine regrowth of n<sup>++</sup> InGaAs for self-aligned contacts next to SiO<sub>2</sub> gate structures as a function of temperature, V/III ratio, and pulsed deposition. Growth is challenging because Si doping above  $5x10^{19}$  cm<sup>-3</sup> is required for contact resistances below  $10^{-8}$   $\Omega$ -cm<sup>2</sup>, but this produces either extremely rough films or gaps near the gate, depending on temperature.

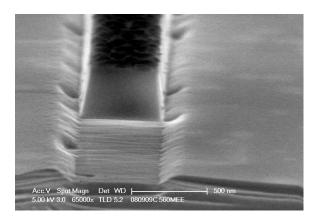

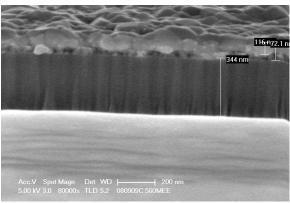

On the other hand, a modification of migration-enhanced epitaxy (MEE) at high temperature with continuous arsenic flux produced smooth films. Single monolayers of Group III atoms were deposited with a flux ratio V/III~3, separated by a 15 sec soak under a 2-5x10<sup>-6</sup> torr As<sub>2</sub> flux. At temperatures below 520 °C, significant crosshatching occured near the gate, which we attribute to preferential migration of In from the SiO<sub>2</sub> to the substrate, resulting in compressive strain and relaxation. Growth at 540-560 °C does not show significant relaxation roughening in SEM. Indium evaporation at these temperatures requires 10-34% additional indium to maintain lattice-matched conditions. In contrast to Shen's results on InAs [2], we find that increasing substrate temperature leads to [111] faceted growth rather than a uniform "rising tide." Growth at 540 °C with alternating 4x2 - 3x1 - 4x2 RHEED patterns produced films which were both smooth in the far field and showed no apparent gap near the gate.

High levels of silicon doping (8x10<sup>19</sup> cm<sup>-3</sup>) initially raised two concerns. First, Si concentrations are well above the solid solubility limit in InGaAs. MEE provides increased time for relaxation processes to occur during growth, and the high temperatures tend to drive toward thermodynamic limits. Second, Si is only a donor when sitting on a Group III lattice site, but MEE creates Group III-rich surfaces. However, electron concentrations as measured by Hall were virtually identical whether the Si was provided simultaneously with Group III atoms or in the middle of the As soak. It appears that Si preferentially takes surface Group III sites even on an arsenic-poor surface.

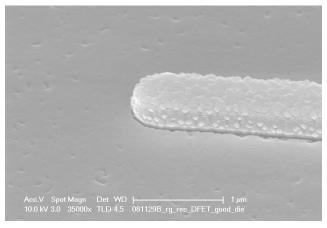

Using these self-aligned regrowth techniques, we have fabricated the first III-V MOSFETs with self-aligned regrowth of source-drain contacts. These techniques will enable lateral scaling of future III-V MOSFETs and HEMTs to tens of nanometers.

<sup>&</sup>lt;sup>1</sup> U. Singisetti, et al., Appl. Phys. Lett., **93**,183502 (2008).

<sup>&</sup>lt;sup>2</sup> X. Q. Shen, et al., *J. Cryst. Growth* **146**, 374 (1995)

Fig. 1. Migration-enhanced epitaxial regrowth next to SiO2 dummy gate at 560 °C. (left) End view with part of gate removed, showing (111) faceted growth up to gate. (right) Side view showing clean sidewalls.

|                              | [Si]<br>(cm <sup>-3</sup> ) | n<br>(cm <sup>-3</sup> ) | $\mu$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) |

|------------------------------|-----------------------------|--------------------------|----------------------------------------------------------|

| Conventional<br>MBE          | 8x10 <sup>19</sup>          | 4.8x10 <sup>19</sup>     | 847                                                      |

| Si during<br>Group III pulse | 8x10 <sup>19</sup>          | 4.3x10 <sup>19</sup>     | 1258                                                     |

| Si during As<br>soak         | 8x10 <sup>19</sup>          | 4.2x10 <sup>19</sup>     | 1295                                                     |

Fig. 2. Hall measurements of samples grown by conventional MBE (nonstop) and MEE.

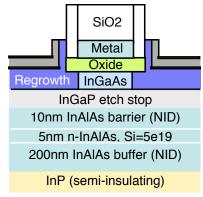

Fig. 3. Depletion-mode InGaAs MOSFET structure (not to scale).

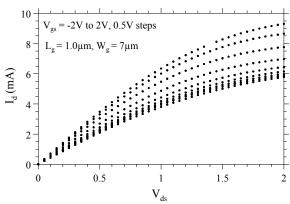

Fig. 3. Depletion-mode InGaAs MOSFET. (Left) Oblique view SEM after InGaAs regrowth and in-situ Mo deposition, before mesa isolation. (Right) Id-Vds. High off-state currents are due to conduction through the doping layer, which is 17 nm away from the gate.