# Influence of gate metallization processes on the electrical characteristics of high-k/ln<sub>0.53</sub>Ga<sub>0.47</sub>As interfaces

### Greg J. Burek

Department of Electrical and Computer Engineering, University of California, Santa Barbara, California 93106

#### Yoontae Hwang

Materials Department, University of California, Santa Barbara, California 93106-5050

## Andrew D. Carter

Department of Electrical and Computer Engineering, University of California, Santa Barbara, California 93106

#### Varistha Chobpattana

Materials Department, University of California, Santa Barbara, California 93106-5050

#### Jeremy J. M. Law

Department of Electrical and Computer Engineering, University of California, Santa Barbara, California 93106

#### William J. Mitchell and Brian Thibeault

Department of Electrical and Computer Engineering, University of California, Santa Barbara, California 93106

#### Susanne Stemmer<sup>a)</sup>

Materials Department, University of California, Santa Barbara, California 93106-5050

# Mark J. W. Rodwellb)

Department of Electrical and Computer Engineering, University of California, Santa Barbara, California 93106

(Received 26 May 2011; accepted 26 June 2011; published 3 August 2011)

The influence of different gate metal deposition processes on the electrical characteristics of dielectric/III-V interfaces is investigated.  $Al_2O_3$  and  $HfO_2$  dielectrics are grown on  $In_{0.53}Ga_{0.47}As$  channels and top metal electrodes are deposited by either thermal evaporation or electron beam deposition. It is shown that metal-oxide-semiconductor capacitors with electron beam evaporated electrodes exhibit substantially larger midgap interface trap densities than those with thermally evaporated electrodes. The damage caused by electron beam metallization can be mitigated by subsequent, long anneals in forming gas. © 2011 American Vacuum Society. [DOI: 10.1116/1.3610989]

# I. INTRODUCTION

The development of metal-oxide-semiconductor field effect transistors with high-mobility, compound (III-V) semiconductor channels and high-permittivity (k) gate dielectrics critically depends on further reducing the typically very high density of interface traps  $(D_{it})$  at the dielectric/semiconductor interface. Although numerous studies have investigated the influence of III-V surface preparation and high-k deposition parameters on the electrical quality of these interfaces, the nature of the interface defects, their spatial location, and energy distribution in the semiconductor band gap remain poorly understood. Fewer studies have focused on the role of post-high-k-deposition device processing steps in determining the interface quality. For example, en-

ergetic species (ions, electrons, and x-rays) generated during gate metal deposition may cause significant damage to the III-V semiconductor far below the surface.<sup>3</sup> In this context, several recent studies have reported significant improvements of the interface electrical characteristics after postmetallization anneals in forming gas, which contains a few percent of hydrogen. 4-7 Among the mechanisms that have been suggested to cause the reduction in  $D_{it}$  are hydrogen passivation of border traps in the oxide<sup>4</sup> and reduction of native oxides of the III-V semiconductor.<sup>8</sup> A third possibility, namely, that the forming gas anneals serve to recover the damage from gate metal deposition, has not yet been considered. In this article, we investigate the influence of two different gate metal deposition processes, electron beam and thermal evaporation, on the  $D_{it}$  of high- $k/In_{0.53}Ga_{0.47}As$  interfaces. We show that gate metallization can cause substantial increases in the  $D_{it}$  and that the main effect of postmetallization forming gas treatments is to anneal out this damage.

a)Electronic mail: stemmer@mrl.ucsb.edu

b) Electronic mail: rodwell@ece.ucsb.edu

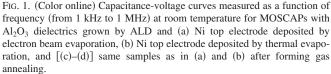

Fig. 2. (Color online) Capacitance-voltage curves measured as a function of frequency (from 1 kHz to 1 MHz) at room temperature for MOSCAPs with HfO<sub>2</sub> dielectrics and (a) Pt electrode deposited by electron beam evaporation, (b) Ni electrode deposited by thermal evaporation, and (c) same sample as in (a) after forming gas annealing.

## **II. EXPERIMENT**

High-k dielectrics were deposited on 300 nm thick  $n-\text{In}_{0.53}\text{Ga}_{0.47}\text{As layers}$  (Si:1×10<sup>17</sup> cm<sup>-3</sup>) grown by molecular beam epitaxy on (001) n<sup>+</sup>-InP. The deposition process for the HfO2 dielectric, which was alloyed with a few percent of Al, has been described elsewhere. 9,10 Al<sub>2</sub>O<sub>3</sub> was deposited by atomic layer deposition (ALD) after cleaning the wafer in a de-ionized water:HCl solution (1:10) for 20 s, followed by 45 cycles of sequential trimethylaluminum (TMA) and H<sub>2</sub>O pulses at 300 °C. Both dielectrics were about 5 nm thick. Metal-oxide-semiconductor capacitor (MOSCAP) structures were fabricated with either Ni or Pt top electrodes. Pt electrodes were deposited by electron beam evaporation, whereas for the Ni electrodes either electron beam or thermal evaporation were used. In all cases, the top electrodes were about 50 nm thick and deposition was through a shadow mask. Back contacts were Ti (20 nm)/Pt (20 nm)/Au (250 nm) or Cr (10 nm)/Au(100 nm). For selected samples, a postmetal deposition anneal was carried out at 400 °C for 50 min in forming gas (95% of N<sub>2</sub> and 5% of H<sub>2</sub>). Frequency-dependent capacitance-voltage (CV) and conductance-voltage (GV) measurements were performed from 1 kHz to 1 MHz at room temperature using an impedance analyzer (Agilent 4294) in the dark. The midgap  $D_{it}$ was quantified using conductance maps after series resistance correction, as described in Ref. 2.

# III. RESULTS AND DISCUSSION

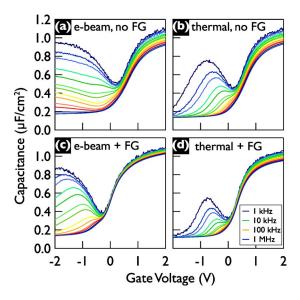

Figures 1(a) and 1(b) show the CV characteristics of MOSCAPs with Al<sub>2</sub>O<sub>3</sub> dielectrics and Ni electrodes at frequencies between 1 kHz and 1 MHz measured without aNY postelectrode deposition anneal. The frequency dispersion in

the capacitance at negative bias is due to midgap  $D_{it}$ response, which is much more pronounced when the gate metal is deposited by electron beam deposition [Fig. 1(a)] rather than by thermal evaporation [Fig. 1(b)]. A measure of the efficiency of Fermi level response is whether the capacitance reaches the minimum capacitance given by the doping level of the semiconductor, i.e., if the applied bias is sufficient to fully deplete the semiconductor. For the MOSCAPs investigated here, the ideal depletion capacitance is about  $0.119 \mu F/cm^2$ . The minimum capacitance values at 1 MHz are 0.174  $\mu$ F/cm<sup>2</sup> (electron beam deposited gate) and  $0.135 \mu F/cm^2$  (thermal gate). This indicates that for both MOSCAPs, the Fermi level movement is not quite sufficient to fully deplete the semiconductor and that the MOSCAP with the electron beam deposited gate has a less efficient Fermi level movement, caused by a higher  $D_{it}$ . Because of the otherwise identical processing of the MOSCAPs, the results show that electron beam deposition of the gate metal causes a much higher  $D_{it}$  than thermal deposition, most likely due to damage to the III-V semiconductor by x-rays and/or secondary electrons. For both MOSCAPs, the electrical characteristics improve after forming gas annealing [Figs. 1(c) and 1(d). The frequency dispersion at negative bias decreases, in particular, for the MOSCAP with the thermal electrode [Fig. 1(d)], which now has a depletion capacitance of 0.118  $\mu$ F/cm<sup>2</sup>, i.e., the ideal value (note that errors in determining the capacitor area correspond to about  $\pm 0.007 \ \mu \text{F/cm}^2$ ). The depletion capacitance for the MOS-CAP with the electron beam deposited electrode is 0.137  $\mu$ F/cm<sup>2</sup>, which, although reduced, indicates that the forming gas annealing was insufficient to anneal out all the damage. In addition, the frequency dispersion in accumula-

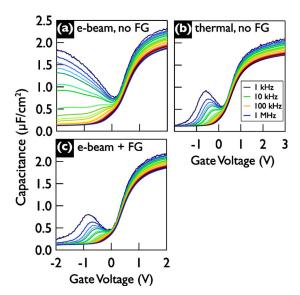

Fig. 3. (Color online) Normalized parallel conductance,  $(G_p/\omega)/Aq$ , as a function of gate voltage and frequency f for MOSCAPs with (a) the  $Al_2O_3$  dielectric with a Ni electrode deposited by thermal evaporation (b) a HfO2 dielectric with a Pt electrode deposited by electron beam evaporation. [(c)–(d)] Same samples as in (a) and (b) after forming gas annealing.

tion is also reduced after the forming gas annealing, to 2%–3% per decade from  $\sim$ 5% per decade for both MOS-CAPs.

Figure 2 shows a comparison of the frequency-dependent CV of MOSCAPs with HfO<sub>2</sub> gate dielectrics and with Pt electrodes deposited by electron beam deposition and Ni electrodes by thermal evaporation, respectively. These capacitors have a higher accumulation capacitance density because of the higher dielectric constant of HfO2. MOSCAPs with Ni electrodes have a slightly lower accumulation capacitance density, most likely because of some degree of oxidation of the Ni. Without forming gas annealing, the MOSCAP with the electron beam deposited electrode [Fig. 2(a)] shows much larger midgap  $D_{it}$ , as evidenced by a large frequency dispersion at negative biases and a minimum capacitance of 0.122  $\mu$ F/cm<sup>2</sup> that is higher than the ideal depletion capacitance. In contrast, the MOSCAP with the thermal gate electrode [Fig. 2(b)] shows only a small "hump" at negative bias and the ideal minimum capacitance  $(0.119 \ \mu F/cm^2)$ , even without the forming gas anneal. After forming gas annealing, the damage from electron beam metallization is largely recovered, see Fig. 2(c).

For a more quantitative measure of the midgap  $D_{ii}$ , Fig. 3 shows maps of the normalized parallel conductance,  $[(G_p/\omega)/Aq]$ , as a function of frequency and gate bias for the MOSCAPs with Al<sub>2</sub>O<sub>3</sub> gate dielectrics and thermal electrodes [Figs. 3(a) and 3(c)] and with HfO<sub>2</sub> gate dielectrics and electron beam deposited electrodes [Figs. 3(b) and 3(d)], before and after forming gas annealings. Here,  $G_p$  is the parallel conductance,  $\omega$  is the angular frequency, A is the MOSCAP area, and q is the elemental charge. For the analysis, an oxide capacitance of 1.57  $\mu$ F/cm<sup>2</sup> for the Al<sub>2</sub>O<sub>3</sub> MOSCAP and 3.1  $\mu$ F/cm<sup>2</sup> for the HfO<sub>2</sub> MOSCAP were used, which were determined independently through a thick-

ness series and the Terman method, respectively. The  $D_{it}$  at about 0.3 eV below the conduction band edge can be estimated by multiplying  $[(G_p/\omega)/Aq]_{\rm max}$  with a factor of 2.5. For the MOSCAP with  ${\rm Al_2O_3}$  and thermally evaporated electrode,  $[(G_p/\omega)/Aq]_{\rm max}$  is  $5.7\times10^{12}~{\rm cm^{-2}~eV^{-1}}$  which decreases to  $3.4\times10^{12}~{\rm cm^{-2}~eV^{-1}}$  after the forming gas annealing. A much larger change is detected for the HfO<sub>2</sub> MOSCAP with the electron beam evaporated gate electrode. Before the forming gas annealing,  $[(G_p/\omega)/Aq]_{\rm max}$  is  $10.8\times10^{12}~{\rm cm^{-2}~eV^{-1}}$  and the peak does not move in frequency for gate biases below  $-1~{\rm V}$ . This indicates that the Fermi level is essentially pinned near midgap. After the forming gas anneal,  $[(G_p/\omega)/Aq]_{\rm max}$  moves efficiently as a function of bias. The highest  $[(G_p/\omega)/Aq]_{\rm max}$  value is  $5.2\times10^{12}~{\rm cm^{-2}~eV^{-1}}$ .

#### **SUMMARY AND CONCLUSIONS**

In summary, we have shown that deposition of gate electrodes using electron beam evaporation causes a significant degradation of high-k/III-V interfacial electrical characteristics, as exhibited by a large midgap  $D_{it}$ . Comparison with MOSCAPs with electrodes deposited by thermal evaporation and processed under otherwise identical conditions demonstrates that the very large midgap  $D_{it}$  is indeed caused by the electron beam deposition process and is not intrinsic to the as-deposited high-k/III-V interface. The results further demonstrate that the reason for  $D_{it}$  reduction by forming gas treatments consists of annealing out of damage in the III-V semiconductor and is not due to the passivation of defects by hydrogen, i.e., as for SiO<sub>2</sub>/Si interfaces. This also explains the fairly long annealing times that are required to restore the interface electrical properties. As shown in the literature for III-V quantum wells,<sup>3</sup> even the thermal electrode deposition process is likely to cause some damage. In particular, for MOSCAPs with Al<sub>2</sub>O<sub>3</sub> dielectrics and thermally deposited electrodes, reduction in  $D_{it}$  was seen after forming gas anneals. Future studies should investigate electrodes deposited by chemical vapor deposition or ALD, which may allow for even lower  $D_{it}$ .

The research was funded by the Semiconductor Research Corporation through the Nonclassical CMOS Research Center (Task IDs 1437.005 and 1437.006) and by the ONR Drift and Define MURIs (Grant Nos. N00014-08-1-0655 and N00014-10-1-0937). The work made use of the UCSB Nanofabrication Facility, a part of the NSF-funded NNIN network.

<sup>&</sup>lt;sup>1</sup>A. M. Sonnet, C. L. Hinkle, D. Heh, G. Bersuker, and E. M. Vogel, IEEE Trans. Electron Devices **57**, 2599 (2010).

<sup>&</sup>lt;sup>2</sup>R. Engel-Herbert, Y. Hwang, and S. Stemmer, J. Appl. Phys. **108**, 124101 (2010).

<sup>&</sup>lt;sup>3</sup>C. H. Chen, E. L. Hu, W. V. Schoenfeld, and P. M. Petroff, J. Vac. Sci. Technol. B **16**, 3354 (1998).

<sup>&</sup>lt;sup>4</sup>E. J. Kim, L. Q. Wang, P. M. Asbeck, K. C. Saraswat, and P. C. McIntyre, Appl. Phys. Lett. **96**, 012906 (2010).

<sup>&</sup>lt;sup>5</sup>E. O'Connor *et al.*, Appl. Phys. Lett. **94**, 102902 (2009).

<sup>&</sup>lt;sup>6</sup>Y. Hwang, R. Engel-Herbert, N. G. Rudawski, and S. Stemmer, J. Appl. Phys. **108**, 034111 (2010).

<sup>&</sup>lt;sup>7</sup>W.-E. Wang, H. C. Lin, and M. Meuris, U.S. Patent Application No. 20100065824.

<sup>&</sup>lt;sup>8</sup>H. D. Trinh *et al.*, Appl. Phys. Lett. **97**, 042903 (2010).

<sup>&</sup>lt;sup>9</sup>Y. Hwang, V. Chobpattana, J. Y. Zhang, R. Engel-Herbert, and S. Stemmer, Appl. Phys. Lett. **98**, 142901 (2011).

<sup>&</sup>lt;sup>10</sup>Y. Hwang, R. Engel-Herbert, and S. Stemmer, Appl. Phys. Lett. **98**, 052911 (2011).

<sup>&</sup>lt;sup>11</sup>R. Engel-Herbert, Y. Hwang, and S. Stemmer, Appl. Phys. Lett. **97**, 062905 (2010).

<sup>&</sup>lt;sup>12</sup>H. C. Lin, G. Brammertz, K. Martens, G. de Valicourt, L. Negre, W. E. Wang, W. Tsai, M. Meuris, and M. Heyns, Appl. Phys. Lett. **94**, 153508 (2009).