# 30% PAE W-band InP Power Amplifiers using Sub-quarterwavelength Baluns for Series-connected Power-combining

<sup>1</sup>Hyun-chul Park, <sup>1</sup>Saeid Daneshgar, <sup>1</sup>Johann C. Rode, <sup>2</sup>Zach Griffith, <sup>2</sup>Miguel Urteaga, <sup>3</sup>Byung-sung Kim, and <sup>1</sup>Mark Rodwell

<sup>1</sup>ECE Department, University of California at Santa Barbara, Santa Barbara, CA, 93106, USA, <sup>2</sup>Teledyne Scientific and Imaging, 1049 Camino Dos Rios, Thousand Oaks, CA, 91360, USA, <sup>3</sup>ECE Department, Sungkyunkwan University, Suwon, 440-746, South Korea,

Email: hcpark@ece.ucsb.edu

Abstract — We present high-efficiency W-band power amplifier (PA) ICs with a new series-connected power-combining technique using sub-quarter-wavelength transmission-line baluns. The PAs are implemented in a 0.25μm InP HBT process. At 86GHz, a single-stage PA exhibits 30.4% peak PAE, 20.37dBm P<sub>out</sub> and 23GHz 3dB-bandwidth. A two-stage PA exhibits 30.2% PAE, and 23.14dBm P<sub>out</sub>. These values of PAE represent a 1.2:1 improvement in the state-of-the-art for E- and W-band PAs having similar RF output powers.

Index Terms — W-band power amplifiers, power-added-efficiency, sub-quarter-wavelength baluns, InP HBT device.

#### I. INTRODUCTION

High efficiency W-band power amplifiers (PAs) are required for future high-speed communications and high-resolution radar/imaging systems. High power allows large signal transmission coverage, while high efficiency extends battery life, saves energy and reduces cost. W-band PA design is challenging because of limited transistor bandwidth and because power-combining networks are lossy and occupy considerable die area [1-3].

With GaN W-band PAs [1-2], where the high FET breakdown voltage allows >10V supplies,  $530 \text{mW/mm}^2$  output power per unit IC die area has been reported, as has 24.7% power-added efficiency (PAE) at 206mW output power and 20.0% PAE at 1.8W [1-2]. InP HBTs have higher power-gain cutoff frequencies- greater than 1THz  $f_{max}$ - hence higher W-band power gain is available than in GaN. Consequently, despite the lower 2.5~3V supply voltages [4], the efficiency of W-band InP PAs can exceed levels currently demonstrated in GaN. High PAE and output powers approaching 1W are feasible in W-band InP HBT power amplifiers.

Efficient output power combining techniques are necessary both for high PAE and for high output power per unit die area. Whether they use quarter-wavelength ( $\lambda$ /4) line sections, i.e. Wilkinson combiners, or subquarter-wavelength lines, classic corporate output power-combiners have high attenuation and occupy large IC die areas [1-2]. Power combiners using transformers [3] or

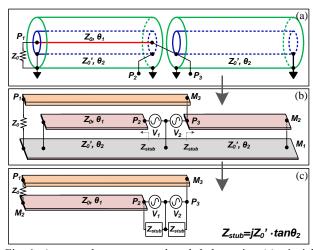

Fig. 1. A new sub-quarter-wavelength balun using (a) triaxial cables, (b) three-metal interconnects and (c) its equivalent-circuit model showing series-connected power-combining.

baluns can occupy smaller die areas, but attenuation, imbalances between ports, and low transformer coupling-factors present design challenges which impair efficiency.

Here we report high performance PAs using a new subquarter-wavelength balun for series-connected powercombining (Fig. 1). We review the InP HBT IC process in Section II. The power-combiner is described in Section III, and the PA design procedure is described in Section IV. Section V presents measured results.

## II. INP DEVICE AND IC PROCESS

The W-band PA ICs reported in this paper are designed using 0.25 µm InP HBTs with a breakdown voltage  $BV_{CEO}$ =4.5 V. An HBT-cell having four fingers, each 0.25 x6 µm², exhibits 590 GHz  $f_{max}$  and 350 GHz  $f_{\tau}$  at  $J_E$ =6 mA/µm² emitter current density. The IC process has three levels of gold interconnects, as shown in Fig. 1 (b), where vias provide access from the top layer  $M_3$  (3 µm thickness) to the bottom two layers  $M_2$  and  $M_1$  (each has 1 µm thickness). The three metal layers are separated by BCB ( $\epsilon_r$ =2.7) dielectric layers  $M_3$ - $M_2$  (5 µm thickness) and  $M_2$ - $M_1$  (1 µm thickness), respectively. MIM capacitors of

$0.3 fF/\mu m^2$  and thin film resistors of  $50\Omega/square$  are incorporated for matching and biasing.

#### III. SUB-QUARTER-WAVELENGTH BALUNS

The output power-combiner is similar to a wideband Marchand balun, but unlike the Marchand design [5], uses line sections much shorter than  $\lambda_g/4$ , a quarter of a guide wavelength. In this sub-quarter-wave design, power-combining losses are greatly reduced simply because of greatly reduced transmission-line length. The required die area is similarly reduced. The sub-quarter-wave design introduces shunt inductive loading at the ports connecting to the transistors, loading which is tolerated by absorbing it into the amplifier output tuning network, thereby tuning the transistor output capacitance. To maintain phase balance, an identical balun is used on the PA input.

### A. Series-connected Power-combining Baluns

The proposed balun structure can be analyzed by considering triaxial cable and triplate transmission-lines (Fig. 1). The triaxial cable in Fig. 1 (a) consists of an inner-conductor (red), mid-conductor (blue) and outerconductor (green) which correspond to the metal planes M<sub>3</sub>, M<sub>2</sub> and M<sub>1</sub>, in Fig. 1 (b) and (c), respectively. In the coaxial structure, conductor M2 shields conductor M1 from conductor M<sub>3</sub>, hence the balun eigenmodes are the voltages between M<sub>1</sub> and M<sub>2</sub>, with characteristic impedance  $Z_0$  selected to be  $50\Omega$ , and the voltage between  $M_2$  and  $M_3$ , with characteristic impedance  $Z_0$ , which can be arbitrary. In the triplate configuration, the conductor M<sub>2</sub> is made much wider than the conductor M<sub>3</sub>, so as to again shield  $M_3$  from  $M_1$ . The  $M_1$ - $M_2$  (impedance  $Z_0$ ) and  $M_2$ - $M_3$  (impedance  $Z_0$ ) voltage differences then again become the normal modes of the structure.

The balun output power-combiner (Fig. 1 (b)) is now clearly and simply understood using the equivalent circuit of Fig. 1 (c), where the voltage sources  $V_1$  and  $V_2$ , connected to balun ports  $P_2$  and  $P_3$  respectively, are connected in series between conductors  $M_2$  and  $M_3$ , the  $50\Omega$  transmission-line connected to the  $50\Omega$  amplifier load. Voltage sources  $V_1$  and  $V_2$  are also loaded by the shunt-stub impedance  $Z_{stub} = jZ_0$ ' tan  $\theta_2$  associated with the short-circuited transmission-line stubs between  $M_1$  and  $M_2$ . Given the series connection,  $V_1$  and  $V_2$  are each individually loaded by the parallel combination of  $25\Omega$  and the inductive shunt impedance  $Z_{stub}$ .

In class-A power amplifier design, highest output power and highest collector/drain efficiency are obtained if the transistor is loaded in a LR parallel network whose resistive part  $R_{L,opt} = (V_{\rm max} - V_{\rm min})/I_{\rm max}$  is the ratio of maximum transistor voltage swing to maximum transistor current, and whose inductive part  $j\omega L = -1/j\omega C_{out}$ ,

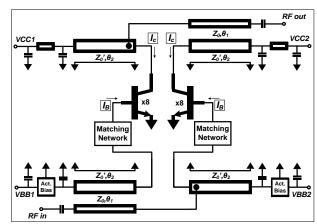

Fig. 2. The single-stage PA circuit schematic.

where  $C_{out}$  is the transistor output capacitance. Design therefore consists of adjusting the HBT junction area, and hence  $I_{\rm max}$ , until  $R_{L,opt}=25\Omega$ , and then subsequently adjusting the balun length  $\theta_2$  until  $Z_{stub}=-1/j\omega C_{out}$ .

In these designs using 2:1 baluns, each of the two HBT power cells has 2:1 larger junction area, and 2:1 larger  $I_{\rm max}$ , than a device sized to directly drive  $50\Omega$  with appropriate shunt inductive tuning. The total output power is therefore increase 4:1. We have also designed and fabricated, and are presently testing, PA designs with 4:1 series-connected baluns. In simulations, these provide a 16:1 increase in output power.

## B. Balun Design in Real ICs

The triaxial cable for the proposed balun concept is designed using the Teledyne Scientific Company's IC process, which supports three-metal interconnects as shown in Fig. 1 (b). This metal stack is not optimum for the proposed balun structure, because the M<sub>3</sub>-M<sub>2</sub> distance of 5µm is higher than the M<sub>2</sub>-M<sub>1</sub> distance of 1µm, and the metal stacks lead non-negligible E-fields between M<sub>3</sub>-M<sub>1</sub>. In order to solve this problem, two sidewalls adjacent to M<sub>3</sub> are used with dense arrays of via<sub>23</sub> supporting the functionality of the triaxial cable. The top-metal M<sub>3</sub> (width  $w_3=12\mu m$ ) and the second-metal  $M_2$  (width  $w_2=42\mu m$ ) with the sidewalls (M<sub>3</sub>-M<sub>3</sub> spacing of 5 $\mu m$ ) produce a  $Z_0$ =50 $\Omega$ . The other characteristic impedance  $Z_0$ '=55 $\Omega$  between M<sub>1</sub>-M<sub>2</sub> is implemented using 3 $\mu$ m slottype spacing transmission-line due to the small distance of  $1 \mu m$  between  $M_1$ - $M_2$ .

In order to verify the operation and the performance of the proposed balun, test structures of two back-to-back baluns have been designed and fabricated, and their insertion losses have been measured at frequencies of 80, 90, and 100GHz with different values of capacitors (103, 78, and 65fF). The measured results verify the predictions with the insertion loss less than 0.6dB which is achieved from one balun as small as  $\sim \lambda/16$ .

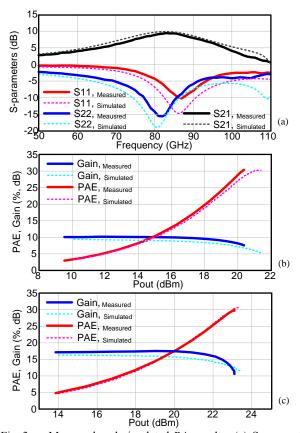

Fig. 3. Measured and simulated PA results: (a) S-parameter results for the single-stage PA, (b) PAE and gain vs. output power for the single-stage PA and (c) PAE and gain vs. output power for the two-stage PA.

## IV. POWER AMPLIFIER IC DESIGNS

The high-efficiency W-band single-stage and two-stage 2:1 series power-combined PAs have been designed using the sub-quarter wavelength *triplate* transmission-line baluns as the single-stage PA schematic diagram shown in Fig. 2. 2x4-finger scaled HBT cells have been selected for a DC current with 25mA, which is slightly lower than a class-A bias in order to maintain the speed of transistors and achieve higher PAEs. The cells have an optimum load impedance R of 25 $\Omega$ , which is an appropriate value for a 2:1 impedance transformation to an un-balanced input and output load of 50 $\Omega$ . Since the outputs of the PA-cells contain a parasitic collector-emitter capacitance  $C_{out}$  of ~90fF, the shrunk balun can fit into the output of PA cells without any other matching components.

The center frequency of 84GHz is targeted for the PA designs where the electrical length of  $\theta_2$ = $\lambda/4$  (400 $\mu$ m) on the slot-type transmission-lines can be decreased to the electrical length of  $\theta_2$ < $\lambda/16$  (91 $\mu$ m). Decoupling capacitors of about 1.8pF between M<sub>2</sub>-M<sub>1</sub> are used on the ending edges of the input and output baluns in order to

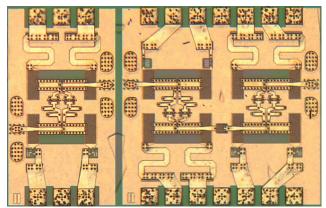

Fig. 4. Die photo of the single-stage and two-stage PAs.

provide RF shorts while maintaining DC bias feeds to the PA input and output. Moreover, semi-  $\lambda/4$  lines with additional bypass capacitors are used on the bias lines to prevent external bias circuit effects. The differential (or push-pull) operation is achieved by having the identical baluns on the input and output while the input of the HBT cells are properly matched to the differential ports of the input balun in order to obtain maximum power transmission. Active bias circuits using an emitter buffered bias topology with two stacked diodes and one resistor to  $V_{BB}$  are utilized for the thermal stability and slightly lower bias operation than a class-A [6]. The two-stage PA has been also designed by the back-to-back connection of the single-stage amplifier with a DC blocking capacitor.

#### V. IC CHARACTERIZATIONS

The two sets of designed and fabricated PA ICs have been measured on the wafer. Small-signal s-parameters on wafer were measured using an Agilent 8510 XF VNA system for single-stage measurements from 50 to 110GHz. A Cascade W-band calibration substrate was used to perform an LRRM probe-tip calibration for these measurements. For large-signal power measurements, high frequency signal was generated with a QuinStar frequency triple and amplified with a Spacek power amplifier (SPW12-10). The set-up was capable of providing ~19mW of power on-wafer at 86GHz. Output power was measured using a Virginia Diodes Erickson PM-4 power meter. The reported power measurements were corrected for the loss of the output probe and connecting waveguide (~1.6dB).

### A. Single-stage power amplifier

The performance of the single-stage PA was measured and compared to the simulation results as shown in Fig. 3 (a) and (b). The DC bias points of  $V_{CC}$ =2.5V,  $I_{C}$ =50mA, and  $I_{B}$ =2mA are set for the PA measurements. Measured

Freq.  $f_{max} \, / \, f_t$  $BW_{3dB}$ Max. Peak mW Pout  $V_{DD}$  or Area Ref. Technology Topology (GHz) (GHz) (GHz)  $S_{21}(dB)$ (dBm) PAE (%)  $V_{CC}(V)$ (mm<sup>2</sup>) $/\text{mm}^2$ 0.14µm GaN 230 / 94 [1] 23.14 24.7 Unit-Cell ~6 12 **HFET** 97 230 / 0.14µm GaN Three-stage 8-way 93.5 ~10 19.0 [1] ~18 33.30 14 **HEMT** 97 Power-combining 0.15µm GaN 91 ~7 ~16 30.79 >20 17.5 2.25 530 [2] Three-Stage Cascades **HEMT** 0.13µmSiGe Three-stage 4-way [3] 62 >10 20.6 20.10 18 1.8 0.72 142 **BiCMOS** Transformer Balun 590 / 294 2-way Series-connected

20.37

23.14

30.4

30.2

9.4

17.5

23

TABLE I – SUMMARY OF RECENT W-BAND POWER AMPLIFIERS

small-signal s-parameter results, as represented in Fig. 3 (a), exhibit a maximum  $S_{21}$  of 9.4dB at 83GHz with a 3-dB bandwidth of 23GHz (72-95GHz). The input power has been swept from -0.5 to 12.8dBm in order to obtain the output power of 9.50 to 20.4dBm at 86GHz as shown in Fig. 3 (b). The single-stage PA exhibits a peak PAE of 30.4% at an output power of 20.4dBm (108.8mW). Fig. 4 (left) shows the IC image of the single-stage PA, with a total chip area of  $448x816\mu m^2$  and core area (excluding DC and RF pads) of  $295x510\mu m^2$  which exhibits a power density (output powers/active chip area) of  $723mW/mm^2$ .

86

86

350

590 /

350

## B. Two-stage power amplifier

0.25µm InP HBT

This

work

The two-stage (back-to-back) PA performance has been also measured and compared to the simulation results as shown in Fig. 4 (c). DC bias points for the first stage are  $V_{CC}$ =3V and  $I_C$ =30mA, and for the second stage are  $V_{CC}$ =3V and  $I_C$ =50mA. Under RF signal drive, the operating voltage can exceeds the  $BV_{CEO}$ , and the PA could support a DC bias of 3.0V. Large signal performance for the two-stage PA has also been measured at 86GHz where the PA shows a peak PAE of 30% at an output power of 23.14dBm (206mW). The PA IC has been designed within a total area of 824x816 $\mu$ m<sup>2</sup> and a core area of 670x618 $\mu$ m<sup>2</sup> which represents a power density of 497mW/mm<sup>2</sup>. Fig. 4 (right) is a photo image for the fabricated two-stage PA IC.

Table-I shows the comparison of the results for the recent high performance PAs at the frequencies around Wband [1-3]. The PA ICs, reported in this paper, have achieved the record PAE of 30.2% with 3-dB bandwidth of 23GHz and high power density of 723mW/mm² using the high speed 0.25µm InP HBT technology and the proposed novel sub-quarter-wavelength balun structure.

We have reported W-band InP power amplifier (PA) ICs designed with  $0.25\mu m$  InP HBT technology. Using a new proposed efficient power combining technique of a sub-quarter-wavelength balun, the two-stage PA IC achieved 30% PAE at an output power of 23.14dBm while the single-stage PA exhibits a wide 3-dB bandwidth of 23GHz as well as high power density of  $723mW/mm^2$ .

307

(723) Power-combining Balun

(497) connected Power-comb.

Two-stage 2-way Series-

0.37

0.67

2.5

3.0

#### ACKNOWLEDGMENT

This work is supported by DARPA Mobile HotSpots program. The author would like to thank to Teledyne Science Company for the PA ICs fabrication.

## REFERENCES

- [1] M. Micovic, A. Kurdoghlian, A. Margomenos, D.F. Brown, K. Shinohara, S. Burnham, I. Milosavljevic, R. Bowen, A.J. Williams, P. Hashimoto, R. Grabar, C. Butler, A. Schmitz, P.J. Willadsen, and D.H. Chow, "92–96 GHz GaN power amplifiers," 2012 IEEE IMS, pp.1,3, 17-22 June 2012.

- [2] A. Brown, K. Brown, J. Chen, K.C. Hwang, N. Kolias, and R. Scott, "W-band GaN power amplifier MMICs," 2011 IEEE IMS, pp.1,4, 5-10 June 2011.

- [3] Z. Yi, and J.R. Long, "A Wideband, Dual-Path, Millimeter-Wave Power Amplifier With 20 dBm Output Power and PAE Above 15% in 130 nm SiGe-BiCMOS," *IEEE JSSC*, vol.47, no.9, pp.1981,1997, Sept. 2012.

- [4] S. Munkyo, M. Urteaga, J. Hacker, A. Young, Z. Griffith, V. Jain, R. Pierson, P. Rowell, A. Skalare, A. Peralta, R. Lin, D. Pukala, and M. Rodwell, "InP HBT IC Technology for Terahertz Frequencies: Fundamental Oscillators Up to 0.57 THz," *IEEE JSSC*, vol.46, no.10, pp.2203,2214, Oct. 2011.

- [5] W. K. Roberts, "A New Wide-Band Balun," *Proceedings of the IRE*, vol.45, no.12, pp.1628,1631, Dec. 1957.

- [6] Y. Youngoo, K. Choi, and K.P. Weller, "DC boosting effect of active bias circuits and its optimization for class-AB InGaP-GaAs HBT power amplifiers," *IEEE Tran. MTT*, vol.52, no.5, pp.1455,1463, May 2004.