## High performance raised source/drain InAs/In0.53Ga0.47As channel metal-oxide-semiconductor field-effect-transistors with reduced leakage using a vertical spacer

Sanghoon Lee, Cheng-Ying Huang, Doron Cohen-Elias, Jeremy J. M. Law, Varistha Chobpattanna et al.

Citation: Appl. Phys. Lett. 103, 233503 (2013); doi: 10.1063/1.4838660

View online: http://dx.doi.org/10.1063/1.4838660

View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v103/i23

Published by the AIP Publishing LLC.

## Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/

Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded

Information for Authors: http://apl.aip.org/authors

metals • ceramics • polymers composites • compounds • glasses

Save 5% • Buy online 70,000 products • Fast shipping

## High performance raised source/drain InAs/In<sub>0.53</sub>Ga<sub>0.47</sub>As channel metal-oxide-semiconductor field-effect-transistors with reduced leakage using a vertical spacer

Sanghoon Lee, <sup>1,a)</sup> Cheng-Ying Huang, <sup>1</sup> Doron Cohen-Elias, <sup>1</sup> Jeremy J. M. Law, <sup>1</sup> Varistha Chobpattanna, <sup>2</sup> Stephan Krämer, <sup>2</sup> Brian J. Thibeault, <sup>1</sup> William Mitchell, <sup>1</sup> Susanne Stemmer, <sup>2</sup> Arthur C. Gossard, <sup>1,2</sup> and Mark J. W. Rodwell <sup>1</sup> Department of Electrical and Computer Engineering, University of California, Santa Barbara, California 93106, USA

<sup>2</sup>Materials Department, University of California, Santa Barbara, California 93106, USA

(Received 18 October 2013; accepted 16 November 2013; published online 3 December 2013)

We demonstrate raised source/drain  $InAs/In_{0.53}Ga_{0.47}As$  metal-oxide-semiconductor field-effect-transistors incorporating a vertical spacer in the high-field region between the channel and the drain. The spacer significantly reduces off-state leakage at a high drain bias  $(V_{DS})$  without increasing the source/drain contact pitch. Subsequently, thinning the InAs layer within the channel further reduces the off-state leakage and subthreshold swing (SS). At  $\sim$ 60 nm gate length and  $V_{DS} = 0.5$  V, devices with a 6 nm/3 nm InAs/In<sub>0.53</sub>Ga<sub>0.47</sub>As channel show 2.7 mS/ $\mu$ m peak transconductance  $(g_m)$  and 125 mV/dec SS, while devices with a 4.5 nm/3 nm InAs/In<sub>0.53</sub>Ga<sub>0.47</sub>As channel show 2.4 mS/ $\mu$ m peak  $g_m$  and 96 mV/dec SS. © 2013 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4838660]

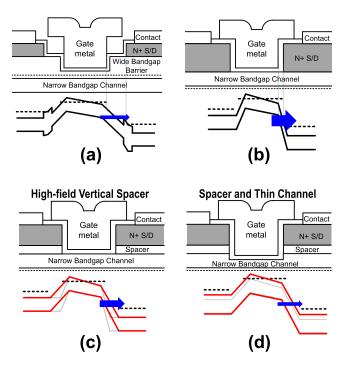

InAs/InGaAs and indium-rich  $In_xGa_{1-x}As$  (x > 0.53) have been widely evaluated as the metal-oxide-semiconductor field-effect transistor (MOSFET) channel for high-performance very large scale integration (VLSI) applications. 1-6 These materials have small bandgap, and high leakage can arise from band-to-band tunneling or from impact ionization in the high-field gate-drain region, degrading off-current and subthreshold swing (SS).7 In metal-oxide-semiconductor high-electron-mobility transistor (MOS-HEMT)<sup>2,3</sup> structures (Figure 1(a)), under bias, the drain depletion edge moves laterally away from gate edge, reducing the drain field, and thereby reducing band-band tunneling, impact ionization, and drain-induced barrier lowering (DIBL). To accommodate this lateral depletion region, the N+ source/drain (S/D) separation must significantly exceed the gate length and contact pitch, which reduces the transistor packing density in VLSI. Using epitaxial regrowth processes, 5,10 a raised N+ source and drain can be aligned within a few nm of the gate edges (Figure 1(b)), enabling the small S/D contact pitch necessary for VLSI, but the gate-drain depletion distance is small and the drain field is large. This increases both leakage and short-channel effects at a given gate length  $(L_{g})^{5}$

Here, we report raised S/D InAs/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs using an undoped vertical spacer (Figure 1(c)) in the high-field region between the channel and the N+ drain. Without increasing the S/D contact pitch, the vertical spacer reduces the drain field, and therefore off-state leakage significantly decreases at a high drain bias ( $V_{DS}$ ). For a short channel (60 nm- $L_g$ ), a 6 nm/3 nm InAs/ In<sub>0.53</sub>Ga<sub>0.47</sub>As channel device with an 8 nm vertical spacer shows 2.7 mS/ $\mu$ m peak transconductance ( $g_m$ ) and 125 mV/dec SS at  $V_{DS} = 0.5$  V. By then thinning the InAs channel (Figure 1(d)) we further improve the off-state characteristics through increased

quantized bandgap and through better gate control, at

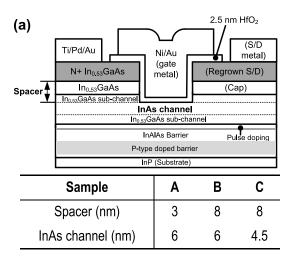

The epitaxial layers for sample A, grown on semiinsulating InP by solid source molecular beam epitaxy, include a 50 nm unintentionally doped (U.I.D) InAlAs buffer, a 250 nm  $1.0 \times 10^{17}$  cm<sup>-3</sup> P-doped InAlAs barrier, a 100 nm U.I.D InAlAs barrier, a 2 nm N-doped  $(2.0 \times 10^{12} \text{ cm}^{-2})$ InAlAs pulse-doping layer, a 5 nm U.I.D InAlAs setback, a 3 nm In<sub>0.53</sub>Ga<sub>0.47</sub>As sub-channel, a 6 nm InAs channel (strained), a 3 nm In<sub>0.53</sub>Ga<sub>0.47</sub>As upper cladding, and a 5 nm  $5 \times 10^{19} \,\mathrm{cm}^{-3}$  N-type doped  $\mathrm{In}_{0.53}\mathrm{Ga}_{0.47}\mathrm{As}$  cap. For samples B and C the cap is 5 nm U.I.D.  $In_{0.53}Ga_{0.47}As$ . To form dummy gates, ~150 nm hydrogen silsesquioxane (HSQ) was spun and patterned by e-beam lithography. To form the N+ S/D, 60 nm Si-doped  $(4 \times 10^{19} \text{ cm}^{-3})$  In<sub>0.53</sub>Ga<sub>0.47</sub>As was then selectively regrown by metal organic vapor deposition (MOCVD) on the cap layer. Device mesas were isolated and the dummy gates removed in buffered oxide etch. For all samples, in the gate region, the exposed cap and upper cladding layers were then removed by digital etching.<sup>5,8</sup> For sample C the upper 1.5 nm of the InAs channel was also removed by digital etching. The samples were then immediately transferred into the atomic layer deposition (ALD) chamber, and pre-cleaned/passivated by alternating cycles of N<sub>2</sub> plasma and of trimethylaluminum (TMA). HfO2 gate dielectric was then deposited. The samples were then annealed at 400 °C in forming gas (5% H<sub>2</sub>/95% N<sub>2</sub>) for 15 min. Ni/Au was thermally deposited as the gate electrode, and Ti/Pd/Au S/D contacts defined by liftoff. Figure 2(a) illustrates a device schematic cross-section. Defining the vertical distance between the N + S/D and the InAs channel as the spacer, the spacer and the InAs thicknesses for sample A, B, and C are listed in the table of Figure 2(a).

<sup>55</sup> nm- $L_g$ , a 4.5 nm/3 nm InAs/ In<sub>0.53</sub>Ga<sub>0.47</sub>As channel device with an 8 nm vertical spacer shows 2.4 mS/ $\mu$ m peak transconductance ( $g_m$ ), 130 mV/V DIBL and 96 mV/dec SS, again at  $V_{DS} = 0.5$  V.

<sup>&</sup>lt;sup>a)</sup>Electronic mail: sanghoon\_lee@ece.ucsb.edu.

FIG. 1. Structures and energy band diagrams of a III-V MOS-HEMT (a) and of a raised S/D MOSFET (b). Leakage is reduced using vertical spacers (c) and thinner channels (d). The dotted lines indicate electron quasi-Fermi level. The band-to-band tunneling rate is qualitatively illustrated with the thicknesses of arrows.

Figure 2(b) shows a cross-sectional HAADF-STEM of a 55 nm- $L_g$  device (*sample C*). The STEM inset shows 2.5 nm HfO<sub>2</sub>, a 0.5 nm interfacial layer formed by the *in-situ*

FIG. 2. (a) The schematic cross-section of the device structure. The table defines the differences between the three experimental samples. (b) HAADF-STEM cross-sections of a 55 nm- $L_g$  device of sample C.

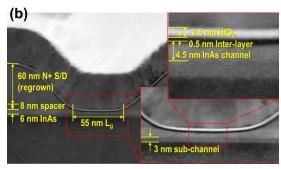

FIG. 3.  $I_D$ - $V_{GS}$  characteristics of Samples A and B at  $\sim$ 75 nm  $L_g$ . Line plus symbol refers to *sample* B and just line refers to *sample* A

$N_2$ /TMA pre-treatment, a 4.5 nm InAs channel (not relaxed) and an 3 nm In<sub>0.53</sub>Ga<sub>0.47</sub>As sub-channel.

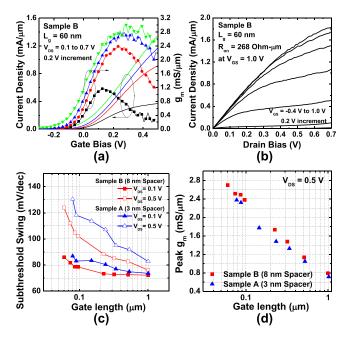

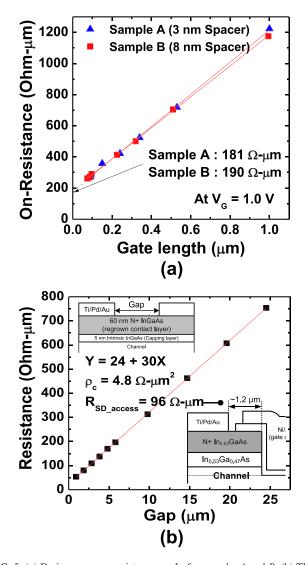

We first compare samples A and B. In the transfer characteristics at  $\sim$ 75 nm  $L_g$  (Figure 3), the 8 nm spacer in the drain high-field region reduces the off-state leakage by 5:1 at  $V_{DS}=0.5\,\mathrm{V}$  and  $V_{GS}=-0.3\,\mathrm{V}$  when compared to the 3 nm spacer. Figures 4(a) and 4(b) show transfer and output characteristics for a 60 nm- $L_g$  device of sample B. Its peak  $g_m$  is  $2.7\,\mathrm{mS}/\mu\mathrm{m}$  at  $V_{DS}=0.5\,\mathrm{V}$  and its  $R_{on}$  is  $268\,\Omega$   $\mu\mathrm{m}$  at  $V_{GS}=1.0\,\mathrm{V}$ . Figure 4(c) shows SS versus  $L_g$  for samples A and B. At  $V_{DS}=0.5\,\mathrm{V}$ , sample B shows 10%-15% improved SS at all gate lengths. Figure 4(d) compares peak  $g_m$  versus  $L_g$  for samples A and B; spacers as thick as 8 nm only negligibly affect the peak  $g_m$ . Figure 5(a) shows on-resistance ( $R_{on}$ ) in terms of gate length for sample A and B. On-resistances for

FIG. 4. (a) Drain current and transconductance vs.  $V_{GS}$  for sample B. (b) Common-source characteristics for sample B showing 1.8 mA/ $\mu$ m maximum  $I_D$ . (c) Subthreshold swing vs.  $L_g$ , at 100 mV and 500 mV  $V_{DS}$ , for samples A and B. (d) Peak transconductance vs.  $L_g$ , at 500 mV  $V_{DS}$ , for samples A and B.

FIG. 5. (a) Drain-source on-resistance vs.  $L_g$  for samples A and B. (b) TLM measurement for the N+ S/D and contacts.

sample A and B, interpolated at the zero gate length, are 181 and 190  $\Omega$   $\mu$ m, respectively, and their discrepancy is within fitting error. This, again, confirms adding the 8 nm spacer layer does not degrade on-state performance by increasing  $R_{on}$ . From transmission line method (TLM) measurement for regrown S/D (Figure 5(b)), the S/D specific contact resistivity is 4.8  $\Omega$   $\mu$ m<sup>2</sup> and sheet resistance ( $R_{sheet}$ ) of the regrown S/D is 30  $\Omega$ /sq. The large 1.2  $\mu$ m distances between the gate edges and the S/D contacts contribute 96  $\Omega$   $\mu$ m to  $R_{on}$  and degrade  $g_m$  by  $\sim$ 11%.

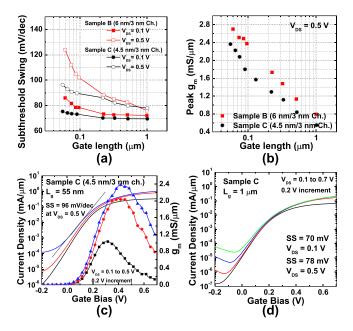

We now compare 6 nm- (sample B) and 4.5 nm-thick-InAs channel devices (sample C). Figure 6(a) compares SS as a function of  $L_g$  for samples B and C. The thin InAs channel (sample C) has significantly improved SS at high  $V_{DS}$  and small  $L_g$ , which we attribute to better electrostatic control and the larger quantized bandgap. The quantized bandgaps for sample B and C, computed from a self-consistent 1-D Schrödinger and Poisson solver, are  $\sim 0.44 \, \mathrm{eV}$  and  $\sim 0.50 \, \mathrm{eV}$ , respectively. Figure 6(b) shows peak  $g_m$  in terms of  $L_g$ . The peak  $g_m$  of sample C is  $\sim 10\%$  smaller than that of sample B at every gate length. This is possibly due to increased surface roughness scattering. Figure 6(c) shows a transfer characteristic of a 55 nm- $L_g$  device for sample C. At  $V_{DS} = 0.5 \, \mathrm{V}$ , its

FIG. 6. (a) Subthreshold swing vs.  $L_g$ , at  $100 \,\mathrm{mV}$  and  $500 \,\mathrm{mV}$   $V_{DS}$ , for samples B and C. (b) Peak transconductance vs.  $L_g$ , at  $500 \,\mathrm{mV}$   $V_{DS}$ , for samples B and C. (c)  $I_D\text{-}V_{GS}$  characteristics and transconductance of sample C at  $L_g = 55 \,\mathrm{nm}$ . (d)  $I_D\text{-}V_{GS}$  characteristics of sample C at  $L_g = 1 \,\mu\mathrm{m}$ .

SS is  $96 \,\mathrm{mV/dec}$  and peak  $g_m$  is 2.4 mS/ $\mu$ m. Defined  $I_D = 1 \,\mu\mathrm{A/\mu m}$ , the threshold voltage  $(V_T)$  is  $60 \,\mathrm{mV}$  and DIBL is  $130 \,\mathrm{mV/V}$ . Figure 6(d) plots the transfer curve for an  $1 \,\mu\mathrm{m-}L_g$  device of sample C. Its SS at  $V_{DS} = 0.1 \,\mathrm{V}$  is  $70 \,\mathrm{mV/dec}$  from which its interfacial trap density  $(D_{it})$  is determined to be  $\sim 5 \times 10^{12} \,\mathrm{/cm^2}$  eV. Its gate leakage  $(I_G)$  is less than  $0.1 \,\mathrm{A/cm^2}$  at relevant bias conditions (not shown).

In conclusion, we have demonstrated raised S/D InAs/In<sub>0.53</sub>Ga<sub>0.47</sub>As channel MOSFETs using an intrinsic In<sub>0.53</sub>Ga<sub>0.47</sub>As spacer in a high-field region between InAs channel and N+S/D. The devices with an 8 nm spacer shows 5:1 reduced off-state leakage and 10%–15% lower SS at  $V_{DS} = 0.5$  V when compared to those with a 3 nm spacer. The device with a 6 nm/3 nm InAs/In<sub>0.53</sub>Ga<sub>0.47</sub>As channel and 60 nm  $L_g$  shows 2.7 mS/ $\mu$ m peak  $g_m$  and 125 mV/dec SS at  $V_{DS} = 0.5$  V, which is record peak  $g_m$  in any III-V MOSFETs technology to date. Furthermore, by thinning the InAs channel to 4.5 nm, the device with an 8 nm spacer and 55 nm- $L_g$  shows 2.4 mS/ $\mu$ m peak  $g_m$ , 96 mV/dec SS at  $V_{DS} = 0.5$  V, and 130 mV/V DIBL.

The authors gratefully acknowledge support for this work by the Semiconductor Research Corporation through the Nonclassical CMOS Research Center (Task ID 1437.009). A portion of this work was performed in UCSB nanofabrication facility, which is part of the NSF-funded NNIN network.

<sup>&</sup>lt;sup>1</sup>M. Radosavljevic, B. Chu-Kung, S. Corcoran, G. Dewey, M. K. Hudait, J. M. Fastenau, J. Kavalieros, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, W. Rachmady, U. Shah, and R. Chau, Tech. Dig. - Int. Electron Devices Meet. **2009**, 319.

<sup>&</sup>lt;sup>2</sup>D.-H. Kim, J. A. del Alamo, D. A. Antoniadis, J. Li, J.-M. Kuo, P. Pinsukanjana, Y.-C. Kao, P. Chen, A. Papavasiliou, C. King, E. Regan, M. Urteaga, B. Brar, and T.-W. Kim, Appl. Phys. Lett. 101, 223507 (2012).

<sup>&</sup>lt;sup>3</sup>J. Lin, D. A. Antoniadis, and J. A. del Alamo, in 2012 IEEE International Electron Devices Meeting (IEDM) (2012), p. 32.

- <sup>4</sup>T. W. Kim, D. Kim, D. H. Koh, R. J. W. Hill, R. T. P. Lee, M. H. Wong, T. Cunningham, J. A. del Alamo, S. K. Banerjee, S. Oktyabrsky, A. Greene, Y. Ohsawa, Y. Trickett, G. Nakamura, Q. Li, K. M. Lau, C. Hobbs, P. D. Kirsch, and R. Jammy, in 2012 IEEE International Electron Devices Meeting (IEDM) (2012), p. 32.

- <sup>5</sup>S. Lee, C.-Y. Huang, A. D. Carter, D. C. Elias, J. J. M. Law, V. Chobpattana, S. Krämer, B. J. Thibeault, W. Mitchell, S. Stemmer, A. C. Gossard, and M. J. W. Rodwell, Symposium on VLSI Technology (2013), p. T246.

- <sup>6</sup>S. H. Kim, M. Yokoyama, R. Nakane, O. Ichikawa, T. Osada, M. Hata, M. Takenaka, and S. Takagi, Symposium on VLSI Technology (VLSIT) 2013.

- <sup>7</sup>D. Kim, T. Krishnamohan, Y. Nishi, and K. C. Saraswat, in *Proceedings of International Conference on Simulation of Semiconductor Processes and Devices (SISPAD)* (2006), pp. 389–392.

- <sup>8</sup>S. Lee, C. Y. Huang, A. D. Carter, J. J. M. Law, D. C. Elias, V. Chobpattana, B. J. Thibeault, W. Mitchell, S. Stemmer, A. C. Gossard, and M. J. W. Rodwell, in *2013 International Conference on Indium Phosphide and Related Materials (IPRM)* (IEEE, 2013).

- <sup>9</sup>V. Chobpattana, J. Son, J. J. M. Law, R. Engel-Herbert, C. Y. Huang, and S. Stemmer, Appl. Phys. Lett. **102**, 022907 (2013).

- <sup>10</sup>M. Egard, L. Ohlsson, B. M. Borg, F. Lenrick, R. Wallenberg, L.-E. Wernersson, and E. Lind, in 2011 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2011), pp. 13.2.1–13.2.4.