## Reduction of leakage current in In0.53Ga0.47As channel metal-oxidesemiconductor field-effect-transistors using AlAs0.56Sb0.44 confinement layers

Cheng-Ying Huang, Sanghoon Lee, Doron Cohen-Elias, Jeremy J. M. Law, Andrew D. Carter et al.

Citation: Appl. Phys. Lett. 103, 203502 (2013); doi: 10.1063/1.4831683

View online: http://dx.doi.org/10.1063/1.4831683

View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v103/i20

Published by the AIP Publishing LLC.

## Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/

Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded

Information for Authors: http://apl.aip.org/authors

metals • ceramics • polymers composites • compounds • glasses

Save 5% • Buy online 70,000 products • Fast shipping

## Reduction of leakage current in In<sub>0.53</sub>Ga<sub>0.47</sub>As channel metal-oxide-semiconductor field-effect-transistors using AlAs<sub>0.56</sub>Sb<sub>0.44</sub> confinement layers

Cheng-Ying Huang, <sup>1,a)</sup> Sanghoon Lee, <sup>1</sup> Doron Cohen-Elias, <sup>1</sup> Jeremy J. M. Law, <sup>1</sup> Andrew D. Carter, <sup>1</sup> Varistha Chobpattana, <sup>2</sup> Susanne Stemmer, <sup>2</sup> Arthur C. Gossard, <sup>1,2</sup> and Mark J. W. Rodwell <sup>1</sup>

<sup>1</sup>Department of Electrical and Computer Engineering, University of California, Santa Barbara, California 93106, USA

(Received 3 October 2013; accepted 1 November 2013; published online 14 November 2013)

We compare the DC characteristics of planar  $In_{0.53}Ga_{0.47}As$  channel MOSFETs using  $AlAs_{0.56}Sb_{0.44}$  barriers to similar MOSFETs using  $In_{0.52}Al_{0.48}As$  barriers.  $AlAs_{0.56}Sb_{0.44}$ , with  $\sim 1.0\,\mathrm{eV}$  conduction-band offset to  $In_{0.53}Ga_{0.47}As$ , improves electron confinement within the channel. At gate lengths below 100 nm and  $V_{DS}=0.5\,\mathrm{V}$ , the MOSFETs with  $AlAs_{0.56}Sb_{0.44}$  barriers show steeper subthreshold swing (SS) and reduced drain-source leakage current. We attribute the greater leakage observed with the  $In_{0.52}Al_{0.48}As$  barrier to thermionic emission from the  $N+In_{0.53}Ga_{0.47}As$  source over the  $In_{0.53}Ga_{0.47}As/In_{0.52}Al_{0.48}As$  heterointerface. A 56 nm gate length device with the  $AlAs_{0.56}Sb_{0.44}$  barrier exhibits 1.96 mS/ $\mu$ m peak transconductance and SS = 134 mV/dec at  $V_{DS}=0.5\,\mathrm{V}$ . © 2013 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4831683]

Driven by the potential for improved on-current over Si,  $InAs/In_xGa_{1-x}As$  and  $In_xGa_{1-x}As$  channel materials are being investigated to replace Si in future generations of CMOS VLSI. To date, most reported III-V MOSFETs grown lattice-matched to InP use  $In_{0.52}Al_{0.48}As$  lower electron confinement (barrier) layers. For this barrier layer, the  $In_{0.53}Ga_{0.47}As/In_{0.52}Al_{0.48}As$  conduction band offset is approximately  $0.52 \, \text{eV}$ . In the heavily doped source and drain regions, at  $4 \sim 8 \times 10^{19} \, \text{cm}^{-3}$  doping, the electron Fermi level,  $E_f$ , is  $\sim 0.3-0.4 \, \text{eV}$  above the conduction band edge of  $In_{0.53}Ga_{0.47}As$ , leaving the  $In_{0.52}Al_{0.48}As$  conduction band energy,  $E_{c,b}$ , only  $\sim 0.1-0.2 \, \text{eV}$  above this Fermi level. This small barrier energy is insufficient to fully confine electrons in the channel; the thermionic emission current density over the barrier can be approximated by

$$J_{th} \approx q(kT/m^*)^{1/2} N_c \exp((E_f - E_{c,b})/kT),$$

(1)

where  $N_c = 2 \times 10^{17}/{\rm cm}^3$  effective density of states of  ${\rm In}_{0.53}{\rm Ga}_{0.47}{\rm As}$  and m\* is the electron effective mass. Given a 0.2 eV barrier, this thermionic current is approximately 5  $\mu{\rm A}/\mu{\rm m}^2$ . Given both small (<100 nm) separations between the N+ source and drain, and significant ( $\sim$ 500 mV) drain-source bias voltage, the drain-source field is large, and electrons thermally emitted from the N+ source into the  ${\rm In}_{0.52}{\rm Al}_{0.48}{\rm As}$  barrier layer are then carried under high field to the drain.

We here show that barrier leakage can be the dominant source of off-state leakage current in short-channel InGaAs MOSFETs with  $In_{0.52}Al_{0.48}As$  barriers and small separations between the N+ source and drain. The magnitude of barrier leakage will depend in detail upon the MOSFET's source-drain structure; presence of an  $In_{0.52}Al_{0.48}As$  upper

In this letter, we demonstrate  $In_{0.53}Ga_{0.47}As$  MOSFETs with an  $AlAs_{0.56}Sb_{0.44}$  barrier layer, grown lattice-matched to an InP substrate, and compare its DC characteristics to that of similar MOSFETs using  $In_{0.52}Al_{0.48}As$  confinement layers. The  $In_{0.53}Ga_{0.47}As/AlAs_{0.56}Sb_{0.44}$  conduction-band offset is  $\sim 1.0\,\mathrm{eV}$ , providing much greater suppression of barrier leakage current than provided by an  $In_{0.53}Ga_{0.47}As/In_{0.52}Al_{0.48}As$  heterointerface. At gate lengths below 100 nm, and for 0.5 V drain-source bias voltage, the MOSFETs with  $AlAs_{0.56}Sb_{0.44}$  barriers show steeper subthreshold swing and reduced off-state drain-source leakage current. A 56 nm gate length device shows  $1.96\,\mathrm{mS}/\mu\mathrm{m}$  transconductance and  $134\,\mathrm{mV/dec}$  subthreshold swing, both measured at  $V_{DS} = 0.5\,\mathrm{V}$ .

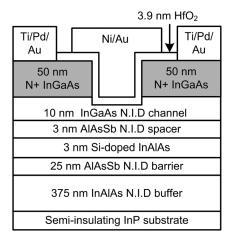

The epitaxial layer structures (Figure 1) were grown on semi-insulating InP substrates using solid-source molecular beam epitaxy. Sample A consists of a 400 nm non-intentionally doped (N.I.D.) In<sub>0.52</sub>Al<sub>0.48</sub>As buffer layer, a 3 nm Si-doped  $(1.3 \times 10^{19} \, \text{cm}^{-3})$  In<sub>0.52</sub>Al<sub>0.48</sub>As pulse doping layer, and a 10 nm In<sub>0.53</sub>Ga<sub>0.47</sub>As channel. Sample B consists of a 375 nm N.I.D.  $In_{0.52}Al_{0.48}As$  buffer layer, a 25 nm N.I.D  $AlAs_{0.56}Sb_{0.44}$ bottom barrier layer, a 3 nm Si-doped  $(1.3 \times 10^{19} \text{ cm}^{-3})$ In<sub>0.52</sub>Al<sub>0.48</sub>As pulse doping layer, a 3 nm N.I.D AlAs<sub>0.56</sub>Sb<sub>0.44</sub> spacer layer, and a 10 nm In<sub>0.53</sub>Ga<sub>0.47</sub>As channel, with details of AlAs<sub>0.56</sub>Sb<sub>0.44</sub> growth as described in Ref. 8. To characterize the interface quality of  $In_{0.53}Ga_{0.47}As/In_{0.52}Al_{0.48}As$  and In<sub>0.53</sub>Ga<sub>0.47</sub>As/AlAs<sub>0.56</sub>Sb<sub>0.44</sub> heterojunctions, InGaAs single quantum well double heterostructures (DH) with 5 nm and 10 nm well thickness were grown and investigated. The detailed structures were presented in Ref. 8. The measured Hall

<sup>&</sup>lt;sup>2</sup>Materials Department, University of California, Santa Barbara, California 93106, USA

barrier layer between the  $In_{0.53}Ga_{0.47}As$  channel and the N+  $In_{0.53}Ga_{0.47}As$  source and drain will reduce the electron density within the channel, increasing  $(E_{c,b}-E_f)$  and thereby reducing the thermionic leakage, while in other reported III-V MOSFETs the separation between the N+ source and drain is significantly greater than the gate length.

a)Electronic mail: cyhuang@ece.ucsb.edu

FIG. 1. Structure of sample B (AlAs $_{0.56}$ Sb $_{0.44}$  barrier). The pulse doping layer is 3 nm,  $1.3 \times 10^{19}$  cm $^{-3}$  Si-doped In $_{0.52}$ Al $_{0.48}$ As. In sample A, the two AlAs $_{0.56}$ Sb $_{0.44}$  layers are omitted and the In $_{0.52}$ Al $_{0.48}$ As buffer layer is 400 nm thick. (N.I.D. = non-intentionally doped).

mobilities are summarized in Table I. The electron mobility for a 10 nm InGaAs quantum well is about ~9500 cm²/V·s at room temperature for both DHs with InAlAs barriers and AlAsSb barriers. As reducing the well thickness from 10 nm to 5 nm, the electron mobility significantly decreased and was lower for InGaAs/AlAsSb DHs than for InGaAs/InAlAs DHs. The decrease in mobility could be the result of stronger interface scattering associated with the higher conduction band offset of AlAsSb barriers, or a rougher interface for InGaAs grown on a higher aluminum content barrier layer. 10–12

To fabricate MOSFETs, hydrogen silsesquioxane (HSQ) dummy gates were patterned by e-beam lithography, and  $\sim 50 \text{ nm}$  thick, *n*-type  $In_{0.53}Ga_{0.47}As$  (Si:  $4 \times 10^{19} \text{ cm}^{-3}$ ) source-drain layers were regrown by metal organic chemical vapor deposition (MOCVD). After MOCVD regrowth, the dummy gates were removed in buffered HF. Channel surface damage caused by regrowth was then removed by two cycles of digital etching. <sup>13</sup> The final In<sub>0.53</sub>Ga<sub>0.47</sub>As channel thickness is  $\sim 7.5 \, \text{nm}$  for both samples. Transistors were then mesa-isolated, were cleaned in buffered HF for 2 min and then in-situ cleaned in an atomic layer deposition (ALD) reactor using alternating cycle of nitrogen plasma and trimethylaluminum pretreatment. 14 Approximately 3.9 nm HfO<sub>2</sub> gate dielectric was then blanket-deposited. Samples were then annealed in forming gas  $(5\% \text{ H}_2/95\% \text{ N}_2)$  at  $400\,^{\circ}\text{C}$  for  $15\,\text{min}$ . 35 nm/120nm thermally evaporated Ni/Au gate metal and 20 nm/50nm/100nm Ti/Pd/Au source/drain metal were then deposited and patterned by liftoff. Because AlAs<sub>0,56</sub>Sb<sub>0,44</sub> is readily oxidized by air exposure and is etched during the mesa

TABLE I. Comparison of Hall mobility between InGaAs/InAlAs and InGaAs/AlAsSb double heterostructures (detailed structures depicted in Ref. 8).

| Well<br>thickness (nm) | Barrier<br>layer | $N_s$ , 300 K ( $10^{12}$ cm $^{-2}$ ) | $\mu$ , 300 K (cm <sup>2</sup> /V·s) |

|------------------------|------------------|----------------------------------------|--------------------------------------|

| 10                     | InAlAs           | 2.28                                   | 9530                                 |

| 10                     | AlAsSb           | 2.40                                   | 9541                                 |

| 5                      | InAlAs           | 2.28                                   | 6785                                 |

| 5                      | AlAsSb           | 2.13                                   | 4777                                 |

isolation,  $0.75~\mu m$  mesa etch undercut is observed at the edge of the bottom barrier in the final devices. The final gate width determined by scanning electron microscope is  $\sim 23.5~\mu m$  (25  $\mu m$  as drawn) for sample B.

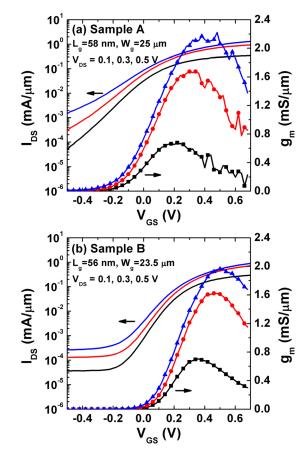

Figure 2 shows the transfer characteristic of sample A and sample B, at 58 nm and 56 nm gate lengths ( $L_o$ ) respectively. At  $V_{DS} = 0.5 \text{ V}$ , sample A shows 2.2 mS/ $\mu$ m peak transconductance and 242 mV/dec subthreshold swing (SS), while sample B shows 1.96 mS/µm peak transconductance and  $134 \,\mathrm{mV/dec}$  SS. The drain-source leakage current ( $I_{DS}$ at, e.g.,  $V_{GS} = -0.2$  to -0.4 V) is significantly reduced in sample B. The slightly reduced transconductance of sample B may be due to reduced mobility arising from stronger interface roughness scattering of InGaAs/AlAsSb heterojunction.8 As a function of gate lengths, threshold voltages are 0.1-0.15 V more positive for sample B, possibly a result of the increased eigenstate energy in the InGaAs channel, also due to stronger quantum confinement.

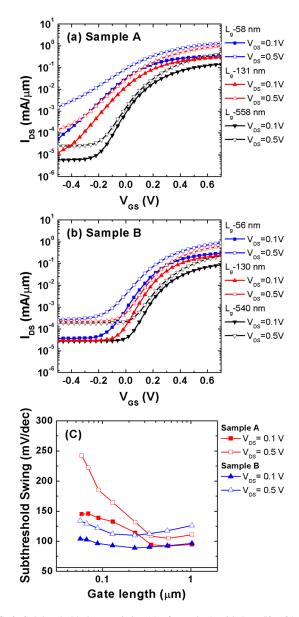

Figures 3(a) and 3(b) compare the subthreshold characteristics of samples A and B as a function of gate lengths. With sample A (InAlAs barrier), the off-state drain leakage current ( $I_{DS}$  at, e.g.,  $V_{GS} = -0.2$  to -0.4 V) increases rapidly as  $L_g$  is reduced from 558 nm to 131 nm and 58 nm, particularly for  $V_{DS} = 0.5$  V. At short gate lengths, 130 nm and 56 nm  $L_g$ , sample B (AlAsSb barrier) exhibits much smaller off-state leakage than sample A. For  $L_g < 200$  nm, sample B shows considerably smaller subthreshold swing as shown in Figure 3(c). Sample B shows a residual off-state leakage of

FIG. 2. Transfer characteristics of (a) sample A with  $L_g = 58 \,\mathrm{nm}$  and (b) sample B with  $L_g = 56 \,\mathrm{nm}$  at  $V_{DS}$  of 0.1, 0.3, and 0.5 V.

FIG. 3. Subthreshold characteristics (a) of sample A with  $L_g$  = 58, 131, and 558 nm and (b) of sample B with  $L_g$  = 56, 130, and 540 nm. (c) Subthreshold swing vs.  $L_g$  for sample A and sample B at  $V_{DS}$  = 0.1 V and  $V_{DS}$  = 0.5 V.

$3-4 \times 10^{-5}$  mA/ $\mu$ m at  $V_{DS} = 0.1$  V and  $2-3 \times 10^{-4}$  mA/ $\mu$ m at  $V_{DS} = 0.5$  V. This background leakage has an approximately linear (Ohmic) variation with  $V_{DS}$ , and is only weakly dependent upon the gate length; on other experimental samples, we have observed similar background leakage when the isolation mesa etch depth is insufficient.

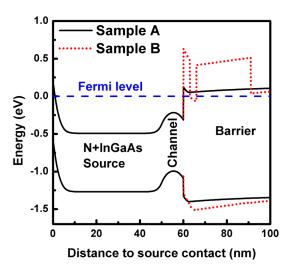

Off-state drain leakage current arising from simple electrostatics (excessive channel or gate dielectric thickness) or from source-drain or band-band tunneling would not show the strong observed dependence upon the energy offset of the lower barrier. Leakage by thermal emission from the N+ source over the channel-barrier interface should however show a strong dependence upon the barrier energy, consistent with Figures 2 and 3. Figure 4 shows a computed energy band diagram drawn vertically through the MOSFET regrown N+ In<sub>0.53</sub>Ga<sub>0.47</sub>As source (Si-doped:  $4 \times 10^{19} \, \mathrm{cm}^{-3}$ ), through the un-doped In<sub>0.53</sub>Ga<sub>0.47</sub>As channel, and into In<sub>0.52</sub>Al<sub>0.48</sub>As or AlAs<sub>0.56</sub>Sb<sub>0.44</sub> bottom barrier layer. The band diagram is calculated by self-consistent 1-D Schrödinger and Poisson

FIG. 4. Energy band diagram of sample A ( $In_{0.52}Al_{0.48}As$  barrier) and sample B ( $AlAs_{0.56}Sb_{0.44}$  barrier) with raised N+ InGaAs source/drain (Si-doped:  $4\times10^{19}\,\mathrm{cm}^{-3}$ ), drawn on a vertical line passing through the N+ source, the InGaAs channel, and the InAlAs or AlAsSb bottom barrier. Given the high source doping, the InAlAs barrier energy lies only  $\sim 0.1-0.2\,\mathrm{eV}$  above the Fermi energy, while AlAsSb barrier provides  $\sim 0.6-0.7\,\mathrm{eV}$  carrier confinement.

equation. The conduction band energy and valence band energy of AlAs $_{0.56}$ Sb $_{0.44}$  barrier are linearly interpolated from unstrained AlAs and AlSb layers without considering bowing parameter. As shown in Figure 4, the electron Fermi level lies  $\sim 0.4\,\text{eV}$  above the conduction band of the N+ source and  $\sim 0.2\,\text{eV}$  above that of the un-doped InGaAs channel. The In $_{0.52}$ Al $_{0.48}$ As layer provides only  $\sim 0.1-0.2\,\text{eV}$  barrier above the electron Fermi level, insufficient to strongly suppress thermal emission from the N+ source. Using an oxide barrier, 5 or a wide band-gap semiconductor barrier will potentially reduce this barrier leakage current. Replacement of the In $_{0.52}$ Al $_{0.48}$ As barrier with AlAs $_{0.56}$ Sb $_{0.44}$  increases the barrier energy by  $\sim 0.5\,\text{eV}$ , and should suppress this thermal emission by ca.  $10^8$ : 1.

In summary, we have demonstrated planar  $In_{0.53}Ga_{0.47}As$  MOSFETs with a wide band-gap  $AlAs_{0.56}Sb_{0.44}$  barrier layer. A device with 56 nm gate length shows the peak transconductance about 1.96 mS/ $\mu$ m and SS = 134 mV/dec, both at  $V_{DS} = 0.5$  V. Replacing the  $In_{0.52}Al_{0.48}As$  barrier with  $AlAs_{0.56}Sb_{0.44}$  greatly reduces the drain-source leakage current, which we attribute to suppression of the carrier injection from the N+ InGaAs source into the back barrier.

The authors gratefully acknowledge support for this work by the Semiconductor Research Corporation through the Nonclassical CMOS Research Center (Task ID 1437.009). A portion of this work was performed in UCSB nanofabrication facility, which is part of the NSF-funded NNIN network.

<sup>&</sup>lt;sup>1</sup>M. Radosavljevic, B. Chu-Kung, S. Corcoran, G. Dewey, M. K. Hudait, J. M. Fastenau, J. Kavalieros, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, W. Rachmady, U. Shah, and R. Chau, in *IEEE International Electron Devices Meeting (IEDM)* (IEEE, 2009), p. 319.

<sup>2</sup>D.-H. Kim, J. A. del Alamo, D. A. Antoniadis, J. Li, J.-M. Kuo, P. Pinsukanjana, Y.-C. Kao, P. Chen, A. Papavasiliou, C. King, E. Regan, M. Urteaga, B. Brar, and T.-W. Kim, Appl. Phys. Lett. 101, 223507 (2012).

- <sup>3</sup>J. J. Gu, X. W. Wang, H. Wu, J. Shao, A. T. Neal, M. J. Manfra, R. G. Gordon, and P. D. Ye, in *IEEE International Electron Devices Meeting (IEDM)* (IEEE, 2012), p. 633.

- <sup>4</sup>M. Egard, L. Ohlsson, B. M. Borg, F. Lenrick, R. Wallenberg, L.-E. Wernersson, and E. Lind, in *IEEE International Electron Devices Meeting (IEDM)* (IEEE, 2011), p. 303.

- <sup>5</sup>S. Kim, M. Yokoyama, N. Taoka, R. Nakane, T. Yasuda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, IEEE Trans. Electron Devices **60**, 2512 (2013).

- <sup>6</sup>S. Lee, C.-Y. Huang, A. D. Carter, D. C. Elias, J. J. M. Law, V. Chobpattana, S. Krämer, B. J. Thibeault, W. Mitchell, S. Stemmer, A. C. Gossard, and M. J. W. Rodwell, in *Symposium on VLSI Technology (VLSIT)* (IEEE, 2013), p. T246.

- <sup>7</sup>I. Vurgaftman, J. R. Meyer, and L. R. Ram-Mohan, J. Appl. Phys. **89**, 5815 (2001).

- <sup>8</sup>C. Y. Huang, J. J. M. Law, H. Lu, M. J. W. Rodwell, and A. C. Gossard, MRS Online Proc. Library **1561**, mrss13-1561-cc01-10 (2013).

- <sup>9</sup>J. M. Li, J. J. Wu, X. X. Han, Y. W. Lu, X. L. Liu, Q. S. Zhu, and Z. G. Wang, Semicond. Sci. Technol. **20**, 1207 (2005).

- <sup>10</sup>N. Ikarashi, M. Tanaka, H. Sakaki, and K. Ishida, Appl. Phys. Lett. **60**, 1360 (1992).

- <sup>11</sup>P. M. Petroff, R. C. Miller, A. C. Gossard, and W. Wiegmann, Appl. Phys. Lett. 44, 217 (1984).

- <sup>12</sup>C. R. Bolognesi, H. Kroemer, and J. H. English, Appl. Phys. Lett. **61**, 213 (1992).

- <sup>13</sup>S. Lee, C. Y. Huang, A. D. Carter, J. J. M. Law, D. C. Elias, V. Chobpattana, B. J. Thibeault, W. Mitchell, S. Stemmer, A. C. Gossard, and M. J. W. Rodwell, in 2013 International Conference on Indium Phosphide and Related Materials (IEEE, 2013), p. 1.

- <sup>14</sup>V. Chobpattana, J. Son, J. J. M. Law, R. Engel-Herbert, C. Y. Huang, and S. Stemmer, Appl. Phys. Lett. **102**, 022907 (2013).