## Performance Impact of Post-Regrowth Channel Etching on InGaAs MOSFETs Having MOCVD Source-Drain Regrowth

Andrew D. Carter<sup>1</sup>, S. Lee<sup>1</sup>, D.C. Elias<sup>1</sup>, C.-Y. Huang<sup>1</sup>, J. J. M. Law<sup>1</sup>, W. J. Mitchell<sup>1</sup>, B. J. Thibeault<sup>1</sup>, V. Chobpattana<sup>2</sup>, S. Stemmer<sup>2</sup>, A. C. Gossard<sup>1</sup>, and M. J. W. Rodwell<sup>1</sup>

<sup>1</sup>ECE Department, <sup>2</sup>Materials Department, University of California, Santa Barbara, CA 93106-9560 Phone: 805-893-3273, Fax: 805-893-3262, Email: adc@ece.ucsb.edu

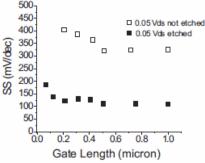

Given low interface trap densities and low access resistances, InGaAs MOSFETs can provide greater onstate current than silicon MOSFETs at the same effective oxide thickness (EOT), and are thus strong candidates for use in VLSI. Transconductance as high as 2.1 mS/μm (V<sub>dt</sub>=0.5 V) with 115 mV/decade (V<sub>dt</sub>=0.5 V) subthreshold swing has been reported<sup>2</sup> in planar III-V MOSFETs using a gate recess etch through the N+ InGaAs contact layer. It remains to be established whether the necessary etch depth control can be obtained at VLSI integration scales and 10-20 nm gate lengths. Using self-aligned regrowth of the N+ source and drain, III-V MOSFETs can be fabricated without requiring this gate recess etch;<sup>3</sup> 1.9 mS/µm (V<sub>dt</sub>=1 V) with 116 mV/decade (V<sub>dt</sub>=0.05 V) subthreshold swing was reported in a 55 nm Lg InGaAs MOSFET with MOCVD source-drain regrowth. 4 Note that no postregrowth etching of the channel surface is reported in (4). We have recently found<sup>5</sup> that InGaAs MOSFETs using MBE source-drain regrowth, subthreshold swing and transconductance are substantially improved by removing a 5 nm N+ InGaAs channel cap post-regrowth and immediately prior to gate dielectric deposition, suggesting damage to the channel surface during regrowth. Here, we report similar findings for MOCVD regrowth. We fabricated 65 nm Lg In<sub>0.53</sub>Ga<sub>0.47</sub>As surface-channel MOSFETs in a gate-last process with self-aligned raised InGaAs S/D access regions formed by MOCVD regrowth. Removal of ~ 2.4 nm of the channel surface by digital etching improved the transconductance from 1.1 to 1.58 mS/ $\mu$ m (65 nm  $L_g$ ,  $V_{dz}$ =0.5 V), and reduced the subthreshold swing from 326 to 110 mV/dec (1 µm Lg, Vdt=0.05 V). These results suggest that substantial surface damage arises, and must be addressed, in MOCVD regrowth III-V MOSFET processes.

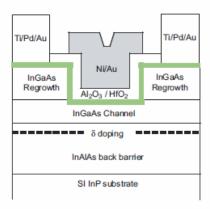

The epitaxial layer structure is similar to that found in (3). Approximately 70 nm of PECVD SiO<sub>2</sub> was deposited on the sample for dummy gate formation, gate stripes patterned using electron beam lithography, transferred to the SiO<sub>2</sub> using SF<sub>6</sub>/Ar ICP etching. Immediately prior to MOCVD regrowth, <sup>4</sup> the semiconductor surface was oxidized in UV ozone for 30 minutes, and etched in H<sub>2</sub>O:HCl. MOCVD regrowth of ~30 nm In<sub>0.53</sub>Ga<sub>0.47</sub>As n-type (Si-doped ~ $4 \cdot 10^{19}$  cm<sup>-3</sup>) used TBA, TMI, TMG, and disilane (400 ppm), at 600°C growth temperature. Devices were isolated using both citric acid:H<sub>2</sub>O:H<sub>2</sub>O<sub>2</sub> and H<sub>2</sub>O<sub>2</sub>:H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O. Dummy gates were removed in buffered HF. One sample was exposed to UV ozone for 15 minutes, the InGaAs oxide etched in H<sub>2</sub>O:HCl for 1 minute, and oxidized again for 15 minutes. UV ozone-exposed and unexposed samples were then treated with buffered HF prior to dielectric deposition. Each oxidation/etch removed approximately 1.2 nm of In<sub>0.53</sub>Ga<sub>0.47</sub>As.<sup>5</sup> Samples were then immediately loaded into the atomic layer deposition loadlock. After *in-situ* H<sub>2</sub>/TMA treatment, <sup>6</sup> ~1 nm Al<sub>2</sub>O<sub>3</sub> and ~4 nm HfO<sub>2</sub> were deposited (EOT ≈ 1.35 nm). Gate metal liftoff was thermally evaporated 50/160 nm Ni/Au. Source/drain region oxide was etched in buffered HF and source-drain metallization was electron beam evaporation of Ti/Pd/Au, 20/60/75 nm.

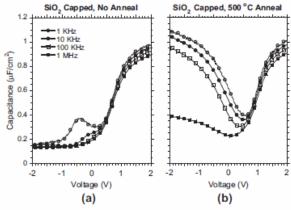

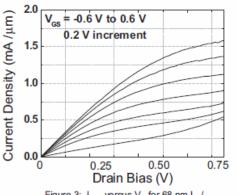

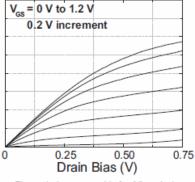

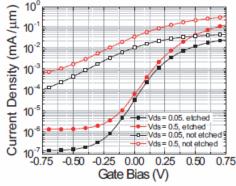

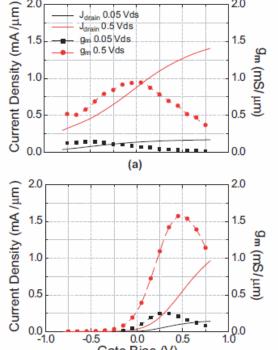

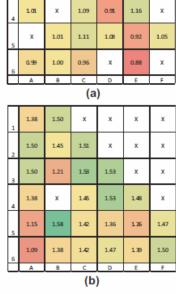

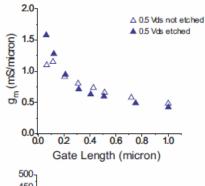

Further investigating process damage, off-wafer frequency-dependent CV data on 5 nm Al<sub>2</sub>O<sub>3</sub> MOS capacitors were measured with one capacitor experiencing 500 °C anneal in a rapid thermal annealer to simulate source-drain regrowth conditions. The annealed capacitor showed greatly increased frequency dispersion at biases below threshold, suggesting increased interface trap density. FETs without channel etching have a threshold voltage of -0.69 V by linear extrapolation, a current density of 0.58 mA/ $\mu$ m at  $V_{ds}$  = 0.5 V and  $V_{gs}$  –  $V_{th}$  = 0.5 V, and peak transconductance of 1.1 mS/ $\mu$ m at a  $V_{ds}$  = 0.5 V. 65 nm FETs with channel etching have a threshold voltage of 0.15 V by linear extrapolation, a current density of 0.78 mA/ $\mu$ m at  $V_{ds}$  = 0.5 V and  $V_{gs}$  –  $V_{th}$  = 0.5 V, and peak transconductance of 1.58 mS/ $\mu$ m at  $V_{ds}$  = 0.5 V. 1  $\mu$ m FETs without channel etching have a subthreshold swing of 326 mV/dec at  $V_{ds}$  = 0.05 V, compared to 110 mV/dec when the channel is etched. For the digitally etched sample, transmission line measurements of the metal/regrowth interface show 19.8 ohm-micron and 46 ohm/sq for the metal-semiconductor contact resistance and N+ regrowth sheet resistance, respectively. The short-  $L_g$  FETs suffer from severe short channel effects, likely due to the large delta doping below the channel. This can be addressed by decreasing or removing the delta doping, more deeply etching the channel, and decreasing the dielectric EOT. Future work will investigate the cause of surface damage.

Acknowledgements: This research was supported by the SRC Non-classical CMOS Research Center (Task 1437.009). A portion of this work was done in the UCSB nanofabrication facility, part of NSF funded NNIN network

<sup>1</sup>M. J. W. Rodwell, et al, Device Research Conference (DRC) 2010. <sup>2</sup>D.H. Kim et al, International Electron Device Meeting (IEDM), 2012. <sup>3</sup>A.D. Carter et al, DRC 2011. <sup>4</sup>M. Egard et al, IEDM 2011. <sup>5</sup> S.Lee et al, Indium Phosphide and Related Materials Conference (IPRM) 2013, accepted. <sup>6</sup>V. Chobpattana et al. Appl. Phys. Letters. 102, (2013). 022907. <sup>7</sup>R. Engel-Herbert, et al. J. Appl. Phys. 108 (2010) 124101.

Figure 1: Schematic cross-section of the gate last MOSFET. Green indicates regions digitally etched prior to gate dielectric deposition.

2.0

1.5

Figure 2: MOSCAP CV epi, SiO2-capped a) 500°C annealed and (b) not annealed, prior to cap stripping and 5 nm ALD Al2O3 deposition.

Figure 3:  $J_{drain}$  versus  $V_{ds}$  for 68 nm  $L_g/$  9.5  $\mu$ m  $W_g$  FET, no channel etching.

J<sub>drain</sub> 0.05 Vds

J<sub>drain</sub> 0.5 Vds

gm 0.05 Vds

g<sub>m</sub> 0.5 Vds

2.0

1.5

Figure 4:  $J_{\text{drain}}$  versus  $V_{\text{ds}}$  for 65 nm  $L_g/$  9.5  $\mu$ m  $W_g$  FET, channel etch applied.

X

X

х

1.10 0.90 X

0.89 0.92 1.00

0.99

0.90 1.10 X

Figure 5:J $_{\text{dmin}}$  versus V $_{\text{gs}}$  for 1 micron L $_{\text{g}}$  FETs, channel etching and no etching.

Figure 6:J<sub>drah</sub> versus V<sub>ss</sub> for a) 68 nm L<sub>s</sub> FET, no channel etching b) 95%nn+2,992%3/ha7/h3/%3/h49 ©2013 IEEE

Gate Bias (V)

(b)

Figure 7: Peak g<sub>m</sub> wafer map (mS/micron), V<sub>ds</sub>= 0.5 V a) no channel etching, ~ 110 nm L<sub>g</sub> b) channel etching, ~ 65 nm L<sub>g</sub>

Figure 8: Peak transconductance and minimum subthreshold swing versus gate length for channel etched and not etched samples.