# An 18-GHz Continuous-Time $\Sigma$ - $\Delta$ Analog-Digital Converter Implemented in InP-Transferred Substrate HBT Technology

Shrinivasan Jaganathan, Sundararajan Krishnan, Dino Mensa, Thomas Mathew, Yoram Betser, Yun Wei, Dennis Scott, Miguel Urteaga, and Mark Rodwell

Abstract—We report an 18-GHz clock-rate second-order continuous-time  $\Sigma$ - $\Delta$  analog-digital converter (ADC) implemented using InP-transferred substrate HBTs. Under two-tone test conditions, the ADC achieved 43 dB and 33 dB SNR at signal frequencies of 500 MHz and 990 MHz, respectively. The IC occupied 1.95 mm² die area and dissipated  $\sim$ 1.5 W.

Index Terms—ADC, delta-sigma, heterojunction bipolar transistor, substrate transfer.

# I. INTRODUCTION

IGH speed analog-to-digital converters (ADCs) find widespread applications in wideband communications and radar receivers. Efforts are being made to move the ADC forward in the signal chain, closer to the antenna. Such efforts depend critically on the ability to digitize wideband signals with very high resolution. This modified architecture should result in a more robust receiver implementation consisting of the ADC followed by DSP hardware and software.

A popular oversampling ADC architecture is based on  $\Sigma$ - $\Delta$  modulation. These achieve high signal/noise ratio (SNR) without requiring high precision in component values or device matching. Moreover, the requirements on the analog anti-aliasing filter are significantly relaxed.  $\Sigma$ - $\Delta$  modulators achieve high resolution by utilizing high sampling rates; a second-order ADC achieves a 15-dB improvement in SNR for every octave increase in sampling rate.

The SNR of a  $\Sigma$ - $\Delta$  modulator depends on the order of the loop filter and the oversampling ratio [1]. While a high-order loop-filter results in a high SNR, it is difficult to design a stable modulator with order greater than two. High SNR can be obtained by using a second-order filter and as high an oversampling ratio as permitted by the technology of implementation. This is our approach. We seek as high a clock rate as is feasible in the technology, so as to obtain a high resolution; an ideal second-order ADC at 18-GHz clock would exhibit 10 effective

Manuscript received January 15, 2001; revised April 12, 2001. This work was supported by the ONR under Grant N00014-98-1-0830.

Publisher Item Identifier S 0018-9200(01)06105-4.

number of bits (ENOB) resolution at 200 MHz and 6.8 ENOB resolution at 500 MHz.

InAlAs/InGaAs transferred-substrate heterojunction bipolar transistors (HBTs) have achieved very high device bandwidths [2], [3], permitting very high speed digital circuits [12]. In bipolar processes, fast, low-offset switches are difficult to implement, and the continuous-time architecture [4] is more readily implemented than the discrete-time, switched-capacitor architecture prevalent in CMOS  $\Sigma$ - $\Delta$  ADCs. Continuous-time  $\Sigma$ - $\Delta$  modulators have been reported with clock rates as high as 3.2 GHz [5] and 5 GHz [6]. Raghavan *et al.* [7] recently reported a fourth-order bandpass delta–sigma modulator operating at a clock rate of 4 GHz. Here we report an 18-GHz clock-rate, second-order continuous-time  $\Sigma$ - $\Delta$  ADC.

# II. DEVICE TECHNOLOGY

We obtained high ADC clock frequencies by using very wide bandwidth bipolar transistors. As with MOS transistors, high HBT cutoff frequencies are obtained by scaling. Scaling for high current-gain cutoff frequencies  $f_{\tau}$  requires thinning the base and collector epitaxial layers, increasing the bias current density, and decreasing the extrinsic emitter resistance [8]. HBTs are typically fabricated using a series of mesa etches; this produces a device whose collector-base junction lies beneath both the emitter stripe and the base Ohmic contacts. Reducing the collector junction width results in reduced base contact dimensions, and the base contact resistivity must then be greatly decreased if low base resistance is to be maintained. By using a substrate transfer step, HBTs can be fabricated with narrow emitter-base and collector-base junctions on opposing sides of the base epitaxial layer [2].

Single heterojunction bipolar transistors (SHBTs) fabricated in the transferred-substrate process use InAlAs emitters, InGaAs base layers, and InGaAs collectors. Devices fabricated using electron-beam lithography have obtained 200 GHz  $f_{\tau}$  [9], over 800 GHz  $f_{\max}$  [2], and 21-dB unilateral power gain at 100 GHz [9]. ICs fabricated in the process to date have used 0.5- $\mu$ m-resolution optical projection lithography, and have obtained simultaneous 295 GHz  $f_{\tau}$  and  $f_{\max}$  [3] for devices with thin base and collector layers. The SHBTs have a low  $\sim$ 1.5-V common-emitter breakdown  $V_{\rm br,ceo}$ , which requires careful control of bias voltages within the ADC. We have recently fabricated double heterojunction bipolar transistors (DHBTs) with InP collectors using the substrate transfer process, and

S. Jaganathan and D. Mensa were with the Department of ECE, University of California, Santa Barbara, CA 93106 USA. They are now with Gtran Inc., Westlake Village, CA 91362 USA.

S. Krishnan, T. Mathew, Y. Wei, D. Scott, M. Urteaga, and M. Rodwell are with the Department of ECE, University of California, Santa Barbara, CA 93106 USA (e-mail: rodwell@ece.ucsb.edu).

Y. Betser was with the Department of ECE, University of California, Santa Barbara, CA 93106 USA. He is now with Anadigics Corporation, Israel.

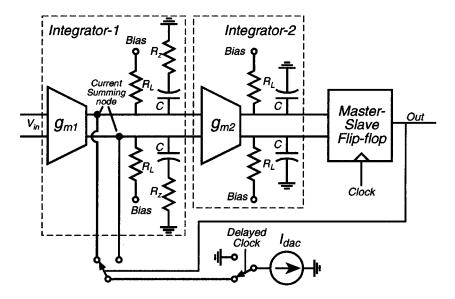

Fig. 1. A block diagram of second-order continuous-time  $\Sigma$ - $\Delta$  ADC.

have obtained  $V_{\rm br,\,ceo} > 5$  V at  $10^5$  A/cm², 165 GHz  $f_{\tau}$ , and 300 GHz  $f_{\rm max}$  [10], but have not yet fabricated ADCs with these transistors. The ADCs reported here use SHBTs with a  $4\times 10^{19}$  cm<sup>-3</sup> Be-doped base of 300 Å thickness and with 2kT band-gap grading. The collector has a 2000 Å thick InGaAs depletion layer, and uses a Schottky collector contact. The HBTs have  $\sim 0.6$ - $\mu$ m emitter junction width and 1.5- $\mu$ m collector junction width.

In mixed-signal ICs, digital circuit switching transients couple to the analog circuits through the power supply or ground connections, degrading the ICs dynamic range. Differential circuits reduce—but do not eliminate—such coupling. In small-scale millimeter-wave ICs [11], circuit-circuit coupling through ground circuit common-lead inductance ("ground bounce") is greatly reduced through use of a microstrip wiring environment, in which all circuit ground-return currents are carried on a low-inductance ground plane on the back surface of the IC. In the substrate transfer process, a continuous, unbroken, ground plane lies under the full IC area, providing a low inductance ground system for low circuit-circuit coupling. The wiring dielectric is a 5- $\mu$ m-thick Benzocyclobutene (BCB) layer with  $\epsilon_r = 2.7$ . All interconnects are microstrip lines, and have a well-controlled and predictable characteristic impedance; a 3- $\mu$ m-width conductor forms a  $Z_0 = 100 \Omega$ transmission line.

# III. CIRCUIT DESIGN

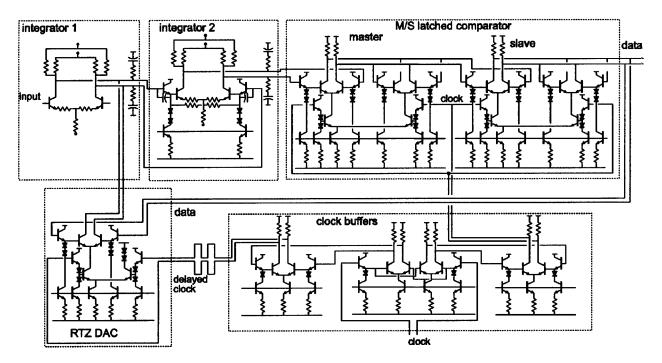

Fig. 1 shows a simplified block diagram of the IC. The ADC consists of two transconductance  $(g_m)$  cells, each followed by a passive integrator. The quantizer is a master—slave flip-flop, while the feedback DAC is a current steering differential amplifier. The error signal is generated by current summing at the output nodes of the first transconductance cell. The entire implementation is differential for low even-order harmonic distortion, high power supply rejection ratio and reduced clock switching noise.

In computer simulations of  $\Sigma$ - $\Delta$  ADCs, several thousand clock cycles must be simulated to obtain, by fast Fourier trans-

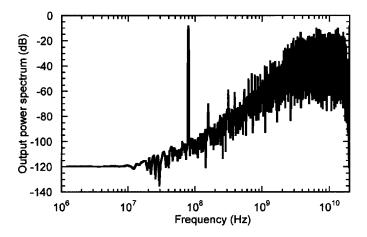

formation (FFT), spectra with the required dynamic range. At the time of IC design, available computers were inadequate for full transistor-level loop simulations, and the preliminary design was instead carried out using system-level simulations using MATLAB. Such simulations indicated the required parameters for each loop element for a desired ADC signal/noise ratio. These parameters were translated into circuit component values using a transistor-level circuit simulator. Fig. 2 shows a simulation of a near-ideal second-order  $\Sigma$ - $\Delta$  ADC with a 20-GHz clock rate. The effects of comparator metastability and dynamic hysteresis, thermal and shot noise, and integrator excess delay are neglected, but the simulation does include the effects of integrator leakage (finite integrator gain), with the integrator transfer functions being modeled as  $A_{int} = A_{DC}/(1+jf/f_0)$ , with  $A_{\rm DC}=30~{\rm dB}$  and  $f_0=50~{\rm MHz}$ . Integrating the noise and signal density from MATLAB over frequency results in 55 dB of SNR for a 312.5 MHz signal. The various circuit imperfections should, however, reduce this SNR considerably.

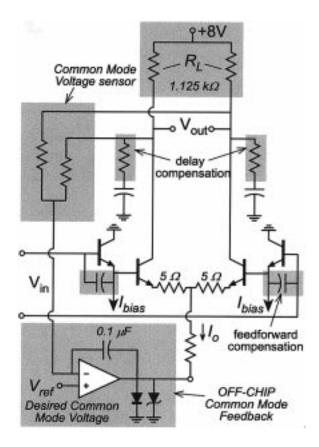

Fig. 3 shows the circuit schematic for the second integrator in the loop. Since noise shaping near dc is limited by the finite dc gain of the integrators [1], high gains are desired. Integrator excess phase delay limits the high frequency noise-shaping and hence limits the maximum oversampling ratio. Low excess phase delay and hence wide integrator bandwidth are desired in addition to high dc gain for high oversampling ratio  $\Sigma$ - $\Delta$  ADCs.

In the absence of PNP transistors in an HBT technology, achieving a high dc gain is challenging. Usually, designers overcome this limitation by employing bootstrapped [5] or negative-resistance loads. These techniques introduce higher order poles, resulting in excess phase delay and thus limiting the oversampling ratio. They also increase the transistor count in the high frequency signal path, which is undesirable in very wideband circuits. Here, high dc gain is obtained simply by using a large pull-up resistive load. This necessitates a large positive power supply voltage and an (off-wafer) common-mode-feedback (CMFB) loop that controls the integrator dc bias. This is

Fig. 2. Simulation result: FFT of the output of an ideal second-order  $\Sigma-\Delta$  modulator loop for  $f_{\rm clock}=20$  GHz,  $f_{\rm signal}=78$  MHz, 1.22 MHz FFT bin (resolution). Integrator leakage is modeled.

important given the small breakdown voltage of the InGaAs collector HBTs.

The integrator is a  $g_m$  stage whose output is loaded by a grounded capacitor (Figs. 1 and 3). Active integrators (using a cascaded pair of  $g_m$  stages whose second stage has a Miller-connected integrating capacitor), used commonly in  $\Sigma$ - $\Delta$  modulator designs, obtain a very high dc gain ( $g_m^2 R_L^2$  vs.  $g_m R_L$ ) but have a lower feasible bandwidth due to the loop-bandwidth and loop-stability considerations associated with the Miller feedback loop. In contrast, the integrator reported here uses a simple  $g_m$  stage loaded by a capacitor, achieving a high bandwidth.

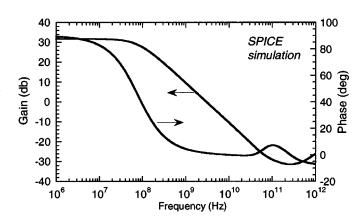

Excess delay due to higher order integrator poles associated with transistor parasitics is partly offset by a zero in the transfer function introduced by placing a resistor in series with the capacitor. Emitter followers (Fig. 3) buffer the integrator inputs, increasing the input impedance and the dc gain. Because the output impedance of the emitter follower is higher than that of the drive point  $(1/j\omega C_{int})$  at high frequencies, the emitter followers are removed from the signal path at high frequencies by feed-forward compensation. The common-mode voltage at the output for CMFB, is sensed with high value on-chip resistors. SPICE simulations (Fig. 4) of the integrator, with all layout parasitics modeled, show a  $(g_m/j\omega C_{int})$  behavior from 40 MHz to  $\sim$ 100 GHz.

The goal of this design is to use the maximum possible clock frequency. Limits to the clock frequency include the uncompensated excess delay accumulated in the signal path, metastability and dynamic hysteresis errors in the quantizer. The excess delay in the signal path includes the delay due to integrator higher order poles, the delay in the interconnects, and the delay in the quantizer decision and the feedback DAC.

A fully differential DAC eliminates feedback errors associated with unequal DAC rise and fall times [5]. However, the DAC is still vulnerable to quantizer metastability errors. Such errors result in the output edge of the quantizer being modulated by the input amplitude. For small quantizer inputs, the quantizer output can take several circuit time-constants to reach the correct logic level. For strong inputs, this delay is reduced. For a quantizer output corresponding to logic 1, the DAC charge delivered to the integrating capacitor varies with the strength of quantizer input

Fig. 3. A schematic of the second integrator in the loop.

Fig. 4. Plot of frequency response of the second integrator.

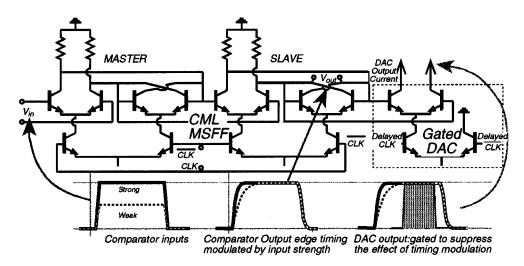

(shown qualitatively in Fig. 5). One method to reduce such errors is to add another latch stage for further regeneration [5]. A second method, used here, is a delayed return-to-zero (RTZ) DAC. The RTZ DAC is gated with a clock pulse delayed such that the DAC is active only in the final 50% of the clock period (Fig. 5). We use a gated DAC because less additional transistors ( $\sim$ 6) are required than for an extra latch stage ( $\sim$ 25).

The use of either an RTZ DAC or an extra latching stage results in an extra half-clock cycle delay in the feedback path, adding to other excess loop delays, and thus limiting the clock rate. Using MATLAB, we observed a 12-dB reduction in SNR with the addition of a half-sample delay (25-ps delay for a 20-GHz clock) in the loop. Together with the excess loop delays

Fig. 5. A qualitative description of metastability in the flip-flop, with RTZ DAC as the proposed solution. While CML flip-flop is shown for simplicity, the circuit uses an ECL flip-flop.

Fig. 6. Circuit simulation results for the linear response and third-order distortion  $(2f_1 - f_2)$  of the input transconductance stage, given input signals  $(f_1, f_2)$  of approximately 100 MHz.

associated with the integrators and the interconnects, this delay is compensated to first order in frequency by introduction of a zero in the transfer function, through addition of a resistor in series with the second-stage integration capacitor. Given compensation of loop delays with insertion of a zero in the loop transmission, MATLAB simulations indicate <3-dB SNR degradation for <30-ps loop delay, given a 20-GHz clock.

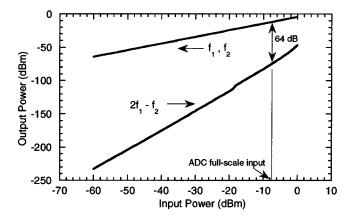

The first  $g_m$  stage is outside the  $\Sigma$ - $\Delta$  loop, hence its nonlinearity directly degrades the ADC linearity. Jensen [5] reported a linearized  $g_m$  stage using Caprio's cell. The  $\Sigma$ - $\Delta$  modulator reported here eliminates this in favor of a differential pair with its smaller transistor count (yield limits in a university process). Given this simple input stage, intermodulation is reduced by selecting an input stage bias current (6 mA) significantly larger than the switched current of the feedback DAC (2 mA). Given that the DAC is gated on only for 50% of the clock period, the input stage overloads at signal levels 6:1 larger than that of the subsequent  $\Sigma$ - $\Delta$  loop. Overload and resulting intermodulation distortion in the input stage is thus reduced. Circuit simulations (Fig. 6) indicate 64 dBc suppression of two-tone intermodulation arising from the input stage. For input signal levels near the ADC full-scale input, intermodulation is then dominated by distortion in the subsequent loop.

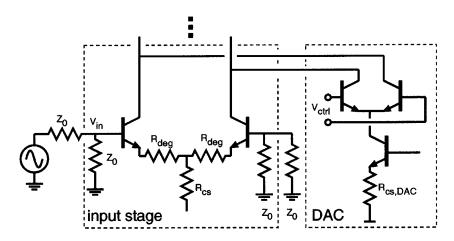

The input stage also contributes thermal and shot noise, and can limit the SNR. Referring to the partial circuit schematic of Fig. 7, the ADC total input-referred noise voltage arising from thermal and shot noise has a spectral density given by

$$\frac{d\langle E_n^2 \rangle}{df} \simeq 4kT(kT/qI_c)

+ 8kT(R_{\text{deg}} + R_{ex} + R_{bb} + Z_0/2)

+ 4qI_b(R_{\text{deg}} + R_{ex} + R_{bb} + Z_0/2)^2

+ (8kT/R_{cs})\gamma^2(R_{\text{deg}} + R_{ex} + kT/qI_c)^2

+ 4kT\left(\frac{kT}{qI_{\text{DAC}}/2}\right) \frac{(R_{\text{deg}} + R_{ex} + kT/qI_c)^2}{R_{\text{cs, DAC}}^2}

+ 8kT\frac{(R_{\text{deg}} + R_{ex} + kT/qI_c)^2}{R_{\text{cs, DAC}}},$$

where

$I_c$ input stage bias current;

base current;

$I_b \\ R_{bb} \\ Z_0 = 50 \Omega$ input-stage base resistance; input interface impedance;

$I_{\mathrm{DAC}}$ DAC switched current;

fractional imbalance in dc bias currents in the

input differential pair.

Comparing this input noise to the maximum input voltage before ADC overload,  $V_{\text{in, max}} = I_{\text{DAC}}(R_{\text{deg}} + R_{ex} + kT/qI_c)$ ,  $(P_{\rm in, max} = -7.5 \, \rm dBm)$  given the IC design values, the thermal and shot noise limits the SNR to 153 dB (1 Hz). This should be compared to the quantization-noise limited SNR, 143 dB (1 Hz) at 200 MHz signal frequency, for an ideal second-order  $\Sigma$ - $\Delta$ ADC at 20-GHz clock rate (Fig. 2). Comparing this input-referred noise to kT, -173.8 dBm (1 Hz), the input stage has a calculated 14-dB noise figure. In the present design, thermal noise from the DAC current mirror and thermal noise in the input degeneration resistance  $R_{\text{deg}}$  dominate.

A simple ECL master-slave flip-flop (demonstrated to operate as a divide-by-two at 75 GHz [13]) was used as the quantizer. The gated DAC is a simple ECL OR gate with open-col-

Fig. 7. Detail of input  $g_m$  stage and RTZ DAC for noise analysis.

Fig. 8. Simplified ADC circuit diagram (omitting current mirror references and microstrip-line terminations).

lector outputs. The final design parameters were:  $g_{m1}=15$  mS,  $g_{m2}=65$  mS, average DAC feedback current  $I_{\rm DAC}=2$  mA, nominal pull-up resistors  $R_L=1.125$  k $\Omega$ , clock frequency  $f_c=20$  GHz and integrating capacitors C=3 pF. A simplified IC schematic is shown in Fig. 8.

## IV. MEASUREMENT AND RESULTS

The HBTs on the fabricated IC wafer had a typical dc current-gain,  $\beta \geq 100$ , current gain cut-off frequency,  $f_{\tau} \approx 190$  GHz, and power gain cut-off frequency,  $f_{\rm max} \approx 200$  GHz at an emitter current density of  $\sim \! 10^5$  A/cm². The common-emitter breakdown voltage,  $BV_{\rm CEO}$ , was  $\sim \! 1.4$  V. Nichrome resistors had resistance approximately 20% lower than design values.

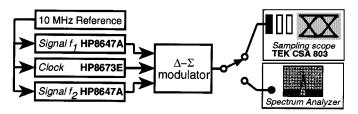

The IC was tested by on-wafer probing using 40 GHz probe cards. The photograph of the die is shown in Fig. 9. The standard technique for testing  $\Sigma$ - $\Delta$  modulators uses a fast logic analyzer

to acquire the digital data stream. Testing under two-tone conditions permits simultaneous measurement of SNR and two-tone third-order distortion. The captured data is analyzed by FFT for its spectral content. Due to the lack of a logic analyzer with sufficient bandwidth for capturing 18-GHz data, we were forced to use an analog spectrum analyzer to view the spectrum of the digital output. Note that the measured ADC output is then corrupted by the spectrum analyzer noise figure and third-order distortion products. The measurement setup is shown in Fig. 10. The ADC is driven simultaneously with a pair of synthesizers, and the output measured on the analog spectrum analyzer. The spectrum analyzer noise-figure was improved by adding an input low-noise high-gain preamplifier with input precision switched attenuators. The attenuators are used for measurements with large ADC input signals, reducing the spectrum analyzer input amplitude in order to avoid intermodulation effects in the analyzer.

Fig. 9. Die photograph of the completed  $\Sigma \text{--}\Delta$  modulator.

Fig. 10. The setup used for testing the  $\Sigma$ - $\Delta$  modulator.

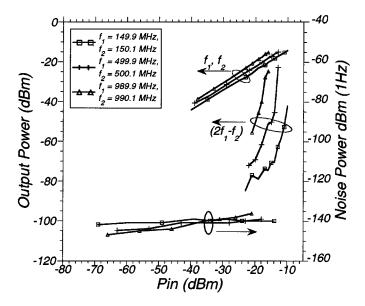

Fig. 11. Noise floor and third-order distortion power as a function of input power for different signal frequencies.

For small ADC inputs, the attenuators are removed, and the ADC output noise spectrum measured on the spectrum analyzer. For large ADC inputs, ADC intermodulation products are measured with the attenuators present, avoiding intermodulation distortion from the spectrum analyzer and its preamplifiers. The ADC low-signal noise floor and third-order intercept can thus both be measured.

Because the spectrum analyzer has dynamic range smaller than that of the ADC under test, it is difficult to measure the

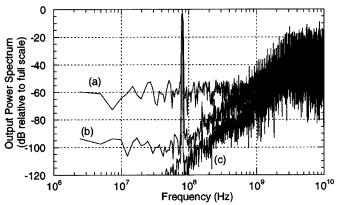

Fig. 12. Full-loop transistor level simulations on SPICE of (a) present ADC and (b) ADC with 3 stage latched comparator and a preamplifier, as compared to (c) MATLAB system level simulation.

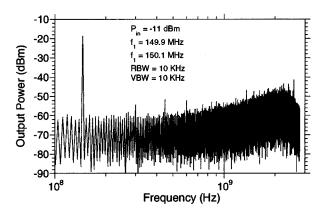

Fig. 13. Spectrum of the  $\Sigma - \Delta$  modulator output for a two-tone input at 150 MHz.

ADC output noise given full-scale ADC input signals. Under strong ADC input drive, with the attenuators present, the ADC output noise falls below the kTF noise floor of the spectrum analyzer; with the attenuators absent, the spectrum analyzer input is driven into gain compression.

The  $\Sigma$ - $\Delta$  modulator was tested with an 18-GHz clock and two-tone measurements were performed at signal frequencies of 150 MHz, 500 MHz, and 990 MHz. The results for variation of the output power in the fundamental and the third-order distortion component are shown in Fig. 11. The observed increase in ADC noise with increased input signal power may be due to instrument effects, as discussed above or ADC nonidealities. The noise floor shows little variation from 150 MHz to 1 GHz. This suggests that the modulator does not shape the quantization-noise below 1 GHz. This is in contrast with our MATLAB simulations, which do not model comparator metastability. The measured ADC SNR is, however, consistent with full-loop transistor-level circuit simulations we have recently performed (Fig. 12). Because of these simulation results, we have recently redesigned the ADC. The modified ADC adds an additional stage of regeneration in the latched comparator and adds a two-stage Cherry-Hooper [15] limiting preamplifier at the comparator input. In SPICE simulations, this improved design exhibits much higher SNR at frequencies below 1 GHz. Hence, we believe that the poor measured noise

is due to quantizer metastability and dynamic hysteresis errors. Fig. 13 shows the spectrum of the output for a two-tone input at 150 MHz. The modulator achieved a two-tone SNR of 48 dB, 42 dB, and 33 dB for input signals at 150 MHz, 500 MHz, and 990 MHz, respectively.

### V. CONCLUSION

We have demonstrated a second-order continuous-time  $\Sigma - \Delta$  modulator fabricated in a 200-GHz  $f_{\tau}$ ,  $f_{\rm max}$  InAlAs/InGaAs HBT process. The chip is clocked at 18 GHz with signal bandwidths ranging from 150 to 990 MHz. The modulator achieved a two-tone SNR of 48 dB, 42 dB, and 33 dB for input signals at 150 MHz, 500 MHz, and 990 MHz, respectively. Poor noise-shaping was observed below 1 GHz. Transistor level full-loop simulations of the ADC and a modified ADC, with additional comparator regeneration and preamplification, suggest that the poor noise shaping is due to quantizer metastability and dynamic hystersis errors. Our analysis further suggests that low hystersis can be obtained at 18-GHz clock rate in a 200 GHz  $f_{\tau}$  process. Confirmation of the analysis must await testing of the revised ADC design. The modified ADC is now in fabrication.

#### REFERENCES

- J. C. Candy, "Oversampling methods for A\D and D\A conversion," in Oversampling Delta-Sigma Data Converters, New York: IEEE Press, 1992, pp. 1–29.

- [2] Q. Lee, S. C. Martin, D. Mensa, R. P. Smith, J. Guthrie, and M. J. W. Rodwell, "Submicron transferred-substrate heterojunction bipolar transistors," *IEEE Electron Device Lett.*, vol. 20, pp. 396–398, Aug. 1999.

- [3] Y. Betser, D. Mensa, S. Jaganathan, T. Mathew, and M. Rodwell, "In-AlAs/InGaAs HBT's with simultaneously high values of Ft and Fmax for mixed analog/digital applications," *IEEE Electron Device Lett.*, vol. 22, pp. 56–8, Feb. 2001.

- [4] V. Comino, M. S. J. Steyaert, and G. C. Temes, "A first-order current-steering Sigma–Delta modulator," *IEEE J. Solid-State Circuits*, vol. 26, pp. 176–183, Mar. 1991.

- [5] J. F. Jensen, G. Raghavan, A. E. Cosand, and R. H. Walden, "A 3.2 GHz second-order delta-sigma modulator implemented in InP HBT technology," *IEEE J. Solid-State Circuits*, vol. 30, pp. 1119–1127, Oct. 1005

- [6] A. Olmos, T. Miyashita, M. Nihei, E. Charry, and Y. Watanabe, "A 5 GHz continuous time sigma–delta modulator implemented in 0.4 μm InGaP/InGaAs HEMT technology," in *IEEE Int. Symp. Circuits Syst.*, vol. 1, 1998, pp. 575–578.

- [7] G. Raghavan, J. F. Jensen, J. Laskowski, M. Kardos, M. G. Case, M. Sokolich, and S. Thomas III, "Architecture, design and test of continuous-time tunable intermediate-frequency bandpass Delta–Sigma modulators," *IEEE J. Solid-State Circuits*, vol. 36, Jan. 2001.

- [8] M. J. W. Rodwell, M. Urteaga, Y. Betser, T. Mathew, P. Krishnan, D. Scott, S. Jaganathan, D. Mensa, J. Guthrie, Q. Lee, S. C. Martin, R. P. Smith, R. Pullela, B. Agarwal, U. Bhattacharya, and S. Long, "Scaling of InGaAs/InAlAs HBT's for high speed mixed-signal and mm-wave ICs," *Int. J. High Speed Electron. Syst.*, Feb. 2001.

- [9] Q. Lee, S. C. Martin, D. Mensa, R. P. Smith, J. Guthrie, S. Jaganathan, Y. Betser, T. Mathew, S. Krishnan, L. Samoska, and M. Rodwell, "Submicron transferred-substrate heterojunction bipolar transistors with greater than 1 THz fmax," in 1999 IEEE Device Res. Conf., Santa Barbara, CA, June 1999, postdeadline paper.

- [10] S. Krishnan, M. Dahlstrom, T. Mathew, Y. Wei, D. Scott, M. Urteaga, and M. J. W. Rodwell, "InP/InGaAs/InP double heterojunction bipolar transistors with 300 GHz fmax," in Indium Phosphide and Related Materials, Nara, May 2001, to be published.

- [11] S. Weinreb, T. Gaier, R. Lai, M. Barsky, Y. C. Leong, and L. Samoska, "High-gain 120–215-GHz MMIC amplifier with integral waveguide transitions," *IEEE Microwave Guided Wave Lett.*, vol. 9, pp. 282–284, July 1999.

- [12] Q. Lee, D. Mensa, J. Guthrie, S. Jaganathan, T. Mathew, Y. Betser, S. Krishnan, S. Ceran, and M. J. W. Rodwell, "66 GHz static frequency divider in transferred-substrate HBT technology," in *IEEE Radio Freq. Integrat. Circuits Symp.*, June 1999, pp. 87–90.

- [13] T. Mathew, H. J. Kim, D. Scott, S. Jaganathan, S. Krishnan, Y. Wei, M. Urteaga, S. Long, and M. J. W. Rodwell, "75 GHz static frequency divider using InAlAs/InGaAs HBTs," IEE Electron. Lett., submitted for publication.

- [14] B. Razavi, *Principles of Data Conversion System Design*. New York: IEEE Press, 1995.

- [15] E. M. Cherry and D. E. Hooper, "The design of wide-band transistor feedback amplifier," *Proc. Inst. Elec. Eng.*, vol. 110, pp. 375–389, Feb. 1963

Shrinivasan Jaganathan received the B.Tech. degree in electrical engineering from the Indian Institute of Technology, Bombay, in 1993 and the M.S. and Ph.D. degrees, also in electrical engineering, from the University of California, Santa Barbara (UCSB), in 1997 and 2000, respectively.

His research at UCSB focused on design of high-speed sigma-delta ADCs using InGaAs/InP HBTs. He is currently a Senior Engineer with Gtran Inc., Newbury Park, CA. His research interests include circuit design for high-speed fiber-optic systems.

**Sundararajan Krishnan** received the B.Tech. degree in electrical engineering from the Indian Institute of Technology, Madras, in 1998.

Since then, he has been with Prof. Rodwell's group at the University of California, Santa Barbara, where he is involved in the design of high-speed delta–sigma A/D converters.

**Dino Mensa** received the B.S. degree in physics, and the M.S. and Ph.D. degrees in electrical engineering from the University of California, Santa Barbara (UCSB), in 1995, 1997, and 1999, respectively.

His research at UCSB focused on MBE growth, high-speed device design, and high-frequency amplifier design in the transferred-substrate InP HBT process. From 1999 to 2000, he worked as a fiber-optic IC Design Engineer at Conexant Systems, Inc. He is currently a Senior Engineer with Gtran Inc.,Newbury Park, CA. His research interests include circuit design for high-speed fiber-optic systems.

**Thomas Mathew** received the B.Tech. degree from the Regional Engineering College, Calicut, India, and the M.Tech. degree from the Indian Institute of Technology, Bombay, India.

In Fall 1997, he joined the University of California, Santa Barbara, where he is working toward a doctorate in the ECE Department. His research interests include the design of high-speed analog and digital ICs.

Yoram Betser, photograph and biography not available at the time of publica-

Yun Wei received the B.S. degree in 1991 from Fudan University, Shanghai, China. He received the M.S. degree in 1997 from Oregon Graduate Institute of Science and Technology. He is now working toward the Ph.D. degree at the Department of Electrical and Computer Engineering, University of California, Santa Barbara. He is working on the design of 94-GHz InP DHBT power amplifiers and quasi-optic antenna array.

Miguel Urteaga received the B.A.Sc. degree in engineering physics from Simon Fraser University, Vancouver, Canada, in 1998 and the M.S. degree in electrical engineering from University of California at Santa Barbara (UCSB), in 2001. He is currently working toward the Ph.D. degree at UCSB under the supervision of Prof. Rodwell. His research includes device design and fabrication of high-speed InP HBTs, as well as the design of ultrahigh-frequency integrated circuits.

Mark Rodwell received the B.S. degree from the University of Tennessee in 1980, and the M.S. and Ph.D. degrees from Stanford University, Stanford, CA, in 1982 and 1988, respectively.

He is Professor and Director of the Compound Semiconductor Research Laboratories at the University of California at Santa Barbara. He was with AT&T Bell Labs during 1982–1984. His research focuses on very high-bandwidth bipolar transistors, high-speed bipolar IC design, and GHz mixed-signal ICs. His group has worked extensively in the area of

GaAs Schottky-diode ICs for subpicosecond/millimeter wave instrumentation.

Dr. Rodwell is the recipient of a 1989 National Science Foundation Presidential Young Investigator award, and his work on submillimeter-wave diode ICs was awarded the 1997 IEEE Microwave Prize.

**Dennis Scott** received the B.S. and M.S. degrees in electrical engineering from the University of Illinois at Urbana-Champaign in 1996 and 1999, respectively. He is currently working toward the Ph.D. degree at the University of California at Santa Barbara, working on high-speed HBTs.