# W-band InP/InGaAs/InP DHBT MMIC Power Amplifiers

Yun Wei, Sangmin Lee, Krishnan Sundararajan, Mattias Dahlstrom, Miguel Urteaga, Mark Rodwell

Department of Electrical and Computer Engineering, University of California Santa Barbara, CA 93106, USA

Abstract — We report W-band MMIC class A power amplifiers in InP/InGaAs/InP DHBT transferred-substrate technology. A cascode amplifier with 64  $\mu m^2$  emitter area exhibits a peak small-signal gain of 10 dB at 90GHz and an output power of 9.5 dBm under 1 dB gain compression. An 8.5-dB-gain common-base amplifier with an emitter area of 128  $\mu m^2$  delivers 14 dBm output power at 85 GHz under 1 dB gain compression and 16.2 dBm (42 mW) saturated output power with an associated 4.6 dB gain. To our knowledge, this is highest reported output power for a W-band HBT power amplifier.

## I. INTRODUCTION

Deep submicron InP-based HEMTs have established record power levels for W-band solid-state power amplifiers [1], substantially exceeding the power levels attained by HBTs. Scaling of InP-based HBTs has resulted in devices with high cutoff frequencies, enabling high-gain amplifiers in W-band [2,3] and at 175 GHz [4]. Unfortunately, these wideband HBTs have low breakdown voltage and hence low output power. We had recently reported [5] 0.5 um InP DHBTs with combined wide bandwidth (425 GHz  $f_{\rm max}$ ) and high breakdown voltage ( $V_{BR,CEO}$ > 8 Volts). Here we report W-band InP DHBT amplifiers in this technology that deliver 42 mW (16.2dBm) saturated output power, substantially larger than previously reported for HBTs in W-band.

# II. DEVICE TECHNOLOGY

The circuits were fabricated using a substrate transfer process [2,3,4]. DHBTs with InP collectors are employed for high breakdown voltages. The epitaxial layer structure is similar to that reported in [5] with a 400-Å-thick InGaAs base and a 3000-Å-thick InP collector and the wafer was grown by IQE Inc. InAlAs/InGaAs digital alloy grades are employed in both the emitter-base and base-collector junctions. In transferred-substrate HBTs, the device is inverted, and heat must flow from the semiconductor junction to the substrate through the emitter semiconductor. InP has ~15:1 higher thermal conductivity than InAlAs, and hence is employed as the DHBT emitter.

transferred-substrate process substantially reduces the collector-base charging time  $R_{bb}C_{cbi}$  and hence increases the HBT  $f_{\rm max}$ . Power DHBTs are realized with a multiple-finger structure in the same process. Finger spacing must be adequate for minimal finger-finger thermal coupling, emitter ballast resistances are provided to prevent thermal instability (current hogging) [6] at the intended  $V_{CE}$  and  $J_{c}$ . The emitter fingers have 16 µm × 1 µm mask dimension with a corresponding 20  $\mu m \times 2 \mu m$  collector finger. Each emitter finger employs an 8 Ohm NiCr ballast resistor. In the circuits, the HBTs are biased to set the peak instantaneous current density at  $1 \times 10^5$  A/cm<sup>2</sup>. While the breakdown voltage of the common emitter power DHBT is greater than 8 volts at low current density, maximum operating voltage at high current density is determined by thermal instability, and is a function of the emitter ballast resistance. Both 4-finger and 8-finger devices (with emitter areas of 64 µm<sup>2</sup> and 128  $\mu$ m<sup>2</sup> respectively) exhibit  $f_{\text{max}}$  above 330 GHz.

The process provides a micro strip wiring environment on a thin 5  $\mu m$  BCB polymer dielectric with  $\epsilon_{eff}$  =2.7. Smaller circuit capacitances use the polymer dielectric, while larger circuit capacitances are realized using MIM structures with 0.4  $\mu m$  thickness SiN dielectric. Resistors are fabricated using thin-film NiCr that has a sheet resistance of 40 Ohms/square.

# III. CIRCUIT DESIGN

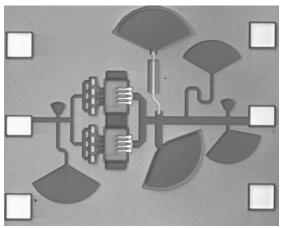

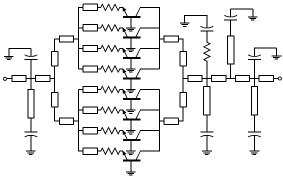

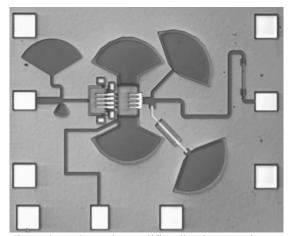

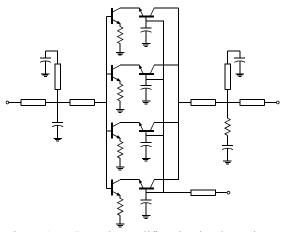

Figures 1 and 3 show the die photographs of the cascode and common-base amplifiers, while figures 2 and 4 show the circuit schematics. Each amplifier consumes a die area of  $0.5 \text{mm} \times 0.4 \text{mm}$ .

The common-base design (Fig.1 and Fig.2) uses 2 parallel 4-finger power DHBT cells, forming a composite 8-finger device with 128  $\mu$ m² emitter junction area. Because of the very low impedance, the input of the two paralleled 4-finger common-base devices are interconnected with inductive microstrip lines and then matched to 50  $\Omega$  with a shunt capacitance. The device is biased at 78 mA (0.6x10 $^5$  A/cm²) and  $V_{CE}$  =3.6 Volts. The output is tuned with two cascaded  $\Pi$ -sections. At

the design frequency, the output tuning network loads the HBT in the optimum admittance for saturated output power as  $Y_{L,opt} = G_L + jB_L$ , where the load susceptance  $B_L = -\omega C_{cb}$  compensates for the HBT output capacitance and  $G_L = I_{c,\max}/(V_{CE,\max} - V_{CE,sat})$  is the optimum load conductance. With design values of  $V_{CE,\max} = 6.1 \text{ V}$ ,  $V_{CE,sat} = 1.1 \text{ V}$ , and  $I_{C,\max} = 128 \text{ mA}$ ,  $G_L$  is  $1/40 \, \Omega^{-1}$  and the expected saturated output power is  $P_{sat} = I_{C,\max} (V_{CE,\max} - V_{CE,sat})/8 = 80 \text{mW}$ . In the cascode design (Fig.3 and Fig.4), both the

In the cascode design (Fig.3 and Fig.4), both the common-emitter and common-base HBTs are 4-finger (64  $\mu$ m<sup>2</sup>) devices. The output common-base device is biased at 40 mA (0.63x10<sup>5</sup>A/cm<sup>2</sup>) and  $V_{CE}$ =3.5 Volts, hence the expected saturated output power is 40 mW. The input is matched for maximum gain using a T-section tuning network, while the output tuning network is a shunt inductive stub and a quarter-wave transformer.

The tuning networks uses capacitors with both SiN and BCB dielectrics. The SiN capacitors have much larger capacitance per unit die area, but have substantially larger processing variability due to variations in the thickness of the deposited dielectric film. Parallel combinations of the two, with capacitances appropriately partitioned between the SiN and BCB elements, result in a compact IC layout with reduced processing variability.

# IV. TESTING

Amplifier small-signal gains and return losses were measured on-wafer using GGB wafer probes and a W-band Agilent 8510 network analyzer calibrated with a commercial LRM substrate. For power measurements, the amplifiers were driven by a W-band frequency multiplier and power amplifier, and the output power measured directly with a power meter without additional off-wafer load impedance tuning. The data is corrected for the measured attenuation of wave guides and wafer probes.

# IV. RESULTS

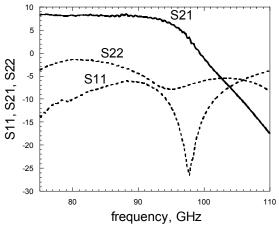

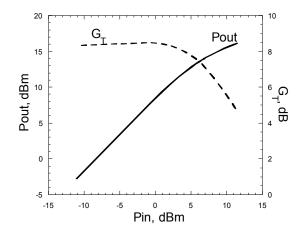

Figure 5 shows the small-signal characteristics of the common-base power amplifier, while gain compression and saturation power data are shown in figure 6. The insertion gain is 8.5 dB while the 1 dB compression output power is 14 dBm at 85 GHz. The saturated output power is 16.2 dBm (42 mW) with a corresponding gain of 4.6 dB.

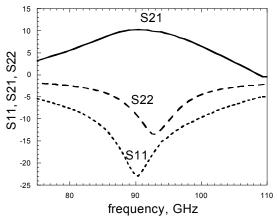

The cascode amplifier exhibits an insertion gain  $(S_{21})$  of 10 dB when biased for peak gain and 8.5 dB when biased for maximum saturated power at 90 GHz,

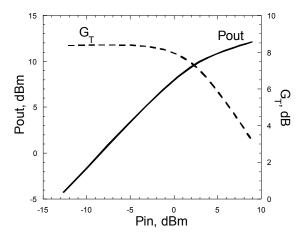

with the input and output return losses greater than 10dB. Fig. 7 shows the measured small-signal characteristics. Fig. 8 shows the gain and saturated power characteristics at 90 GHz. The amplifier has an output power of 9.5 dBm under 1 dB gain compression and the saturated output power is greater than 12 dBm.

## IV. CONCLUSIONS

The InP/InGaAs/InP transferred-substrate DHBT MMIC technology provides high breakdown voltages whose bandwidth is sufficient for W-band applications. Output power can be directly increased by increasing the transistor emitter junction areas and by power-combining several stages. With attained DHBT cutoff frequencies of 330-425 GHz, G-band (140-220 GHz) power amplifiers are also feasible.

## ACKNOWLEDGEMENT

This work is a co-research with California Institute of Technology that is funded by ARO-MURI program under contract number PC249806.

Figure 1: Common-base amplifier die photograph.

Figure 2: Common-base amplifier circuit schematic.

Figure 3: Cascode amplifier die photograph

Figure 4: Cascode amplifier circuit schematic

Figure 5: Small-signal parameters of the common-base power amplifier

Figure 6: Power saturation characteristics of the common-base power amplifier

Figure 7: S-parameters of the cascode power amplifier when biased for peak small-signal gain

Figure 8: Power saturation characteristics of the cascode power amplifier

## REFERENCES

- [1] Y.C. Chen, D.L. Ingram, R. Lai, M. Barsky, R. Grunbacher, T. Block, H.C. Yen, D.C. Streit, "A 95GHz InP HEMT MMIC amplifier with 427mW power output". *IEEE Microwave and Guided Wave Lett.*, 8 (11), Nov. 1998 pp.399-401

- [2] T. Morf, S. Hubschuer, D. Huber, A. Huber, V. Schwarz, H. Jackel, "98 GHz InP/InAsGas HBT Amplifier with 26 dB gain", *IEEE Trans. Microwave and Guided Wave Lett.*, Vol. 9, No.12, Dec. 1999, pp. 523-525.

- Dec. 1999, pp.523-525

[3] Guthrie, J.R.; Urteaga, M.; Scott, D.; Mensa, D.; Mathew, T.; Lee, Q.; Krishnan, S.; Jaganathan, S.; Betser, Y.; Rodwell, M.J.W. "HBT MMIC 75 GHz and 78 GHz power amplifiers." Proceedings of 2000 International Conference on Indium Phosphide and Related Materials, Piscataway, NJ, USA: IEEE, 2000, p.246-2499

- USA: IEEE, 2000. p.246-2499

[4] M. Urteaga, D. Scott, T. Mathew, S. Krishnan, Y. Wei, M. Rodwell "Single-stage G-band HBT Amplifier with 6.3 dB Gain at 175 GHz", 2001 GaAs IC Symposium, Baltimore, Maryland, October 21-24, 2001.

- [5] Lee, S.; Kim, H.J.; Urteaga, M.; Krishnan, S.; Wei, Y.; Dahlstrom, M.; Rodwell, M. "Transferred-substrate InP/InGaAs/InP double hetero-junction bipolar transistors with f<sub>max</sub>=425 GHz." *Electronics Letters*, vol.37, 16 Aug. 2001. pp.1096-1098

[6] Liu, William., Hin-Fai Chau; Beam, E., III "Thermal properties and thermal instabilities of

- [6] Liu, William., Hin-Fai Chau; Beam, E., III "Thermal properties and thermal instabilities of InP-based heterojunction bipolar transistors". *IEEE Transactions on Electron Devices*, vol.43, (no.3), IEEE, March 1996. pp.388-95