## Interface charge compensation in InP based heterojunction bipolar transistors with implanted subcollectors

Navin Parthasarathy, <sup>a)</sup> Christoph Kadow, <sup>b)</sup> Zach Griffith, and Mark J. W. Rodwell Department of Electrical and Computer Engineering, University of California, Santa Barbara, California 93106

Miguel Urteaga, Keisuke Shinohara, Richard Pierson, and Bobby Brar Rockwell Science Company, Thousand Oaks, California 91360

(Received 24 February 2006; accepted 23 May 2006; published online 13 July 2006)

We report InP/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP double heterojunction bipolar transistors (DHBTs) with implanted subcollectors. We demonstrate the compensation of charge at the regrowth interface by the use of a blanket Fe implant. An isolated  $N^{++}$  subcollector is then formed by a patterned Si implant. With the compensation of the interface charge, this patterned subcollector eliminates the extrinsic base-collector capacitance  $C_{\rm cb}$  associated with the base interconnect pad over the entire range of bias voltages. These implanted subcollector DHBTs with the shallow Fe implant have 363 GHz  $f_{\tau}$  and 410 GHz  $f_{\rm max}$ . The dc current gain  $\beta \sim$  40, BV<sub>ceo</sub>=4.9 V, BV<sub>cbo</sub>=5.4 V, and  $I_{\rm cbo}$ < 70 pA at  $V_{\rm cb}$ =0.3 V. © 2006 American Institute of Physics. [DOI: 10.1063/1.2221512]

While InP based double heterojunction bipolar transistors (HBTs) benefit from high carrier mobilities and saturated velocities, SiGe HBTs have smaller junction dimensions and smaller extrinsic parasitics. Consequently, digital circuit speed in SiGe and InP has been comparable, with SiGe offering higher integration scales. Further reduction of parasitics in InP HBTs is therefore important. The base-collector capacitance  $C_{\rm cb}$  contributes significantly to analog bandwidth and digital delay and must be reduced as InP HBTs are scaled. In small-junction-area HBTs used in low-power logic, the parasitic base interconnect pad capacitance becomes a significant fraction of the total  $C_{\rm cb}$ . Several approaches have been pursued for eliminating this access pad capacitance.

InP HBTs with implanted collectors are very promising as a manufacturable, high yield process and have demonstrated reduced  $C_{\rm cb}$ . In these processes, Si is selectively implanted into an undoped or SI InP layer to form a  $N^+$ pedestal link<sup>5,6</sup> or a buried subcollector, respectively. Outside the implanted regions, the depletion depth is increased and the extrinsic capacitance is reduced. The active HBT layers are then grown. However, exposed InP surfaces have donor-like charge states attributed to Si impurities.<sup>8,9</sup> HBTs reported in Ref. 5 also suffer from this process-dependent charge at the regrowth interface. This charge, if left uncompensated, results in incomplete depletion and hence no reduction in extrinsic  $C_{cb}$  at low bias voltages. Several methods have been utilized for reduction of this interface charge, including process related techniques,9 annealing in a phosphine ambient,  $^8$  and overgrowth of a  $p^+$  charge compensation layer.<sup>5</sup> This interface charge is process dependent, and full compensation might not be possible with process techniques or a  $p^+$  compensation layer.

To alleviate these problems, we demonstrate InP HBTs with implanted subcollectors wherein Fe implantation eliminates this interface charge and a selective, patterned Si implant forms the  $N^{++}$  subcollector. In addition to the reduced

extrinsic  $C_{\rm cb}$  associated with the elimination of the base access pad capacitance and compensation of charge at the epitaxial growth interface, this process provides increased wafer planarity and hence potentially improved yield in the fabrication of large circuits.

In the first demonstration of this double implanted process, the device gain, collector leakage current, and ideality factors are similar to a fully epitaxial standard mesa HBT. The  $f_{\tau}$  and  $f_{\rm max}$  of 363 and 410 GHz, respectively, are the best reported for HBTs with implanted subcollectors. Prior to this work, the highest simultaneous  $f_{\tau}$  and  $f_{\rm max}$  reported for an InP HBT employing implantation to reduce  $C_{\rm cb}$  were 240 and 310 GHz, respectively.

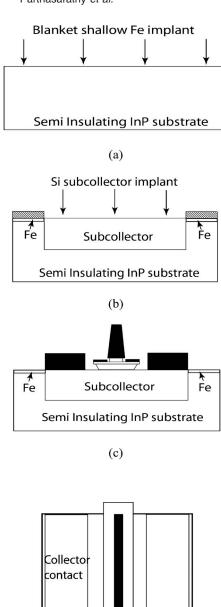

The process flow of the implanted subcollector HBT with Fe is shown in Fig. 1. A semi-insulating InP substrate is implanted with Fe at 10 keV at a fluence of  $2 \times 10^{13}$  ions cm<sup>-2</sup> [Fig. 1(a)]. The wafer is annealed at 700 °C for 5 min to activate the Fe, which is a midgap acceptor in InP.<sup>11</sup> The Fe implant conditions are selected to fully compensate the *N*-type charge at the growth interface between the substrate and collector epitaxial layers over the observed  $(1-5)\times 10^{12}$  cm<sup>-2</sup> range of regrowth interface charge densities. In order to ensure complete charge depletion at the regrowth interface in the region under the base pad contact area,

$$n_{\text{Fe}} \ge n_s + \frac{N_c T_c}{2} - \frac{(V_{\text{cb}} + V_{\text{bi}})\varepsilon}{qT_c},\tag{1}$$

where  $n_{\rm Fe}$  is the density of Fe in cm<sup>-2</sup>,  $n_s$  is the regrowth interface charge density,  $N_c$  is the doping in the drift collector,  $T_c$  is the thickness of the drift collector,  $V_{\rm bi}$  is the built-in potential of the base-collector junction, and  $V_{\rm cb}$  is the base-collector reverse bias voltage.

The sample is then selectively implanted [Fig. 1(b)], using  $\mathrm{SiN}_x$  as the implant mask, with Si at 200 keV/4  $\times$  10<sup>14</sup> ions cm<sup>-2</sup>, 40 keV/7  $\times$  10<sup>13</sup> ions cm<sup>-2</sup>, and 10 keV/3  $\times$  10<sup>13</sup> ions cm<sup>-2</sup>, and then activated by annealing at 800 °C/30 s.<sup>12</sup> The Si implant dose is much larger than the Fe acceptor density ( $n_{\mathrm{Fe}}$ ) in the selectively implanted region. This ensures that a highly  $N^{++}$  doped, isolated sub-

a)Electronic mail: navin@ece.ucsb.edu

b)Present address: Infineon Technologies AG, München, Germany.

FIG. 1. Implanted subcollector process cross section: (a) blanket shallow Fe implant to suppress interface, (b) Si implant to form the subcollector, (c) active HBT layers are grown and device is formed, and (e) top view of implanted subcollector DHBT.

(d)

Base

pad

access

Subcollector

**Implant**

collector region [Fig. 1(b)] is formed. The base access pad [Fig. 1(d)] lies outside the subcollector implant boundary and, in the absence of interface charge, does not contribute to  $C_{\rm cb}$ .

A test wafer is coprocessed without the blanket Fe implant to observe the effect of uncompensated charge. This process is otherwise identical to the one described above.

The active InP HBT layers are then grown by molecularbeam epitaxy (MBE). The device  $N^-$  drift collector, base, and emitter layers for both wafers are identical to that reported in

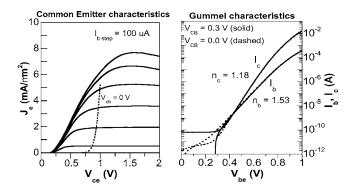

FIG. 2. Common-emitter I-V and forward Gummel characteristics. Device dimensions:  $A_{ie} = 0.65 \times 4.3 \ \mu \text{m}^2$ .

Ref. 10. Growth is initiated with a 3.5 nm undoped InGaAs etch-stop layer between the InP collector and the InP substrate. The  $N^-$  drift collector, base, and emitter layers are grown, and devices are formed<sup>10</sup> by wet etching the emitter and base mesas. With the selectively implanted subcollector, HBT isolation does not require a mesa etch, reducing the HBT mesa height by  $\sim 500$  nm.

For the implanted HBT with the blanket Fe implant, standard transmission line measurements (TLM) show the base sheet resistivity  $\rho_s \approx 1050 \Omega/\text{sq}$  and contact resistivity  $\rho_c \approx 30 \ \Omega \ \mu \text{m}^2$ . The emitter contact resistivity  $\rho_c$  determined from RF parameter extraction is  $\approx 15 \Omega \mu m^2$ . From TLMs and Hall measurements, the subcollector sheet resistance  $\rho_s$ is  $\approx 25 \Omega/\text{sq}$ . The collector contact is made to  $N^{++}$  InP and partially annealed (Ni/Ge/Au/Ni/Au, 320 °C/60 s). The anneal temperature was kept low because higher temperature anneals greatly increased the base  $\rho_c$  on test samples. Consequently, the collector  $\rho_c$  is very high at  $\approx 300 \ \Omega \ \mu \text{m}^2$ . The HBTs have dc current gain  $\beta \approx 40$ , common-emitter and common-base breakdown voltages BV<sub>ceo</sub>=4.9 V and BV<sub>cbo</sub> =5.4 V (at  $I_c$ =50  $\mu$ A), collector and base ideality factors  $n_c$ =1.18 and  $n_b$ =1.53, and low collector leakage current  $I_{\rm cbo}$  < 70 pA (at an applied  $V_{\rm cb,offset}$  = 0.3 V). Figure 2 shows the common-emitter DC and Gummel characteristics. The device  $\beta$ , ideality factors, and collector leakage current are consistent with those measured from the triple mesa HBT equivalent. 10 Leakage between adjacent HBTs at 5 μm separation was  $\sim 10$  pA/ $\mu$ m at 3 V bias, indicating good device isolation.

DC 45 GHz S-parameter measurements are carried out after performing an off wafer line-reflect-reflect-match calibration on an Agilent 8510C network analyzer. Device data

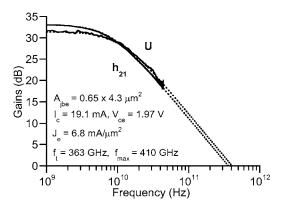

FIG. 3. Measured microwave gains  $H_{21}$  and Mason's unilateral power gain U at a bias associated with peak  $f_{\tau}$  and  $f_{\rm m}$ Downloaded 30 Aug 2006 to 128.111.239.135. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

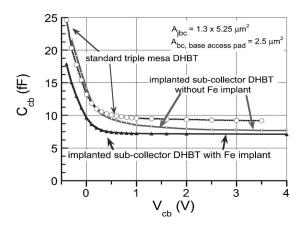

FIG. 4. Variation of  $C_{\rm cb}$  with  $V_{\rm cb}$  at  $I_c$ =0 mA for standard triple mesa HBT, <sup>10</sup> implanted subcollector HBTs with shallow Fe implant, and implanted subcollector HBTs without Fe. Junction areas and epitaxial layer structures (drift collector, base, and emitter) of the HBTs are identical.

are deembedded from probe pad parasitics. A maximum 363 GHz  $f_{\tau}$  and 410 GHz  $f_{\rm max}$  (Fig. 3) is demonstrated at  $I_c$ =19.1 mA and  $V_{\rm ce}$ =1.97 V ( $J_e$ =6.83 mA/ $\mu$ m²). The  $f_{\tau}$  and  $f_{\rm max}$  are determined from an extrapolation through a least-squares fit between the single-pole transfer functions for  $H_{21}$  and U to the measured data at the frequencies measured. This HBT has a  $0.6\times4.3~\mu$ m² emitter semiconductor junction area and 1.3  $\mu$ m base mesa width. The subcollector stripe as defined on the photomask extends  $\sim0.5~\mu$ m beyond the length of the emitter junction.

Figure 4 compares the variation of  $C_{cb}$  vs  $V_{cb}$  (at  $J_e$ =0 mA/ $\mu$ m<sup>2</sup>) between the implanted subcollector HBT with shallow Fe implant, the implanted subcollector HBT without Fe implant, and a standard triple mesa HBT, 10 all with a similar 120 nm thick drift collector. At low bias voltages, the  $C_{\rm cb}$  of the implanted subcollector HBT without the Fe implant is similar to that of the triple mesa HBT. This suggests the presence of an undepleted sheet charge at the regrowth interface in the contact pad region. The implanted subcollector HBT with shallow Fe implant exhibits lower  $C_{cb}$  over the entire measured range of bias voltages bias. The compensation of interface charge by the shallow Fe implant is thus evident. At ~0.6 V reverse bias the collector is fully depleted and  $C_{\rm ch}$  is  $\sim 23\%$  smaller than that measured for the mesa HBT. This capacitance reduction corresponds well to the fractional area of the base access pad. From Eq. (1), the regrowth interface charge is depleted when

$$V_{\rm cb} + V_{\rm bi} \ge \frac{qT_c(n_s - n_{\rm Fe})}{\varepsilon} + \frac{qN_cT_c^2}{2\varepsilon}.$$

The above equation indicates that larger bias voltage  $(V_{\rm cb})$  is required to fully deplete the interface charge under the base pad when this charge is not compensated. This is evident from Fig. 4 where a high base-collector bias voltage  $(>3~{\rm V})$  is required to fully deplete the uncompensated interface charge on the implanted subcollector HBT without the Fe implant.

The  $f_{\tau}$  and  $f_{\rm max}$  are lower than the triple mesa HBT. We attribute this to higher base resistance and larger collector series resistance of ~20  $\Omega$ . The high collector resistance which is also evident from the  $I_{\rm C}$ - $V_{\rm CE}$  characteristics is due to insufficient annealing of the alloyed collector ohmic contacts to  $N^{++}$  InP. The collector ohmic contact process is being revised to reduce the collector contact resistivity.

This work was supported by DARPA under the TFAST Program No. N66001-02-C-8080.

<sup>1</sup>P. Bhattacharya, *Properties of Lattice-Matched and Strained Indium Gallium Arsenide* (INSPEC/The Institution of Electrical Engineers, London, 1993).

<sup>2</sup>M. Khater, J.-S. Rieh, T. Adam, A. Chinthakindi, J. Johnson, R. Krishnasamy, M. Meghelli, F. Pagette, D. Sanderson, C. Schnabel, K. T. Schonenberg, P. Smith, K. Stein, A. Stricker, S.-J. Jeng, D. Ahlgren, and G. Freeman, Tech. Dig. - Int. Electron Devices Meet. 2004, 247.

<sup>3</sup>W. Hafez, J. W. Lai, and M. Feng, IEEE Electron Device Lett. **24**, 292 (2003).

<sup>4</sup>D. Sawdai, P. C. Chang, V. Gambin, X. Zeng, J. Yamamoto, K. Loi, G. Leslie, M. Barsky, A. Gutierrez-Aitken, and A. Oki, *Proceedings of the Device Research Conference, Notre Dame, IN, 21–23 June 2004* (IEEE, New York, 2004), Vol. 2, pp. 14–15.

<sup>5</sup>Y. Dong, Z. Griffith, M. Dahlstrom, and M. J. W. Rodwell, *Proceedings of the Device Research Conference, Notre Dame, IN, 21–23 June 2004* (IEEE, New York, 2004), Vol. 1, pp. 67–68.

<sup>6</sup>J. C. Li, M. Chen, D. A. Hitko, C. H. Fields, B. Shi, R. Rajavel, P. M. Asbeck, and M. Sokolich, IEEE Electron Device Lett. **26**, 136 (2005).

<sup>7</sup>M. Y. Chen, M. Sokolich, D. H. Chow, S. S. Bui, Y. Royter, D. A. Hitko, S. Thomas III, C. H. Fields, R. D. Rajavel, and B. Shi, IEEE Trans. Electron Devices **51**, 1736 (2004).

<sup>8</sup>H. Ishikawa, S. Miwa, T. Maruyama, and M. Kamada, J. Appl. Phys. 71, 3898 (1992).

<sup>9</sup>M. Hollfelder, H. Hardtdegen, U. Breuer, H. Holzbrecher, R. Carius, and H. Lüth, *Proceedings of the Conference on Indium Phosphide and Related Materials, Hokkaido, Japan, 9–13 May 1995* (IEEE, New York, 1995), pp. 132–135.

<sup>10</sup>Z. Griffith, M. J. W. Rodwell, X.-M. Fang, D. Lubyshev, Y. Wu, J. M. Fastenau, and W. K. Liu, IEEE Electron Device Lett. 26, 530 (2005).

<sup>11</sup>J. Cheng, S. R. Forrest, B. Tell, D. Wilt, B. Schwartz, and P. D. Wright, J. Appl. Phys. **58**, 1780 (1985).

<sup>12</sup>Properties of Indium Phosphide (INSPEC/The Institution of Electrical Engineers, London, 1991), pp. 33–35.