# Millimeter-Wave CMOS Circuit Design

Hisao Shigematsu, Member, IEEE, Tatsuya Hirose, Forrest Brewer, and Mark Rodwell, Fellow, IEEE

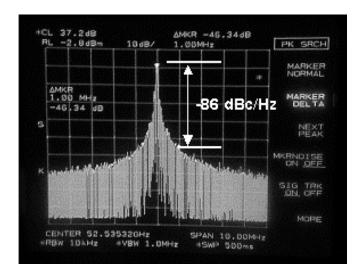

Abstract—We have developed a 27- and 40-GHz tuned amplifier and a 52.5-GHz voltage-controlled oscillator using  $0.18-\mu m$  CMOS. The line-reflect-line calibrations with a microstrip-line structure, consisting of metal1 and metal6, was quite effective to extract the accurate S-parameters for the intrinsic transistor on an Si substrate and realized the precise design. Using this technique, we obtained a 17-dB gain and 14-dBm output power at 27 GHz for the tuned amplifier. We also obtained a 7-dB gain and a 10.4-dBm output power with a good input and output return loss at 40 GHz. Additionally, we obtained an oscillation frequency of 52.5 GHz with phase noise of -86 dBc/Hz at a 1-MHz offset. These results indicate that our proposed technique is suitable for CMOS millimeter-wave design.

Index Terms—Millimeter wave, phase noise, tuned amplifier, voltage-controlled oscillator (VCO).

## I. Introduction

THE RAPID growth of wireless communication using, for example, mobile phones and wireless local area networks (LANs), has created a great demand for Si-based RF integrated circuits (RFICs), operating at microwave and millimeter-wave bands. These applications require a low production cost, thus, CMOS is the most attractive solution and the best component. However, the CMOS maximum oscillation frequency  $f_{\text{max}}$ , an important parameter for analog circuits, is no higher than those of other devices, such as SiGe HBT and III-V devices. Therefore, it has been difficult to realize analog circuits, especially tuned amplifiers, which operate at close to millimeter-wave frequencies. The III-V devices have accurate parameters around these frequencies because they are fabricated on semi-insulating substrates, and it is easy to eliminate the parasitic parameters. However, CMOS has to be fabricated on a conductive substrate, and its parameters are not applicable to this frequency range. Amplifiers based on III-V and SiGe technologies have been reported. However, there have been very few reports about CMOS amplifiers [1]. In this paper, we propose an accurate parameter-extraction technique with a line-reflect-line (LRL) calibration for CMOS technology, and report a 27- and 40-GHz tuned amplifier and a 52.5-GHz voltage-controlled oscillator (VCO). This parameter-extraction technique provides us with accurate S-parameters of the intrinsic transistor and enables the precise design of the integrated circuits.

Manuscript received April 20, 2004; revised August 7, 2004.

Digital Object Identifier 10.1109/TMTT.2004.840758

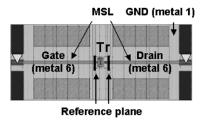

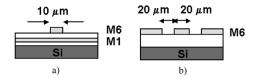

Fig. 1. Parameter-extraction pattern of the transistor.

## II. CIRCUIT DESIGN

## A. S-Parameter Extraction

The extraction of accurate parameters for transistors and transmission lines is important for millimeter-wave circuit design. To achieve this, we used a microstrip-line (MSL) structure, which consists of a metal1 ground and a metal6 signal line [2]. This line structure eliminates the effect of the conductive substrate and provides us with accurate characteristic impedance, allowing us to avoid unwanted differences between the simulation and measured values. The MSL characteristics, obtained through electric-magnetic (EM) simulation, agreed well with the measured results, even though our metal1 had slots to relax the stress. This enabled us to design the matching circuits more precisely. We prepared the parameter-extraction pattern for the transistor, as shown in Fig. 1.

This pattern consisted of an intrinsic transistor and outgoing electrode lines for the gate and drain, which uses metal6 with probe pads. We used LRL calibrations to extract the S-parameters. This method needs two lines of different lengths and an open pattern. Therefore, we also prepared on-wafer patterns. With this technique, we were able to set the calibration reference planes to the edges of the outgoing lines and obtain the intrinsic S-parameters. Yang et al. reported a measurement technique using line-reflect-reflect-match (LRRM) up to 110 GHz, but the reference plane is on the probe tips, as shown by the triangles in Fig. 1 [3]. Therefore, our extraction technique enables easier and more accurate measurement of the S-parameters of the intrinsic transistors [4].

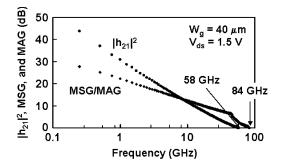

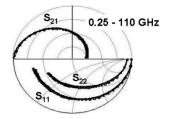

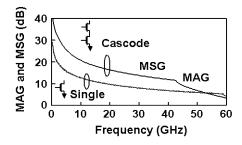

Fig. 2 shows the frequency dependence of the  $|h_{21}|^2$ , maximum stable gain (MSG) and the maximum available gain (MAG). The profiles were very smooth, and the cutoff frequency  $f_T$  and maximum oscillation frequency  $f_{\rm max}$  were 58 and 84 GHz. This indicates that we can obtain accurate S-parameters with this technique, and design the circuits precisely. Fig. 3 shows measured and simulated  $S_{11}$  and  $S_{22}$  from 0.25 to 110 GHz on a Smith chart.

The S-parameters turned smoothly up to 110 GHz, and no unwanted resonance could be seen up to 110 GHz. We extracted the transistor parameter and created the model. The model is

H. Shigematsu and T. Hirose are with the High-Speed Integrated Circuits Technology Division, Fujitsu Laboratories Ltd., Atsugi 243-0197, Japan.

F. Brewer and M. Rodwell are with the University of California at Santa Barbara, Santa Barbara, CA 93106 USA.

Fig. 2.  $|h_{21}|^2$ , MSG, and MAG of the intrinsic transistor from 0.25 to 110 GHz.

Fig. 3. Measured and simulated  $S_{11}$  and  $S_{22}$  from 0.25 to 110 GHz (dotted line: simulated data, solid line: measured data).

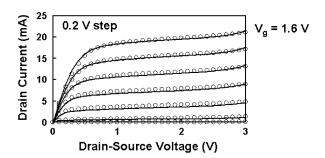

Fig. 4. Measured and simulated *I–V* (dotted lines: simulated data, solid lines: measured data).

in good agreement with the measured data shown in Fig. 3. Fig. 4 shows the measured and simulated I–V characteristics of the transistor with a gatewidth of 40  $\mu$ m. The off-breakdown voltage is over 3 V, where the body is tied to the source terminal. The model is also a good agreement with the measured data in dc characteristics. We used this model for the following designs.

# B. Tuned Amplifier Design

At millimeter-wave regions, the loss of the transmission line increases so the transistor's gain is very important for the CMOS amplifier design. A cascode configuration does not degrade the frequency-response at high-frequency regions due to the Miller effect. Therefore, it is superior to the single transistor configuration at high-frequency regions. Fig. 5 shows the MAG of the single and cascode transistors. The cascode configuration has a much larger stable gain than the single transistor configuration. We used the cascode configuration for the amplifier design.

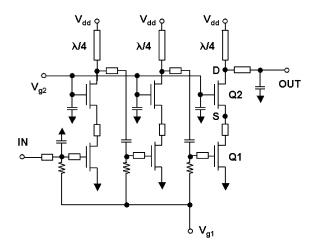

Fig. 6 shows a schematic of the tuned amplifier. It consists of three stages with a cascode configuration. Each drain bias was applied through a quarter-wavelength line. Each gate bias was applied through the high-impedance resistor. We used

Fig. 5. MAG and MSG of the single and cascode transistors.

Fig. 6. Schematic of the tuned amplifier.

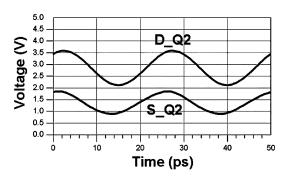

Fig. 7. Source and drain voltage of Q2 at 10-dBm input.

metal–insulator–metal (MIM) capacitors at the interstage. The design was based on gain matching, rather than power matching because of the insufficient gain of CMOS at millimeter-wave frequency range. We utilized a transmission line between Q1 and Q2 to stabilize each stage. The optimized 120- $\mu$ m lengths exist for the stabilization of the amplifier. The amplifier stability factor was above 50.

Fig. 7 shows the simulated results for the source and drain voltage of Q2 at the saturated 10-dBm input at 40 GHz. The maximum drain—source voltage of Q2 is less than 1.7 V. Therefore, both transistors Q1 and Q2 operate under the breakdown voltage.

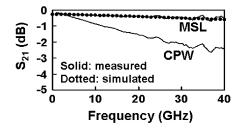

Next, we will mention the design for the transmission line. Fig. 8 shows the frequency dependence for the MSL and a coplanar-waveguide (CPW) line on an Si substrate. Fig. 9 shows their structures. For the MSL, metal1 was used for the ground planes and metal6 was used for the signal line. Metal1 shields the unwanted effects of the conductive substrate. The loss is

Fig. 8. Frequency dependence for the MSL and CPW on an Si substrate.

Fig. 9. Line structures on an Si substrate. (a) MSL (b) CPW.

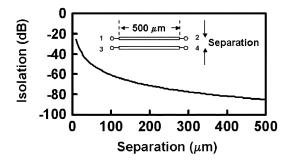

Fig. 10. Simulated isolation between two parallel lines at 40 GHz.

0.25 dB/mm for the MSL, and 2.3 dB/mm for the CPW at 40 GHz. The MSL had a much better performance than the CPW. The EM simulation result for the MSL was in good agreement with the measured one, as shown in this figure. The MSL structure can provide a precise design, and we applied it to the layout design.

When we use an MSL, we must consider the isolation between the adjacent lines because the coupling between the two adjacent lines changes the characteristic impedance. This degrades preciseness for the design, especially at millimeter-wave frequencies. Fig. 10 shows the simulated isolation between two parallel lines at 40 GHz. We obtained a -50-dB isolation at a distance of  $50~\mu m$ . This distance was sufficient to retain the characteristic impedance. Here, the length of the parallel line was  $500~\mu m$ . Even at a distance of  $20~\mu m$ , we obtained a -30-dB isolation at 40 GHz. This value was more than adequate for the layout. However, we used a 50- $\mu m$  separation to eliminate the unwanted effects of coupling completely this time.

## C. VCO Design

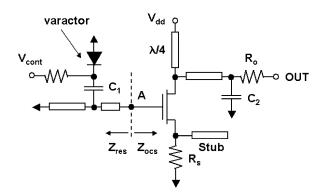

Fig. 11 shows a schematic of the VCO. We chose a single-ended fundamental oscillator design to demonstrate the effectiveness of our technique. Recently, harmonics-type VCOs using CMOS technology have been reported to obtain a higher oscillation frequency [5]. This kind of VCO usually consists of two VCOs and combines each of the second harmonics of the output. The fundamental frequencies cancel each other out at the cross point. The highest oscillation frequency ever reported

Fig. 11. Schematic of the VCO.

in a CMOS fundamental oscillator was 51 GHz without a special process, such as a high-resistivity substrate and buried and epi layers [6]. (This oscillator used 0.13- $\mu$ m technology.)

We designed the VCO with  $0.18-\mu m$  CMOS technology to overcome this oscillation frequency. If we obtain a higher oscillation frequency in the fundamental frequency, the oscillation frequency in the harmonics VCO also increases because this is the basis of the harmonics VCO design. We used a combination of the extrinsic source resistance of  $R_s$  and the parallel source stub to generate negative resistance around the target frequency. The tank inductor was made of an MSL to realize an accurate inductance. We used a multifinger CMOS diode for the varactors. To reduce the gate resistance, we used a multifinger transistor in the oscillator core. The gate resistance is a parameter that is very sensitive to the oscillation conditions. The resistor was located at the output port to realize impedance matching and isolation between the output and oscillator core. The drain bias was applied through the quarter-wavelength line at a fundamental frequency. Regarding the design procedure, we first determined the startup oscillation conditions with the extracted S-parameters as follows. The negative resistance generated by the oscillator must exceed the resistive losses of the resonator. This means that the VCO must have a net negative resistance

$$\operatorname{Re}\{Z_{\text{osc}} + Z_{\text{res}}\} < 0. \tag{1}$$

Also, we set the oscillation frequency according to the equation

$$\frac{\partial \operatorname{Im}\{Z_{\operatorname{osc}} + Z_{\operatorname{res}}\}}{\partial \omega} > 0 \tag{2}$$

where

$$\operatorname{Im}\{Z_{\text{osc}} + Z_{\text{res}}\} = 0. \tag{3}$$

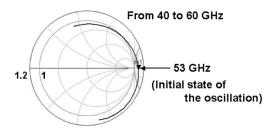

Fig. 12 shows the simulated results for the VCO startup frequency at point A, with S-parameter analysis. In this method, the startup oscillation frequency is 53 GHz.

After setting the startup oscillation frequency, we also performed a harmonic-balance simulation with a large-signal model to compensate for the difference between the startup oscillation frequency and the steady-state one.

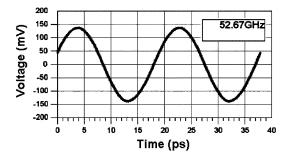

Fig. 13 shows the harmonic-balance simulation result of the VCO. The oscillation frequency of 52.7 GHz is slightly lower than that using S-parameter analysis. An output of approximately  $0.3\ V_{pp}$  was obtained.

Fig. 12. Oscillation frequency simulations with S-parameters.

Fig. 13. Harmonic-balance simulations with the extracted model.

Fig. 14. 27-GHz tuned amplifier.

# III. CIRCUIT MEASUREMENTS

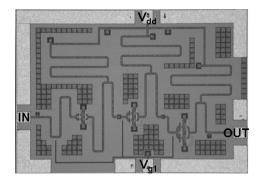

The circuits were fabricated using a 0.18- $\mu m$  mixed-signal process. In this process, metal6 was 2- $\mu m$  thick to reduce losses. The measured transistor's cutoff frequency  $f_T$  and the maximum oscillation frequency  $f_{\rm max}$  were 58 and 84 GHz, respectively. Fig. 14 shows a microphotograph of the 27-GHz tuned amplifier. The chip size was  $1.2 \times 1.7$  mm and the power dissipation was 300 mW. We measured the S-parameters using an HP8510XF network analyzer.

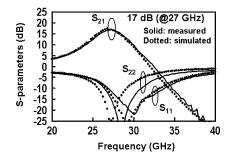

Fig. 15 shows the frequency characteristics of the amplifier at a  $V_{dd}$  of 3 V. A small-signal gain of 17 dB was obtained at 27 GHz. This is the highest yet reported for a CMOS amplifier at 27 GHz.  $S_{11}$  and  $S_{22}$  were below -10 dB. The simulation agreed well with the measurements.

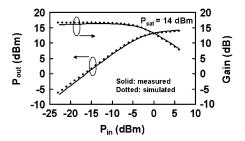

We also measured the  $P_{\rm in}$ – $P_{\rm out}$  characteristics at 27 GHz (Fig. 16). We used an HP1131 frequency synthesizer to generate the input signal, and the output signal was measured with an HP E4418B power meter. We obtained saturated power of 14 dBm at 27 GHz. As far as we know, this performance is the best ever reported for CMOS amplifiers. The simulation results with the large-signal model are also shown in this figure. This simulation agreed well with the measurements, as well as with

Fig. 15. Measured S-parameters of the 27-GHz tuned amplifier.

Fig. 16. Measured  $P_{\rm in}$ - $P_{\rm out}$  characteristics at 27 GHz.

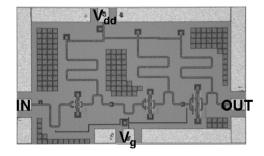

Fig. 17. 40-GHz tuned amplifier.

Fig. 18. Measured S-parameters of the 40-GHz tuned amplifier.

the small-signal characteristics. Our amplifier can be applied to short-range wireless communication.

Fig. 17 shows a microphotograph of the 40-GHz tuned amplifier. The chip size was  $1.2 \times 1.7$  mm and the power dissipation was 300 mW. The minimum separation between one line and the other line was 50  $\mu$ m to prevent coupling, as previously mentioned.

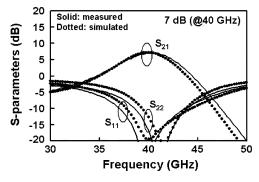

Fig. 18 shows the frequency characteristics of the amplifier at  $V_{dd}$  of 3 V. A small-signal gain of 7 dB was obtained at 40 GHz. The impedance matching was done well for the input

Fig. 19. Measured  $P_{\rm in}$ - $P_{\rm out}$  characteristics at 40 GHz.

## TABLE I PERFORMANCE COMPARISON

|           | Freq. (GHz) | Gain (dB) | P <sub>out</sub> (dBm) | Technology   |

|-----------|-------------|-----------|------------------------|--------------|

| This work | 27          | 17        | 14                     | 0.18 μm      |

| This work | 40          | 7         | 10.4                   | 0.18 μm      |

| [7]       | 40          | 9.5       | 4<br>(P1dB)            | 90 nm<br>SOI |

| [8]       | 20          | 5.8       | 1<br>(P1dB)            | 90 nm        |

| [8]       | 40          | 6         | -1.5                   | 90 nm        |

and output, and  $S_{11}$  and  $S_{22}$  were below -15 dB. The simulation agreed well with the measurement, as well as with the 27-GHz tuned amplifier. This performance is comparable to the previous reported 90-nm silicon-on-insulator (SOI) CMOS amplifier [7]. This superior performance can be obtained without such advanced technology.

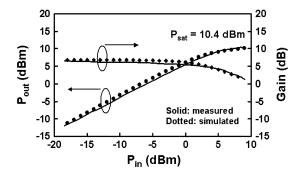

We also measured the  $P_{\rm in}$ – $P_{\rm out}$  characteristics at 40 GHz (Fig. 19). We obtained saturated power of 10.4 dBm at 40 GHz. As far as we know, this performance is the best yet reported for CMOS amplifiers. The simulation results with the large-signal model are also shown in this figure. The simulation agreed well with the measurements, as well as with the small-signal characteristics. These results indicate that our proposed technique is quite effective for the medium-power amplifier at millimeter-wave frequencies. Our amplifier is applicable to short-range wireless communication. Table I summarizes the current CMOS amplifiers.

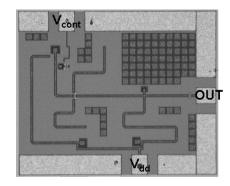

Fig. 20 shows a microphotograph of the VCO. The chip size was  $0.8 \times 1.0$  mm, and the power dissipation was 41 mW. Fig. 21 shows the measured oscillation spectrum of the VCO.

This measurement was done with waveguided (WG) tubes. The oscillator output signal was down-converted by the HP4211A mixer module, and the spectrum was measured by the HP2411 spectrum analyzer. We obtained an oscillation frequency of 52.5 GHz and output power of -8 dBm (after removing the WG tube loss). This oscillation frequency is the highest ever reported for a fundamental VCO without a high-resistivity substrate, such as an SOI structure, or buried and epi layers. The measured oscillation frequency is nearly equal to the simulated one. These results indicate our proposed LRL

Fig. 20. 53-GHz VCO.

Fig. 21. Measured oscillation frequency of the VCO.

calibration design technique is promising for high-frequency designs. The control range was 100 MHz. In this study, we intended to use the loose coupling capacitor for the varactor to confirm the design accuracy and this causes the narrow control range. We can easily improve the frequency control range by changing the ratio of the coupling capacitor and varactor.

# IV. CONCLUSION

We developed a CMOS tuned amplifier and VCO based on a 0.18- $\mu$ m process. The LRL calibration technique along with an MSL structure consisting of metal1 and metal6 enabled us to extract the accurate S-parameters for the intrinsic transistor and realize the precise design. Using this method, we obtained a 17-dB gain and a 14-dBm output power with good input and output return loss at 27 GHz. We also obtained a 7-dB gain and a 10.4-dBm output power, with a good input and output return loss at 40 GHz. Additionally, we realized an oscillation frequency of 52.5 GHz, with phase noise of -86 dBc/Hz at 1-MHz offset for the VCO. These results indicate that our proposed technique is promising for millimeter-wave-circuit designs.

## ACKNOWLEDGMENT

The authors would like to thank Dr. M. Urteaga, University of California at Santa Barbara, and Dr. Takigawa, Fujisu Laboratories Ltd., Japan, for their advice, encouragement, and support.

## REFERENCES

- B. Floyd, L. Shi, U. Taur, I. Lagnado, and K. K. O, "A 23.5-GHz SOI CMOS tuned amplifier," *IEEE Trans. Microw. Theory Tech.*, vol. 50, no. 9, pp. 2193–2196, Sep. 2002.

- [2] H. Shigematsu, M. Sato, T. Hirose, F. Brewer, and M. Rodwell, "A 40 Gb/s CMOS distributed amplifier for fiber-optic communication systems," in *IEEE Int. Solid-State Circuits Conf. Tech. Dig.*, Feb. 2004, pp. 476–477.

- [3] M. Yang, P. Ho, Y. Wang, T. Yeh, and Y. Chia, "Broadband small-signal model and parameter extraction for deep sub-micron MOSFETS valid up to 110 GHz," in RF Integrated Circuits Dig., Jun. 2003, pp. 369–372.

- [4] M. Urteaga, S. Krishnan, D. Scott, Y. Wei, M. Dahlstrom, S. Lee, and M. J. W. Rodwell, "Submicron InP-based HBT's for ultra-high frequency amplifiers," *Int. J. High-Speed Electron. Syst.*, to be published.

- [5] R. Liu, H. Chang, and C. Wang, "A 63 GHz VCO using a standard 0.25 μm CMOS process," in *IEEE Int. Solid-State Circuits Conf. Tech. Dig.*, Feb. 2004, pp. 446–447.

- [6] M. Tiebout, H. Wohlmuth, and W. Simburger, "A 1 V 51 GHz fully-integrated VCO in 0.12 μm CMOS," in *IEEE Int. Solid-State Circuits Conf. Tech. Dig.*, Feb. 2002, pp. 300–301.

- [7] F. Ellinger, "26–42 GHz SOI CMOS low noise amplifier," IEEE J. Solid-State Circuits, vol. 39, no. 3, pp. 522–528, Mar. 2004.

- [8] M. A. Masud, H. Zirath, M. Ferndahl, and H. Vickes, "90 nm CMOS MMIC amplifier," in RF Integrated Circuits Dig., Jun. 2004, pp. 201–204

**Tatsuya Hirose** received the B.E. degree from Tokyo Denki University, Tokyo, Japan, in 1987, the M.E. degree from Hokkaido University, Sapporo, Japan, in 1989, and the Ph.D. degree from Tohoku University, Sendai, Japan, in 2004.

He is currently a Senior Researcher with the High-Speed Integrated Circuits Technology Division, Fujitsu Laboratories Ltd., Atsugi, Japan. In 1989, he joined Fujitsu Laboratories, Kanagawa, Japan, where he was engaged in research on characterization and modeling for heterostructure devices

and the development of MMICs based on their technologies. His current research interest includes microwave and millimeter-wave IC design for automotive radar systems, wireless communication systems, and fiber-optic communication systems.

Dr. Hirose is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan.

**Forrest Brewer** received the B.S. degree in physics (with honors) from the California Institute of Technology, Pasadena, and the M.S. and Ph.D. degrees in computer science from the University of Illinois at Urbana-Champaign.

He is currently a Professor with the University of California at Santa Barbara. His research spans high-level very large scale integration (VLSI) system formal modeling to physical VLSI design for power, noise, and timing constraints. This research includes synthesis of production-based specifications (tech-

nology underlying the Synopsys Protocol Compiler · toolset), NDFA-based scheduling (symbolic scheduling), and related high-level synthesis procedures. His current research includes high-reliability finite-state machine synthesis for field-programmable gate array (FPGA) and deep-submicrometer CMOS, as well as cryogenic ultra-low-power CMOS sensors.

Dr. Brewer has served on the Technical Advisory Boards of several silicon valley startups and is a member of the Association for Computing Machinery (ACM), the IEEE Antennas and Propagation Society (IEEE AP-S), Tau Beta Pi, and Phi Kappa Phi.

**Hisao Shigematsu** (M'04) graduated from Osaka University, Osaka, Japan, in 1990.

He is currently a Senior Researcher with the High-Speed Integrated Circuits Technology Division, Fujitsu Laboratories Ltd., Atsugi, Japan. In 1990, he joined Fujitsu Laboratories, Kanagawa, Japan, where he was engaged in research on development of high-speed compound semiconductor devices (high electron-mobility transistors (HEMTs), HBTs) and ICs. In 2003, he was a Visiting Researcher with the University of California at

Santa Barbara, where he was involved with millimeter-wave CMOS circuits. His current research interest includes high-speed IC design for fiber-optic communication systems.

Mr. Shigematsu is a member of the Japan Society of Applied Physics.

Mark Rodwell (M'89–SM'99–F'03) received the B.S. degree from the University of Tennessee at Knoxville, in 1980, and the M.S. and Ph.D. degrees from Stanford University, Stanford, CA, in 1982 and 1988, respectively.

He is currently Professor and Director of the Compound Semiconductor Research Laboratories and the National Science Foundation (NSF) Nanofabrication Users Network (NNUN), University of California at Santa Barbara. From 1982 to 1984, he was with AT&T Bell Laboratories, Whippany, N.J. His

research focuses on high-bandwidth InP bipolar transistors and multigigahertz bipolar circuit design. His recent research activities also include microwave power amplifiers, and monolithic analog and digital transistor circuits operating above 100 GHz.

Dr. Rodwell was the recipient of a 1989 NSF Presidential Young Investigator Award. His work on GaAs Schottky-diode ICs for subpicosecond/millimeter-wave instrumentation was awarded the 1997 IEEE Microwave Prize.