UNIVERSITY of CALIFORNIA Santa Barbara

## III-V Ultra-Thin-Body InGaAs/InAs MOSFETs for Low Standby Power Logic Applications

A Dissertation submitted in partial satisfaction of the requirements for the degree

> Doctor of Philosophy in Electrical and Computer Engineering

> > by

Cheng-Ying Huang

Committee in Charge:

Professor Mark J. W. Rodwell, Chair Professor Arthur C. Gossard Professor John E. Bowers Professor Umesh K. Mishra

September 2015

The Dissertation of Cheng-Ying Huang is approved.

Professor Arthur C. Gossard

Professor John E. Bowers

Professor Umesh K. Mishra

Professor Mark J. W. Rodwell, Committee Chair

August 2015

# III-V Ultra-Thin-Body InGaAs/InAs MOSFETs for Low Standby Power Logic Applications

Copyright  $\bigodot$  2015

by

Cheng-Ying Huang

#### Acknowledgements

Four years in UC Santa Barbara is not a long journey but definitely a wonderful adventure in my life. This adventure would not have been completed without the help and efforts from so many people. I am truly indebted to my advisor, Professor Mark Rodwell, for his support and guidance during my PhD studies. I was really fortunate to work with him and have greatly benefited from his extraordinary talent and enthusiasm on semiconductor device technology. I am also deeply thankful to Professor Arthur Gossard, for his encouragement and invaluable input on material growth. I would also want to thank my committee members, Professor John Bowers and Professor Umesh Mishra, for their time, efforts, and valuable suggestions on my work.

I started my PhD studies as a MBE grower in 2011. I do owe my sincere thanks to Dr. Jeremy Law for teaching me MBE growth on system C and mentoring me for the development of AlAlSb barriers. I did learn rapidly from him, widely from MBE growth, materials characterizations, to device physics. I would also like to thank John English, Hong Lu, Kurt Olsson, Peter Burke, Alan Liu and Justin Norman for their help on system C. I always called John, my MBE savior, because of his incredible knowledge and experience in MBE tools as well as his amazing skill for saving a dropped sample. I would especially like to thank Hong for her kindness and always being so helpful to me during my days in MBE lab.

I would like to thank Dr. Doron Cohen-Elias for teaching me InGaAs/InP MOCVD growth. Doron ramped up the MOCVD source/drain regrowth that greatly improved the throughput of UCSB MOSFET, speeding up our learning curve and reducing the process variations. I was fortunate that I had the opportunity to learn with Doron and the access to abundant growth resources in MBE lab and MOCVD lab. I would also like to thank Chong Zhang, David Whitlatch, and the MOCVD staff members for their help on MOCVD maintenance.

In the last two years of my PhD studies, I was more focused on III-V MOSFET fabrications. In fact, the story in this dissertation would never have been possible without the efforts and contributions from Dr. Andrew Carter and Dr. Sanghoon Lee. Andy began developing the gate last process flow, and later on, Sanghoon developed the HSQ dummy gate process and the digital etch technique. The HSQ dummy gate process enables extremely small gate lengths, and the digital etch technique greatly improves transistor performance and has now been widely used in III-V MOSFET community. I was so lucky to help Andy and Sanghoon develop the gate last process flow by providing MBE channel growth and MBE/MOCVD source/drain regrowth. I was even luckier that I could learn the whole process flow with Andy and Sanghoon, and finally make my own devices, and continue their successful story.

I would like to express my gratitude to Gift Chobpattana and Professor Susanne Stemmer for their incredible ALD magic of high-k dielectrics on III-V channels. The TMA/N plasma pretreatment might be the best recipe in the world that surprised everyone with a demonstration of subthreshold swing around 61 mV/dec. I am also grateful to Professor Andrew Kummel in UC San Diego and Professor Paul McIntyre in Stanford for the long-term cooperation and the discussions on the high-k/III-V interfaces.

There are too many people whom I do owe my sincere thanks. Thanks to Pro-

fessor Debdeep Jena for his valuable discussion on 2DEG simulation. Thanks to Stephan Kraemer for his incredible skills on STEM images. Thanks to Dr. Xinyu Bao and Dr. Errol Sanchez from Applied Materials for providing III-V buffer on 12 inch Si substrates. Thanks to Hanwei Chiang and Prateek Choudhary for their help on TEM sample preparation. Thanks to Haoran Li for her assistance on AFM measurements. Thanks to all the UCSB cleanroom staff members (William Mitchell, Brian Thibeault, Brain Lingg, Don Freeborn, Aidan Hopkins, and Tom Reynolds) for their support and the maintenance of the process tools. Without their dedication, this work would never have been possible.

I would also like to thank all the members of Rodwell's group (Johann, Rob, Hyunchul, Seong-Kyun, Trea, Afrodite) for their help and assistance. I am deeply thankful to UCSB Taiwanese student association (TSA), TSA basketball team, and TSA softball team for your friendship and company in the past four years. I also want to thank my friends in Taiwan who constantly encourage me and care for me.

Last, I would like to thank my girlfriend, Fuqin. I am truly blessed to meet you here in Santa Barbara and later in Puerto Rico. I would like to thank my parents and my brother, for their unconditional love and patience. Without your encouragement and support, I could never have reached this far.

#### Curriculum Vitæ Cheng-Ying Huang

Cheng-Ying Huang

| Personal  |                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------|

| Jan. 1985 | Born in Kaohsiung, Taiwan.                                                                                            |

| Education |                                                                                                                       |

| 2011-2015 | Ph.D. in Electrical and Computer Engineering, University of Cal-<br>ifornia, Santa Barbara, USA.                      |

| 2007-2009 | M.S. in Graduate Institute of Electronics Engineering, National Taiwan University, Taiwan.                            |

| 2003-2007 | B.S. in Materials Science and Engineering and minor degree in Electrophysics, National Chiao Tung University, Taiwan. |

| Awards    |                                                                                                                       |

| 2015      | UCSB ECE Department Dissertation Fellowship.                                                                          |

| 2015      | Best Student Paper Award, International Symposium on VLSI<br>Technology, Systems and Applications (VLSI-TSA).         |

| 2014      | Best Student Paper Award, IEEE Lester Eastman Conference on<br>High Performance Devices.                              |

| 2013      | Outstanding Student Paper Award (Poster Presentation), North<br>American Molecular Beam Epitaxy Conference.           |

#### **First Author Publications**

- C. Y. Huang, P. Choudhary, S. Lee, S. Kraemer, V. Chobpattana, B. Thibeault, W. Mitchell, S. Stemmer, A. Gossard, and M. Rodwell, *"12 nm-Gate-Length Ultrathin-Body InGaAs/InAs MOSFETs with 8.3*·10<sup>5</sup>:1 I<sub>ON</sub>/I<sub>OFF</sub>," 73rd IEEE Device Research Conference(DRC), pp. 260-261, 2015. (Conference oral presentation and proceeding)

- [2] C. Y. Huang, S. Lee, E. Wilson, P. Long, M. Povolotskyi, V. Chobpattana, S. Stemmer, A. C. Gossard, G. Klimeck, and M. J. W. Rodwell, "Comparison of ultra-thin InAs and InGaAs quantum wells and ultra-thin-body surfacechannel MOSFETs," International Conference on Indium Phosphide and Related Materials (IPRM), 2015. (Conference oral presentation and abstract)

- [3] C. Y. Huang, X. Bao, Z. Ye, S. Lee, H. Chiang, H. Li, V. Chobpattana, B. Thibeault, W. Mitchell, S. Stemmer, A. Gossard, E. Sanchez, and M. Rodwell, "Ultrathin InAs-Channel MOSFETs on Si substrates," International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), pp. 1-2, 2015. (Conference oral presentation and proceeding)

- [4] C. Y. Huang, S. Lee, V. Chobpattana, S. Stemmer, A. C. Gossard, B. J. Thibeault, W. Mitchell, and M. J. W. Rodwell, "Low power III-V InGaAs MOSFETs featuring InP recessed source/drain spacers with I<sub>on</sub> =120 μA/μm at I<sub>off</sub> = 1 nA/μm and V<sub>DS</sub> = 0.5 V," IEEE International Electron Device Meeting (IEDM), pp. 586-589, 2014. (Conference oral presentation and proceeding)

- [5] C. Y. Huang, S. Lee, V. Chobpattana, S. Stemmer, A. C. Gossard, and M. J. W. Rodwell, "Leakage current suppression in InGaAs-channel MOSFETs: Recessed InP source/drain spacers and InP channel caps," IEEE Proceeding of Lester Eastman Conference on High Performance Devices (LEC), pp. 1-4, 2014. (Conference oral presentation and proceeding)

- [6] C. Y. Huang, S. Lee, D. C. Elias, J. J. M. Law, V. Chobpattana, S. Stemmer, A. C. Gossard, and M. J. W. Rodwell, "Influence of InP source/drain layers upon the DC characteristics of InAs/InGaAs MOSFETs," IEEE 72nd Device Research Conference (DRC), pp. 225-226, 2014. (Conference oral presentation and proceeding)

- [7] C. Y. Huang, J. J. M. Law, H. Lu, M. J. W. Rodwell, and A. C. Gossard, "Two dimensional electron transport in modulation-doped InGaAs/AlAsSb ultrathin quantum wells," Journal of Applied Physics, v. 115, p. 123711, 2014. (Journal paper)

- [8] C. Y. Huang, S. Lee, D. C. Elias, J. J. M. Law, A. D. Carter, V. Chobpattana, S. Stemmer, A. C. Gossard, M. J. W. Rodwell, "Reduction of leakage current in In<sub>0.53</sub>Ga<sub>0.47</sub>As channel metal-oxide-semiconductor field-effecttransistors using AlAs<sub>0.56</sub>Sb<sub>0.44</sub> confinement layers," Applied Physics Letters, v. 103, p. 203502, 2013. (Journal paper)

- [9] C. Y. Huang, A. D. Carter, J. J. M. Law, S. Lee, D. C. Elias, V. Chobpattana, S. Stemmer, A. C. Gossard, M. J. W. Rodwell, "High Performance In<sub>0.53</sub> Ga<sub>0.47</sub>As Channel Metal-Oxide-Semiconductor Field-Effect Transistors with AlAs<sub>0.56</sub>Sb<sub>0.44</sub> Barrier Layer," Semiconductor Research Corporation (SRC) TECHCON, Austin, 2013. (Conference oral presentation and proceeding)

- [10] C. Y. Huang, A. D. Carter, J. J. M. Law, S. Lee, D. C. Elias, V. Chobpattana, S. Stemmer, A. C. Gossard, M. J. W. Rodwell, "In<sub>0.53</sub> Ga<sub>0.47</sub> As Channel

Metal-Oxide-Semiconductor Field-Effect Transistors with  $AlAs_{0.56}Sb_{0.44}$  Barrier Layers and InAs MBE Source/Drain Regrowth," 30th North American Molecular Beam Epitaxy Conference (NAMBE), 2013. (Conference oral presentation and abstract)

[11] C. Y. Huang, J. J. M. Law, H. Lu, M. J. W. Rodwell, and A. C. Gossard, "Development of AlAsSb as barrier material for sub-10-nm Lg InGaAs channel nMOSFETs," MRS Online Proceedings Library 1561, mrss13-1561-cc01-10, 2013. (Conference oral presentation and proceeding)

#### Other Publications

- P. Choudhary, C. -Y. Huang, J.C. Rode, H.W. Chiang, M.J.W. Rodwell, "InGaAs/InP DHBTs using MOCVD Selective Emitter Regrowth," International Conference on Indium Phosphide and Related Materials (IPRM), 2015.

- [2] M. Rodwell, C.-Y. Huang, S. Lee, A.C. Gossard, V. Chobpattanna, S. Stemmer, B. Thibeault, W. Mitchell, P. Long, E. Wilson, S. Mehrotra, M. Povolotskyi, G. Klimeck, "Record-Performance Thermally-Limited Devices, Prospects for High-On-Current Steep Subthreshold Swing Devices," International Conference on Indium Phosphide and Related Materials (IPRM), 2015. (Invited paper)

- [3] M. J. W. Rodwell, C.-Y. Huang, J. Rode, P. Choudhary, S. Lee, A.C. Gossard, P. Long, E. Wilson, S. Mehrotra, M. Povolotskyi, G. Klimeck, M. Urteaga, B. Brar, V. Chobpattanna, S. Stemmer, "Transistors for VLSI, for Wireless: A View Forwards Through Fog," 73rd IEEE Device Research Conference(DRC), 2015. (Invited paper)

- [4] M. J. Rodwell, C. Y. Huang, S. Lee, V. Chobpattana, B. Thibeault, W. Mitchell, S. Stemmer, A. Gossard, "Record-Performance In (Ga) As MOS-FETS Targeting ITRS High-Performance and Low-Power Logic," ECS Transactions, v. 66, pp.135-140, 2015. (Invited paper)

- [5] S. Lee, V. Chobpattana, C. Y. Huang, B. J. Thibeault, W. Mitchell, V. Chobpattana, S. Stemmer, A. C. Gossard, M. J. W. Rodwell, "Record I<sub>on</sub> (0.50 mA/μm at V<sub>DD</sub> = 0.5 V and I<sub>off</sub> = 100 nA/μm) 25 nm-Gate-Length ZrO<sub>2</sub>/InAs/InAlAs MOSFETs," Symposium on VLSI Technology, pp. 1-2, 2014.

- [6] S. Lee, C. Y. Huang, D. C. Elias, B. J. Thibeault, W. Mitchell, V. Chobpattana, S. Stemmer, A. C. Gossard, M. J. W. Rodwell, "Highly Scalable Raised Source/Drain InAs Quantum Well MOSFETs Exhibiting I<sub>on</sub> =482 μA/μm

at  $I_{\text{off}}$  100 nA/µm and  $V_{\text{DD}} = 0.5$  V," IEEE Electron Device Letters, pp. 621-623, 2014.

- [7] M. J. Rodwell, S. Lee, C. Y. Huang, D. Elias, V. Chobpattanna, J. Rode, H.-W. Chiang, P. Choudhary, R. Maurer, M. Urteaga, B. Brar, A. C. Gossard, S. Stemmer, "Nanometer InP electron devices for VLSI and THz applications," 72nd Device Research Conference (DRC), pp. 215-216, 2014.

- [8] S. Lee, C. Y. Huang, D. C. Elias, B. J. Thibeault, W. Mitchell, V. Chobpattana, S. Stemmer, A. C. Gossard, M. J. W. Rodwell, "35 nm-L<sub>g</sub> raised S/D In<sub>0.53</sub>Ga<sub>0.47</sub> As quantum-well MOSFETs with 81 mV/decade subthreshold swing at V<sub>DS</sub> = 0.5 V," 72nd Device Research Conference (DRC), pp. 223-224, 2014.

- [9] D. C. Elias, A. Sivananthan, C. Zhang, S. Keller, H. W. Chiang, J. J. M. Law, B. J. Thibeault, W. J. Mitchell, S. Lee, A. D. Carter, C.-Y. Huang, V. Chobpattana, S. Stemmer, S. P. Denbaars, L. A. Coldren and M. J. W. Rodwell, "Formation of InGaAs fins by atomic layer epitaxy on InP sidewalls," Jpn. J. Appl. Phys., vol. 53, no. 6, pp. 065503, 2014.

- [10] S. Lee, C. Y. Huang, D. C. Elias, J. J. M. Law, V. Chobpattana, S. Krmer, B. J. Thibeault, W. Mitchell, S. Stemmer, A. C. Gossard, and M. J. W. Rodwell, "High performance raised source/drain InAs/In<sub>0.53</sub>Ga<sub>0.47</sub>As channel metal-oxide-semiconductor field-effect-transistors with reduced leakage using a vertical spacer," Applied Physics Letters, v. 103, p. 233503, 2013.

- [11] S. Lee, C. Y. Huang, A. D. Carter, D. C. Elias, J. J. M. Law, V. Chobpattana, S. Krmer, B. J. Thibeault, W. Mitchell, S. Stemmer, A. C. Gossard, and M. J. W. Rodwell, "Record Extrinsic Transconductance (2.45 mS/μm at V<sub>DS</sub> = 0.5 V) InAs/In<sub>0.53</sub> GaAs Channel MOSFETs Using MOCVD Source-Drain Regrowth," Symposium on VLSI Technology, T246, 2013.

- [12] S. Lee, C. Y. Huang, A. D. Carter, J. J. M. Law, D. C. Elias, V. Chobpattana, B. J. Thibeault, W. Mitchell, S. Stemmer, A. C. Gossard, and M. J. W. Rodwell, "High Transconductance Surface Channel In<sub>0.53</sub> Ga<sub>0.47</sub> As MOSFETs Using MBE Source-Drain Regrowth and Surface Digital Etching," International Conference on Indium Phosphide and Related Materials (IPRM), pp. 1-2, 2013.

- [13] A. D. Carter, S. Lee, D. C. Elias, C. -Y. Huang, J. J. M. Law, W. Mitchell, B. Thibeault, V. Chobpattana, S. Stemmer, A. C. Gossard, M. J. W. Rodwell, "Performance impact of post-regrowth channel etching on InGaAs MOS-FETs having MOCVD source-drain regrowth," 71st Device Research Conference (DRC), pp. 23-24, 2013.

- [14] D. C. Elias, J. J. M. Law, H. W. Chiang, A. Sivananthan, C. Zhang, B. J. Thibeault, W. J. Mitchell, S. Lee, A. D. Carter, C.-Y. Huang, V. Chobpattana, S. Stemmer, S. Keller, and M. J. W. Rodwell, "Formation of Sub-10 nm width InGaAs finFETs of 200 nm Height by Atomic Layer Epitaxy," 71st Device Research Conference (DRC), pp. 1-2, 2013.

- [15] V. Chobpattana, J. Son, J. J. M. Law, R. Engel-Herbert, C. Y. Huang, and S. Stemmer, "Nitrogen-passivated dielectric/InGaAs interfaces with sub-nm equivalent oxide thickness and low interface trap densities," Applied Physics Letters, v. 102, p. 022907, 2013.

- [16] J. J. M. Law, A. D. Carter, S. Lee, C. -Y. Huang, H. Lu, M. J. W. Rodwell, and A. C. Gossard, "CoDoping of In<sub>x</sub>Ga<sub>1x</sub>As with Silicon and Tellurium for Improved Ultra-Low Contact Resistance," Journal of Crystal Growth, v. 378, p. 92, 2013.

- [17] M. L. Che, C. Y. Huang, S. Choang, Y. H. Chen, and J. Leu, "Thermal and mechanical properties of hybrid methylsilsesquioxane/poly (styreneb-4-vinylpyridine) low-k dielectrics using a late porogen removal scheme," J. Mater. Res., v. 25, p. 1049, 2010.

#### Abstract

## III-V Ultra-Thin-Body InGaAs/InAs MOSFETs for Low Standby Power Logic Applications

by

#### Cheng-Ying Huang

As device scaling continues to sub-10-nm regime, III-V InGaAs/InAs metaloxide-semiconductor field-effect transistors (MOSFETs) are promising candidates for replacing Si-based MOSFETs for future very-large-scale integration (VLSI) logic applications. III-V InGaAs materials have low electron effective mass and high electron velocity, allowing higher on-state current at lower  $V_{DD}$  and reducing the switching power consumption. However, III-V InGaAs materials have a narrower band gap and higher permittivity, leading to large band-to-band tunneling (BTBT) leakage or gate-induced drain leakage (GIDL) at the drain end of the channel, and large subthreshold leakage due to worse electrostatic integrity. To utilize III-V MOSFETs in future logic circuits, III-V MOSFETs must have high on-state performance over Si MOSFETs as well as very low leakage current and low standby power consumption. In this dissertation, we will report InGaAs/InAs ultra-thin-body MOSFETs. Three techniques for reducing the leakage currents in InGaAs/InAs MOSFETs are reported as described below.

1) Wide band-gap barriers: We developed  $AlAs_{0.44}Sb_{0.56}$  barriers lattice-match to InP by molecular beam epitaxy (MBE), and studied the electron transport in  $In_{0.53}Ga_{0.47}As/AlAs_{0.44}Sb_{0.56}$  heterostructures. The InGaAs channel MOS- FETs using  $AlAs_{0.44}Sb_{0.56}$  bottom barriers or p-doped  $In_{0.52}Al_{0.48}As$  barriers were demonstrated, showing significant suppression on the back barrier leakage.

2) Ultra-thin channels: We investigated the electron transport in InGaAs and InAs ultra-thin quantum wells and ultra-thin body MOSFETs ( $t_{\rm ch} \sim 2-4$  nm). For high performance logic, InAs channels enable higher on-state current, while for low power logic, InGaAs channels allow lower BTBT leakage current.

3) Source/Drain engineering: We developed raised InGaAs and recessed InP source/drain spacers. The raised InGaAs source/drain spacers improve electro-statics, reducing subthreshold leakage, and smooth the electric field near drain, reducing BTBT leakage. With further replacement of raised InGaAs spacers by recessed, doping-graded InP spacers at high field regions, BTBT leakage can be reduced  $\sim 100$ :1.

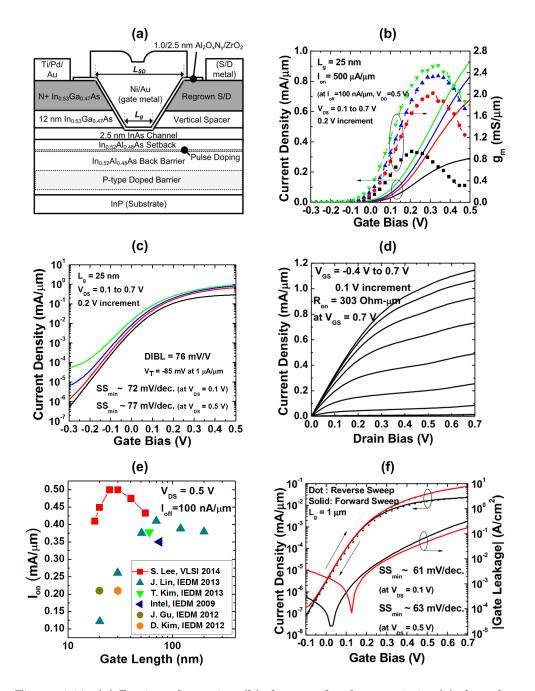

Using the above-mentioned techniques, record high performance InAs MOS-FETs with a 2.7 nm InAs channel and a ZrO<sub>2</sub> gate dielectric were demonstrated with  $I_{\rm on} = 500 \ \mu A/\mu m$  at  $I_{\rm off} = 100 \ nA/\mu m$  and  $V_{\rm DS} = 0.5 \ V$ , showing the highest on-state performance among all the III-V MOSFETs and comparable performance to 22 nm Si FinFETs. Record low leakage InGaAs MOSFETs with recessed InP source/drain spacers were also demonstrated with minimum  $I_{\rm off} = 60 \ pA/\mu m$  at 30 nm- $L_{\rm g}$ , and  $I_{\rm on} = 150 \ \mu A/\mu m$  at  $I_{\rm off} = 1 \ nA/\mu m$  and  $V_{\rm DS} = 0.5 \ V$ . This recessed InP source/drain spacer technique improves device scalability and enables III-V MOSFETs for low standby power logic applications. Furthermore, ultrathin InAs channel MOSFETs were fabricated on Si substrates, exhibiting high yield and high transconductance  $g_{\rm m} \sim 2.0 \ mS/\mu m$  at 20 nm- $L_{\rm g}$  and  $V_{\rm DS}=0.5 \ V$ . imum  $I_{\rm on}/I_{\rm off}$  ratio ~8.3×10<sup>5</sup>, confirming that III-V MOSFETs are scalable to sub-10-nm technology nodes.

## Contents

| Acknowledgements                                                                                  | iv    |

|---------------------------------------------------------------------------------------------------|-------|

| Curriculum Vitæ                                                                                   | vii   |

|                                                                                                   | vii   |

|                                                                                                   | ix    |

| Abstract                                                                                          | xii   |

| List of Tables                                                                                    | xviii |

| List of Figures                                                                                   | xix   |

| 1 Introduction                                                                                    | 1     |

| 1.1 Introduction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 2     |

| 1.2 Why III-V MOSFETs?                                                                            | 5     |

| 1.3 Outline                                                                                       | 8     |

| References                                                                                        | 11    |

| 2 MOSFET Theory and Design                                                                        | 14    |

| 2.1 Ideal MOSFETs theory                                                                          | 15    |

| 2.1.1 Ballistic MOSFET model                                                                      | 15    |

| 2.1.2 Ballistic Si and III-V MOSFETs                                                              |       |

| 2.2 Practical MOSFETs design considerations                                                       | 19    |

| 2.2.1 On-state performance                                                                        | 20    |

| 2.2.2 Electrostatics and subthreshold characteristics                                             |       |

| 2.2.3 Off-state leakage: band-to-band tunneling                                                   |       |

| 2.3 Summary                                                                                       |       |

| References                                                                                        |       |

| 3        | Bar   | rier Engineering: Wide Band-gap AlAsSb Barriers 33                                                 |

|----------|-------|----------------------------------------------------------------------------------------------------|

|          | 3.1   | MBE growth of AlAsSb barriers                                                                      |

|          |       | 3.1.1 AlAsSb lattice-matched to InP                                                                |

|          |       | 3.1.2 N-type doping in AlAsSb layers                                                               |

|          | 3.2   | Electron transport in InGaAs/AlAsSb and InGaAs/InAlAs het-                                         |

|          |       | erostructures                                                                                      |

|          |       | 3.2.1 InGaAs quantum well 2DEG structure                                                           |

|          |       | 3.2.2 Transport scattering model                                                                   |

|          |       | 3.2.3 2DEG results and simulation                                                                  |

|          |       | 3.2.4 As and Sb interface soaking                                                                  |

|          |       | 3.2.5 Mobility enhanced layers                                                                     |

|          | 3.3   | Leakage reduction I: III-V FETs with wide band-gap barriers 50                                     |

|          |       | 3.3.1 InGaAs FETs with AlAsSb barriers                                                             |

|          |       | 3.3.2 InGaAs FETs with P-type doped InAlAs barriers 6                                              |

|          | 3.4   | Summary                                                                                            |

|          | Refe  | erences                                                                                            |

| 4        | Ch    | annel Engineering: Ultra-thin InGaAs and InAs Channels 70                                          |

| -        | 4.1   | MBE growth of composite channel 2DEGs                                                              |

|          | 4.2   | Electron transport in InGaAs and InAs ultra-thin quantum wells . 7                                 |

|          | 4.3   | Leakage reduction II: ultra-thin channels                                                          |

|          | 1.0   | 4.3.1 Channel materials: InAs versus InGaAs                                                        |

|          |       | 4.3.2 Channel thickness scaling                                                                    |

|          |       | 4.3.3 Effective channel mobility of ultra-thin channels 8'                                         |

|          | 4.4   | Record high performance III-V FET: 2.7 nm InAs channel and $ZrO_2$ 9                               |

|          | 4.5   | Summary                                                                                            |

|          |       | erences                                                                                            |

|          | 10010 |                                                                                                    |

| <b>5</b> | Sou   | rce-Drain Engineering: InGaAs and InP Source/Drain Spac-                                           |

|          | ers   | 98                                                                                                 |

|          | 5.1   | MBE and MOCVD source/drain regrowth                                                                |

|          |       | Raised InGaAs and InP source/drain spacers                                                         |

|          | 5.3   | Recessed InP source/drain spacer and InP channel cap 110                                           |

|          | 5.4   | Optimization of InP source/drain spacer                                                            |

|          |       | 5.4.1 InP source/drain spacer thickness                                                            |

|          |       | 5.4.2 Doping-graded InP source/drain spacers                                                       |

|          | 5.5   | Record low leakage III-V MOSFETs 12                                                                |

|          |       | 5.5.1 Minimum $I_{\text{off}} \sim 60 \text{ pA}/\mu\text{m}$ : III-V FETs for low power logic 12. |

|          |       | 5.5.2 Benchmark of $I_{\text{on}}$ - $I_{\text{off}}$ for III-V MOSFETs                            |

|          |       | 5.5.3 Residual leakage: sidewall passivation                                                       |

|   | 5.6 Summary                                                               | 126 |

|---|---------------------------------------------------------------------------|-----|

|   | References                                                                | 129 |

| 6 | 12 nm- $L_{ m g}$ III-V MOSFETs with High $I_{ m on}/I_{ m off}$ Ratio    | 132 |

|   | 6.1 A 12 nm- $L_{\rm g}$ ultra-thin-body III-V MOSFET: device performance | 134 |

|   | 6.1.1 Device fabrication and performance                                  | 134 |

|   | 6.1.2 Comparison with record high performance and low leakage             |     |

|   | III-V FETs                                                                | 137 |

|   | 6.1.3 Effective channel mobility of 2.5 nm composite channels .           | 141 |

|   | 6.2 Summary                                                               | 142 |

|   | References                                                                | 144 |

| 7 | Ultrathin InAs Channel MOSFETs on Si substrates                           | 146 |

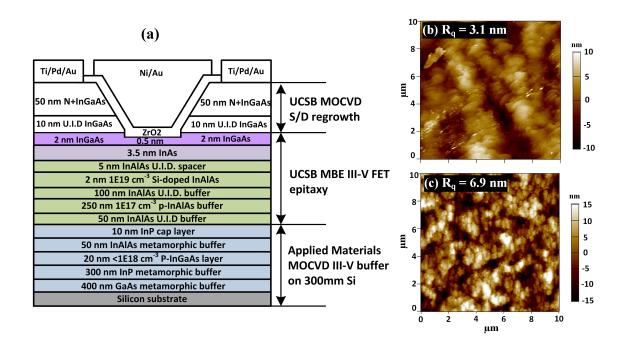

|   | 7.1 Device epitaxial layers growth                                        | 148 |

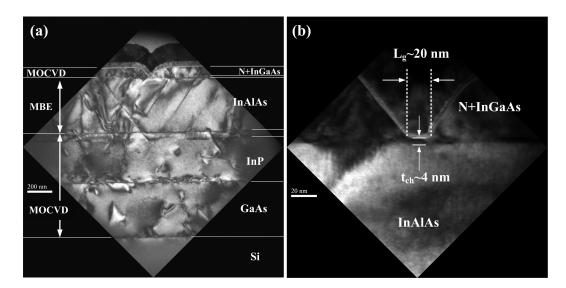

|   | 7.2 Device performance and comparisons                                    | 150 |

|   | 7.3 Summary                                                               | 155 |

|   | References                                                                | 156 |

| 8 | Conclusion                                                                | 158 |

|   | 8.1 Summary                                                               | 159 |

|   | 8.2 Future work                                                           | 162 |

|   | References                                                                | 164 |

| A | MOSFET Process Flow                                                       | 165 |

## List of Tables

| 1.1 | Material properties for Si, Ge and III-V compound semiconductors.                                                                                        | 6   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | The growth conditions and Hall measurements for Si-doped (sample A series) and Te-doped (sample B series) AlAs <sub>0.56</sub> Sb <sub>0.44</sub> layers | 40  |

| 3.2 | Material parameters used in the calculations of the InGaAs/AlAsSb                                                                                        |     |

|     | 2DEG mobility.                                                                                                                                           | 48  |

| 3.3 | InGaAs/AlAsSb 2DEG Hall mobility as a function of column-V ex-                                                                                           |     |

|     | posure during growth interruptions at the InGaAs/AlAsSb interfaces.                                                                                      | 54  |

| 3.4 | Comparison of InGaAs/AlAsSb 2DEG Hall mobility with As in-                                                                                               |     |

|     | terruption and with an insertion of two monolayer InAlAs at the                                                                                          |     |

|     | InGaAs/AlAsSb heterointerfaces.                                                                                                                          | 55  |

| 5.1 | The doping concentration of source/drain layers grown by MBE                                                                                             |     |

|     | and MOCVD. In MBE system, MME represents metal-modulation                                                                                                |     |

|     | epitaxy [11,12]. Si and Te co-doping were used with Si cell at 1395                                                                                      |     |

|     | $^{\circ}\mathrm{C}$ and Te cell at 635 $^{\circ}\mathrm{C}.$ In MOCVD, 400 ppm disilane was used                                                        |     |

|     | with disilane flow $40/45/10$ (out/in/dilution)                                                                                                          | 103 |

|     |                                                                                                                                                          |     |

## List of Figures

| 1.1 | (a) $V_{\rm DD}$ scaling, $V_{\rm th}$ scaling, and the oxide thickness scaling for the previous CMOS generations (Modified figure from [2]). (b) Active |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | power consumption and standby power consumption as a function of gate lengths [3].                                                                       | 3  |

| 1.2 | Comparison of electron injection velocity of III-V HEMT and Si                                                                                           | 0  |

|     | MOSFETs [7]                                                                                                                                              | 6  |

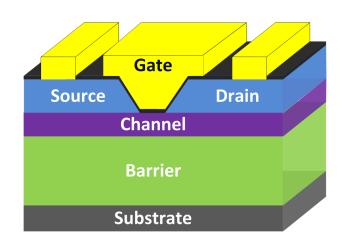

| 1.3 | UCSB ultra-thin channel planar MOSFETs                                                                                                                   | 9  |

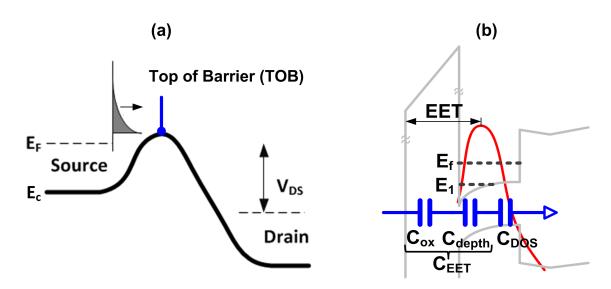

| 2.1 | (a) The band diagram of MOSFETs along the channels, showing                                                                                              |    |

|     | that the position of top-of-barrier determines the amount of cur-                                                                                        |    |

|     | rent flow from the source to the drain. (b) The gate-to-channel                                                                                          |    |

|     | capacitance consists three series capacitances, including oxide ca-                                                                                      |    |

|     | pacitance, wave-function depth capacitance, and density-of-state capacitance (Courtesy of Sanghoon Lee).                                                 | 16 |

| 2.2 | MOSFET normalized drive current for ballistic III-V and Si MOS-                                                                                          | 10 |

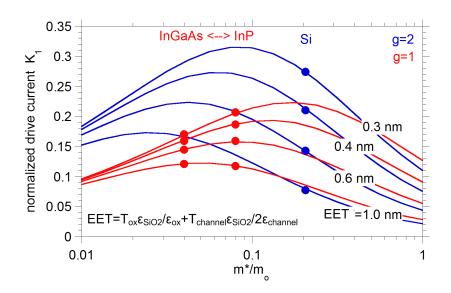

|     | $FETs [4]. \dots \dots$                            | 19 |

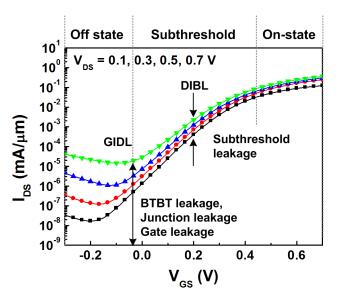

| 2.3 | A typical MOSFET transfer characteristic, showing on-state region,                                                                                       |    |

|     | subthreshold region, and off-state region                                                                                                                | 20 |

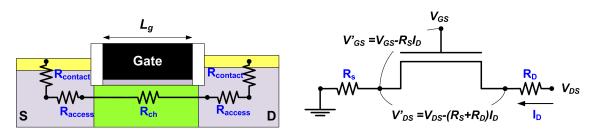

| 2.4 | (a) The series resistance in MOSFETs. (b) The circuit diagram of                                                                                         |    |

|     | MOSFETs with series resistance                                                                                                                           | 21 |

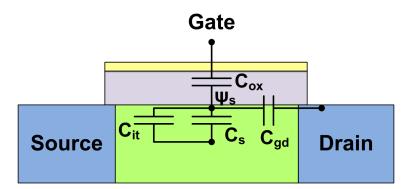

| 2.5 | The equivalent circuit diagram for the capacitances that are con-                                                                                        |    |

|     | nected to the channel surface potential.                                                                                                                 | 24 |

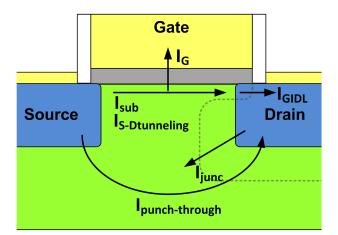

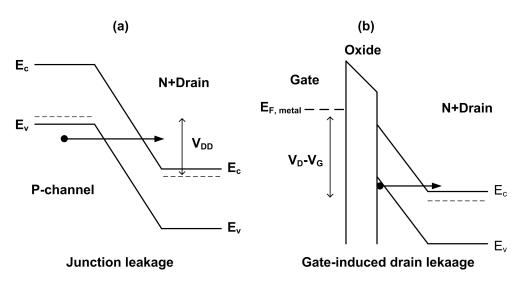

| 2.6 | The possible leakage paths in nanoscale MOSFETs                                                                                                          | 27 |

| 2.7 | (a) The band profile of drain-to-channel junction under reverse bias.                                                                                    |    |

|     | (b) The band profile at the gate-drain overlap region at large neg-                                                                                      | 00 |

|     | ative $V_G$ and positive $V_D$                                                                                                                           | 28 |

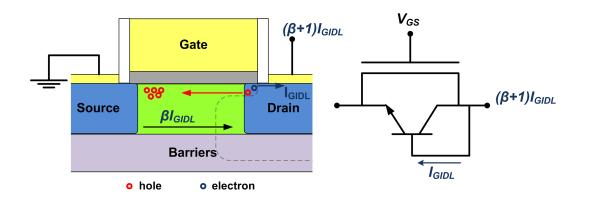

| 2.8  | A lateral bipolar effect in quantum well MOSFETs. The accumu-<br>lation of holes in quantum well channels decreases the channel po-<br>tential, forward-biasing the source-channel barriers and increasing<br>leakage.                                             | 30 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

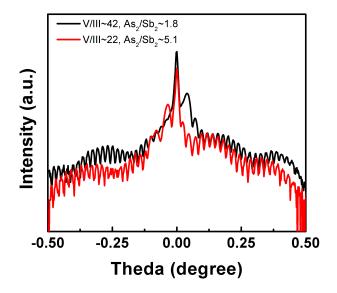

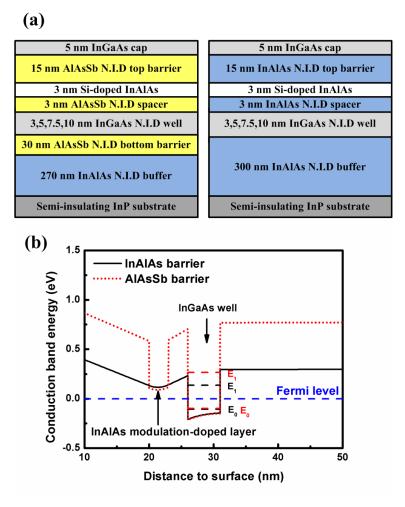

| 3.1  | X-ray diffraction of n-doped $AlAs_{0.56}Sb_{0.44}$ layers grown at different V/III ratio. The beam equivalent pressure ratio of $As_2$ to $Sb_2$ is around 5.1 for the total $(As_2+Sb_2)/Al$ ratio~22 and $As_2/Sb_2\sim1.8$ for total $(As_2+Sb_2)/Al\sim42$ .  | 39 |

| 3.2  | (a) The InGaAs/AlAsSb and InGaAs/InAlAs 2DEG quantum well<br>layer structures using modulation-doped InAlAs layers above the<br>well. (b) Simulated conduction band profile for a 5 nm InGaAs<br>well. The dashed lines indicate the Fermi level and the first two |    |

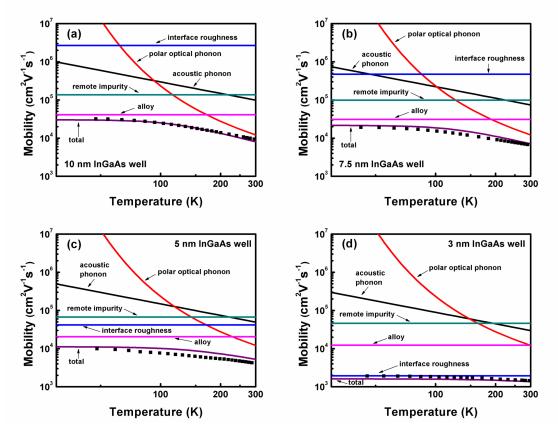

| 3.3  | bound states band minima within the well                                                                                                                                                                                                                           | 43 |

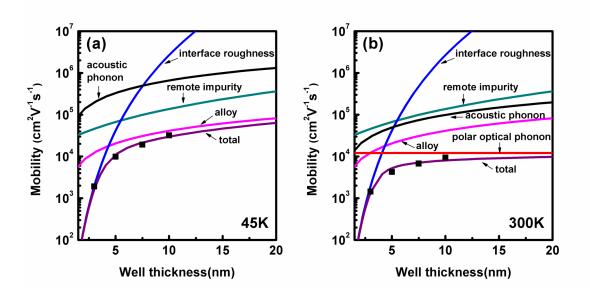

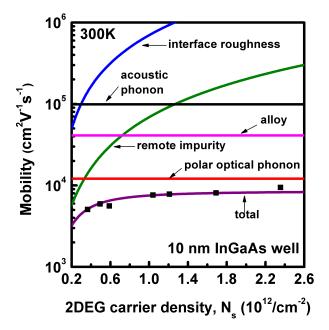

|      | rameters used in the calculations are shown in Table 3.2                                                                                                                                                                                                           | 50 |

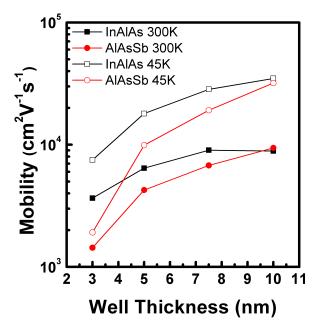

| 3.4  | Measured and calculated (a) low temperature (45 K) and (b) room<br>temperature (300 K) Hall mobilities of InGaAs/AlAsSb 2DEGs as                                                                                                                                   | ۳1 |

| 3.5  | a function of InGaAs quantum well thickness                                                                                                                                                                                                                        | 51 |

| 2.6  | K) mobilities of InGaAs/InAlAs and InGaAs/AlAsSb 2DEGs as<br>a function of the InGaAs well thickness.                                                                                                                                                              | 52 |

| 3.6  | The measured and the calculated room temperature mobilities of InGaAs/AlAsSb 2DEGs as a function of 2DEG carrier concentra-                                                                                                                                        |    |

|      | tion (N <sub>s</sub> ). The modulation-doped impurity concentration was var-<br>ied from $1.0 \times 10^{12}$ to $3.9 \times 10^{12}$ cm <sup>-2</sup> by controlling the Si shutter                                                                               |    |

|      | opening time or the Si cell temperature. The calculation assumes                                                                                                                                                                                                   | 50 |

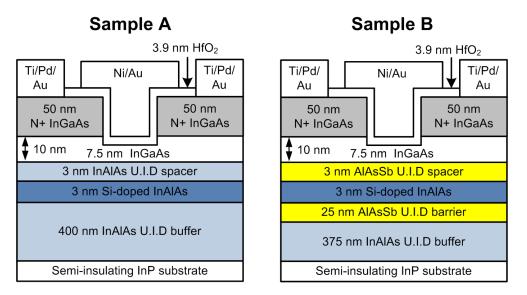

| 3.7  | the modulation-doped impurity concentration, Ni, is $2 \times 10^{12}$ cm <sup>-2</sup> . Device structure of sample A(In <sub>0.52</sub> Al <sub>0.48</sub> As barrier) and sample B                                                                              | 53 |

|      | (AlAs <sub>0.56</sub> Sb <sub>0.44</sub> barrier). The pulse doping layer is 3 nm, $1.3 \times 10^{19}$                                                                                                                                                            |    |

|      | $cm^{-3}$ Si-doped In <sub>0.52</sub> Al <sub>0.48</sub> As. The InGaAs channel thickness is 7.5                                                                                                                                                                   |    |

| 2 0  | nm. (U.I.D. = un-intentionally doped) $\dots \dots \dots \dots \dots \dots$                                                                                                                                                                                        | 57 |

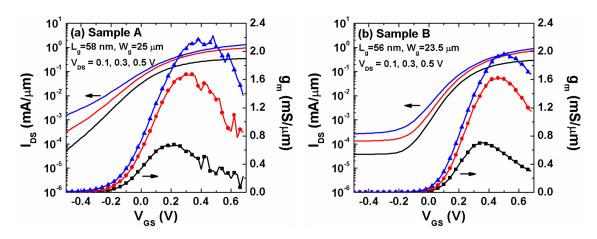

| 3.8  | Transfer characteristics of (a) sample A with $L_g=56$ nm and (b) sample B with $L_g=58$ nm at $V_{c}$ of 0.1, 0.2, and 0.5 V                                                                                                                                      | ۲Q |

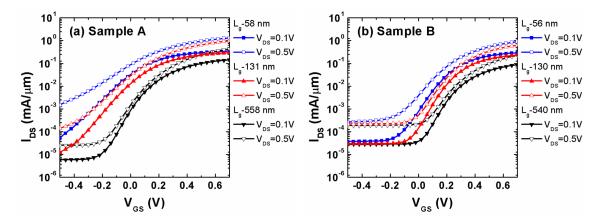

| 3.9  | sample B with $L_g=58$ nm at $V_{DS}$ of 0.1, 0.3, and 0.5 V Subthreshold characteristics (a) of sample A with $L_g=56$ , 131, and                                                                                                                                 | 58 |

| 0.5  | 558 nm and (b) of sample B with $L_g=58$ , 130, and 540 nm                                                                                                                                                                                                         | 59 |

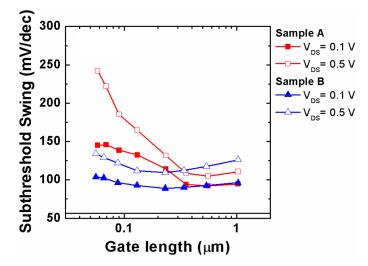

| 3.10 |                                                                                                                                                                                                                                                                    | 00 |

|      | V and $V_{\rm DS} = 0.5$ V                                                                                                                                                                                                                                         | 60 |

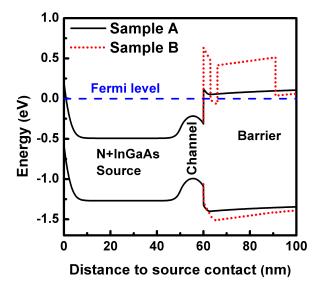

| 3.11 | Energy band diagram of sample A ( $In_{0.52}Al_{0.48}As$ barrier) and sample B ( $AlAs_{0.56}Sb_{0.44}$ barrier) with raised N+ InGaAs source/drain (Si-doped: $4 \times 10^{19}$ cm <sup>-3</sup> ), drawn on a vertical line passing through the N+ source, the InGaAs channel, and the InAlAs or AlAsSb bottom barrier. Given the high source doping, the InAlAs barrier energy lies only ~ 0.1-0.2 eV above the Fermi energy, while the AlAsSb barrier provides ~ 0.6-0.7 eV carrier confinement | 61       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

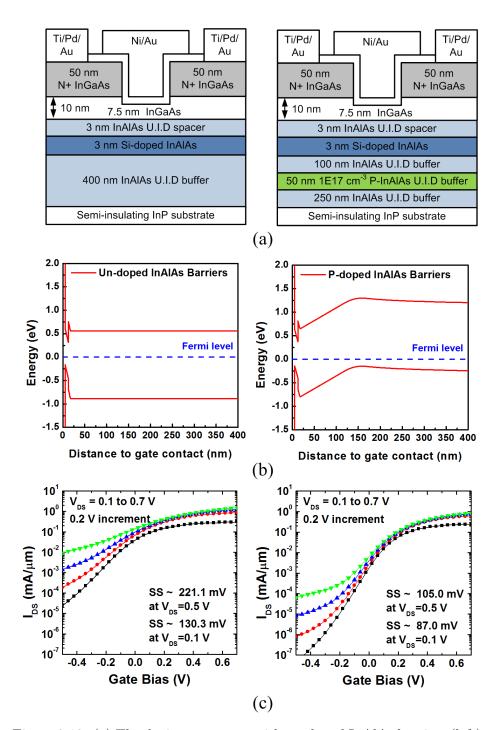

| 3.12 | (a) The device structures with un-doped InAlAs barriers (left) and<br>P-doped InAlAs barriers (right). (b) The corresponding band en-<br>ergy diagrams. (c) The corresponding $I_{\rm DS}$ - $V_{\rm GS}$ curves of 50 nm- $L_{\rm g}$<br>devices.                                                                                                                                                                                                                                                   | 63       |

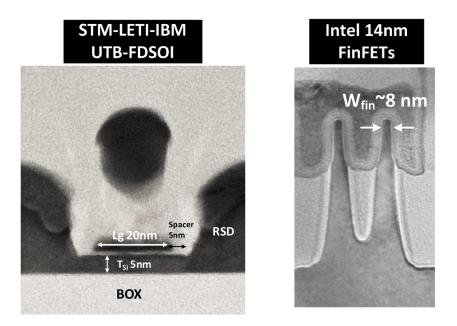

| 4.1  | A TEM image of ultra-thin-body (UTB) fully depleted silicon on<br>insulator (FDSOI), featuring a 5 nm thick Si channel [2]. A TEM                                                                                                                                                                                                                                                                                                                                                                    | 70       |

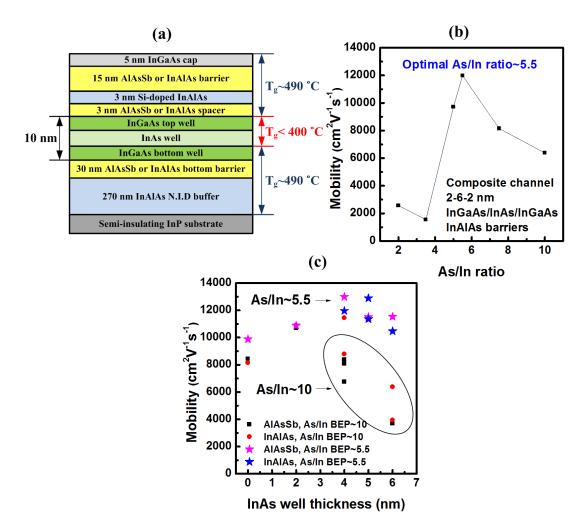

| 4.2  | image of Intel 14 nm FinFETs, featuring a 8 nm narrow fin [3]<br>(a) The composite channel 2DEG structures and the respective growth temperature for each layer. (b)The dependency of 2DEG mobility for 2-6-2 nm InGaAs-InAs-InGaAs composite channels on the As/In BEP ratio during the 6 nm InAs growth. (c) Composite channel 2DEG mobility as a function of the InAs well thickness.(The channels are 10 nm InGaAs, 4-2-4 nm, 3-4-3 nm, 2.5-5-2.5                                                | 72       |

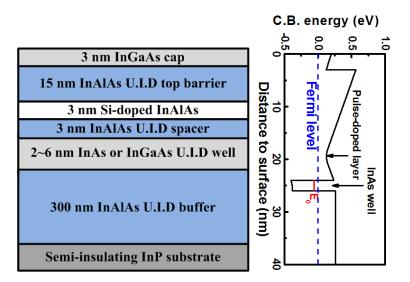

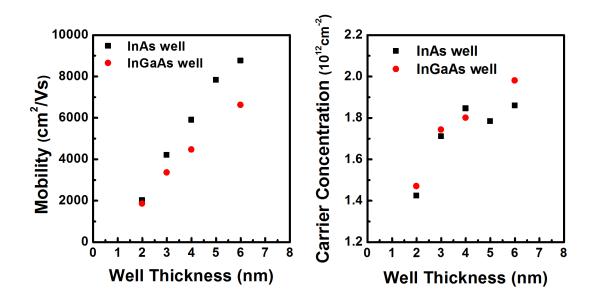

| 4.3  | nm, and 2-6-2 nm InGaAs-InAs-InGaAs composite channels.) Double heterostuctures for the study of electron transport in quantum wells and the associated band diagram calculated by 1-D self-                                                                                                                                                                                                                                                                                                         | 74       |

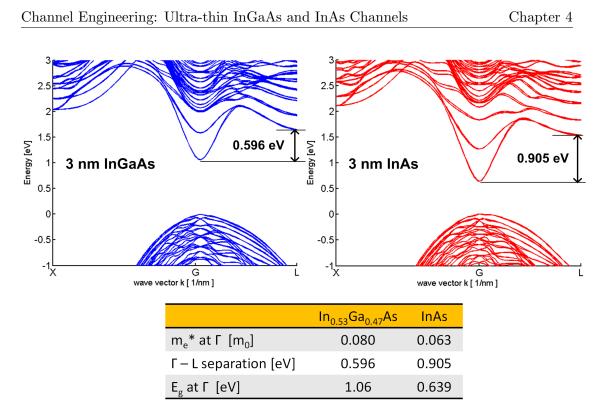

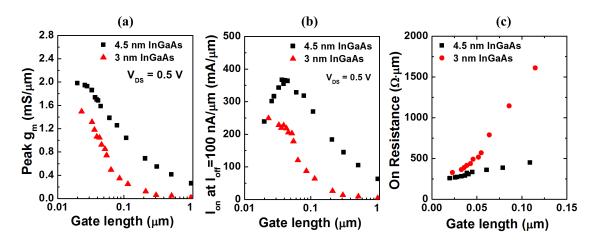

| 4.4  | consistent Schrödinger-Poisson simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 76       |

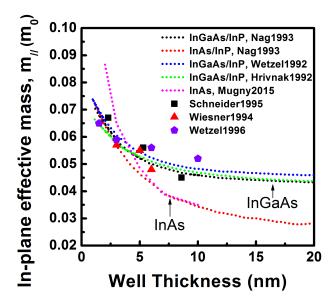

| 4.5  | InAs and InGaAs quantum wells as a function of well thickness<br>Summary of in-plane electron effective mass reported in the liter-<br>ature [7–12].(Dot line: theoretical calculations, solid dot: experi-                                                                                                                                                                                                                                                                                          | 77       |

| 4.6  | mental data from InGaAs channels)                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77       |

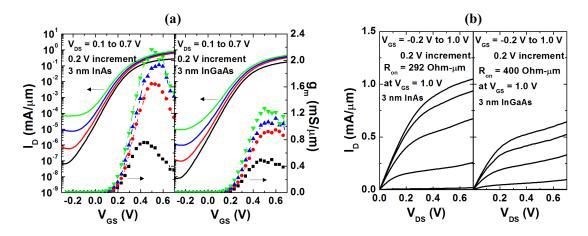

| 4.7  | body MOSFETs with a 3 nm InGaAs or a 3 nm InAs channel (a) The transfer characteristics and (b) the output characteristics                                                                                                                                                                                                                                                                                                                                                                           | 78       |

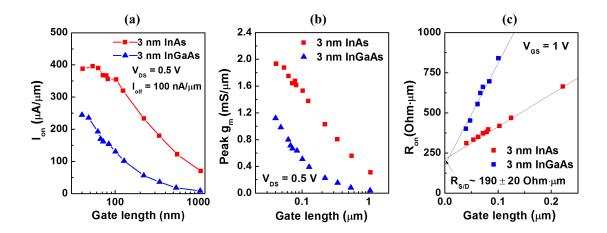

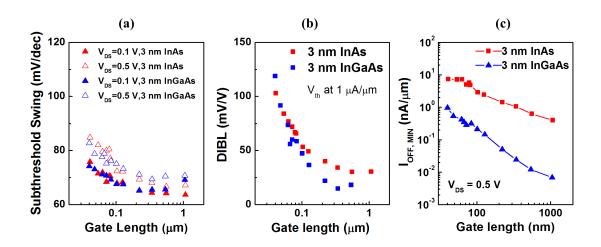

| 4.8  | of $L_{\rm g}$ -40 nm devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 79       |

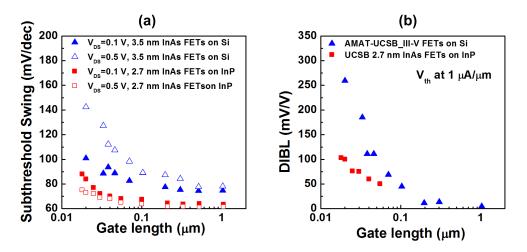

| 4.9  | $L_{\rm g}$ at $V_{DS}=0.5$ V. (c) $R_{\rm on}$ vs. $L_{\rm g}$ at $V_{GS}=1$ V (a) Subthreshold swing vs. $L_{\rm g}$ . (b) $DIBL$ vs. $L_{\rm g}$ . (c) $I_{\rm off,min}$ vs. $L_{\rm g}$ at $V_{DS}=0.5$ V                                                                                                                                                                                                                                                                                        | 80<br>81 |

| 4.10  | Tight binding band structures of 3 nm InGaAs and 3nm InAs wells $$                                                                         |     |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

|       | with a hydrogen-terminated top surface and 2 nm InAlAs bottom                                                                              |     |

|       | barriers. No strain effect on InAs channel is considered in the cal-                                                                       |     |

|       | culations.                                                                                                                                 | 82  |

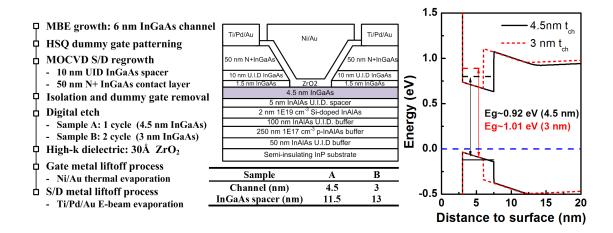

| 4.11  | The process flow, detailed device structure and the corresponding                                                                          |     |

|       | energy band diagrams for 4.5 nm and 3 nm InGaAs channel MOS-                                                                               |     |

|       | FETs.                                                                                                                                      | 84  |

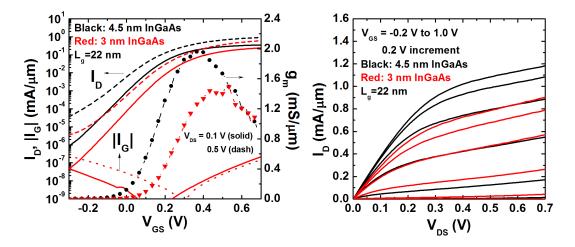

| 4.12  | The transfer and output characteristics for 4.5 nm and 3 nm InGaAs                                                                         | ~ ( |

|       | channel MOSFETs                                                                                                                            | 84  |

| 4.13  | (a) The transconductance, (b) on-state current at 100 nA/ $\mu$ m $I_{\text{off}}$ ,                                                       |     |

|       | and (c) on-resistance as a function of gate length for 4.5 nm InGaAs                                                                       | ~   |

|       | and 3 nm InGaAs MOSFETs.                                                                                                                   | 85  |

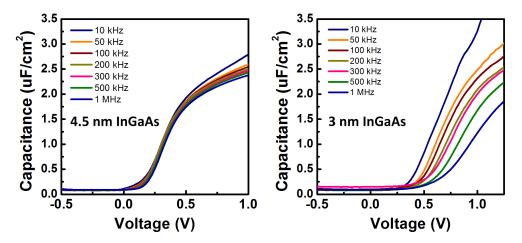

| 4.14  | The capacitance-voltage measurements of $L_{\rm g}$ -25 $\mu$ m MOSFETs for                                                                |     |

|       | $4.5 \text{ nm}$ and $3 \text{ nm}$ InGaAs channels and $\text{ZrO}_2$ gate dielectrics. The                                               |     |

|       | source and drain are grounded and the measured frequency varies                                                                            | 00  |

| 4 1 5 | from 10 kHz to 1 MHz.                                                                                                                      | 86  |

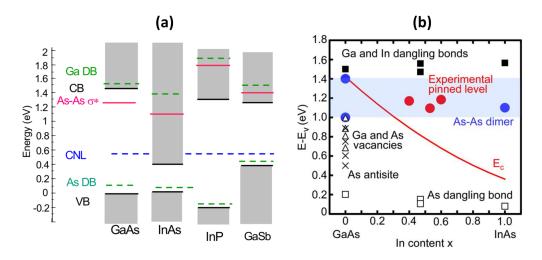

| 4.15  | (a) The interface trap energy calculated by density-functional the-                                                                        |     |

|       | ory by J. Robertson [18]. (Note: CB=conduction band, VB=valence band, CNL=charge neutrality level, DB=dangling bond, and $\sigma^*$ =anti- |     |

|       | bonding) (b) High indium content channels lower minimum con-                                                                               |     |

|       | duction band edge and reduce the interactions between channel                                                                              |     |

|       | electrons and the traps above conduction band [20]                                                                                         | 88  |

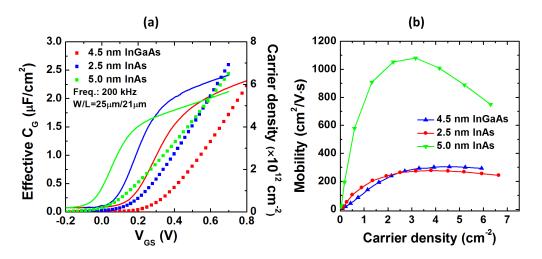

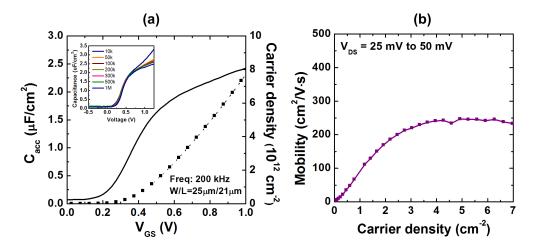

| 1 16  | (a) Comparison of capacitance-voltage measurements for 4.5 nm                                                                              | 00  |

| 4.10  | InGaAs, 2.5 nm InAs, and 5 nm InAs channels. (b) The extracted                                                                             |     |

|       | effective channel mobility using split C-V measurements for differ-                                                                        |     |

|       | ent channel designs.(The results of InAs channels provided from                                                                            |     |

|       | Sanghoon Lee)                                                                                                                              | 89  |

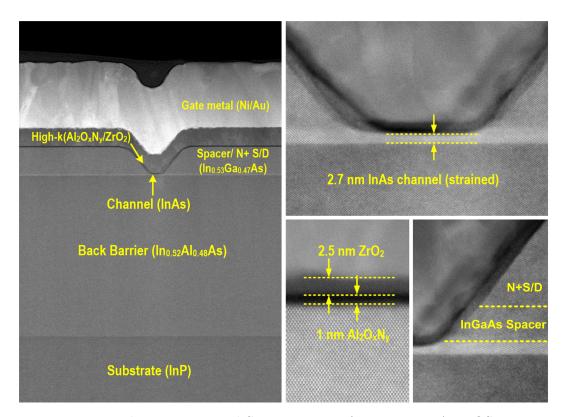

| 4.17  | The cross-sectional STEM images of 25 nm- $L_{\rm g}$ InAs MOSFETs,                                                                        | 00  |

|       | showing $\sim 2.7$ nm InAs channel, $\sim 1$ nm AlO <sub>x</sub> N <sub>1-x</sub> interfacial layer                                        |     |

|       | and $\sim 2.5$ nm ZrO <sub>2</sub> gate dielectric. The source/drain has $\sim 12$ nm                                                      |     |

|       | un-doped InGaAs vertical spacer and the N+InGaAs contact lay-                                                                              |     |

|       | ers.(Courtesy of Sanghoon Lee)                                                                                                             | 92  |

| 4.18  | (a) Device schematics, (b) the transfer characteristic, (c) the sub-                                                                       |     |

|       | threshold characteristic, and (d) the output characteristic of a 25                                                                        |     |

|       | nm- $L_{\rm g}$ InAs MOSFET. (e) Benchmark of $I_{\rm on}$ at fixed $I_{\rm off}=100$                                                      |     |

|       | $nA/\mu m$ to recent published III-V MOSFETs. (f) The subthreshold                                                                         |     |

|       | characteristics of $L_{g}$ -1 $\mu$ m device, showing $SS$ =61 mV/dec.(Courtesy                                                            |     |

|       | of Sanghoon Lee)                                                                                                                           | 93  |

|       |                                                                                                                                            |     |

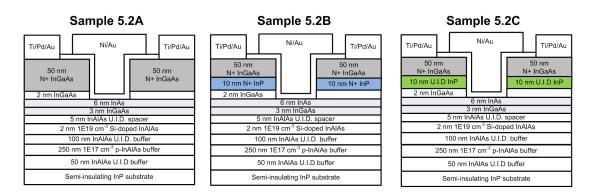

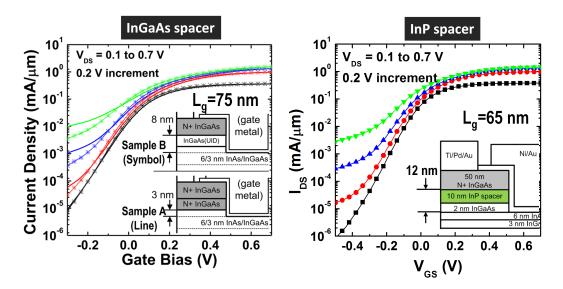

| 5.1  | Device structures of sample 5.2A with N+InGaAs source/drain, sample 5.2B with N+InP source/drain, and sample 5.2C with 10           |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| ۲ Q  | nm undoped InP source/drain spacers. $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ $\dots$                                                | 105 |

| 5.2  | Transfer and output characteristics of $L_g=65$ nm devices for (a) sample 5.2A, (b) sample 5.2B, and (c) sample 5.2C                | 106 |

| 5.3  | Comparison of raised InGaAs spacers and raised InP spacers for                                                                      |     |

|      | FETs with the similar channel design. The result of raised InGaAs spacers were reported by Sanghoon Lee [7]                         | 108 |

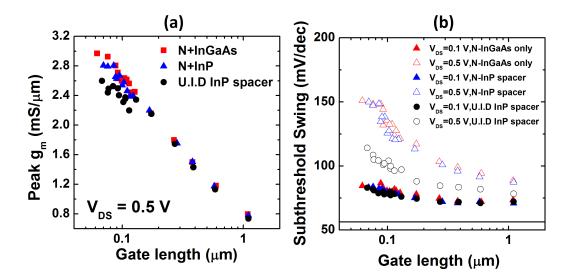

| 5.4  | (a) Comparison of $g_{\rm m}$ versus $L_{\rm g}$ for samples 5.2A, 5.2B, and 5.2C.                                                  |     |

| ББ   | (b) Comparison of $SS$ versus $L_{\rm g}$ for samples 5.2A, 5.2B, and 5.2C.                                                         | 109 |

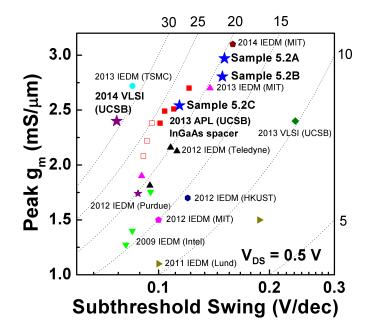

| 5.5  | Benchmark of $g_{\rm m}$ and $SS$ for the three samples in this section to recently reported III-V MOSFETs.                         | 109 |

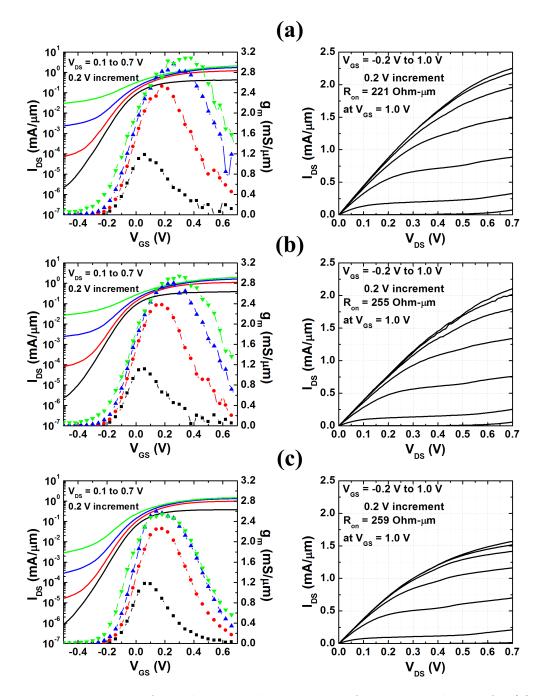

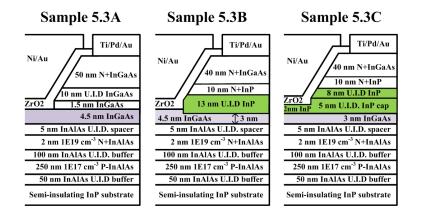

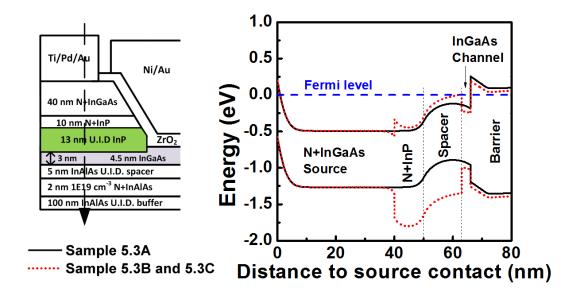

| 5.6  | Devices structures of sample 5.3A (raised InGaAs spacer), 5.3B                                                                      |     |

|      | (recessed InP spacer), and 5.3C (InP cap layer). The devices have                                                                   |     |

|      | symmetric source/drain and only the drain side of the devices is shown here.                                                        | 111 |

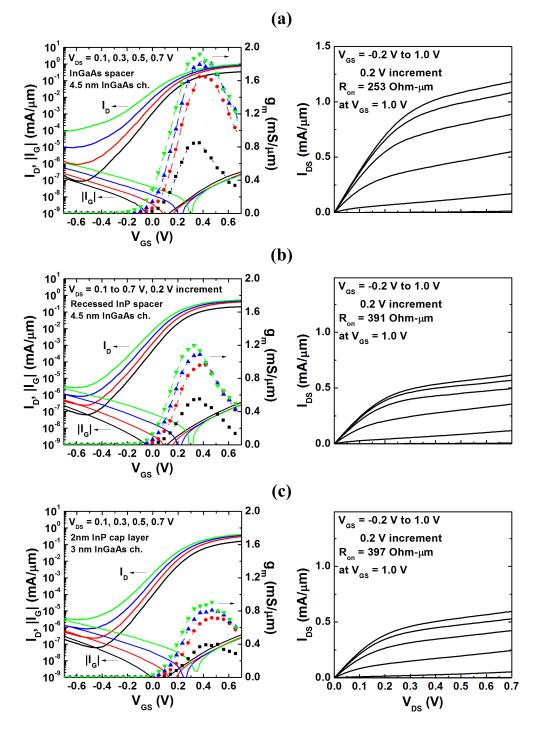

| 5.7  | Transfer and output characteristics for (a) sample 5.3A, (b) sample                                                                 |     |

| 5.8  | 5.3B, and (c) sample 5.3C. $\dots$ and (b) $R$ versus $L$ for sample                                                                | 113 |

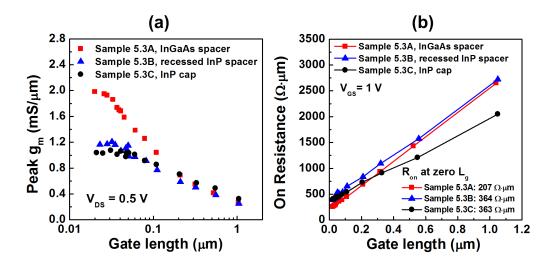

| 5.8  | Comparison of (a) $g_{\rm m}$ versus $L_{\rm g}$ and (b) $R_{\rm on}$ versus $L_{\rm g}$ for sample 5.3A, 5.3B, and 5.3C.           | 114 |

| 5.9  | Energy band diagrams of the three samples, drawn on a path pass-                                                                    |     |

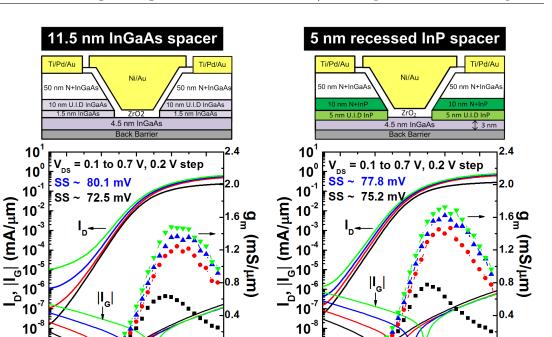

| 5.10 | ing through the N+source and into the channel and the barrier<br>Transfer characteristics of FETs with 11.5 nm InGaAs spacers (sam- | 115 |

| 5.10 | ple 5.3A) and 5 nm recessed InP spacers (sample 5.4A) at 60 nm                                                                      |     |

|      | $L_{\rm g}$                                                                                                                         | 117 |

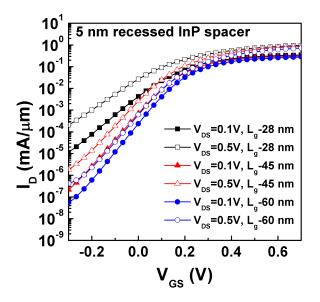

| 5.11 | $I_{\rm D}$ - $V_{\rm GS}$ characteristics vs. $L_{\rm g}$ for InGaAs FETs with 5 nm recessed<br>InP spacers.                       | 118 |

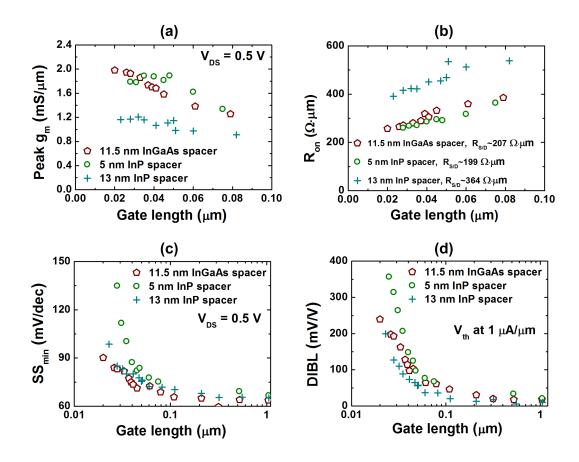

| 5.12 | Comparisons of (a) $g_{\rm m}$ vs. $L_{\rm g}$ , (b) $R_{\rm on}$ vs. $L_{\rm g}$ , (c) $SS$ vs. $L_{\rm g}$ , (d)                  | 110 |

|      | $DIBL$ vs. $L_{\rm g}$ for 4.5 nm InGaAs channel MOSFETs with a 5 nm                                                                |     |

|      | recessed InP spacer (sample 5.4A), a 13 nm recessed InP spacer (sample 5.3B), and a 11.5 nm InGaAs spacer (sample 5.3A).            | 119 |

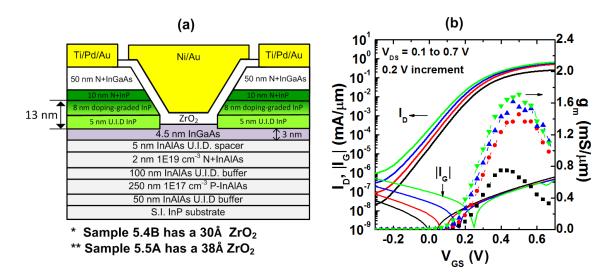

| 5.13 | (a) The device schematic diagram of the InGaAs MOSFET with a                                                                        | 110 |

|      | recessed, doping graded InP spacer. (b) The transfer characteristic                                                                 | 100 |

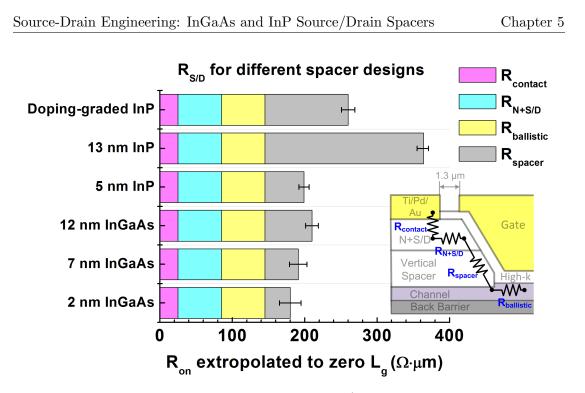

| 5.14 | of sample 5.4B at $L_g$ -30 nm, having a 30 Å ZrO <sub>2</sub> Comparison of the parasitic source/drain resistance with respect to  | 120 |

| 0    | different spacer designs.                                                                                                           | 121 |

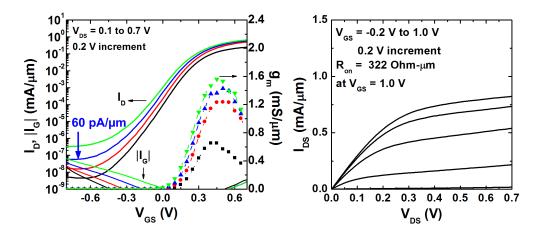

| 5.15 | The transfer and output characteristics of 4.5 nm InGaAs FETs                                                                       |     |

|      | with a 3.8 nm $ZrO_2$ and a recessed, doping graded InP spacers at $L_g$ -30 nm.                                                    | 123 |

|      | 0                                                                                                                                   |     |

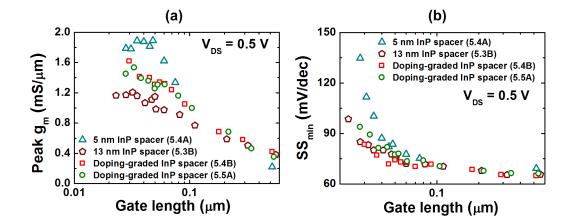

| 5.16 | Comparisons of (a) $g_{\rm m}$ vs. $L_{\rm g}$ and (b) $SS$ vs. $L_{\rm g}$ for a doping-graded InP spacer, a 5 nm undoped InP spacer, and a 13 nm undoped InP                                                                                                                                                                                                                                                                    |            |

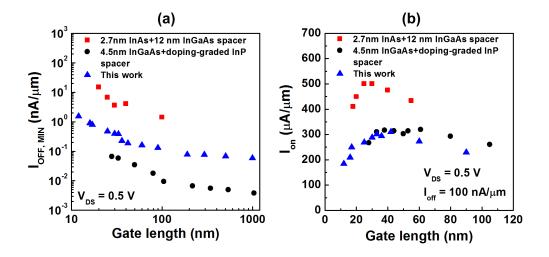

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5.17 | spacer                                                                                                                                                                                                                                                                                                                                                                                                                            | 123        |

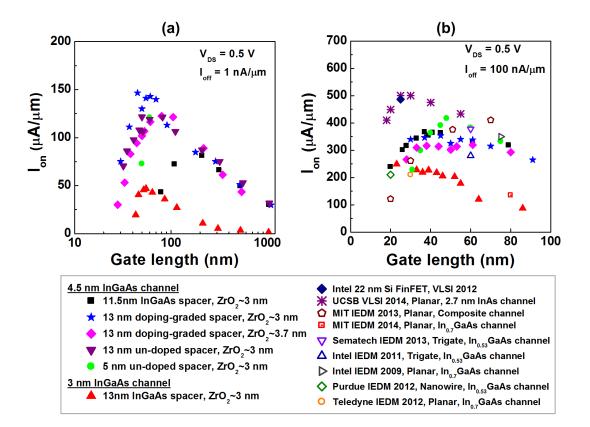

|      | $I_{\text{off}}=100 \text{ nA}/\mu\text{m}$ and $V_{\text{DS}}=0.5 \text{ V}$ and the benchmark with recently published III-V MOSFETs.                                                                                                                                                                                                                                                                                            | 125        |

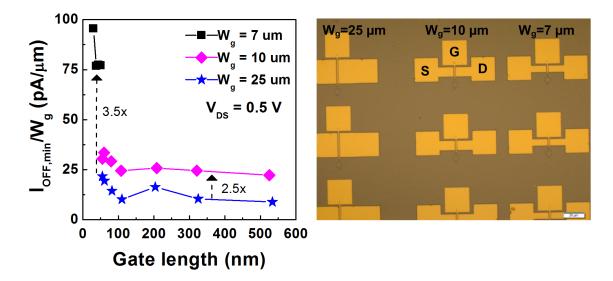

| 5.18 | (a) The dependence of $I_{\text{off}}$ as a function of gate lengths and gate widths. (b) The top view of MOSFET mask layout in this study.                                                                                                                                                                                                                                                                                       | 127        |

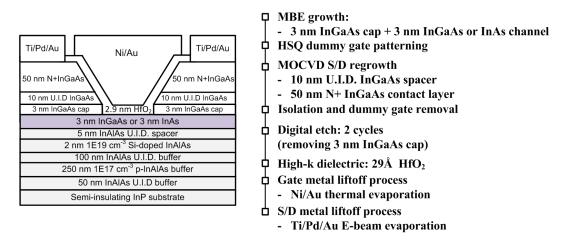

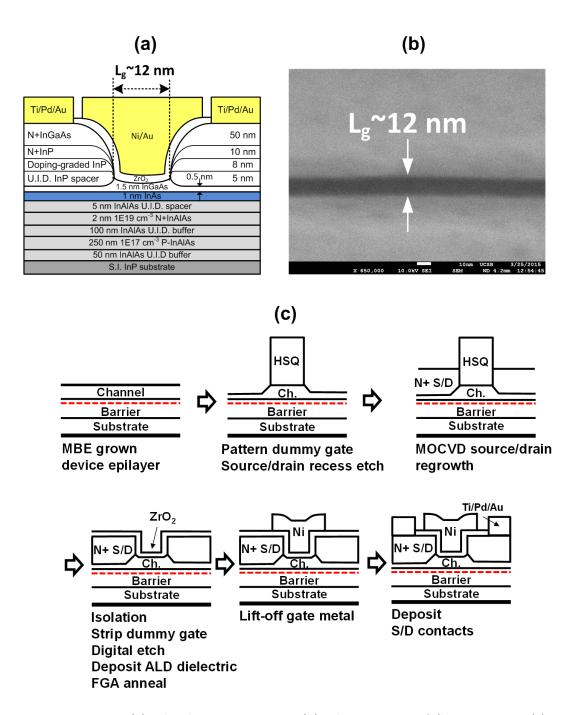

| 6.1  | (a) The device structure. (b) The top-view of SEM images. (c) The schematic diagram of process flow.                                                                                                                                                                                                                                                                                                                              | 135        |

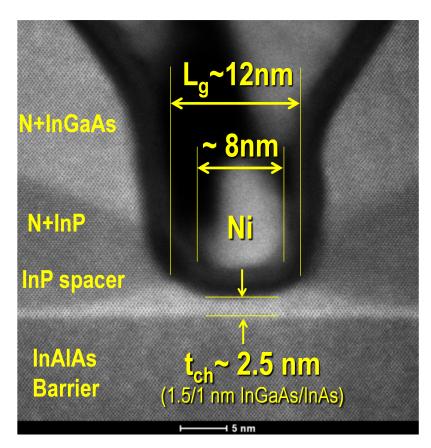

| 6.2  | The scanning TEM image for a $12\text{nm-}L_g$ FET. (Image courtesy of Stephan Kraemer.)                                                                                                                                                                                                                                                                                                                                          | 137        |

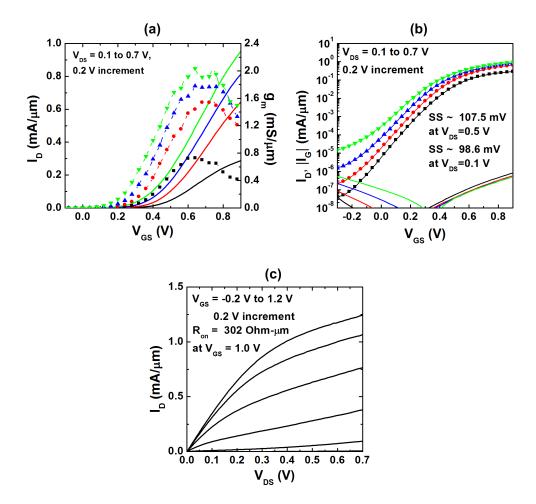

| 6.3  | (a) $I_{\rm D}$ and transconductance $g_{\rm m}$ versus $V_{\rm GS}$ , (b) subthreshold char-<br>acteristics, and (c) output characteristics for a 12 nm- $L_{\rm g}$ FET                                                                                                                                                                                                                                                         | 138        |

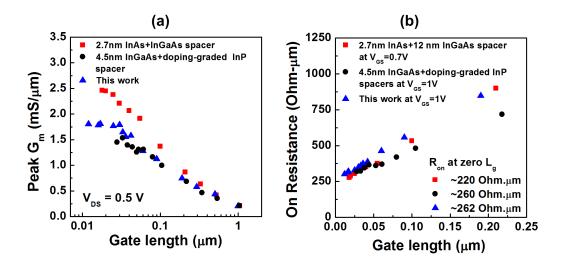

| 6.4  | (a) Comparison of $g_{\rm m}$ and (b) $R_{\rm on}$ as a function of $L_{\rm g}$ for 2.5 nm composite channels MOSFETs to previously reported high performance InAs MOSFETs (chapter 4.4 and [10]) and low leakage In-                                                                                                                                                                                                             |            |

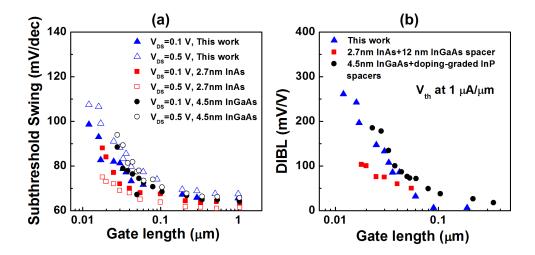

| 6.5  | GaAs MOSFETs with recessed InP spacers (chapter 5.5 and [11])<br>(a) Comparison of $SS$ and (b) $DIBL$ as a function of $L_g$ for 2.5<br>nm composite channels MOSFETs to previously reported high per-<br>formance InAs MOSFETs (chapter 4.4 and [10]) and low leakage                                                                                                                                                           | 139        |

| 6.6  | InGaAs MOSFETs with recessed InP spacers (chapter 5.5 and [11])<br>(a) Comparison of minimum $I_{\text{off}}$ at $V_{\text{DS}}=0.5$ V and (b) $I_{\text{on}}$ at fixed<br>$I_{\text{off}}=100 \text{ nA}/\mu\text{m}$ and $V_{\text{DS}}=0.5$ V as a function of $L_{\text{g}}$ for 2.5 nm com-<br>posite channels MOSFETs to previously reported high performance<br>InAs MOSFETs (chapter 4.4 and [10]) and low leakage InGaAs | 140        |

| 6.7  | MOSFETs with recessed InP spacers (chapter 5.5 and [11]) (a) Capacitance-voltage measurements for 2.5 nm composite channel MOSFETs. The inset shows C-V frequency dispersion. (b) The extracted effective channel mobility using split C-V measurements for 25 $\mu$ m- $L_{\rm g}$ devices                                                                                                                                       | 141<br>142 |

| 7.1  | <ul> <li>(a) Device structure of ultra-thin InAs channel MOSFETs on Si substrates.</li> <li>(b) The AFM image of Applied Materials III-V buffer on Si.</li> <li>(c) The AFM image of the channel surface after MBE III-V FET epitaxy.</li> </ul>                                                                                                                                                                                  | 149        |

|      | <b>1</b> J                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| 7.2 | (a) A TEM image of the whole device structure, showing Applied                                                                        |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Material III-V buffers on Si, UCSB MBE grown back barriers and                                                                        |     |

|     | the InAs/InGaAs channels with ZrO <sub>2</sub> high-k/Ni metal gate, and                                                              |     |

|     | UCSB MOCVD InGaAs source/drain regrowth. (b) The magnified                                                                            |     |

|     | TEM image on the channel regions of a 20 nm- $L_{\rm g}$ device                                                                       | 150 |

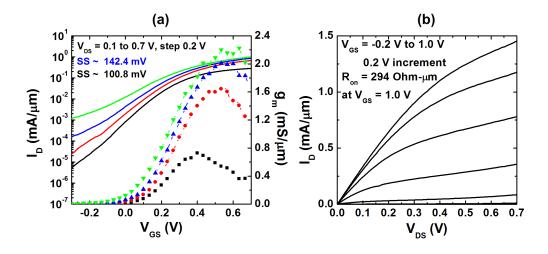

| 7.3 | (a) $I_{\rm D}$ - $V_{\rm GS}$ of a 20 nm- $L_{\rm g}$ device. (b) $I_{\rm D}$ - $V_{\rm DS}$ of a 20 nm- $L_{\rm g}$ device.         | 151 |

| 7.4 | (a) $I_{\rm D}$ - $V_{\rm GS}$ of a 1 $\mu$ m- $L_{\rm g}$ device. (b) $I_{\rm D}$ - $V_{\rm DS}$ of a 1 $\mu$ m- $L_{\rm g}$ device. | 151 |

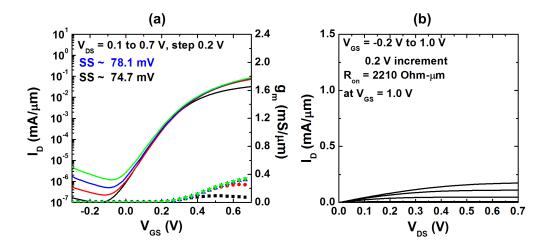

| 7.5 | (a) Comparison of $g_{\rm m}$ and (b) $R_{\rm on}$ as a function of $L_{\rm g}$ for this work                                         |     |

|     | on Si substrates and 2.7 nm InAs MOSFETs on InP                                                                                       | 153 |

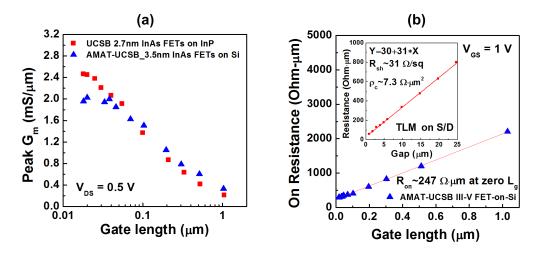

| 7.6 | (a) Comparison of SS and (b) $DIBL$ as a function of $L_{\rm g}$ for this                                                             |     |

|     | work on Si substrates and 2.7 nm InAs MOSFETs on InP. $\ldots$ .                                                                      | 153 |

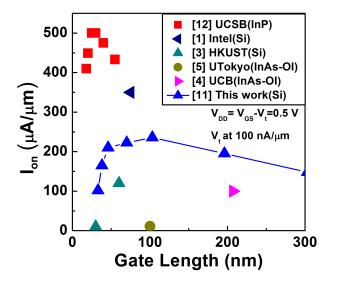

| 7.7 | $I_{\rm on}$ at fixed $I_{\rm off}$ =100 nA/ $\mu$ m for recently reported planar III-V                                               |     |

|     | FETs on Si $[1, 3-5, 11]$ , and compared to results on InP $[12]$                                                                     | 154 |

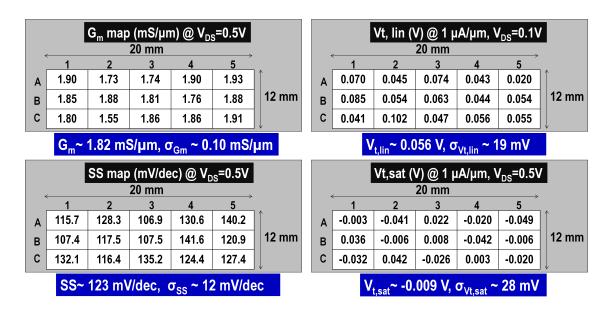

| 7.8 | The maps of $g_{\rm m}$ , $SS$ , $V_{t,lin}$ , $V_{t,sat}$ for 45 nm- $L_{\rm g}$ devices on the 2                                    |     |

|     | $mm \times 1.2 mm$ samples                                                                                                            | 155 |

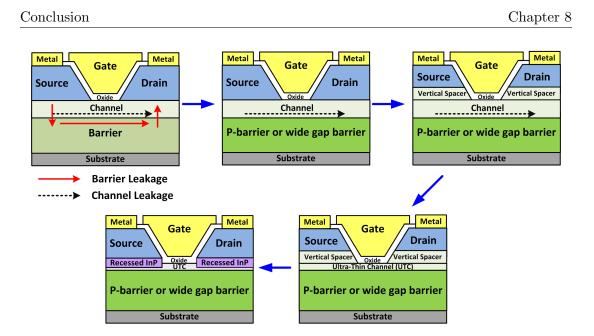

| 8.1 | Progression of III-V MOSFET designs for reduced off-state leakage.                                                                    | 160 |

| A.1 | UCSB Gate Last Process Flow.                                                                                                          | 166 |

Chapter 1 Introduction

### **1.1** Introduction

In 1965, a paper entitled, "Cramming More Components onto Integrated Circuits," published by Gordon Moore predicted that the number of components in integrated circuits will double roughly every two years [1]. This prediction afterwards became widely known as "Moore's law" in technology history, driving the success of computer industries for more than four decades and the fast-growing mobile computing electronics. Miniaturization of metal-oxide-semiconductor field effect transistor (MOSFET) has led to higher transistor density, higher computational capability, and simultaneously lower production cost. However, as Si complementary metal-oxide-semiconductor (CMOS) technology approaches sub-10-nm generations, increasing leakage current (standby power consumption) and increasing switching power (active power) consumption become the fundamental limits for continuous MOSFET scaling and slow down the progress of Moore's law.

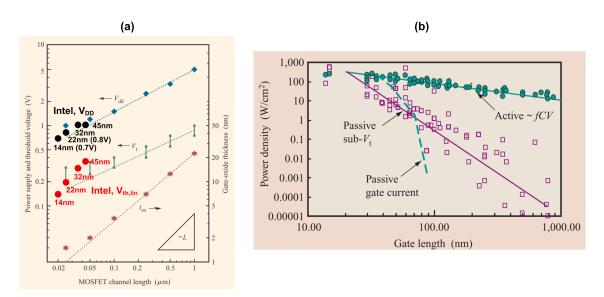

Conventional MOSFET scaling not only involves the reduction of device size but also requires the reduction in the transistor supply voltage  $(V_{\rm DD})$ . The active power consumption decreases proportionately to the square of supply voltage  $(P_{\rm active} \sim f C V_{\rm DD}^2)$ . Fig. 1.1(a) shows the  $V_{\rm DD}$  scaling for the successive CMOS logic generations [2]. To keep constant electric field in the channel and reduce the switching power consumption,  $V_{\rm DD}$  must be reduced, while low  $V_{\rm DD}$  results in low on-state current and increases the switching delay  $(CV_{\rm DD}/I_{\rm on})$ . To attain reasonable on-state current and reduce delay, the threshold voltage  $V_{\rm th}$  must be scaled down simultaneously with  $V_{\rm DD}$  to maintain sufficient gate overdrive voltage  $(V_{\rm GS} - V_{\rm th})$ . However, low  $V_{\rm th}$  causes a dramatic increase on subthreshold leak-

Figure 1.1: (a)  $V_{\text{DD}}$  scaling,  $V_{\text{th}}$  scaling, and the oxide thickness scaling for the previous CMOS generations (Modified figure from [2]). (b) Active power consumption and standby power consumption as a function of gate lengths [3].

age, and increases standby power ( $P_{\text{standby}} \sim I_{\text{leakage}}V_{\text{DD}}$ ). Given that there is a lower limit for  $V_{\text{th}}$  (~0.1 V),  $V_{\text{DD}}$  scaling also slows down around ~0.7-0.8 V to avoid unacceptable performance loss. Therefore, the incapable of continued  $V_{\text{DD}}$ scaling gives rise to high active power consumption and is the main roadblock for continuous CMOS scaling.

The other limitation of MOSFET scaling is excess off-state leakage. High off-state leakage current can arise from large subthreshold leakage due to worse electrostatics, or from the tunneling leakage caused by large electric field in the oxides and the channels. Fig. 1.1(b) shows the active power and standby power consumption as a function of gate lengths [3]. As device scaling continues, the standby power consumption ( $P_{\text{standby}} \sim I_{\text{leakage}}V_{\text{DD}}$ ) increases with the increment of leakage current and might approach the active power consumption if the leakage current can not be properly controlled (e.g. gate leakage in Fig. 1.1(b)). Normally the MOSFET off-state leakage is limited by thermionic current and the minimum off-state leakage can be set by adjusting the threshold voltage. However, with the aggressive gate length scaling and oxide thickness scaling, the other leakage components such as gate leakage, junction leakage, and band-to-band tunneling leakage now become significant as compared to thermionic leakage. Reducing these leakage currents in nanoscale MOSFETs are of the utmost importance for continuous device scaling, in particular for low standby power logic applications and the battery-driven mobile electronics.

A successful extension of Moore's law to next technology nodes requires a solution to alleviate the above-mentioned power constraint and leakage constraint. In the past decade, new materials and new device architecture have been successfully implemented in modern CMOS technology to enable continued MOSFET scaling, for examples, SiGe source/drain stressor at 90 nm node [4], high-k/metal gate process at 45 nm node [5], and tri-gate transistor at 22 nm node [6]. To extend Moore's law to sub-10-nm generations, more innovations are indispensable and will definitely come in the foreseeable future.

Recently, new channel materials such as III-V compound semiconductors and Ge have drawn great attention because of their superior transport properties. III-V InGaAs/InAs materials are considered as promising candidates to replace Si n-channel MOSFETs. InGaAs channels have higher electron mobility and electron velocity than that of Si MOSFETs, which could deliver higher  $I_{on}$  at lower supply voltage. On the counterpart of p-channel, Ge is a very attractive replacement of Si p-channel MOSFETs because Ge has higher hole mobility and hole velocity. By introducing these heterogeneous channels (III-V and Ge) on the existing Si CMOS process platform, higher  $I_{\rm on}$  could be achieved at an aggressively scaled  $V_{\rm DD}$  around ~0.5 V. Therefore, these high mobility channels could alleviate the limitations of  $V_{\rm DD}$  scaling and enable lower active power consumption.

## 1.2 Why III-V MOSFETs?

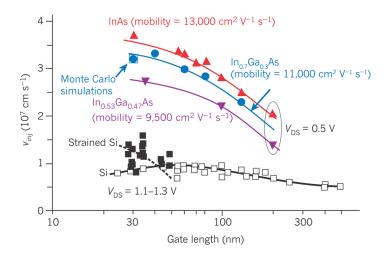

III-V InGaAs/InAs materials have smaller electron effective mass ( $m^* \sim 0.041$ for  $In_{0.53}Ga_{0.47}As$ ) than Si channels ( $m_t^* \sim 0.19$ ). Smaller electron effective mass provides the excellent transport properties, as evidenced by high electron mobility  $(\mu \sim 1/m^*)$  and high injection velocity  $(v_{\rm inj} \sim \sqrt{1/m^*})$ . Table 1.1 compares the material properties of Si, Ge, and III-V materials. Fig. 1.2 shows the injection velocity of III-V channels and Si channels [7]. Even at lower  $V_{\rm DD}$  at 0.5 V, the injection velocity of III-V channels is about  $3 \times 10^7$  (cm/s), at least two times higher than strained-Si channels. Besides the superior transport properties, III-V materials also have relatively mature manufacturing experiences from the radiofrequency (RF), microwave and millimeter wave analog industries. A wide variety of compound semiconductors provides an immense playground (e.g. band-gap, band alignment, effective mass, and strain etc.) to engineer the device structure and improve transistor performance. Because of smaller effective mass and higher tunneling probability, lower contact resistivity (n-type) on III-V materials can also be obtained, which is pivotal for the on-state performance of nanoscale transistors |8|.

Introducing III-V channels for VLSI logic applications has encountered tremendous challenges that still have not been resolved yet [9]. A suitable gate di-

| 300K                                      | Si   | Ge   | GaAs  | InAs  | $\mathrm{In}_{0.53}\mathrm{Ga}_{0.47}\mathrm{As}$ |

|-------------------------------------------|------|------|-------|-------|---------------------------------------------------|

| Electron effective mass, $m_{\rm e}^*$    | 0.19 | 0.08 | 0.063 | 0.023 | 0.041                                             |

| Electron mobility, $\mu_{\rm e}(cm^2/Vs)$ | 1450 | 3900 | 9200  | 33000 | 12000                                             |

| Hole mobility, $\mu_{\rm h}(cm^2/Vs)$     | 370  | 1800 | 400   | 450   | 300                                               |

| Band gap, $E_{\rm g}(eV)$                 | 1.12 | 0.66 | 1.42  | 0.35  | 0.74                                              |

| Relative permittivity, $\epsilon_{\rm r}$ | 11.7 | 16.2 | 12.9  | 15.2  | 13.9                                              |

| Lattice $constant(\mathring{A})$          | 5.43 | 5.66 | 5.65  | 6.06  | 5.87                                              |

| Thermal expansion coefficient             | 2.6  | 5.9  | 5.73  | 4.52  | 5.66                                              |

| $(10^{-6} \circ \mathrm{C}^{-1})$         |      |      |       |       |                                                   |

Table 1.1: Material properties for Si, Ge and III-V compound semiconductors.

Figure 1.2: Comparison of electron injection velocity of III-V HEMT and Si MOSFETs [7].

electric with high permittivity and lower interface trap density is crucial for MOS-FET operations. Unlike Si/SiO<sub>2</sub> interfaces, to achieve high quality gate dielectrics on III-V channels poses the first formidable challenge. The widely-held belief is the exposure of III-V channels to the air must be prevented so that the in-situ oxide deposition immediately after channel growth is necessary [10,11]. Recently, the development of self-cleaning process in atomic layer deposition (ALD) has significantly improved high-k/III-V interfaces [12–14] and allowed a more flexible gate-last integration solution. The other major challenge is a suitable and manufacturable scheme to integrate III-V materials on Si wafers. The very dissimilar material properties between III-V and Si give rise to a high density of defects such as threading dislocations, anti-phase boundaries, and stacking faults/twins. These defects might imperil the device operations, so an effective method to prevent defect formation or to divert defects away from the device active area must be established [9, 15, 16]. On the other hand, for VLSI CMOS, n-/p- channels must coexist on the Si wafers. This greatly increases the process/integration complexity, and the solution must be found and validated.

In terms of device performance, high off-state leakage currents render III-V MOSFETs unsuitable for VLSI logic circuits. Since III-V channels have smaller band-gap, as shown in Table 1.1, large band-to-band tunneling occurs at the regions of crowded electric field, leading to excess off state leakage and limiting the device scalability. Higher relative permittivity of III-V channel also results in worse electrostatics and the increased subthreshold leakage. The band-to-band tunneling leakage and high subthreshold leakage strongly jeopardize the application of III-V MOSFETs at sub-10-nm technology nodes. To meet the requirements for wide-span logic products from high performance (HP) servers to low-power (LP) mobile computing electronics, the leakage current must be sufficiently low ( $I_{off} \sim 100 \text{ nA}/\mu\text{m}$  for HP, and 30 pA/ $\mu\text{m}$  for LP). Therefore, toward the ultimate success, III-V MOSFETs must be demonstrated on Si, with substantial higher performance than Si MOSFETs as well as very low leakage currents for different types of logic products.