## UNIVERSITY OF CALIFORNIA

## Santa Barbara

# Indium Phosphide Heterojunction Bipolar Transistors with Emitter Regrowth by Molecular Beam Epitaxy

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering

by

Dennis W. Scott

Committee in charge:

Professor Mark Rodwell, Chair

Professor Arthur C. Gossard

Professor Evelyn Hu

Professor Umesh Mishra

Professor Chris Palmstrøm

June 2013

| Chris Palmstrøm               |  |

|-------------------------------|--|

|                               |  |

| Umesh Mishra                  |  |

|                               |  |

| Evelyn Hu                     |  |

|                               |  |

| Arthur C. Gossard             |  |

|                               |  |

| Mark Rodwell, Committee Chair |  |

The dissertation of Dennis W. Scott is approved.

June 2013

Indium Phosphide Heterojunction Bipolar Transistors with Emitter Regrowth by Molecular Beam Epitaxy

Copyright © 2013

by

Dennis W. Scott

#### **ACKNOWLEDGEMENTS**

I would like to thank Professor Mark Rodwell. Mark has been a great teacher and an excellent boss. Without the support, encouragement, and opportunities that he provided, I am sure that I would be in a far different place in my career and in life. I am grateful to have Mark Rodwell as my research advisor, and I take great pride in having my name and my work associated with him.

I am also grateful to Professor Art Gossard and John English for allowing the opportunity to work and learn in their MBE labs. My time in the MBE lab provides many fond memories; I learned so many things, and I was exposed to subjects that many electrical engineers might never see. I immensely appreciate the opportunity.

I would also like to acknowledge and thank the fab staff and those who shared the fab while I was at UCSB. I would also like to thank the guys in Mark Rodwell's group who shared the lab and office space during my time at UCSB. I remember my time at UCSB with great fondness, and I realize that it was one of the most creative, insightful, and productive periods in my career. I learned so much, and I had such a great time at UCSB. I attribute my awesome experience to those who helped me along the way and to those who shared in the experience.

Finally, I would like to acknowledge and thank Pei Pei. Although completely outside the technical aspects of my graduate career, she has provided the stability and the strength that benefits me and benefits those around me; even if few were aware of the role that she had served.

## VITA OF DENNIS W. SCOTT June 2013

#### **EDUCATION**

Bachelor of Science in Electrical Engineering, University of Illinois, Urbana-Champaign, May 1996

Master of Science in Electrical Engineering, University of Illinois, Urbana-Champaign, October 1999

Doctor of Philosophy in Electrical Engineering, University of California, Santa Barbara, June 2013

#### PROFESSIONAL EMPLOYMENT

1993-95, 97: Summer Intern, AT&T Microelectronics/Lucent, Orlando, Florida

1996: Summer Intern, Motorola Semiconductor, Phoenix, Arizona

1997-99: Graduate Research Assistant, University of Illinois, Urbana, Illinois

1999: Summer Intern, Intel, Aloha, Oregon

1999-04: Graduate Research Assistant, University of California, Goleta, California

2004-05: II-VI MBE Growth & Analysis, Rockwell Scientific, Camarillo, California

2005-present: III-V HBT & Technology Development, Northrop Grumman, Redondo Beach, California

#### SELECT PUBLICATIONS

D. Scott, H. Xing, S. Krishnan, M. Urteaga, N. Parthasarathy, and M. Rodwell, "InAlAs/InGaAs/InP DHBTs with polycrystalline InAs extrinsic emitter regrowth," IEEE Device Research Conference, Santa Barbara, CA, June 24-26, 2002.

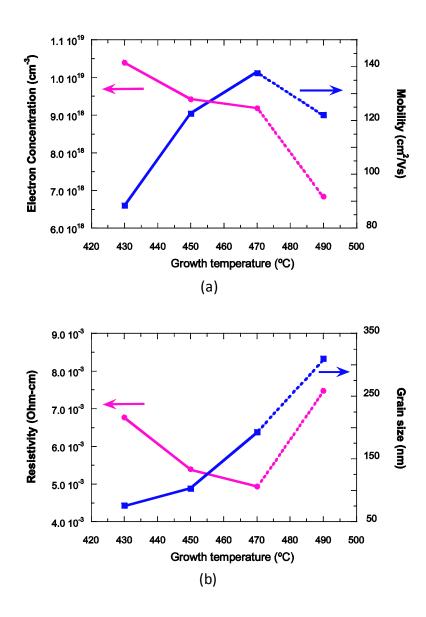

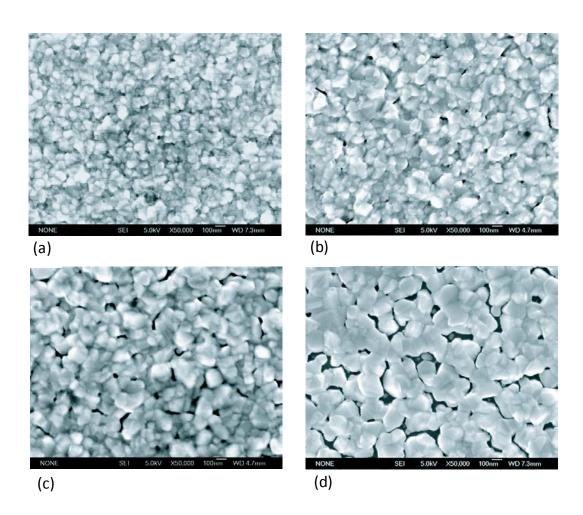

D.W. Scott, C. Kadow, Y. Dong, Y. Wei, A.C. Gossard, and M.J.W. Rodwell "Low-resistance n-type polycrystalline InAs grown by molecular beam epitaxy," *Journal of Crystal Growth*, vol. 267, no. 1-2, June 2004, pp. 35-41.

D. Scott, Y. Wei, M. Urteaga, and M.J.W. Rodwell, "RF performance and process development of InP DHBTs using non-selective emitter regrowth," IEEE International Conference on Indium Phosphide and Related Materials, Kagoshima, Japan, May 31-June 4, 2004.

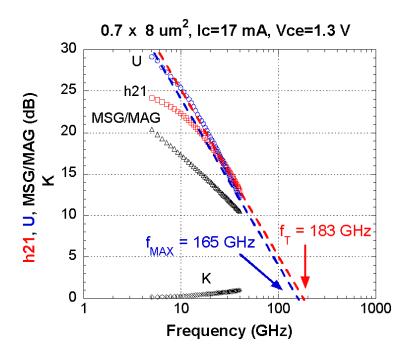

D.W. Scott, Y. Wei, Y. Dong; A.C. Gossard, and M.J.W. Rodwell, "A 183 GHz and 165 GHz regrown-emitter DHBT with abrupt InP emitter," *IEEE Electron Device Letters*, vol. 25, no. 6, June 2004, pp. 360-2.

#### **ABSTRACT**

Indium Phosphide Heterojunction Bipolar Transistors with Emitter Regrowth by Molecular Beam Epitaxy

by

#### Dennis W. Scott

A novel InP-based heterojunction bipolar transistor (HBT) technology using molecular beam epitaxy (MBE) regrowth to form the emitter-base heterojunction and emitter capping layers is presented in this dissertation. The motivation for this work is to combining the positive attributes of the SiGe HBT device structure and fabrication technology with the superior attributes of III-V material systems. The intention of this work is to provide initial investigations into the required material properties as well as initial demonstrations of devices with regrown emitters.

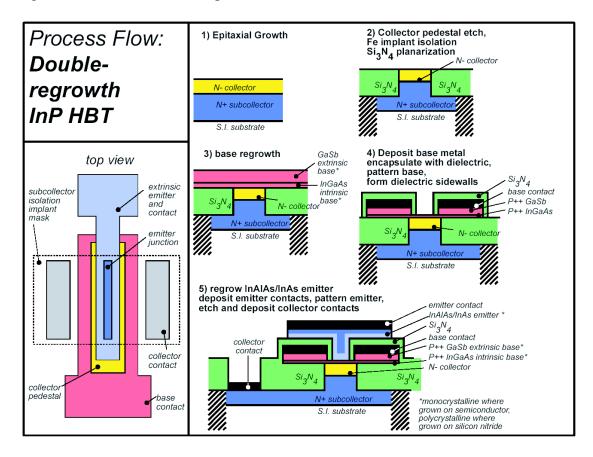

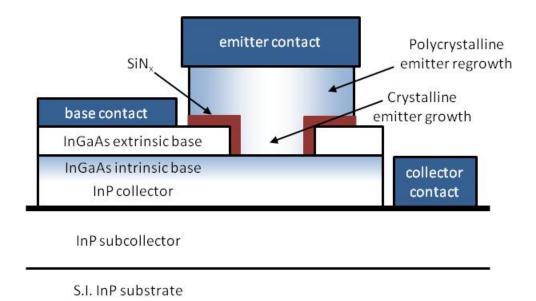

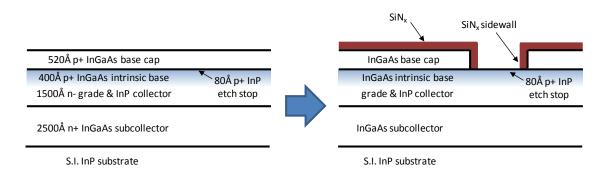

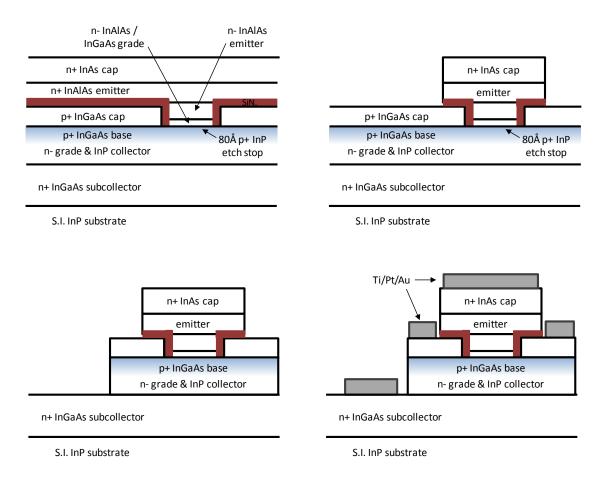

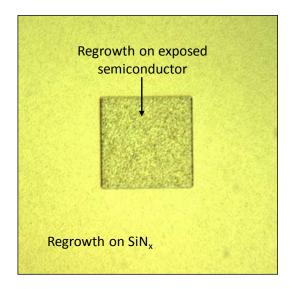

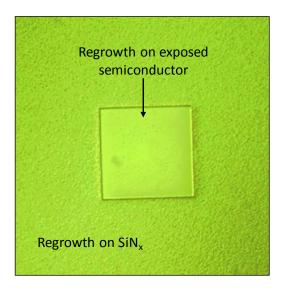

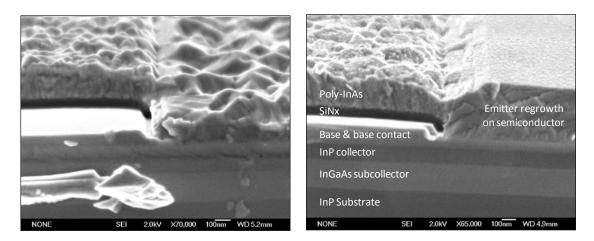

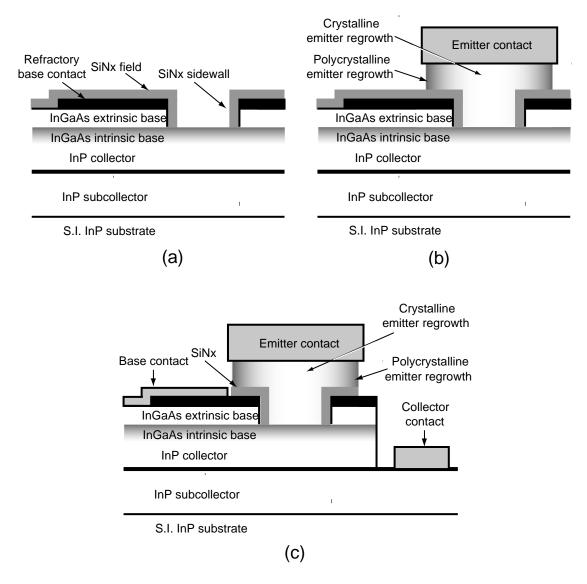

Low-resistance polycrystalline InAs (poly-InAs) deposited onto silicon nitride  $(SiN_x)$  dielectric is demonstrated, and an investigation into material property dependencies on deposition conditions is presented. Low-resistance poly-InAs may be used as an emitter capping material in an InP HBT with regrown emitter where the emitter contact material is wider than the base-emitter junction area. An emitter contact area larger than the emitter junction allows scaling of the device to reduce parasitic capacitances without introducing detrimental parasitics to the emitter contact resistance. Such an HBT could be produced using a patterned base-collector template covered in  $SiN_x$  with openings in the dielectric in areas where emitter junctions are

desired. Areas where the base semiconductor is exposed to emitter regrowth would produce a monocrystalline emitter, and areas where deposition occurs onto  $SiN_x$  would produce polycrystalline material.

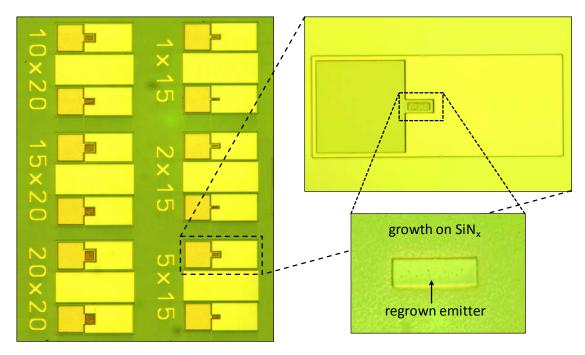

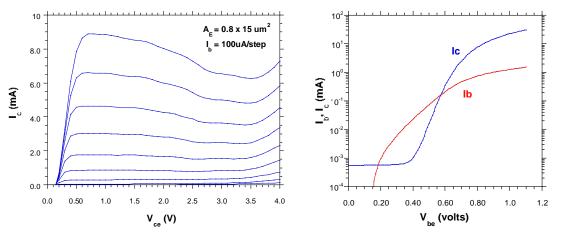

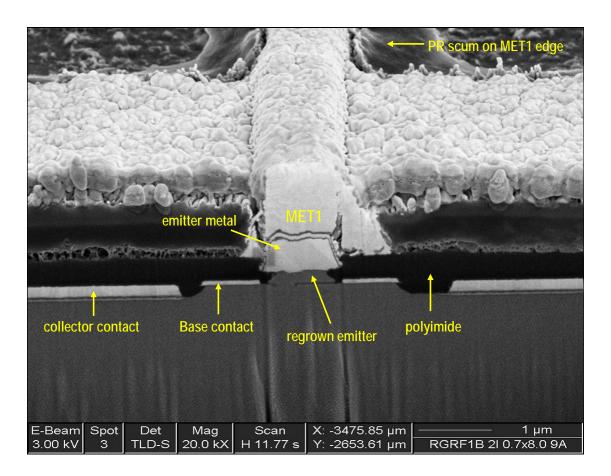

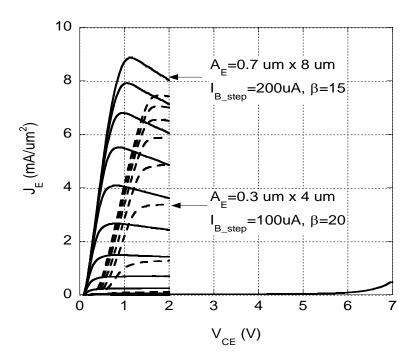

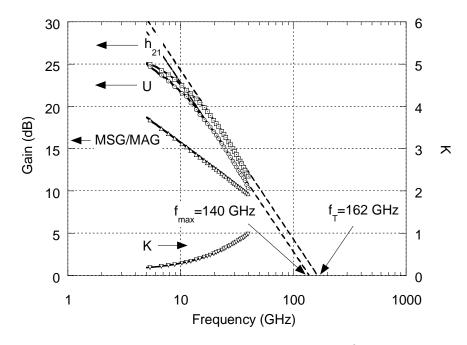

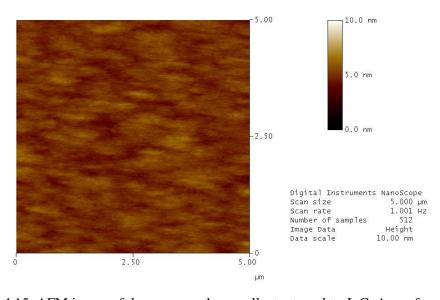

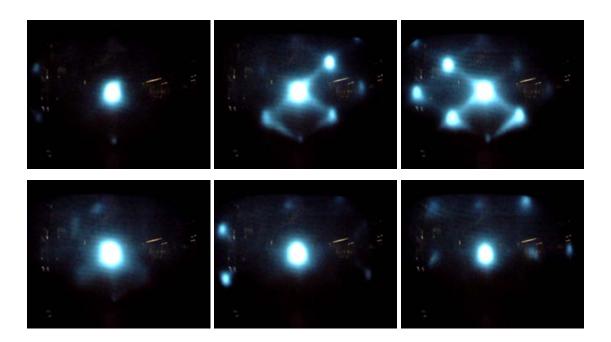

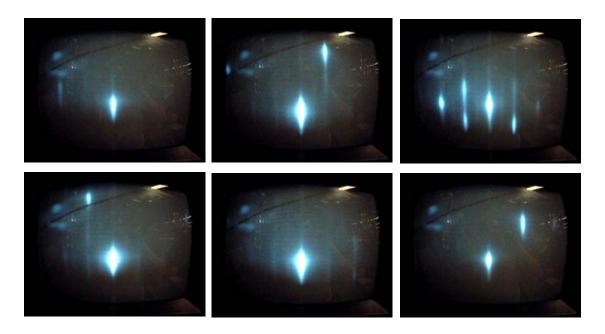

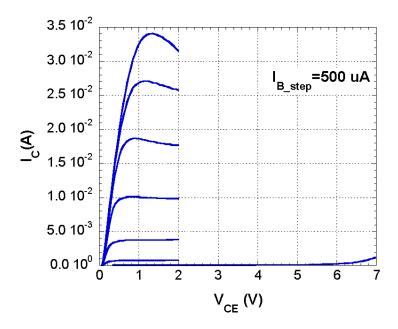

A graded InAlAs emitter with InAs emitter cap was used in the initial demonstrations of the regrown emitter HBT. Large-area devices were used to successfully demonstrate proof-of-concept devices and to make the first-order improvements required for a small-area RF device demonstration. The first small-area regrown emitter InP HBT with emitter contact area wider than the  $0.7 \times 8 \mu m^2$  base-emitter junction demonstrated 160 GHz peak  $f_\tau$  and simultaneous 140 GHz  $f_{max}$ . Further studies into the base-collector template surface preparation process produced an improved regrowth surface with near-epitaxial smoothness. A simplified, abrupt InP emitter regrowth onto this surface produces regrowth similar to what is observed for growth onto epi-ready InP substrates. The improved regrown emitter HBT with  $0.7 \times 8 \mu m^2$  InP emitter area is used to demonstrate a simultaneous 183 GHz  $f_\tau$  and 165 GHz  $f_{max}$ .

## TABLE OF CONTENTS

| CHAPTER 1                                                  |         |

|------------------------------------------------------------|---------|

| INTRODUCTION                                               | 1       |

| 1.1 Brief history of the heterojunction bipolar transi-    | STOR 3  |

| 1.2 SCALING IN III-V HBTs                                  | 5       |

| 1.2.1 Factors determining $f_{\tau}$                       | 8       |

| 1.2.2 Factors determining $f_{max}$                        |         |

| 1.3 HIGHLY SCALED III-V HBTS                               | 17      |

| 1.3.1 Transferred-substrate HBTs                           |         |

| 1.3.2 Trends in highly scaled mesa HBTs                    |         |

| 1.4 HIGHLY SCALED SIGE HBTS                                | 29      |

| CHAPTER 2                                                  | 38      |

| MBE GROWTH OF INP HBTS                                     |         |

| 2.1 Introduction to HBT Growth                             | 38      |

| 2.2 HBT EPITAXIAL STRUCTURE                                |         |

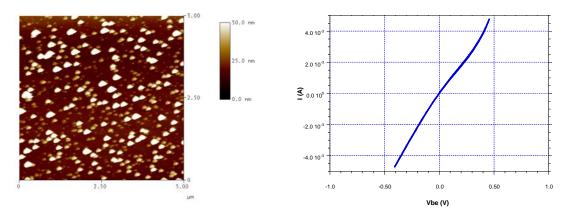

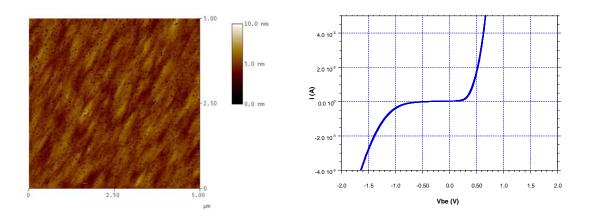

| 2.3 BASE LAYER GROWTH – INGAAS:BE                          |         |

| 2.4 BASE LAYER GROWTH – INGAAS:C                           |         |

| 2.5 GROWTH OF THE COLLECTOR LAYERS                         | 56      |

| 2.6 GROWTH OF THE EMITTER LAYERS                           | 60      |

| CHAPTER 3                                                  | 66      |

| MBE GROWTH OF POLYCRYSTALLINE SEMICONDUC                   | TORS 66 |

| 3.1 MOTIVATION FOR POLYCRYSTALLINE MATERIAL                | 66      |

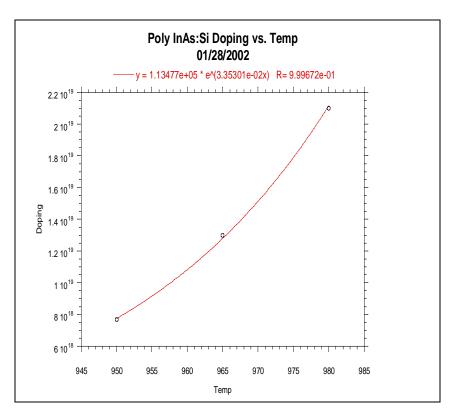

| 3.2 LOW-RESISTANCE POLYCRYSTALLINE INAS                    | 72      |

| 3.2.1 Polycrystalline InAs: Experimental Procedures        |         |

| 3.2.2 Polycrystalline InAs: Results and discussion         | 76      |

| CHAPTER 4                                                  | 86      |

| REGROWN EMITTER HBTS                                       | 86      |

| 4.1 MOTIVATION FOR REGROWN EMITTER HBTs                    | 86      |

| 4.2 INITIAL DEVELOPMENT OF REGROWN EMITTER HBTs            | 87      |

| 4.2.1 Initial DC results                                   | 94      |

| 4.2.2 Initial RF results                                   | 99      |

| 4.3 IMPROVEMENTS TO THE REGROWN EMITTER HBT                | 104     |

| 4.3.1 Improvements to emitter regrowth surface preparation |         |

| 4.3.2 Simplified epitaxial structure for emitter regrowth  |         |

| 433 Regrown emitter HRT RF results after improvements      | 112     |

| CHAPTER 5                                               |     |

|---------------------------------------------------------|-----|

| CONCLUSION                                              | 119 |

| 5.1 ADVANCEMENT IN INP HBTs                             | 119 |

| 5.2 RETROSPECTS AND FUTURE WORK ON REGROWN EMITTER HBTs | 124 |

# Chapter 1

# Introduction

This work presents a summary of a novel InP-based heterojunction bipolar transistor (HBT) technology that employs molecular beam epitaxy (MBE) regrowth to form the emitter-base heterojunction and emitter capping layers. This work is intended as a first step in combining the positive attributes of the SiGe HBT structure and fabrication technology with the positive attributes of III-V material systems. A simple understanding of the recent trends in III-V and SiGe-based HBT technology is helpful to understand the factors that motivate this work. A brief review of HBT technology, device parameters, and current trends in HBT performance will be presented in this chapter.

Research in wide bandwidth HBTs is driven by applications in radar, high-speed communication such as microwave and millimeter-wave wireless, and large capacity optical fiber communications systems. Wireless receivers and transmitters require low-noise RF preamplifiers, multiple stages of amplification, and frequency conversion, which are typically implemented as small-scale monolithic millimeter integrated circuits (MMICs). Although the operating frequency of these circuits is set by the application, advancements in transistor performance allows for the evolution of

the applications to progressively higher frequencies. III-V HBT technology offers advantages in higher transconductance, better threshold voltage control, higher output resistance, and higher current driving capability than its III-V counterparts in metal semiconductor field effect transistors (MESFETs) and high electron mobility transistors (HEMTs) which currently dominate the MMIC applications.

InP-based HEMTs are prevalent in MMIC applications because the technology has established a lead in high frequency performance. InGaAs/InAlAs HEMTs with 45 nm gate lengths were reported with maximum current gain cutoff frequencies ( $f\tau$ ) over 400 GHz as early as 2001.<sup>[1]</sup> Separately, transistors with 100 nm gate lengths and maximum oscillation frequencies ( $f_{max}$ ) of 600 GHz were reported in 1995.<sup>[2]</sup> These performance demonstrations were achieved through the use of aggressive lithographic scaling in the III-V material system. In contrast, aggressive lithographic scaling of III-V HBTs has not been prevalent. Commercial InP and GaAs-based HBTs are typically fabricated with emitter widths of 1 to 2  $\mu$ m and collector junction widths of 3 to 5  $\mu$ m.

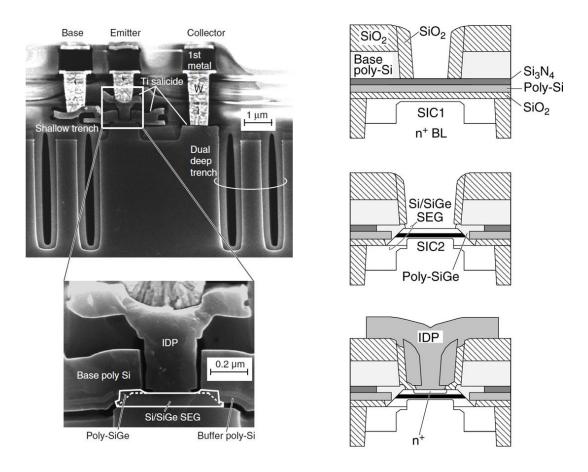

By comparison, state-of-the-art SiGe-based HBTs are fabricated with  $< 0.2 \, \mu m$  emitter-base junction widths, and have obtained simultaneous  $f_{\tau}$  and  $f_{max}$  results of 270 and 260 GHz and a record  $f_{\tau}$  of 350 GHz.<sup>[3]</sup> SiGe-based HBTs employ superior fabrication techniques to obtain deep submicron features in a planar, Si-compatible fabrication process. The silicon fabrication technology and the silicon bipolar device structure allows for extreme levels of parasitic reduction in SiGe HBTs relative to III-V HBTs. These features allow SiGe to remain competitive in the high-speed digital and mixed-signal applications. III-V HBTs maintain a superior bandwidth advantage

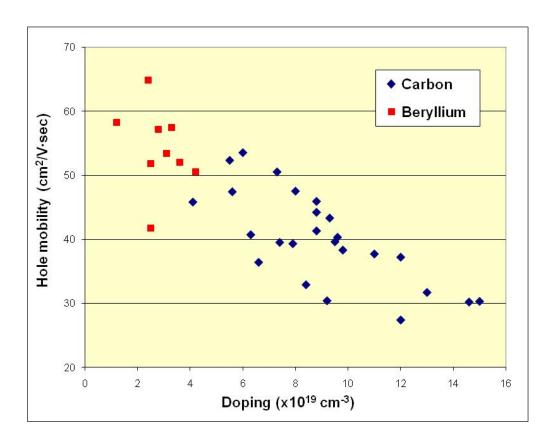

despite larger device parasitics, a relatively immature fabrication technology, and consequently, higher costs and lower scales of integration. The lead in device bandwidth is maintained by the intrinsic properties of the III-V material system. GaAs and InP lattice-matched materials allow for bandgap energy variations so the emitter bandgap may be much larger than that of the base material. This allows the base region to be very heavily doped,  $\sim 10^{20}$  cm<sup>-3</sup>, to reduce base sheet resistance while minority carrier injection into the emitter region remains low. In contrast, the lattice mismatch constraints in Si/SiGe HBTs limit the allowable Ge to Si alloy ratio and a weaker heterojunction is formed. The emitter-base bandgap energy difference is much less than that in III-V materials and lower base doping must be used. Higher electron velocities are also a significant advantage in III-V materials. In InAlAs/InGaAs HBTs with 0.2 to 0.3  $\mu$ m collector thickness, the effective electron velocity is approximately four times higher than that observed in Si. The higher electron velocity results in higher current-gain cutoff frequencies.

## 1.1 Brief history of the heterojunction bipolar transistor

W. H. Brattain and J. Bardeen demonstrated power amplification in a three-terminal point-contact semiconductor device on December 16, 1947 at Bell Telephone Laboratories.<sup>[4,5]</sup> Shortly afterwards, group leader W. B. Shockley presented the theory of p-n junctions and of bipolar junction transistors.<sup>[6]</sup> In June 1948, Shockley filed a U.S. patent describing the idea of a wide bandgap semiconductive emitter material to achieve a bipolar transistor with high carrier injection efficiency into a

narrower bandgap base.<sup>[7]</sup> Independently, Kroemer theoretically described the same principle in a 1957 paper published in *Proceedings of the IRE*.<sup>[8]</sup>

It was at about this time that the first experimental demonstrations of heterojunctions began to appear. Jenny of RCA Laboratories attempted to form a GaAsP/GaAs heterojunction by diffusing phosphorous into GaAs<sup>[9]</sup>, but the technique was never successful because the diffused junctions were not very abrupt. This work emphasized the need to create abrupt junctions by epitaxial growth. Researchers at IBM were the first to report grown heterojunctions of Ge on GaAs in 1958.<sup>[10]</sup> The experimental behavior of the Ge/GaAs junction was verified by the theory of heterojunction operation developed by Anderson in 1962<sup>[11]</sup>, and the success of this initial work motivated continued efforts on the growth of heterojunctions.

It was not until 1969 that Jadus and Feucht demonstrated the first functional HBT with a heterojunction formed by growing Ge on GaAs. This transistor structure achieved a common-emitter current gain of ~10 with a base doping level four orders of magnitude higher than that of the emitter. This confirmed the theoretical proposals set forth by Shockley and Kroemer years earlier. It was generally realized, though, that defect currents caused by poor interfacial properties limited the gain of these devices. Further research, therefore, began to focus on the employment of new material systems and epitaxial growth methods to realize heterojunction interfaces with relatively low defect levels.

By the early 1970s it was shown that the AlGaAs/GaAs material system could be used to produce a heterointerface with low defect density. This low defect density

is attributed to the small lattice mismatch over the full range of the Al<sub>x</sub>Ga<sub>1-x</sub>As alloy composition. Dumke, Woodall, and Rideout at IBM grew the first AlGaAs/GaAs HBT in 1972 using liquid phase epitaxy (LPE). Work on the HBT continued throughout the 1970s and 1980s with emphasis still being placed on the development of growth techniques and material systems. The emergence of MBE and metalorganic chemical vapor deposition (MOCVD) as viable methods for growing high-quality epitaxial structures helped to accelerate HBT research and lead to high-performance HBTs.

## 1.2 Scaling in III-V HBTs

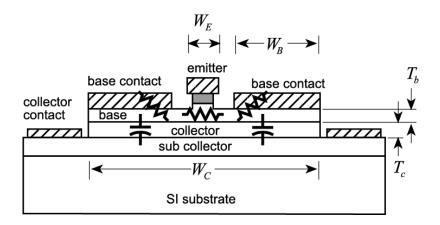

Despite the evolution of III-V material epitaxy, less attention has been focused on improving the device structure until the last decade. For instance, in 1995 the fastest InP-based HBTs<sup>[14]</sup> were still formed using a triple-mesa structure as shown in Figure 1.1. Moderate scaling of the epitaxy (vertical scaling) and device dimensions (lateral scaling) allowed for progress up to this point, but the triple-mesa device structure eventually impeded further progress. Improvements to the device by scaling suggest that the reduction in device dimensions, either lateral or vertical, will result in an improved frequency response. Transistor bandwidths are generally determined by carrier transit times and RC charging time constants. HBT transit times are reduced by decreasing the thickness of the base and collector epitaxial layers. Reducing the epitaxial thicknesses, however, will lead to an increase in base resistance and collector capacitance unless accompanied by lateral scaling of the base and collector junction

widths. This example suggests that the full benefits of scaling III-V HBTs are only realized if all transistor parasitics are simultaneously reduced.

Figure 1.1 Cross-section of a mesa HBT. The emitter-base junction has width  $W_e$ , length  $L_e$ , and area  $A_e = L_e W_e$ . The collector-base junction has width  $W_c$ , length  $L_c$ , and area  $A_c = L_c W_c$ .

The simplified cross-section of a mesa HBT shown in Figure 1.1 illustrates the difficulty in scaling the transistor's collector-base junction. The patterned etches and metal depositions that form the HBT junctions result in a device structure where the collector-base junction must lie beneath the full area of the base ohmic contacts. To obtain low base contact resistance, the base ohmic contact must be at least one contact transfer length,  $L_{contact}$ , wide at the sides of the emitter stripe. For an HBT with a 400 Å thick InGaAs base and  $5 \times 10^{19}$  cm<sup>-3</sup> doping,  $L_{contact} \cong 0.4$  µm. Process tolerances for lithographic alignment may further limit the minimum collector-base junction dimensions.

In literature, transistor bandwidth is often described by the figures-of-merit current gain cutoff frequency  $f_{\tau}$  and the power gain cutoff frequency  $f_{max}$ . The current

gain cutoff frequency is the maximum frequency at which the magnitude of AC current gain ( $h_{21}$ ) decreases to unity. Beyond  $f_{\tau}$  the device will have current gain less than unity. The maximum oscillation frequency  $f_{max}$  is the frequency at which the unilateral power gain of the transistor tends to unity. The unilateral power gain effectively represents the maximum power gain that is achievable by the transistor, and transistors cannot provide power gain at frequencies above  $f_{max}$ . In more general analog and digital circuits, these figures-of-merit may not accurately predict the circuit performance. For instance,  $f_{\tau}$  is commonly used to evaluate a transistor's potential in digital logic applications. However, a detailed charge analysis of switching times reveals that device current density, collector-base junction capacitance, and emitter resistance make much larger fractional contributions to logic gate delay than they contribute to the emitter-collector forward delay  $\tau_{ec}=1/2\pi f_{\tau}$ . In analog and digital circuits,  $f_{\tau}$  and  $f_{max}$  are used to provide a first order estimate of device transit delays and of the magnitude of the dominant transistor parasitics.

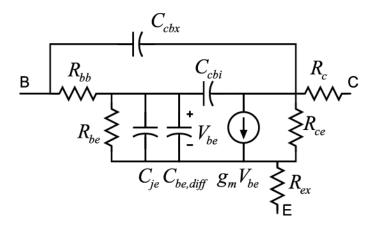

The cutoff frequencies can be estimated from HBT parameters calculated from the physical device properties and fit to a lumped-element device model. Experience shows that the simple hybrid- $\pi$  small-circuit equivalent model shown in Figure 1.2 is sufficient to describe all but the most highly scaled devices up to a frequency of 110 GHz. Although some concerns exist regarding the accuracy of the model at higher frequencies and in describing highly scaled devices<sup>[16]</sup>, this first-order model is excellent for determining the terms that limit transistor bandwidth.

Figure 1.2 Hybrid- $\pi$  small-signal HBT equivalent circuit.  $C_{cbe,diff} = g_m(\tau_b + \tau_c)$ .

The scaling analysis that follows has been presented elsewhere in greater detail. It is repeated here for completeness as the benefits of device scaling motivate the approach of using the regrown emitter structure presented in this thesis.

## 1.2.1 Factors determining $f_{\tau}$

This approach to HBT scaling is derived from the parameters that limit device bandwidth. The current-gain cutoff frequency is given by a sum of transit times and charging delays:

$$\frac{1}{2\pi f_{\tau}} = \tau_b + \tau_c + \frac{kT}{qI_c} (C_{je} + C_{cb}) + (R_{ex} + R_c) C_{cb}$$

(1.1)

where  $\tau_b$  and  $\tau_c$  are the base and collector transit times,  $R_{ex}$  and  $R_c$  are the parasitic emitter and collector resistances,  $C_{je}$  and  $C_{cb}$  are the emitter-base and base-collector junction capacitances, and  $I_c$  is the collector current.

Examining each component separately,  $\tau_b$  is the base transit time which depends on the base thickness, bandgap energy grading variation in the base layer, and upon the carrier properties such as mobility and diffusion in the base region. If a linear grading of the base semiconductor bandgap energy with position is used to reduce  $\tau_b$ , then [17]

$$\tau_b = \frac{T_b^2}{D_n} \left(\frac{kT}{\Delta E}\right) - \frac{T_b^2}{D_n} \left(\frac{kT}{\Delta E}\right)^2 \left(1 - e^{-\Delta E/kT}\right) + \frac{T_b}{\upsilon_{exit}} \left(\frac{kT}{\Delta E}\right) \left(1 - e^{-\Delta E/kT}\right) \tag{1.2}$$

where  $\Delta E$  is the grading in the base bandgap energy,  $T_b$  the base thickness, and  $D_n$  is the base minority carrier diffusivity. The base exit velocity  $v_{exit}$  is of the order  $(kT/m^*)^{1/2}$  for a non-graded base<sup>[18]</sup>, and is somewhat larger with base bandgap grading. In this relation,  $m^*$  is the effective mass of the electron. For a typical InGaAs base at  $5 \times 10^{19}$  cm<sup>-3</sup> doping, 52 meV bandgap grading is sufficient to reduce  $\tau_b$  by ~2:1.<sup>[15]</sup> For a thick base layer or a large  $v_{exit}$ ,  $\tau_b \propto T_b^2$ ; with InGaAs base layers below ~400 Å thickness, the exit velocity term in Eqn. 1.2 adds a significant correction.

The collector transit time  $\tau_c$  is the mean delay of the collector displacement current which is a ratio of the collector thickness  $T_c$  and the effective carrier velocity given by [19,20]

$$\tau_c = \int_0^{T_c} \frac{(1 - x/T_c)}{v(x)} dx \equiv \frac{T_c}{2v_{eff}},$$

(1.3)

where v(x) is the position-dependent electron velocity in the collector drift region and  $v_{eff}$  is an effective electron velocity.  $\tau_c$  is most strongly dependent upon the electron

velocity in the proximity of the base, and becomes progressively less sensitive to the electron velocity as the electron passes through the collector. In HBTs with thin epitaxial layers, nonequilibrium electron transport is observed in the collector drift region. At low collector-base bias voltages, electrons may travel through a significant fraction of the collector drift region in the high velocity  $\Gamma$ -valley before acquiring sufficient kinetic energy (0.55 eV for InGaAs [22], 0.6 eV for InP [23]) to scatter to the lower velocity L-valley. The result is that v(x) is highest near the base. This velocity overshoot effect significantly reduces collector transit time and in structures with thin InGaAs or InP collector regions (< 3000 Å),  $v_{eff}$  = 3-5 × 10<sup>7</sup> cm/s. By contrast, measured saturation velocities in thick InGaAs drift layers are in the range of  $v_{sat}$  = 6 to 9 × 10<sup>7</sup> cm/s.

The RC charging terms in Eqn. 1.1 contribute a significant fraction of the total forward delay in submicron HBTs, and these terms must be considered in detail. In the term  $[kT/qI_c]C_{cb}$  the collector current density is limited by the onset of base pushout (the Kirk effect<sup>[24]</sup>). At high collector current densities, electron space charge screening at the edge of the base-collector junction eventually leads to a collapse of the electric field. Holes may then diffuse into the collector and effectively extend the base region, leading to an increase in base transit time and collector-base capacitance. It has been demonstrated that GaAs HBTs may exhibit improved  $f_{\tau}$  when biased close to the Kirk threshold<sup>[21]</sup>, as the reduced electric field at the collector-base junction edge increases velocity overshoot and reduces the collector transit time. We will ignore this possibility while considering the contribution of  $(kT/qI_c)C_{cb}$  to  $f_{\tau}$ .

From electrostatic considerations, the maximum collector current before base push-out is

$$I_{c,\text{max}} = A_e (V_{cb} + \phi) 3\varepsilon v_{sat} / T_c^2 \propto A_e / T_c^2$$

(1.4)

where  $v_{sat}$  is an assumed uniform electron velocity within the collector, and the collector doping  $N_d$  is chosen to obtain a fully-depleted collector at zero bias current and the applied  $V_{cb}$ . The collector capacitance is  $C_{cb} = \varepsilon A_c / T_c$ . With the HBT biased at  $I_{c,max} \propto 1/T_c^2$ ,  $(kT/qI_c)C_{cb} = T_c(A_c/A_e)$ . This delay term is thus minimized by scaling (reducing  $T_c$ ), but bias current densities must increase in proportion to the square of the desired fractional improvement in  $f_\tau$ .

The emitter charging time  $(kT/qI_c)C_{je}$  in Eqn. 1.1 plays a significant role in determining  $f_\tau$ . If  $C_{je}$  is assumed to be a simple depletion capacitance, it would be reasonable to expect that the charging time could be minimized by making the emitter-base depletion region very thick with use of very low emitter doping combined with a thick bandgap grading region in the base-emitter heterojunction. The tradeoffs between the depletion capacitance and excessive charge storage in the depletion layer are described in detail elsewhere and the results are repeated here. [15] Using methods similar to those used to derive the collector transit time [19,20]

$$C_{je}/A_{e} = \varepsilon/T_{eb} + \frac{\partial}{\partial V_{be}} \left[ \int_{0}^{T_{eb}} (x/T_{eb}) qn(x) dx \right]$$

(1.5)

where  $T_{eb}$  is depletion layer thickness and n(x) is the electron density in the depletion region. The term in  $(kT/qI_c)C_{je}$  Eqn. 1.1 can then be written as

$$(kT/qI_c)C_{je} = \left(\frac{\varepsilon A_e}{T_{eb}}\right)\left(\frac{kT}{qI_c}\right) + \frac{\Gamma T_{eb}T_b}{D_n} \int_0^1 \frac{n(\zeta T_{eb})}{n(T_{eb})} \zeta^2 d\zeta$$

(1.6)

where  $\Gamma = kT/\Delta E$  -  $(kT/\Delta E - D_n/v_{exit} T_b)e^{-\Delta E/kT}$  is a factor involving the base bandgap grading ( $\Gamma \approx 1$  for a non-graded base) and  $\zeta = x/T_{eb}$  is a normalized position variable.

The first term in Eqn. 1.6 describes the depletion-layer capacitance, and is minimized by using high bias current densities  $J_e = I_e = A_e$ . The second term describes storage of mobile electron charge within the depletion layer, and is minimized by reducing  $T_{eb}T_b$ . This analysis shows that the depletion region thickness cannot be indefinitely extended to reduce base-emitter junction capacitance, as charge storage in the region also contributes to the transistor's forward delay. The  $R_{ex}C_{cb}$  delay term in Eqn. 1.1 is thus a significant limitation when scaling for high  $f_{\tau}$ . The relative sizes of the emitter and collector contacts in a well-designed submicron HBT allow  $R_c$  to be four to ten times smaller than  $R_{ex}$ , and  $R_cC_{cb}$  can be neglected in a first order analysis. To calculate  $R_{ex}$ , we must consider the geometry of the emitter epitaxial structure.

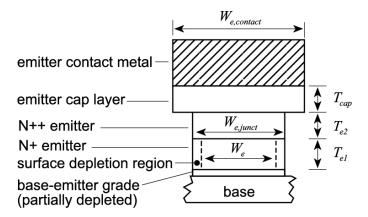

Figure 1.3 Cross-section of a base-emitter structure including epitaxial layers and emitter contact metal. For submicron emitters, the lateral depletion of the N+ emitter can comprise a significant portion of the emitter width.

The emitter layer structure shown in Figure 1.3 is composed of a heavily-doped narrow-bandgap contacting "cap" layer, an N++ heavily-doped wide-bandgap emitter layer, and a more lightly-doped (N+) emitter layer near the base interface to avoid dopant diffusion from the N++ layers into the emitter-base junction. If the heterojunction is properly graded to avoid conduction band barriers, the parasitic emitter resistance may be expressed as

$$R_{ex} = \frac{\rho_{c,e}}{L_{e}W_{e \ contact}} + \frac{\rho_{cap}T_{cap}}{L_{e}W_{e \ contact}} + \frac{\rho_{e2}T_{e2}}{L_{e}W_{e \ innet}} + \frac{\rho_{e1}T_{e1}}{L_{e}W_{e}}$$

(1.7)

where  $\rho_{c,e}$  is the emitter specific ohmic contact resistivity, and  $\rho_{cap}$ ,  $\rho_{e2}$ , and  $\rho_{e1}$  are the bulk resistivities of the cap, N++, and N+ emitter layers. For submicron emitters in a mesa HBT, the junction width  $W_{e,junct}$  is significantly smaller than the contact width  $W_{e,contact}$  due to lateral undercutting of the emitter material by the etch process used to form the emitter-base junction, and the electrically active junction width  $W_e$  can be

significantly smaller than  $W_{e,junct}$  because of the surface (edge) depletion regions of width  $(2\varepsilon\phi/qN_{e1})^{1/2}$ , where  $N_{e1}$  is the N+ layer doping and  $\phi$  is the band bending due to pinning of the Fermi energy at the surface. For simplicity in the scaling analysis, we will approximate

$$R_{av} \cong \rho_a / A_a \tag{1.8}$$

where  $\rho_e$  is a fitted parameter, approximately 50  $\Omega$ - $\mu$ m<sup>2</sup> for submicron HBTs fabricated at UCSB using a graded InAlAs/InGaAs emitter-base structure <sup>[25]</sup> and 25  $\Omega$ - $\mu$ m<sup>2</sup> for abrupt InP/InGaAs junctions. <sup>[26]</sup>

From these values of  $R_{ex}$  the  $R_{ex}C_{cb}$  charging time can then be examined. Since  $C_{cb} = \varepsilon A/T_c$ ,

$$R_{ex}C_{cb} = \left(\frac{\varepsilon\rho_c}{T_c}\right)\left(\frac{A_c}{A_e}\right). \tag{1.9}$$

This term can contribute a significant delay to  $f_{\tau}$ . An  $f_{\tau}$  of 295 GHz has been obtained in HBTs fabricated at UCSB using the substrate transfer process.<sup>[27]</sup> Although the substrate transfer process allows  $A_c/A_e$  to be small at 2.3:1, the  $R_{ex}C_{cb}$  still constitutes 11% of the total  $1/2\pi f_{\tau}$  forward delay. In mesa HBTs (Figure 1.1)  $A_c/A_e$  is often larger than 2.3:1 and hence,  $R_{ex}C_{cb}$  contributes an even larger delay. Because  $R_{ex}C_{cb} \propto 1/T_c$ , thinning the collector to reduce  $\tau_c$  also increases  $R_{ex}C_{cb}$ .

To increase HBT current gain cutoff frequencies, the base and collector layers must be thinned and the bias current density increased. Thinning the collector increases  $R_{ex}C_{cb}$ , imposing a limit to epitaxial scaling. Limits to bias current density

imposed by device reliability, and loss in breakdown voltage with reduced collector thickness, are two further potential limits to scaling. Finally, unless the device structure of Figure 1.1 is laterally scaled, vertical HBT scaling for increased  $f_{\tau}$  will result in reduced power-gain cutoff frequencies  $f_{max}$ .

## 1.2.2 Factors determining $f_{max}$

In an HBT with base resistance  $R_{bb}$  and collector capacitance  $C_{cb}$ , the power gain cutoff frequency is approximately  $f_{\text{max}} \cong (f_{\tau}/8\pi\tau_{cb})^{1/2}$ . The base-collector junction is a distributed network, and the  $\tau_{cb}$  term represents an effective, weighted time constant. The distributed network arises because the current distribution in the base-collector mesa is non-homogeneous, e.g. current density is greatest directly beneath the emitter. Because the base-collector junction parasitics are distributed, calculation of  $\tau_{cb}$  is of complex. To simplify the analysis,  $f_{max}$  is first approximated as  $f_{max} \cong (f_{\tau}/8\pi R_{bb}C_{cb})^{1/2}$ , where  $R_{bb}C_{cb}$  is the product of the base resistance and the full capacitance  $C_{cb} = \varepsilon A/T_c$  of the base-collector junction.

The base resistance  $R_{bb}$  represents the sum of contact resistance  $R_{b,cont}$ , baseemitter gap resistance  $R_{gap}$ , and spreading resistance under the emitter  $R_{spread}$ . With base sheet resistance  $\rho_s$ , and specific contact resistance  $\rho_v$ , we have

$$R_{bb} = R_{b,cont} + R_{gap} + R_{spread}$$

$$R_{b,cont} = \sqrt{\rho_s \rho_v} / 2L_e$$

$$R_{gap} = \rho_s W_{cb} / 2L_e$$

$$R_{spread} = \rho_s W_c / 12L_e$$

(1.10)

The base-collector time constant is then

$$R_{bb}C_{cb} = \left[ \left( \sqrt{\rho_{s}\rho_{v}} + \rho_{s}W_{eb} \left( \frac{\varepsilon}{2} \right) \left( \frac{L_{c}}{L_{e}} \right) \right] \left[ \frac{W_{c}}{T_{c}} \right] + \left[ \left( \frac{\rho_{s}\varepsilon}{12} \right) \left( \frac{L_{c}}{L_{e}} \right) \right] \left[ \frac{W_{c}W_{e}}{T_{c}} \right]$$

$$(1.11)$$

Equation 1.11 shows the influence of device scaling on the time constant  $R_{bb}C_{cb}$ . Decreasing the base thickness to reduce  $\tau_b$  increases the base sheet resistivity  $\rho_s$ , increasing  $R_{bb}C_{cb}$ . Decreasing the collector thickness  $T_c$  to reduce  $\tau_c$  directly increases  $R_{bb}C_{cb}$ , as is shown explicitly in Eqn. 1.11.

Low  $R_{bb}C_{cb}$ , and consequently high  $f_{max}$  may be obtained by scaling the emitter and collector junction widths  $W_e$  and  $W_c$  to submicron dimensions. Reducing the emitter width  $W_e$  alone reduces towards zero the component of  $R_{bb}C_{cb}$  associated with the base spreading resistance (the second term in Eqn. 1.11). In the mesa HBT (Figure 1.1), the minimum collector junction width  $W_c$  is set by the width of the base ohmic contacts which must be at least one contact transfer length ( $L_{contact} = (\rho_v/\rho_s)^{1/2}$ ). As a result, the component of  $R_{bb}C_{cb}$  associated with the base contact resistance (the first term in Eqn. 1.11) has a minimum value, independent of lithographic limits, and consequently,  $f_{max}$  does not increase rapidly with scaling. Given this minimum  $R_{bb}C_{cb}$ , attempts to obtain high  $f_{\tau}$  by thinning the collector results in decreased  $f_{max}$ , frustrating efforts to improve HBT bandwidths.

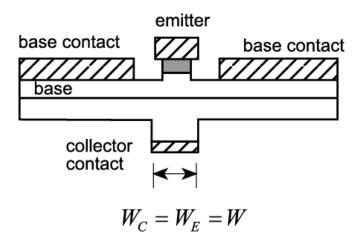

If the parasitic portion of the collector-base junction could be eliminated,  $f_{max}$  would increase rapidly with scaling. The collector-base junction need only be present

where current flows, e.g. under the emitter. An example of one such effort is UCSB's substrate transferred HBT. Various research groups have also demonstrated removal of the parasitic base-collector junction by laterally etching the extrinsic region of the collector. In both methods, the goal is to form emitter and collector junctions of near equal width, hence  $W_c = W_e$ . With submicron scaling of the emitter and collector junction widths, the first term in Eqn. 1.11 dominates becomes scalable to  $W_e$ . By this approximate analysis,  $f_{max}$  then increases as the inverse square root of the minimum feature size.

## 1.3 Highly scaled III-V HBTs

To obtain simultaneously high values of  $f_{\rm r}$  and  $f_{max}$ , the emitter and collector widths must both be scaled. To date, several methods have been successfully applied to reduce or eliminate the parasitic collector-base capacitance and, thus, improve  $f_{max}$ . The transferred substrate process is an extremely aggressive method of reducing the parasitic collector-base junction capacitance, and the method requires substantial departures from the typical mesa HBT fabrication process. Alternative processes requiring less radical alterations have been also demonstrated. In AlGaAs/GaAs HBTs it has been demonstrated that deep proton implantation through the base layer and into the collector region can be used to reduce the extrinsic collector capacitance. Wet chemical etchants can be used to remove the extrinsic collector junction by laterally undercutting beneath the base layer, and the collector capacitance under the base contact pad can be reduced using dielectric spacer layers. Alternatively,  $R_{bb}$  can be reduced by regrowing, prior to base contact

deposition, thick extrinsic P+ contact regions on the exposed base surface. [31,32] Low  $R_{bb}C_{cbi}$  can also be obtained in the typical mesa structure by reducing the lateral width of the base ohmic contacts. InGaAs base layers grown by MBE can be produced with  $> 10^{20}$  cm<sup>-3</sup> doping. At such doping levels, the transfer length  $L_{contact} = (\rho_c/\rho_s)^{1/2}$  can be greatly reduced as long as the correct (low  $\rho_c$ ) base contact is used. The width of the base ohmic contacts can then be accordingly reduced to eliminate excess collector-base junction area. The transferred substrate HBT will be briefly discussed in the following subsection followed by a discussion on recent results of highly-scaled mesa HBTs.

### 1.3.1 Transferred-substrate HBTs

The transferred-substrate process is a means of realizing a highly scalable HBT. In scaling for high  $f_{\tau}$ , limitations include high power and current density, demand for low emitter resistance, and the collapse of  $f_{max}$  due to extrinsic collectorbase junction. The substrate transfer process allows the extrinsic collector-base junction to be reduced or eliminated by providing lithographic access to both the emitter and collector material. This access allows for narrow definition of both the emitter and collector stripes and the formation of an HBT structure similar to that shown in Figure 1.4. With the extrinsic collector-base capacitance greatly reduced, aggressive lithographic scaling without epitaxial scaling greatly increases  $f_{max}$  at constant  $f_{\tau}$ . If high values of both  $f_{\tau}$  and  $f_{max}$  are sought, simultaneous lithographic and epitaxial scaling is required. Further improvements in device bandwidth beyond what

is reported here would require operation at higher current densities and reduction of parasitic base and emitter resistances.

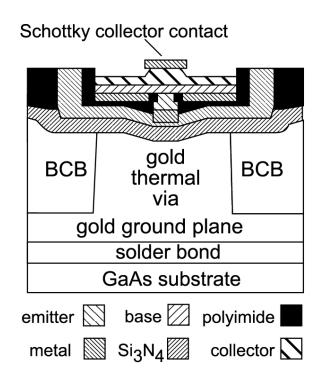

Figure 1.4 Cross-section of an HBT with the collector-base junction lying only under the emitter. Such a device structure can be formed using substrate transfer processes.

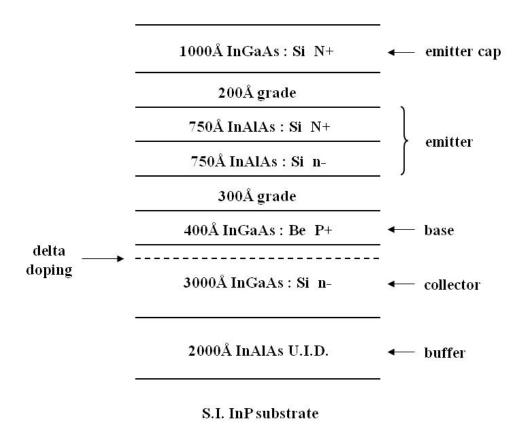

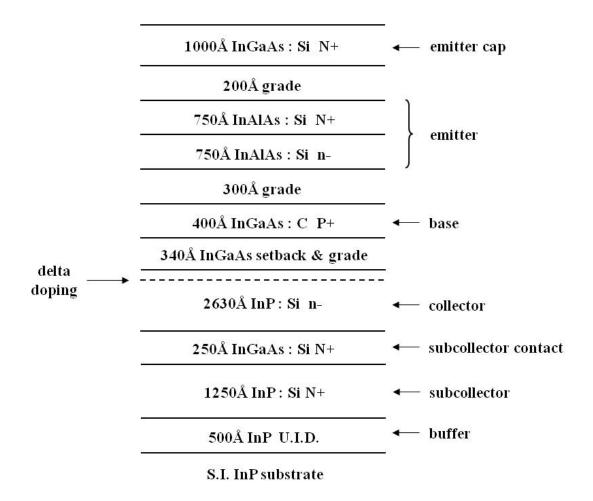

The transferred substrate epitaxial structure has been grown by MBE on semi-insulating InP substrates, and both single and double heterojunction transistors have been fabricated in the transferred-substrate technology. The single heterojunction transistors have an InAlAs/InGaAs emitter-base junction with an InGaAs collector region. The double heterojunction devices have an InP collector for increased breakdown, and an InP emitter may be used in place of the InAlAs ternary for improved heat flow from the emitter. Chirped superlattice grades are used to smooth conduction band discontinuities at the base heterojunctions. The InGaAs base is typically 300 to 400 Å thick, has 2kT bandgap grading, and is Be-doped at  $5 \times 10^{19}$  cm<sup>-3</sup>. The collector thickness is typically 2000 to 3000 Å thick, and an N+ pulsedoped layer placed 400 Å from the base-collector metallurgical junction delays the

onset of base push-out at high collector current densities. High  $f_{max}$  devices are typically fabricated with Schottky collector contacts that provide zero collector series resistance.<sup>[34]</sup>

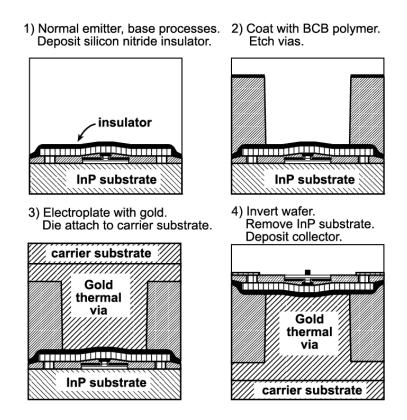

Figure 1.5 Transferred substrate HBT fabrication process flow.

Figure 1.5 shows the transferred substrate process flow. Standard fabrication processes<sup>[35]</sup> are used to define the emitter-base junction, the base mesa, polyimide planarization, and the emitter contacts. The substrate transfer process commences with the deposition of a 5 µm thickness Benzocyclobutene (BCB) transmission-line dielectric. Thermal and electrical vias are etched in the BCB, and electroplating is used to deposit metal vias and to form the wafer's ground plane. The wafer is then

solder-bonded to a GaAs or AlN carrier substrate. The InP substrate is removed in a selective HCl etch to expose the collector epitaxial layer, and collector contacts are patterned onto the exposed collector. Shown in Figure 1.6 is a detailed cross section of the completed transferred substrate device.

Figure 1.6 Schematic cross-section of a transferred substrate HBT.

For the emitter-base junction, deep submicron scaling requires tight control of lateral undercutting during the base contact recess etch. The undercut both narrows the emitter and defines the liftoff edge in self-aligned base contact deposition. For InAlAs emitters, the transferred substrate process uses a combination of dry and wet etch mechanisms. A CH<sub>4</sub>/H<sub>2</sub>/Ar reactive ion etch (RIE) is used to remove the N+ InGaAs emitter contact layer and to partially etch into the InAlAs emitter. A

HCl/HBr/acetic acid selective wet etch is then used to remove the InAlAs emitter and to etch partially into the emitter-base grade. The selective nature of this etch allows it to stop at a consistent depth in the InAlAs/InGaAs grade. A timed, nonselective citric acid-based wet etchant is then used to remove the remaining base-emitter grade. The etch is allowed to penetrate approximately 100 Å into the base layer to ensure that the contacts lay on base material. An all wet etch process is used for transferred substrate devices using an InP emitter. A selective H<sub>2</sub>O<sub>2</sub>/H<sub>3</sub>PO<sub>4</sub> etchant is used to remove the N+ InGaAs emitter contact layer, and the etch stops at the InP emitter layer. A selective HCl/H<sub>3</sub>PO<sub>4</sub> etch is then used to remove the emitter semiconductor, and this etch stops at the InGaAs base. For emitter etch processes, an undercut of ~0.1 μm is desirable to minimize base gap resistance between the emitter and the base metal, and the etch processes must be well controlled to maintain as little undercut as possible.

In defining the collector-base junction, the use of a Schottky-collector contact eliminates the need for an etch of similar precision as when an N+ ohmic collector contact layer is used. The collector junction is defined by the stripe width of the collector metal. After collector deposition, a self-aligned wet etch of ~1000 Å depth removes the collector junction sidewalls to eliminate fringing fields. This etch also reduces the collector junction width by ~2000 Å. The step, intended to reduce  $C_{cb}$ , is observed to provide a greater increase in  $f_{max}$  than would be expected from the physical reduction in collector junction width.

Extrapolated  $f_{max}$  up to 820 GHz and  $f_{\tau}$  up to 300 GHz have been obtained with transferred-substrate HBTs.<sup>[36,37]</sup> Both of these results were obtained using single

heterojunction transistors with a wide-bandgap InAlAs emitter and InGaAs base and collector. The high  $f_{max}$  result was obtained using a 400 Å base layer and 3000 Å collector while the high  $f_{\tau}$  result was achieved using a 300 Å base and 2000 Å collector structure. At the time of each publication, the results were the highest ever reported in a bipolar transistor technology in any material system.

A number of integrated circuit results have been reported in the transferred substrate process. Master-slave latches configured as 2:1 static frequency dividers were fabricated which correctly function at all frequencies in the 5-75 GHz range. This static frequency divider was the fastest ever reported until that time. High-speed analog ICs accomplishments in the transferred substrate technology include 80 GHz distributed amplifiers,  $[^{39}]$  50 GHz broadband differential amplifiers,  $[^{40}]$  and broadband Darlington and  $f_{\tau}$ -doubler resistive feedback amplifiers. Tuned mm-wave amplifiers have been demonstrated using transferred substrate HBTs, including a 75 GHz amplifier and 180 GHz tuned amplifier.  $[^{43,44}]$

The circuits described above contain as few as two and as many as seventy transistors, as well as passive components and interconnects. Larger digital and mixed-signal ICs have been fabricated in the transferred substrate process. For instance,  $\Delta$ - $\Sigma$  modulators composed of 150 HBTs and operating at up to 18 GHz clock rate have been demonstrated, and larger digital circuits (~250 HBTs) were developed to include sum and carry generation circuits for pipeline adderaccumulators. [46]

Despite record results for discrete transferred-substrate HBTs and the success of circuits constructed using the device technology; there have been only a few duplications of the transferred substrate work outside of UCSB. InP DHBTs have been produced at the Ferdinand-Braun-Institut für Höchstfrequenztechnik. [47,48] Along with improvements to the epitaxial stack (InP emitter and collector), changes were made to improve the thermal characteristics of the device after the transferred substrate process. The UCSB transferred substrate process leaves the remaining HBT epi "floating" in low thermoconductivity dielectric; allowing heat leave the device mostly through the emitter and collector contacts. As current density increases, the device will heat. This heat will eventually lead to device failure if the current density is taken too high. The effort at Ferdinand-Braun attempts to resolve the heating issue by sinking heat out of the emitter, through a thick lateral metal layer, and into a high thermoconductivity AlN substrate. This device has produced an  $f_{\tau}$  of 410 GHz and  $f_{max}$  of 480 GHz at current density  $J_c = 6.5 \text{ mA/}\mu\text{m}^2$  for a  $0.8 \times 5 \mu\text{m}^2$  emitter with 300 Å carbon-doped base and 1250 Å total collector thickness.

A transferred substrate HBT demonstration at Northrop Grumman Corporation also attempts to resolve the heating issue by transferring the device to a higher thermal conductivity SiC substrate after patterning the narrow backside collector. The Northrop Grumman device produces an  $f_{\tau}$  of 397 GHz and  $f_{max} > 400$  GHz at current density  $J_c = 10.5$  mA/ $\mu$ m<sup>2</sup> for a  $0.2 \times 3$   $\mu$ m<sup>2</sup> emitter with 280 Å beryllium-doped base and 1500 Å total collector thickness.

The transferred substrate effort at UCSB has had its greatest affect by altering the perception of scaling potential in III-V HBTs. New focus has since been given to the original mesa HBT structure utilizing very aggressive scaling in the device layout and epitaxial structure to minimize device parasitics. This effort is responsible for a new generation of highly-scaled III-V mesa HBTs.

## 1.3.2 Trends in highly scaled mesa HBTs

Aggressive scaling in III-V HBTs using the original mesa structure has lead to new record results. Ida, et al. reported an InP/InGaAs mesa DHBT in late 2002 with aggressive epitaxial and layout scaling. The emitter dimension was  $0.8 \times 3 \mu m^2$ and the paper compares devices with 20 and 30 nm thick base layers and 150 nm collectors. The device incorporated heavy carbon base doping at  $6 \times 10^{19}$  cm<sup>-3</sup> for lattice-matched InGaAs and compositional grading of the GaAs in the InGaAs base. The GaAs mole fraction in the 30 nm base device was linearly increased from 0.47 (lattice matched to InP) to 0.56 towards the base-emitter heterojunction. In the 20 nm base device a larger mole fraction was used to achieve a higher base doping concentration. The composition was 0.56 at the base-collector interface and increased to 0.60 towards the base-emitter junction. The device also incorporated an isolated base pad layout. [51] The base pad isolation structure was used to eliminate the extrinsic collector capacitance at the large area where the base is connected to the pad structure. The 20 nm device achieved a record 351 GHz  $f_{\tau}$  and 288 GHz  $f_{max}$  at a current density of  $J_c = 667 \text{ kA/cm}^2$  while simultaneously high values of 329 GHz was obtained for both  $f_{\tau}$  and  $f_{max}$  in the 30 nm device.

Dahlström, et al. later reported an InP/InGaAs/InP mesa DHBT with 282 GHz  $f_{\tau}$  and 400 GHz  $f_{max}$  using a 25 nm doping-graded InGaAs base and 214 nm collector depletion layer. [52] The high  $f_{max}$  result is attributed to the minimization of base resistance  $R_{bb}$  and collector-base capacitance  $C_{cb}$ . The  $R_{bb}$  parasitic is composed of base current spreading under the emitter stripe, the emitter-base gap resistance, and the contact resistance of the base metal. The first two components are reduced by high base doping to obtain low base resistance, narrow emitter junctions, and minimal spacing between the emitter junction and base contact. The third component—the base contact resistance—is minimized by very high base doping and by the Pd/Ti/Pt/Au ohmic base metal. [53] The base doping in this device is graded from a degenerate  $8 \times 10^{19}$  cm<sup>-3</sup> at the emitter interface to  $5 \times 10^{19}$  cm<sup>-3</sup> at the collector side producing a 49 meV potential drop and a 16.5 kV/cm drift field in the base assuming Fermi-Dirac statistics and accounting for bandgap narrowing. Assuming  $D_{n,b}=43$ cm<sup>2</sup>/sec average diffusivity and  $4 \times 10^7$  cm/s exit velocity into the collector, the calculated base transit time is reduced from 0.18 to 0.10 ps contributing to a lower  $f_{\tau}$ . The emitter metal for this device is 0.7 µm wide with a junction undercut by 80 nm on each side producing an emitter junction width of 0.54 µm. The base metal is selfaligned to the emitter metal and extends 1 µm on each side of the 8 µm emitter length producing a total base-collector junction width of 2.7 µm. The aggressive lateral scaling and the high base doping allow for an InP mesa HBT with high  $f_{\tau}$  and record  $f_{max}$ .

The same team later produced a device with the same epitaxial structure, layer thicknesses, and device dimensions but improved RF performance.<sup>[54]</sup> This device demonstrated a 370 GHz  $f_{\tau}$  and 459 GHz  $f_{max}$  by decreasing base and emitter contact resistances, increasing current density through the device, and undercutting the extrinsic collector region under the base by 200 nm to reduce  $C_{cb}$ . The  $f_{\tau}$  demonstrated in this device was the highest reported for a InP-based mesa HBT at the time. These results were some of the highest simultaneous numbers ever reported at the time, and the  $C_{cb}/I_c$  ratio = 0.28 ps/V at  $V_{cb}$  = 0.5 V was the lowest ever reported for an InP mesa DHBT.

The Ida, et al. group from above also reported simultaneously high  $f_{\tau}$  and  $f_{max}$  results for an InP/InGaAs mesa DHBT in late 2003. The paper presented at the GaAs IC Symposium reported the first sub-4 ps delay in an ECL circuit. As an addendum to the circuit results which used non self-aligned base to emitter electrodes, the group fabricated devices with self-aligned base contacts to demonstrate the capability of the device technology. The circuit results utilized the earlier reported device with the 30 nm compositionally graded base, 150 nm collector, and  $0.8 \times 3 \, \mu m^2$  emitter which produce simultaneous  $f_{\tau}$  and  $f_{max}$  over 300 GHz. The group reports that the dominant part of their non self-aligned base resistance is access resistance between the emitter mesa and base electrode. In their lateral scaling experiment, they used the same epitaxial layer structure as for the non self-aligned device and fabricated devices with 0.6, 0.8, and 1.0  $\mu$ m widths and 5  $\mu$ m lengths. They found that  $f_{max}$  increases with decreased emitter width which they attribute to reduced intrinsic base resistance

and reduced intrinsic base-collector capacitance. The  $0.6 \times 5 \,\mu\text{m}^2$  self-aligned device achieved a maximum simultaneous  $f_{\tau}$  and  $f_{max}$  of 347 and 492 GHz, respectively.

In 2006, Lind, *et al.* reported a record InP/InGaAs/InP DHBT with 650 GHz  $f_{max}$  and simultaneous 420 GHz  $f_r$ . In this work, the emitter width was scaled to 250 nm and substantial improvements had been made to the base and emitter Ohmic contacts. The HBTs were formed using an all wet etch triple mesa fabrication process where undercut determined the 250 nm emitter width. The InGaAs base is 30 nm thick and carbon doped from 7 to  $4 \times 10^{19}$  cm<sup>-3</sup> to create a 50 meV conduction band grade. The total collector thickness including base-collector grade is 150 nm. TLM measurements showed a base contact resistance  $\rho_c < 5 \Omega \cdot \mu \text{m}^2$  and base sheet resistance  $\rho_s = 630 \Omega$ . The emitter  $\rho_c = 5.3 \Omega \cdot \mu \text{m}^2$  was extracted from RF-parameter fitting. These contact resistance numbers represent a 50% improvement compared to previous work from the same group. The  $0.25 \times 3.1 \mu \text{m}^2$  emitter area device demonstrated a 650 GHz  $f_{max}$  and 420 GHz  $f_r$  at  $I_C = 9$  mA and  $V_{ce} = 1.58$  V.

Using epitaxial material and fabrication process identical to Lind, Griffith *et al.* reported a record InP/InGaAs/InP DHBT with 755 GHz  $f_{max}$  and simultaneous 416 GHz  $f_{\tau}$  in 2007. In this work, the base contact resistance  $\rho_c = 6.3~\Omega \cdot \mu \text{m}^2$ , base sheet resistance was measured slightly lower at  $\rho_s = 603~\Omega$ , and the emitter  $\rho_c = 5.1~\Omega \cdot \mu \text{m}^2$ . Despite the similarities, Griffith's  $0.30 \times 2.0~\mu \text{m}^2$  emitter area device was able to demonstrate a record 755 GHz  $f_{max}$  and 416 GHz  $f_{\tau}$  at  $I_C = 6.98$  mA and  $V_{ce} = 1.74$  V.

#### 1.4 Highly scaled SiGe HBTs

SiGe HBTs emerged in the early 2000s as strong RF performance contenders to InP HBTs. In addition to the newly improved performance, SiGe HBTs had the additional promise of process maturity, higher levels of integration and yield, and the ability to monolithically integrated CMOS devices into the SiGe fabrication process (BiCMOS).

In 2002, Hitachi reported an NPN SiGe HBT with heavily-doped and narrow intrinsic base layer and emitter area of  $0.15 \times 1.0 \,\mu\text{m}^2$  demonstrating 227 GHz  $f_{max}$  and 201 GHz  $f_{\tau}$  at  $I_C = 1.2$  mA and  $V_{ce} = 1.5$  V.<sup>[58]</sup> The record RF performance is attributed to optimization of the thickness and profile of the carbon doping in the SiGe base layer to reduce both intrinsic base resistance and contact resistance to the external base elements. The work also indicates emitter width dependence where narrow emitter (and proportionally narrow base) widths of 0.15  $\mu$ m demonstrate higher peak  $f_{max}$  compared to emitter widths up to 0.3  $\mu$ m.

IHP Microelectronics reported an NPN SiGe:C HBT in 2003 with elevated extrinsic base contacts rather than the more conventional implanted extrinsic base. Peak  $f_{max}$  was observed to increase from 186 GHz to 225 GHz when elevated base contacts were used in lieu of the implanted extrinsic base. The improvement is attributed to reduced  $R_{bb}$  and  $C_{cb}$  when using the elevated base structure. A further reduction was obtained in base resistance by shrinking the drawn emitter width from 0.21  $\mu$ m to 0.175  $\mu$ m; increasing the peak  $f_{max}$  to 243 GHz. The 0.175  $\times$  0.84  $\mu$ m<sup>2</sup> emitter area HBT with selectively grown elevated extrinsic base has 243 GHz  $f_{max}$  and

190 GHz  $f_{\tau}$  at  $I_C = 1.5$  mA and  $V_{ce} = 1.5$  V.<sup>[59]</sup> The same group later reported a SiGe HBT with aggressive vertical scaling and a selectively undercut collector to reduce base-collector capacitance. The device improvements produce a  $0.175 \times 0.84 \, \mu \text{m}^2$  NPN HBT with 300 GHz  $f_{\tau}$  and 250 GHz  $f_{max}$  at  $I_C = 1.5$  mA and  $V_{ce} = 1.5$  V where the total  $C_{cb}$  at  $V_{cb} = 0$  V is reduced from 3fF to 2.5fF when comparing a conventionally fabricated device to the device with undercut collector.<sup>[60]</sup>

Infineon Technologies also reported SiGe HBTs with impressive results using a thinned base region with increased doping levels; allowing for reduced base transit time without increasing the intrinsic base sheet resistance. The Infineon HBTs also utilize a mono-crystalline emitter contact for reduced total emitter resistance. The  $0.14 \times 2.6 \, \mu\text{m}^2$  NPN HBT demonstrates a 300 GHz  $f_{max}$  and simultaneous 215 GHz  $f_{\tau}$  at  $I_C = 3.5$  mA and  $V_{cb} = 1$  V. A higher maximum  $f_{\tau}$  of 225 GHz is also reported for  $V_{cb} = 0$  V, but  $f_{max}$  drops to ~260 GHz at this bias condition.

In 2002, IBM reported SiGe HBTs with 70% improvement in  $f_{\tau}$  and  $f_{max}$  compared with their 120 GHz  $f_{\tau}$  production device. To achieve simultaneously high  $f_{\tau}$  and  $f_{max}$ , the NPN vertical and lateral dimensions were reduced compared to the 120 GHz generation. The emitter n-epitaxial layer thickness, collector, and base doping concentrations were scaled to achieve a target  $f_{\tau}$  of 200 GHz. A self-aligned, raised extrinsic base is employed, the emitter dimension is narrowed, and the emitter to extrinsic base spacer is reduced to lower the total base resistance  $R_{bb}$ . The resulting device has a pinched base resistance of 2.5 k $\Omega$ /sq, a peak dc current gain of 400,  $BV_{CEO}$  of 1.7 V, and  $BV_{CBO}$  of 5.5 V. For a 0.12 × 2.5  $\mu$ m<sup>2</sup> emitter area device at  $V_{cb}$

of 1 V,  $f_{\tau}$  is over 200 GHz for a current density range of 8.3-16.5 mA/  $\mu$ m<sup>2</sup>, peaking at 207 GHz; the  $f_{max}$  peaks at 285 GHz. In 2004, further improvement in  $f_{\tau}$  was achieved by vertical profile scaling <sup>[3]</sup>, and reduction of base resistance was achieved by reducing the polysilicon parasitic resistance component of the raised extrinsic base to obtain a  $0.12 \times 2.5 \ \mu$ m<sup>2</sup> emitter area device with 350 GHz  $f_{max}$  and 300 GHz  $f_{\tau}$  at  $I_C = 5.7$  mA and  $V_{cb} = 0.5$  V.<sup>[64]</sup>

<sup>1</sup> K. Shinohara, Y. Yamashita, A. Endoh, K. Hikosaka, T. Matsui, T. Mimura, and S. Hiyamizu, "Ultrahigh-speed pseudomorphic InGaAs/InAlAs HEMTs with 400-GHz cutoff frequency," *IEEE Electron Device Letters*, vol. 22, no. 11, November 2001, pp 507-9.

<sup>&</sup>lt;sup>2</sup> P.M Smith, S.-M.J Liu, M.-Y Kao, P. Ho, S.C. Wang, K.H.G. Duh, S.T. Fu, P.C. Chao, "W-band high efficiency InP-based power HEMT with 600 GHz f<sub>max</sub>," *IEEE Microwave and Guided Wave Letters*, vol.5, no.7, July 1995, pp.230-2.

<sup>&</sup>lt;sup>3</sup> J-S. Rieh, B. Jagannathan, H. Chen, KT. Schonenberg, D. Angell, A. Chinthakindi, J. Florkey, F. Golan, D. Greenberg, S-J. Jeng, M. Khater, F. Pagette, C. Schnabel, P. Smith, A. Stricker, K. Vaed, R. Volant, D. Ahlgren, G. Freeman, K. Stein K, S. Subbanna, "SiGe HBTs with cut-off frequency of 350 GHz," *International Electron Devices Meeting. Technical Digest.* IEEE. 2002, pp.771-4.

<sup>&</sup>lt;sup>4</sup> J. Bardeen and W. H. Brattain, "The transistor, a semi-conductor triode," *Phys. Rev.* **74**, 230 (1948).

<sup>&</sup>lt;sup>5</sup> W. H. Brattain and J. Bardeen, "Nature of the forward current in germanium point contacts," *Phys. Rev.* **74**, 231 (1948).

<sup>&</sup>lt;sup>6</sup> W. Shockley, "The theory of p-n junctions in semiconductors and p-n junction transistors," *Bell System Technology Journal* **28**, 435 (1949).

<sup>&</sup>lt;sup>7</sup> W. Shockley, "Circuit element utilizing semiconductive materials," U.S. Patent No. 2 569 347 September 25, 1951.

<sup>&</sup>lt;sup>8</sup> H. Kroemer, "Theory of a wide-gap emitter for transistors," *Proc. IRE* **45**, 1535 (1957).

<sup>&</sup>lt;sup>9</sup> D. A. Jenny, "The status of transistor research in compound semiconductors," *Proc. Inst. Radio Engrs.* **46**, 959 (1958).

<sup>&</sup>lt;sup>10</sup> R. Ruth, J. C. Marinace and W. C. Dunlap, Jr., "Vapor deposited single-crystal germanium," *J. Appl. Phys.* **31**, 995 (1960).

<sup>&</sup>lt;sup>11</sup> R. L. Anderson, "Experiments on Ge-GaAs heterojunction," *Solid-State Electron.* **5**, 341 (1962).

<sup>&</sup>lt;sup>12</sup> D. K. Jadus and D. L. Feucht, "The realization of a wide band gap emitter transistor," *IEEE Trans. Electron Devices* **16**, 102 (1969).

<sup>&</sup>lt;sup>13</sup> W. P. Dumke, J. M. Woodall, and V. L. Rideout, "GaAs-GaAlAs heterojunction transistor for high-frequency operation," *Solid-State Electron.* **15**, 12 (1972).

<sup>&</sup>lt;sup>14</sup> S. Yamahata, K. Kurishima, H. Ito, Y. Matsuka, "Over-22-GHz-fT-and-fmax InP/InGaAs double-heterojunction bipolar transistors with a new hexagonal-shaped emitter," *IEEE GaAs IC Symposium Technical Journal*, 1995, pp. 163-6.

<sup>&</sup>lt;sup>15</sup> M.J.W. Rodwell, M. Urteaga, Y. Betser, T. Mathew, S. Krishnan, D. Scott, S. Jaganathan, D. Mensa, R. Pullela, Q. Lee, B. Agarwal, U. Bhattacharya, S. Long, "Scaling of InGaAs/InAlAs HBTs for high speed mixed-signal and mm-Wave ICs," *International Journal of High Speed Electronics and Systems*, vol. 11, no. 1, World Scientific Publishing Company, 2001.

<sup>&</sup>lt;sup>16</sup> M. Urteaga, S. Krishnan, D. Scott, Y. Wei, M. Dahlstrom, S. Lee, M.J.W. Rodwell, "Submicron InP-based HBTs for ultra-high frequency amplifiers," *International Journal of High Speed Electronics and Systems*, vol. 13, no. 2, World Scientific Publishing Company, 2003.

<sup>&</sup>lt;sup>17</sup> H. Kroemer, "Two integral relations pertaining to the electron transport through a bipolar transistor with a nonuniform energy gap in the base region," *Solid State Electronics*, vol. 28, 1985, pp. 1101-3.

<sup>&</sup>lt;sup>18</sup> B. G. Streetman, *Solid State Electronic Devices*, third ed., Prentice-Hall, 1990.

<sup>&</sup>lt;sup>19</sup> S. Laux, W. Lee, "Collector signal delay in the presence of velocity overshoot," IEEE Electron Device Letters, vol. 11, no. 4, 1990, pp. 174-6.

<sup>&</sup>lt;sup>20</sup> T. Ishibashi, "Influence of electron velocity overshoot on collector transit times of HBTs," IEEE Transactions on Electron Devices, vol. 37, no. 9, September 1990, pp 2103-5

<sup>&</sup>lt;sup>21</sup> T. Ishibashi, "Nonequilibrium electron transport in HBTs," IEEE Transactions on Electron Devices, vol. 48, no. 11, November 2001, pp. 2595-605.

<sup>&</sup>lt;sup>22</sup> M. Littlejohn, K.W. Kim, H. Tian, "High-field transport in InGaAs and related heterostructures," in *Properties of lattice-matched and strained Indium Gallium Arsenide*, P. Bhattacharya, ed., INSPEC, 1993, London.

<sup>&</sup>lt;sup>23</sup> E. P. O'Reilly, "Band structure of InP: Overview," in *Properties of Indium Phosphide*, INSPEC, 1991, London.

$<sup>^{24}</sup>$  C.T. Kirk, "A theory of transistor cutoff frequency ( $f_{\tau}$ ) fall-off at high current density," IEEE *Transactions on Electron Devices*, ED-9, 1962, p. 164.

<sup>&</sup>lt;sup>25</sup> D. Mensa, *Improved current-gain cutoff frequency and high gain-bandwidth amplifiers in transferred substrate HBT technology*, University of California, Santa Barbara Ph.D. Thesis, September, 1999.

<sup>&</sup>lt;sup>26</sup> M. Dahlström, *Ultra high speed InP heterojunction bipolar transistors*, Royal Institute of Technology, Stockholm Ph.D. Thesis, 2003.

<sup>&</sup>lt;sup>27</sup> M. Urteaga, D. Scott, M. Dahlström, Y. Betser, S. Lee, S. Krishnan, T. Mathew. S. Jaganathan. Y. Wei, M.J.W. Rodwell, "Ultra High Speed Heterojunction Bipolar Transistor Technology," *2001 GOMAC Conference Technical Digest*, March 2001.

<sup>&</sup>lt;sup>28</sup> M.-C. Ho, R.A. Johnson, W.J. Ho, M.F. Chang, P.M. Asbeck, "High-performance low-base-collector capacitance AlGaAs/GaAs heterojunction bipolar transistors fabricated by deep ion implantation," *IEEE Electron Device Letters*, vol. 16, no. 11, November 1995, pp. 512-4.

- <sup>30</sup> T. Oka, K. Hirata, K. Ouchi, H. Uchiyama, K. Mochizuki, T. Nakamura, "Small-scaled InGaP/GaAs HBTs with WSi/Ti base electrode and buried SiO<sub>2</sub>," *IEEE Transactions on Electron Devices*, vol.45, no.11, November 1998, pp.2276-82.

- <sup>31</sup> H. Shimawaki, Y. Amamiya, N. Furuhata, K. Honjo, "High f<sub>max</sub> AlGaAs/InGaAs and AlGaAs/GaAs HBT's with p+/p regrown base contacts," *IEEE Transactions on Electron Devices*, vol. 42, no. 10, October 1995, pp. 1735-44.

- <sup>32</sup> Y. Matsuoka, S. Yamahata, K. kurishima and H. Ito, "Ultrahigh-speed InP/InGaAs double-heterostructure bipolar transistors and analysis of their operation," *Japanese Journal of Applied Physics*, vol. 35, 1996, pp.5646-54.

- <sup>33</sup> I. Harrison, M. Dahlström, S. Krishnan, Z. Griffith, Y.M. Kim, M.J.W. Rodwell, "Thermal limitations of InP HBTs in 80 and 160Gbit integrated circuits," *Conference Proceedings, IEEE International Conference on Indium Phosphide and Related Materials*, 2003, pp.160-3.

- <sup>34</sup> R. P. Smith, S.T. Allen, M. Reddy, S.C. Martin, J. Liu, R. E. Muller, M.J.W. Rodwell, "0.1 μm Schottky-collector AlAs/GaAs resonant tunneling diodes," *IEEE Electron Device Letters*, vol. 15, no. 8, August 1994, pp. 295-7.

- <sup>35</sup> W. E. Stanchina, R.H. Walden, M. Hafizi, H.-C. Sun, T. Liu, C. Raghavan, K.E. Elliott, M. Kardos, A.E. Schmitz, Y.K. Brown, M.E. Montes, M. Yung, "An InP-based HBT fab for high-speed digital, analog, mixed-signal, and optoelectronic ICs," *Technical Digest, IEEE GaAs IC Symposium*, 1995, pp. 31-4.

- <sup>36</sup> Q. Lee, S. C. Martin, D. Mensa, R.P. Smith, J. Guthrie, and M.J.W. Rodwell, "Submicron transferred-substrate heterojunction bipolar transistors," *IEEE Electron Device Letters*, vol. 20, no. 8, August 1999, pp. 396-8.

- $^{37}$  Y. Betser, D. Scott, D. Mensa, S. Jaganathan. T. Mathew and Mark Rodwell, "InAIAs/InGaAs HBTs with simultaneously high values of  $f_{\tau}$  and  $f_{max}$  for mixed analog/digital applications," *IEEE Electron Device Letters*, vol. 22, no. 2, February 2001, pp. 56-8.

- <sup>38</sup> T. Mathew, H.J. Kim, S. Jaganathan, D. Scott, S. Krishnan, Y. Wei, M. Urteaga, M.J.W. Rodwell, S. Long, "75 GHz ECL Static Frequency Divider Using InAIAs/InGaAs HBTs," *IEE Electronic Letters*, vol. 37, no. 11, May 2001, pp. 667-8.

- <sup>39</sup> S. Krishnan, S. Jaganathan, T. Mathew, Y. Wei, M. J. W. Rodwell, "Broadband HBT amplifiers," 2000 IEEE Cornell Conf. High Speed Electronics. Ithaca, NY.

<sup>&</sup>lt;sup>29</sup> W. Liu, D. Hill, H.F. Chau, J. Sweder, T. Nagle and J. Delany, "Laterally etched undercut (LEU) technique to reduce base-collector capacitance in heterojunction bipolar transistors," *Technical Digest*, *IEEE GaAs IC Symposium*, 1995, pp. 167-170.

<sup>&</sup>lt;sup>40</sup> B. Agarwal, Q. Lee, R. Pullela, D. Mensa, J. Guthrie, and M. J.W. Rodwell, "A transferred-substrate HBT wideband differential amplifier to 50 GHz," *IEEE Microwave Guided Wave Lett.*, vol. 8, July 1998, pp. 263–265.

<sup>&</sup>lt;sup>41</sup> D. Mensa, R. Pullela, Q. Lee, B. Agarwal, J. Guthrie, S. Jaganathan, M. J.W. Rodwell, "Baseband amplifiers in the transferred-substrate HBT technology," *Technical Digest, IEEE GaAs IC Symposium*, 1998, pp. 33-6.

<sup>&</sup>lt;sup>42</sup> S. Krishnan, D. Mensa, J. Guthrie, S. Jaganathan, T. Mathew, R. Girish, Y. Wei and M.J.W. Rodwell, "Broadband lumped HBT amplifiers," *IEE Electronics Letters*, vol. 36, no. 5, March 2000, pp.466-7.

<sup>&</sup>lt;sup>43</sup> J.R. Guthrie, M. Urteaga, D. Scott, D. Mensa, T. Mathew, Q. Lee, S. Krishnan, S. Jaganathan, Y. Betser and M.J.W. Rodwell, "HBT MMIC 75GHz Power Amplifiers," *Conference Proceedings, IEEE International Conference on Indium Phosphide and Related Materials*, 2000, pp.246-9.

<sup>&</sup>lt;sup>44</sup> M. Urteaga, D. Scott, T. Mathew, S. Krishnan, Y. Wei and M.J.W. Rodwell, "185 GHz Monolithic amplifier in InGaAs/InA1As transferred-substrate HBT technology," *IEEE MTT-S International Microwave Symposium Digest*, vol. 3, 2001, pp. 1713-1716.

<sup>&</sup>lt;sup>45</sup> S. Jaganathan, D. Mensa, T. Mathew, Y. Betser, S. Krishnan. Y. Wei. D. Scott, M. Urteaga, M. Rodwell, "A 18 GHz continuous time ∑-Δ modulator implemented in InP transferred substrate HBT technology," *Technical Digest, IEEE GaAs IC Symposium*, 2000, pp. 251-4.

<sup>&</sup>lt;sup>46</sup> T. Mathew, S. Jaganathan, D. Scott, S. Krishnan, Y. Wei, M. Urteaga, M.J.W. Rodwell, S. Long, "2 Bit Adder: Carry and Sum Logic Circuits at 19 Ghz Clock Frequency in InA1As/InGaAs HBT Technology," *IEE Electronics Letters*, vol. 37, no. 19, September 2001, pp. 1156-7.

<sup>&</sup>lt;sup>47</sup> Kraemer, T.; Lenk, F.; Maassdorf, A.; Wuerfl, H.J.; Traenkle, G., "High yield transferred substrate InP DHBT," *Indium Phosphide & Related Materials*, 2007. *IPRM '07. IEEE 19th International Conference on*, vol., no., pp.407-408, 14-18 May 2007.

<sup>&</sup>lt;sup>48</sup> Kraemer, T.; Rudolph, M.; Schmueckle, F.J.; Wuerfl, J.; Traenkle, G., "InP DHBT process in transferred-substrate technology with  $f_{\tau}$  and  $f_{max}$  over 400 GHz," *Electron Devices, IEEE Transactions on*, vol.56, no.9, pp.1897-1903, Sept. 2009.

<sup>&</sup>lt;sup>49</sup> Scott, D.W.; Monier, C.; Wang, S.; Radisic, V.; Phuong Nguyen; Cavus, A.; Deal, W.R.; Gutierrez-Aitken, A., "InP HBT transferred to higher thermal conductivity substrate," *IEEE Electron Device Letters*, vol. 33, no. 4, 2012, pp. 507-509.

$<sup>^{50}</sup>$  M. Ida, K. Kurishima, N. Wantannabe, "Over 300 GHz  $f_{\tau}$  and  $f_{max}$  double heterojunction bipolar transistors with a thin pseudomorphic base," *IEEE Electron Device Letters*, vol. 23, no. 12, December 2002, pp. 694-6.

<sup>&</sup>lt;sup>51</sup> M. Ida, S. Yamahata, H. Nakajima, N. Wantannabe, "High-performance small InP/InGaAs HBTs with reduced parasitic base-collector capacitance fabricated using novel base-metal design," *Proceedings of the International Symposium on Compound Semiconductors*, 1999, pp. 293-6.

<sup>&</sup>lt;sup>52</sup> M. Dahlstrom, X.M. Fang, D. Lubyshev, M. Urteaga, S. Krishnan, N. Parthasarathy, Y.M. Kim, Y. Wu, J.M. Fastenau, W.K. Liu, M.J.W. Rodwell, "Wideband DHBTs using a graded carbon-doped InGaAs base," *IEEE Electron Device Letters*, vol. 24, no. 7, July 2003, pp. 433-5.

<sup>&</sup>lt;sup>53</sup> E.F. Chor, R.J. Malik, R.A. Hamm, R. Ryan, "Metallurgical stability of ohmic contacts on thin base InP/InGaAs/ InP HBTs," *IEEE Electron Device Letters*, vol. 17, February 1996, pp. 62-4.

$<sup>^{54}</sup>$  Z. Griffith, M. Dahlstrom, M. Urteaga, M.J.W. Rodwell, X.M. Fang, D. Lubyshev, Y. Wu, J.M. Fastenau, W.K. Liu, "InGaAs-InP mesa DHBTs with simultaneously high  $f_{\tau}$  and  $f_{max}$  and low  $C_{cb}/I_c$  ratio," *IEEE Electron Device Letters*, vol. 25, no. 5, May 2004, pp. 250-3.

<sup>&</sup>lt;sup>55</sup> M. Ida, K. Kurishima, K. Ishii, N. Wantannabe, "High-speed InP/InGaAs DHBTs with a thin pseudomorphic base," *IEEE GaAs IC Symposium Technical Digest*, 2003, pp. 211-4.

<sup>&</sup>lt;sup>56</sup> Lind, E.; Griffith, Z.; Rodwell, M.J.W.; Xiao-Ming Fang; Loubychev, D.; Yu Wu; Fastenau, J.M.; Liu, A.W.K., "250 nm InGaAs/InP DHBTs w/650 GHz  $f_{max}$  and 420 GHz  $f_{\tau}$ , operating above 30 mW/μm<sup>2</sup>," *Device Research Conference Digest*, 64th, June 2006, pp. 26-28.

<sup>&</sup>lt;sup>57</sup> Griffith, Z.; Lind, E.; Rodwell, M.J.W.; Xiao-Ming Fang; Loubychev, D.; Ying Wu; Fastenau, J.M.; Liu, A.W.K., "Sub-300 nm InGaAs/InP Type-I DHBTs with a 150 nm collector, 30 nm base demonstrating 755 GHz f<sub>max</sub> and 416 GHz f<sub>T</sub>," *IEEE 19th International Conference on Indium Phosphide & Related Materials Technical Digest*, 14-18 May 2007, pp.403-406.

<sup>&</sup>lt;sup>58</sup> T. Hashimoto, Y. Nonaka, T. Tominari, H. Fujiwara, K. Tokunaga, M. Arai, S. Wada, T. Udo, M. Seto, M. Miura, H. Shimamoto, K. Washio, H. Tomioka, "Direction to improve SiGe BiCMOS technology featuring 200-GHz SiGe HBT and 80-nm gate CMOS," *IEDM Technical Digest*, 2003, pp. 129-132.

<sup>&</sup>lt;sup>59</sup> H. Rücker, B. Heinemann, R. Barth, D. Bolze, J. Drews, U. Haak, W. Höppner, D. Knoll, K. Köpke, S. Marschmeyer, H.H. Richter, P. Schley, D. Schmidt, R. Scholz, B. Tillack, W. Winkler, H.E. Wulf, Y. Yamamoto, "SiGe:C BiCMOS technology with 3.6 ps gate delay," *IEDM Technical Digest*, 2003, pp. 121-124.

<sup>&</sup>lt;sup>60</sup> B. Heinemann, R. Barth, D. Bolze, J. Drews, P. Formanek, T. Grabolla, U. Haak, W. Höppner, D.K. Köpke, B. Kuck, R. Kurps, S. Marschmeyer, H.H. Richter, H. Rücker, P. Schley, D. Schmidt, W. Winkler, D.Wolansky, H.E. Wulf, Y. Yamamoto, "A low-parasitic collector construction for high-speed SiGe:C HBTs," *IEDM Technical Digest*, 2004, pp. 251-254.

<sup>&</sup>lt;sup>61</sup> T.F. Meister, H. Schifer, K. Aufinger, R. Stengl, S. Boguth, R. Schreiter, M. Rest, H. Knapp, M. Wurzer, A. Mitchell, T. Bottner, J. Bock, "SiGe bipolar technology with 3.9 ps gate delay," *IEEE Bipolar BiCMOS Circuits and Technology Meeting Technical Digest*, 2003, pp. 103-106.

<sup>&</sup>lt;sup>62</sup> J. Böck, H. Schäfer, H. Knapp, K. Aufinger, M. Wurzer, S. Boguth, T. Böttner, R. Stengl, W. Perndl, and T. F. Meister, "3.3 ps SiGe bipolar technology," *IEDM Technical Digest*, 2004, pp. 255-258.

$<sup>^{63}</sup>$  B. Jagannathan, M. Khater, F. Pagette, J.-S. Rieh, D. Angell, H. Chen, J. Florkey, F. Golan, D. R. Greenberg, R. Groves, S. J. Jeng, J. Johnson, E. Mengistu, K. T. Schonenberg, C. M. Schnabel, P. Smith, A. Stricker, D. Ahlgren, G. Freeman, K. Stein, S. Subbanna, "Self-aligned SiGe NPN transistors with 285 GHz  $f_{max}$  and 207 GHz  $f_T$  in a manufacturable technology," *IEEE Electron Device Letters*, vol. 23, no. 5, May 2002, pp. 258-260.

$<sup>^{64}</sup>$  M. Khater, J.S. Rieh, T. Adam, A. Chinthakindi, J. Johnson, R. Krishnasamy, M. Meghelli, F. Pagette, D. Sanderson, C. Schnabel, K. T. Schonenberg, P. Smith, K. Stein, A. Strieker, S.J. Jeng, D. Ahlgren, G. Freeman, "SiGe HBT technology with  $f_{max}/f_T = 350/300$  GHz and gate delay below 3.3 ps," *IEDM Technical Digest*, 2004, pp. 247-250.

# Chapter 2

## **MBE Growth of InP HBTs**

#### 2.1 Introduction to HBT Growth

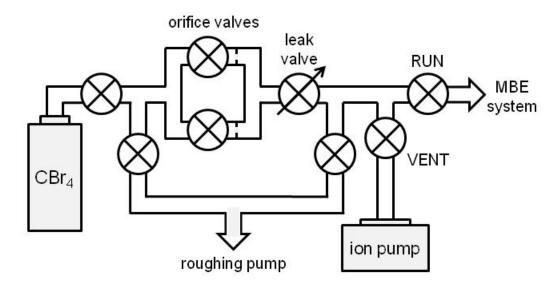

The material growth for HBTs and the regrown emitter HBT work was performed in Varian Gen II MBE systems at UCSB. The MBE systems are typically used for the growth of optoelectronic devices, such as surface and vertical cavity lasers and detectors. In recent years, the growth of electron devices, such as HEMTs and HBTs, has become more common in the epitaxial systems. Two systems, referred to as System A and System B, were used for this work. Both systems contain the group III elemental solid sources gallium, aluminum, and indium. Valved cracker sources provide the group V elements in each system. System A has an arsenic source installed, and System B has arsenic, phosphorous, and antimony sources available. Both systems have beryllium and carbon as p-type dopant sources, and silicon is available as an n-type dopant.

The Gen II MBE systems are designed to accommodate a single 3-inch, round substrate. However, material growth at UCSB is typically performed on full 2-inch substrates, quarters of 2-inch substrates, or even smaller samples. Molybdenum face-

plates and silicon backing wafer mounting blocks are available and typically used to convert the 3-inch growth stage for full 2-inch wafers and quarters of 2-inch wafers. Indium bonding may also be used to attach smaller samples or quarter wafers to solid molybdenum blocks for growth. Indium bonded samples allow multiple small and non-standard shaped samples to be mounted for growth. The indium mounting technique also provides strong, uniform thermal contact between the growth sample and the mounting block. The mounting, however, requires additional effort, it may be difficult to remove the indium from the sample backside, and there is potential for contamination or oxidation buildup as the sample is being handled and heated during the mounting process. The use of molybdenum adapter plates and silicon backing wafers is therefore generally preferred over indium mounting.

HBT growths, emitter regrowths, and the growth of base-collector templates are generally performed on full 2-inch Fe-doped semi-insulating InP substrates using the molybdenum adapter plates and backing wafer mountings. Epi-ready substrates were purchased from Sumitomo Electric Semiconductor Materials, Inc. and Wafer Technology, Ltd. Both vendors provide substrates that are identical in specification, and no significant difference is observed in the growth conditions or epitaxial quality when switching between the substrate vendors.

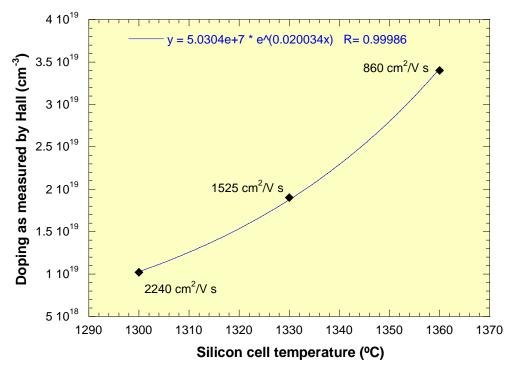

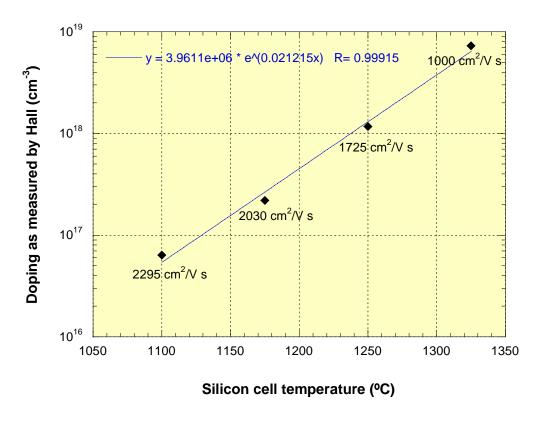

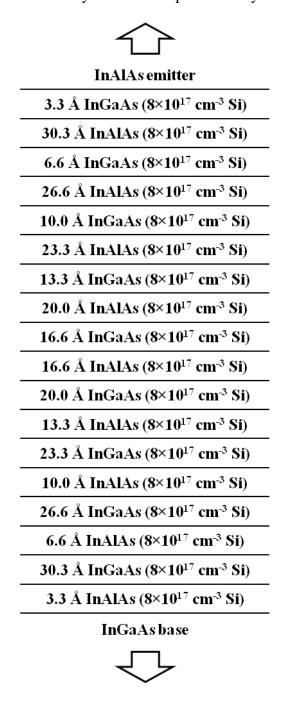

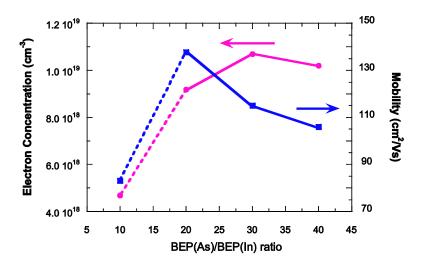

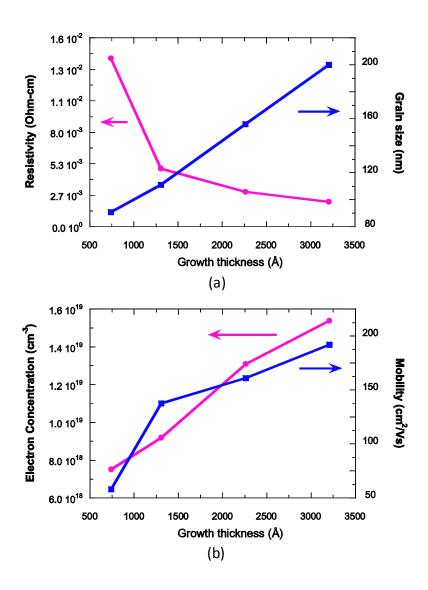

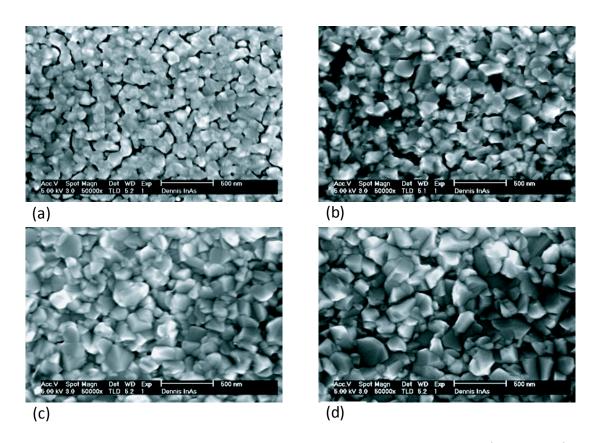

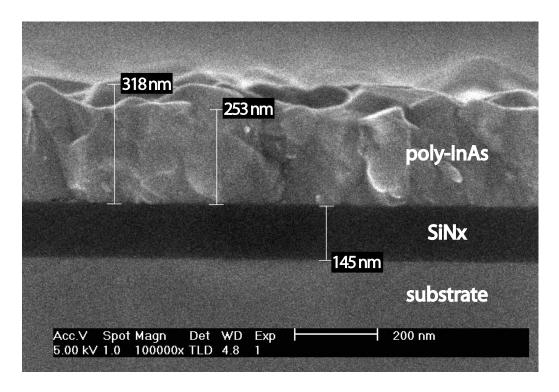

The epitaxial growth rates and ternary compositions used during this work were determined using either reflected high energy electron diffraction (RHEED) oscillations or beam equivalent flux. When using RHEED calibrations, the binary growth rates for InAs on InAs, GaAs on GaAs, and for AlAs on GaAs were