### UNIVERSITY OF CALIFORNIA

### Santa Barbara

# Fabrication Processes and Epitaxial Growth Technologies for Base-Collector Parasitics Reduction in Indium Phosphide HBT

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

**Electrical and Computer Engineering**

by

Yingda Dong

Committee in charge:

Professor Mark J.W. Rodwell, Co - Chair

Professor Umesh K. Mishra, Co - Chair

Professor Stephen I. Long

Professor Arthur C. Gossard

June 2004

| The disse | ertation of Yingda Dong is approved. |

|-----------|--------------------------------------|

|           |                                      |

|           |                                      |

|           |                                      |

|           |                                      |

|           | Umesh K. Mishra                      |

|           |                                      |

|           |                                      |

|           |                                      |

|           | Stephen I. Long                      |

|           |                                      |

|           |                                      |

|           |                                      |

|           | Arthur C. Gossard                    |

|           |                                      |

|           |                                      |

|           |                                      |

| Mark      | J.W. Rodwell, Committee Chair        |

# Fabrication Processes and Epitaxial Growth Technologies for Base-Collector Parasitics Reduction in Indium Phosphide HBT

Copyright © 2004

By

Yingda Dong

All rights reserved

# **Acknowledgements**

Working at UC Santa Barbara has been a deeply rewarding experience. I have been fortunate to work with many excellent researchers who inspired, guided and assisted me. I would like to thank my advisors Prof. Mark Rodwell and Prof. Umesh Mishra for all their support and guidance during my time at UCSB. I have benefited greatly from Prof. Rodwell's extraordinary ability to teach, unbelievably broad knowledge, and infectious enthusiasm for work. I am indebted to Prof. Mishra for constantly providing good advice and brilliant ideas, while at the same time giving me freedom to explore my own thoughts. I would also like to thank my defense committee members Prof. Arthur Gossard and Prof. Steve Long for their very kind encouragement and support. As head of the MBE lab Prof. Gossard had constant contact and input into my work of InP HBT material growth.

I am thankful to members of both groups for their support and friendship: Christoph, Dennis, Heng-Kuang, Jong-Uk, Mattias, Miguel, Munkyo, Navin, Paidi, Shouxuan, Young-Min, Yun, and Zach in the Rodwell group, and Ale, Ariel, Arpan, Can, Dan, Dario, DJ, Haijiang, Huili, Ilan, James, Lee, Likun, Michael, Naiqian, Rob, Siddarth, Sten, Tomas, Yuvarajj in the Mishra group. I am grateful also to the York group members with whom I have shared the office

for four years: Bruce, Chris, Hongtao, Jaehoon, Nadia, Paolo, Peter, Pengcheng, Troy, and Vicki.

Many thanks go to John English for his dedication to keep the world-class MBE lab running smoothly. Thanks also go to all the System B growers: Andy, Borys, Dave, Mahdu, Max, and Mehgan.

I also owe gratitude to Yae Okuno for taking up all the InP MOCVD growth for me and doing a truly superb job.

And finally, I would like to thank my wife and parents. Without your love and support, I would never have reached this far.

# Vita

### Education

- **B.S.** Physics, Fudan University, Shanghai, China, June 1997

- **M.S.** Physics, University of Delaware, Newark, Delaware, December 1999

- **Ph.D.** Electrical Engineering, University of California, Santa Barbara, California, June 2004

### **Publications**

- 1. **Y. Dong**, Y. Wei, Z. Griffith, M. Urteaga, M. Dolstrom, A. Gossard, and M. Rodwell, 'InP Heterojunction Bipolar Transistor with a Selectively Implanted Collector', submitted to IEEE Electron. Dev. Lett.

- 2. **Y. Dong**, Z. Griffith, M. Urteaga, M. Dolstrom, A. Gossard, and M. Rodwell, 'C<sub>BC</sub> Reduction in InP Heterojunction Bipolar Transistor with Selectively Implanted Collector Pedestal', *62nd Device Research Conference*, *Notre Dame*, *IN*, *2004*.

- 3. **Y. Dong**, A.C. Gossard, and M.J.W Rodwell, 'Compensation of Interfacial Charges at the Regrowth Interface between InP Layers', *46th Electronic Materials Conference, Notre Dame, IN, 2004.*

- 4. **Y. Dong**, Y. Wei, Z. Griffith, M. Urteaga, M. Dolstrom, A. Gossard, and M. Rodwell, 'InP Heterojunction Bipolar Transistor with Selectively Implanted Collector', 2003 International Semiconductor Device Research Symposium, Washington, DC, (ISDRS 2003).

- 5. **Y. Dong**, Y. Wei, Z. Griffith, M. Urteaga, M. Dolstrom, A. Gossard, and M. Rodwell, 'InP Heterojunction Bipolar Transistor with Selectively Implanted Collector Pedestal', accepted by *Solid State Electronics*.

- Y. Dong, Y. Okuno, and U. Mishra, 'InP Heterojunction Bipolar Transistor with Extrinsic Base Laterally Overgrown on Buried SiO<sub>2</sub>', submitted to Solid State Electronics.

- 7. **Y. Dong**, Y. Okuno, and U. Mishra, 'MOCVD Selective Growth of InP through Narrow Openings and its Application to InP HBT Extrinsic Base Regrowth', *Journal of Crystal Growth*, 260 (2004) 316-321.

- 8. **Y. Dong**, D. Scott, Y. Wei, A. Gossard, and M. Rodwell, 'Low Resistance P-type Polycrystalline GaSb grown by Molecular Beam Epitaxy', *Journal of Crystal Growth*, 256 (2003) 223-229.

- 9. **Y. Dong**, D. Scott, A. Gossard, and M. Rodwell, 'Characterization of Contact Resistivity on InAs/GaSb Interface', *Electronic Materials Conference, Salt Lake City, UT, 2003*.

- 10. **Y. Dong**, Y. Okuno, and U. Mishra, 'Selective Area Growth of InP through Narrow Openings by MOCVD and its Application to InP HBT', *15th International Conference on Indium Phosphide and Related Materials, Santa Barbara, CA, 2003 (IPRM 2003)*.

- 11. **Y. Dong**, D. Scott, A. Gossard, and M. Rodwell, 'Molecular Beam Epitaxy of Low-Resistance Polycrystalline P-type GaSb', *15th International Conference on Indium Phosphide and Related Materials, Santa Barbara, CA, 2003, (IPRM 2003).*

- 12. N. Parthasarathy, **Y. Dong**, D. Scott, M. Urteaga and M.J.W. Rodwell, 'Planar Device Isolation for InP Based DHBTs', 62nd Device Research Conference, Notre Dame, IN, 2004.

- 13. D. Scott, C. Kadow, **Y. Dong**, Y. Wei, A. C. Gossard, and M.J.W. Rodwell, 'Low Resistance n-type Polycrystalline InAs grown by Molecular Beam Epitaxy', accepted by *Journal of Crystal Growth*.

- 14. Y. Wei, D. Scott, **Y. Dong,** A.C. Gossard, and M.J.W. Rodwell, 'A 160-GHz  $f_T$  and 140-GHz  $f_{MAX}$ , Submicronmeter InP DHBT in MBE Regrown-Emitter Technology', IEEE Electron Dev. Lett., 25 (2004) 232-234.

- 15. D. Scott, Y. Wei, **Y. Dong,** A.C. Gossard, and M.J.W. Rodwell, 'A 183GHz f<sub>T</sub> and 165GHz f<sub>MAX</sub> Regrown-Emitter DHBT with Abrupt InP Emitter', IEEE Electron Dev. Lett., 25 (2004) 360-362.

- 16. Y. Wei, D. Scott, Y. Dong, A.C. Gossard, and M.J.W. Rodwell, '280GHz f<sub>T</sub> InP DHBT with 1.2μm<sup>2</sup> Base-Emitter Junction Area in MBE Regrown Emitter Technology', 62nd Device Research Conference, Notre Dame, IN, 2004.

### **Abstract**

Fabrication Processes and Epitaxial Technologies For Base-Collector Paracitics

Reduction in Indium Phosphide HBT

by

# Yingda Dong

The increasing demand in communication and radar technology for higher bitrates and increased frequency resolution is eventually reflected in the requirement of devices capable of operating at very high frequencies. Currently the great limitations on heterojunction bipolar transistor (HBT) speed are the parasitic components of the device, most notably the extrinsic base-collector capacitance ( $C_{BC}$ ) and base resistance ( $R_B$ ).

This dissertation is focused on efforts to develop novel regrowth and fabrication process technologies toward reducing InP HBT's base-collector parasitic capacitance and base resistance. Although ultra wide-bandwidth InP HBTs were the end goal, the majority of the efforts were focused on growth and process technologies.

InP HBT with extrinsic base laterally overgrown on buried  $SiO_2$  has been proposed and developed for simultaneous reduction of  $C_{BC}$  and  $R_B$ . To obtain

maximum lateral overgrowth length, the MOCVD selective growth of InP through narrow mask openings has been carefully examined. Both DC and RF characteristics of the base-regrown HBTs are demonstrated.

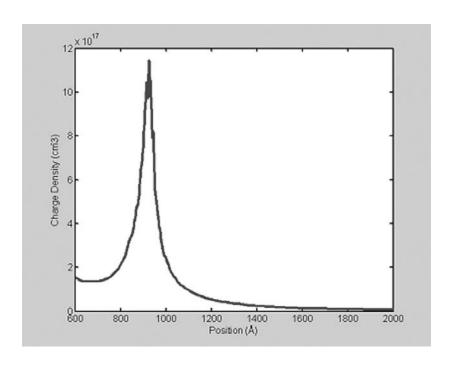

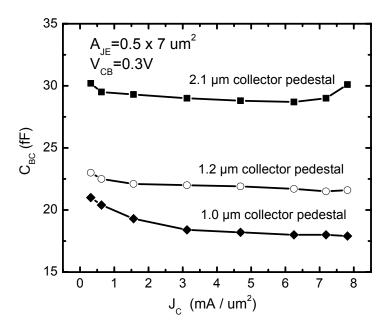

InP HBT with a collector pedestal has also been developed for base-collector capacitance reduction. The collector pedestal is formed by using selective ion implantation and regrowth by molecular beam epitaxy. Many aspects of Si implantation in InP have been examined. Concerns relating to HBT layer structure design, epitaxial growth, and device fabrication have been addressed. N-type sheet charge accumulation is discovered on the InP regrowth interface and P-type counter-doping layer is successfully introduced to compensate the interfacial charge. Both DC and RF performances of pedestal HBTs are demonstrated with 40% base-collector capacitance reduction achieved.

Finally to combine the best features of SiGe and InP HBT technology, double-poly regrowth InP HBT is proposed with structural features and process flow close to that of a Si/SiGe HBT. In our efforts to find a low resistivity material for the extrinsic base, the MBE growth and electrical properties of carbon-doped polycrystalline GaSb, as well as the interfacial contact resistivity of N-InAs/P-GaSb heterostructure are thoroughly investigated.

# **Table of Contents**

| Chapter 1                                                                                                                                      | 1  |

|------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Introduction                                                                                                                                   | 1  |

| 1.1 Overview                                                                                                                                   | 1  |

| 1.2 Motivations of InP HBT's Base-collector Parasitic Reduction                                                                                | 2  |

| 1.3 Synopsis of the Dissertation                                                                                                               | 5  |

| References                                                                                                                                     |    |

| Chapter 2                                                                                                                                      | 11 |

| InP HBT with Extrinsic Base Laterally Overgrown on SiO <sub>2</sub> .                                                                          | 11 |

| 2.1 Introduction                                                                                                                               | 11 |

| 2.2 Epitaxial Techniques                                                                                                                       | 14 |

| 2.2.1 Molecular Beam Epitaxy                                                                                                                   | 14 |

| 2.2.2 Metal-Organic Chemical Vapor Deposition                                                                                                  | 17 |

| 2.3 Epitaxial Lateral Overgrowth of InP on SiO <sub>2</sub>                                                                                    | 20 |

| 2.3.1 Overview                                                                                                                                 |    |

| 2.3.2 Crystallographic Structures of Zinc Blende                                                                                               |    |

| <ul><li>2.3.3 InP Lateral Overgrowth Experiments and Results</li><li>2.3.4 Qualitative Explanations for Lateral Overgrowth Behaviors</li></ul> | 27 |

| 2.4 InP HBT with Laterally Overgrown Base on Buried SiO <sub>2</sub>                                                                           |    |

| 2.4.1 Intrinsic HBT Material Structure and Growth                                                                                              |    |

| 2.4.1 Intrinsic HBT Material Structure and Growth                                                                                              |    |

| 2.4.3 DC Measurements of the Regrown Base HBTs                                                                                                 |    |

| 2.4.4 RF Measurements of the Regrown Base HBTs                                                                                                 |    |

| 2.5 Summary                                                                                                                                    | 49 |

| References                                                                                                                                     | 52 |

| Chapter 3                                                                                                                                      | 57 |

| InP HBT with Selectively Implanted Collector                                                                                                   | 57 |

| 3.1 Introduction                                                                                                                               |    |

| 3.2 Si Ion Implantation in InP                                                                                                                 | 60 |

| 3.2.1 Overview                                            | 60  |

|-----------------------------------------------------------|-----|

| 3.2.2 Implantation Energy and Fluence                     | 60  |

| 3.2.3 Implant Lateral Distribution                        |     |

| 3.2.4 Annealing of Implanted Si Dopants                   |     |

| 3.2.5 Regrowth Crystalline Quality on Implanted Substrate | 68  |

| 3.3 HBT Layer Structure Design                            | 71  |

| 3.3.1 Emitter Design                                      | 71  |

| 3.3.2 Base Design                                         | 72  |

| 3.3.3 Collector Design                                    | 73  |

| 3.4 MBE Growth                                            | 75  |

| 3.4.1 Oxide Desorption                                    | 75  |

| 3.4.2 Lattice Matching                                    | 76  |

| 3.4.3 Interfaces                                          |     |

| 3.4.4 Carbon Doping                                       | 78  |

| 3.5 Device Fabrication                                    | 80  |

| 3.5.1 Overview                                            | 80  |

| 3.5.2 Alignment Mark                                      |     |

| 3.5.3 SiN Implant Mask                                    |     |

| 3.5.4 Implant Window Etch                                 |     |

| 3.5.5 Metal Contact on n-type InP                         |     |

| 3.5.6 Regrowth Interface Treatment                        |     |

| 3.6 Regrowth Interface Charge Accumulation                |     |

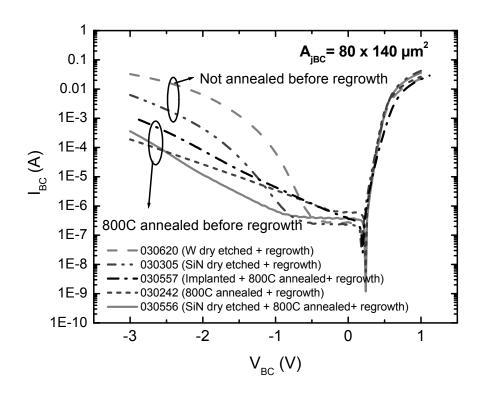

| 3.6.1 First Generation Pedestal HBT                       |     |

| 3.6.2 Regrowth Interface Charge Accumulation              |     |

| 3.6.3 Interfacial Charge Compensation                     |     |

| 3.6.4 Be-InP and C-InGaAs charge compensation layers      |     |

| 3.7 Device Results                                        |     |

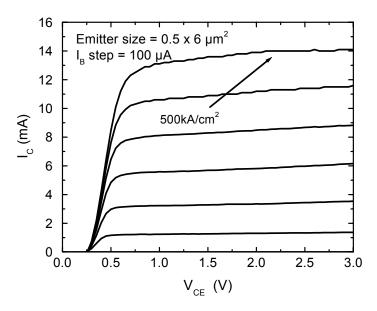

| 3.7.1 DC Characteristics                                  |     |

| 3.7.2 RF Characteristics                                  |     |

| 3.8 Summary                                               |     |

| References                                                | 134 |

| Chapter 4                                                 | 139 |

| InP HBT with Polycrystalline Extrinsic Base — Material    |     |

| Aspects                                                   | 139 |

| 4.1 Introduction                                          | 139 |

| 4.2 Low-Resistance P-type Polycrystalline GaSb            | 145 |

| 4.2.1 Overview                                            | 145 |

| 4.2.2 Experimental Procedures                  | 148 |

|------------------------------------------------|-----|

| 4.2.3 Results and Discussions                  |     |

| 4.2.4 Summary                                  | 156 |

| 4.3 Contact Resistivity on InAs/GaSb Interface | 157 |

| 4.3.1 Overview                                 | 157 |

| 4.3.2 Experimental Procedures                  | 160 |

| 4.3.3 Results and Discussions                  |     |

| 4.4 Summary                                    | 167 |

| References                                     |     |

| Chapter 5                                      |     |

| Conclusion                                     |     |

| 5.1 Achievements                               | 173 |

| 5.2 Future Work                                | 176 |

| 5.2.1 Lateral Overgrowth of Extrinsic Base     | 176 |

| 5.2.2 Collector Pedestal HBTs                  |     |

| 5.2.3 Double-Poly Regrowth Process             |     |

| References                                     | 184 |

# **Chapter 1**

# Introduction

### 1.1 Overview

Heterojunction bipolar transistors (HBTs) have high transconductance, extremely reproducible parameters and wide bandwidth. These attributes make HBTs the device of choice for many precision high-speed circuits. In recent years, research in wide bandwidth HBTs<sup>[1],[2]</sup> have been driven fast by applications in high-frequency communications and radar. First, in optical fiber communications, the emergence of 160Gb/s transmission equipment in the near future must rely on a timely and substantial improvement in the bandwidth of semiconductor electronics. Amplifiers with flat gain and linear phase over a ~DC-110GHz bandwidth and master-slave latches<sup>[3]</sup> operable at 80GHz or 160GHz clock frequency will be required. A second set of driving applications are wideband, high resolution and analog-digital converters (ADCs). Digital-analog converters (DACs), and direct digital frequency synthesizers<sup>[4]</sup>. Increased bandwidths of these mixed-signal ICs will increase the bandwidth and frequency agility of military radar and communication systems. High resolution ADCs and

DACs require transistor bandwidths  $10^2$ :1 to  $10^4$ :1 larger than the signal frequencies involved. Transistors with several hundred GHz  $f_T$  and  $f_{max}$  would enable high-resolution microwave mixed-signal ICs. A third driving application is in monolithic millimeter-wave integrated circuits (MIMICs). Progressive improvements in transistor bandwidths permit the evolution of radar and communications ICs to higher frequencies. A transistor with 1THz power gain cut-off frequency would provide useful gain over the full 30GHz-300GHz millimeter-wave band. This would permit e.g. digital radio links with millimeter-wave carrier frequencies and 1-10Gb/s channel capacities.

These ever-growing demands in communications and radar technologies for increased bit-rates and frequency resolution all require system capable of providing increased bandwidth and clock rates, which is eventually reflected in the requirement that the HBTs, which are the building blocks of these systems, must be capable of operating at higher and higher frequencies.<sup>[5],[6]</sup>

# 1.2 Motivations of InP HBT's Base-collector Parasitic Reduction

Two measures or figure-of-merit useful in evaluating the high-frequency performance of a transistor are the current-gain cutoff frequency  $f_T$ , and maximum frequency of oscillation  $f_{max}$ .  $f_T$  is defined as the frequency at which

the short-circuit current gain decreases to unity.  $f_{max}$  is defined as the frequency at which the maximum available power gain decreases to unity. Though finally dependent on the application, transistors with increased  $f_T$  and  $f_{max}$  are desirable in order to meet the demands in bandwidth of the next generation of systems.

To a first approximation,  $f_T$  corresponds to the transit time of carriers through the device. For an HBT,  $f_T$  is written as:

$$f_T = \frac{1}{2\pi(\tau_E + \tau_B + \tau_C + \tau_{CC})} , \qquad (1.1)$$

where  $\tau_E$  and  $\tau_{CC}$  are time constants related to the charging and discharging of the device capacitance and  $\tau_B$  and  $\tau_C$  are transit times through the device. In order to increase  $f_T$  in bipolar transistors, the relative time constants and transit times must be reduced. This entails scaling the device vertically to decrease the distances across which the carriers transit. With the advent of precise growth techniques, like molecular beam epitaxy (MBE), which allow for the control of device layer thickness at the atomic scale, vertical or epitaxial scaling is easily achieved, and transistors with  $f_T$  on the order of several hundred GHz are possible. [7],[8]

On the other hand,  $f_{max}$ , which is related to  $f_T$ , is strongly dependent on the magnitude of the base resistance ( $R_B$ ) and base-collector capacitance ( $C_{BC}$ ) time constant:

$$f_{\text{max}} = \sqrt{\frac{f_T}{8\pi R_B C_{BCi}}} , \qquad (1.2)$$

$C_{Bci}$  is the intrinsic part of  $C_{BC}$  in series with the base resistance.  $f_{max}$  is increased by reducing  $R_B$  and  $C_{BCi}$  chiefly through increased doping in the base and horizontal scaling. State-of-the-art conventional emitter-up transistors with  $\sim 0.4 \mu m$  wide emitters demonstrate  $f_{max}$  of up to  $\sim 500 GHz$ . But commonly, conventional mesa-structured HBTs are still limited by the extrinsic base-collector capacitance underneath the base contacts.

At a given HBT scaling generation, defined by the minimum emitter feature size, different transistors layer structures are preferred so as to obtain a differing balance of device parasitics that are more sited for the particular application – i.e. mm-wave tuned amplifiers benefit from high  $f_{max}$  and tolerate appreciably lower  $f_T$ . The minimum gate delay of a digital IC in contrast is not determined by an algebraic function of  $f_T$  and  $f_{max}$ , but instead by a set of time constants of which  $C_{BC}\Delta V_{logic}/I_C$  is a major contributor.

Since base-collector capacitance ( $C_{BC}$ ) is a critical factor limiting the device and IC's high-frequency performance, various technologies and techniques that directly address the reduction of  $C_{BC}$  have been examined: HBT with a buried subcollector by selective epitaxy<sup>[10]</sup> and selective implantation<sup>[11]</sup>, sidewall contacted bases<sup>[12]</sup>, undercut collectors<sup>[13]</sup>, collector-up transistors with regrown

base-collector junction or implanted extrinsic emitters<sup>[14],[15]</sup>, and the transferred substrate HBT<sup>[16]</sup>.

# 1.3 Synopsis of the Dissertation

This dissertation covers several novel regrowth technologies and process techniques toward reducing base-collector parasitic capacitance and base resistance. Although ultra wide-bandwidth InP HBTs were the end goal, the majority of this thesis is focused on process technologies.

Chapter 2 discusses the design, epitaxial growth and fabrication process of InP HBT with extrinsic base laterally overgrown on buried SiO<sub>2</sub> for simultaneous reduction of C<sub>BC</sub> and R<sub>B</sub>. The MOCVD selective growth behaviors of InP through narrow openings have been carefully examined. It is found that the lateral overgrowth of InP on SiO<sub>2</sub> is strongly dependent on both the opening width and orientation. Based on these experimental results, HBTs with extrinsic base laterally overgrown on buried SiO<sub>2</sub> were fabricated. Emitters were aligned 60° off [011] direction to obtain the maximum lateral overgrowth length for the extrinsic base. Both DC and RF characteristics of the base-regrown HBTs are demonstrated.

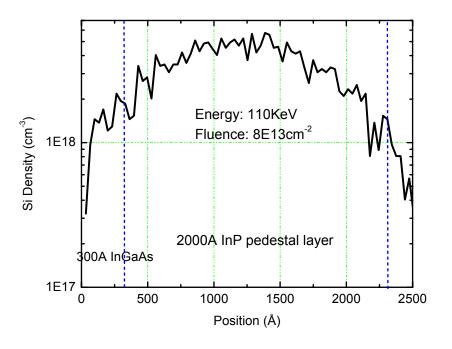

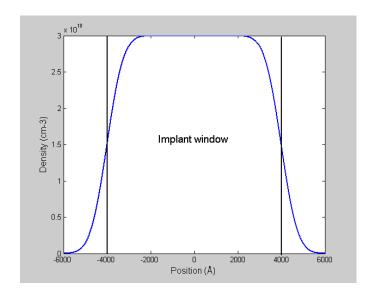

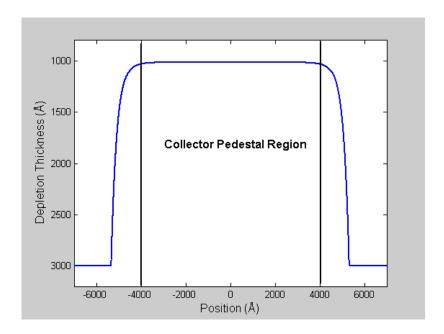

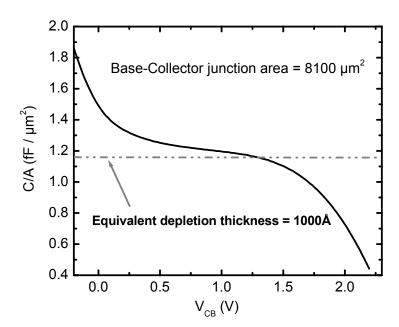

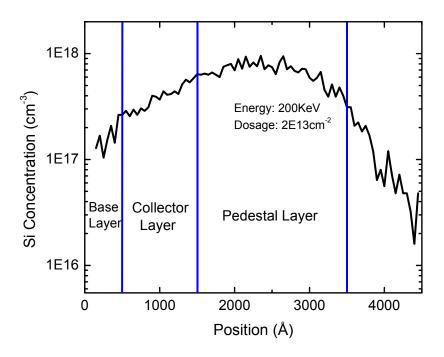

Chapter 3 presents the design and fabrication of an InP HBT with a collector pedestal. The pedestal, formed by selective ion implantation and

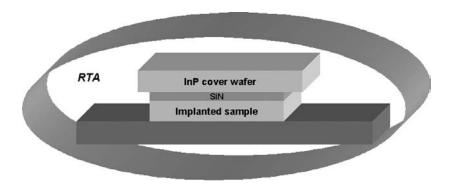

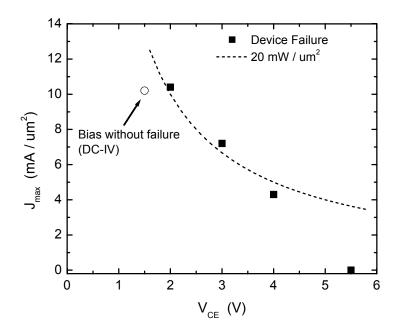

regrowth by molecular beam epitaxy, permits a larger collector depletion thickness under the base contacts than the collector depletion thickness directly under the emitter. The extrinsic C<sub>cb</sub> can then be reduced without increasing the collector transit time or decreasing the Kirk-effect-limited current density. Many aspects of silicon selective implantation in InP are examined, including implant energy and fluence, annealing conditions, dopant activation efficiency, as well as the implanted dopants' lateral distribution. MBE regrowth on implanted and subsequently processed templates is investigated. N-type sheet charge accumulation was discovered on the InP regrowth interface and the possible origins of the N-type sheet charges have been investigated. P-type counter-doping layer is introduced and successfully compensates the regrowth interfacial charges. Both DC and RF performance of pedestal HBTs are demonstrated and analyzed.

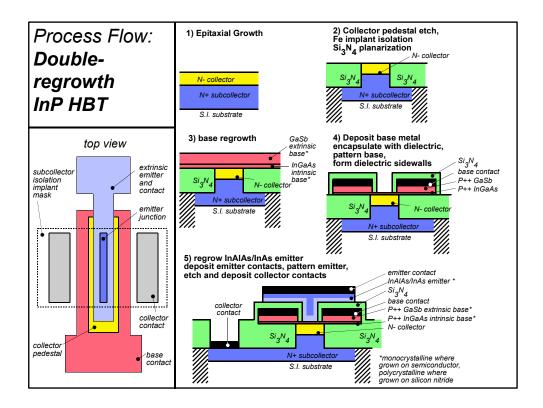

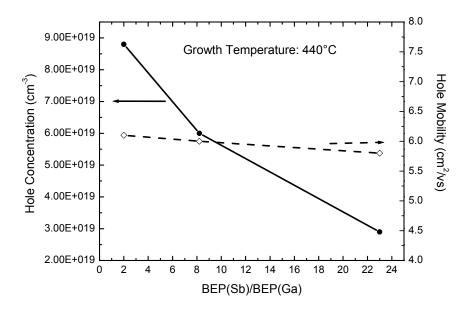

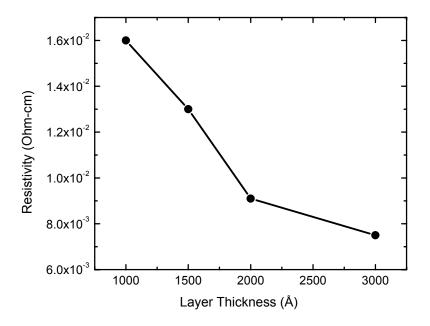

To combine the best features of SiGe and InP HBT technology, double-poly regrowth InP HBT is proposed. This HBT has structural features and process flow close to that of a Si/SiGe HBT, but uses InP-based materials. In Chapter 4, work on the development of double-poly HBT process, with a focus on the development of low resistance polycrystalline extrinsic base, are examined. In our efforts to find a low resistivity p-type polycrystalline material, the MBE growth and electrical properties of carbon-doped GaSb are thoroughly investigated. It has been found that with the same doping level, grain size and

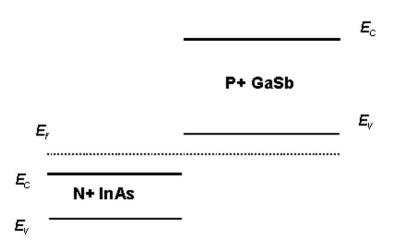

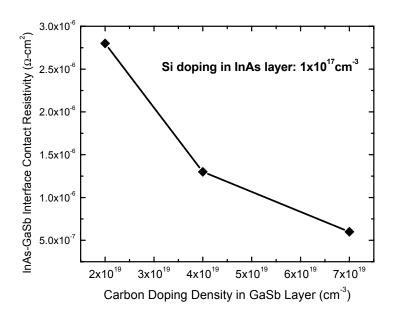

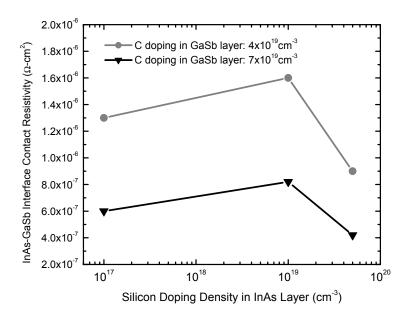

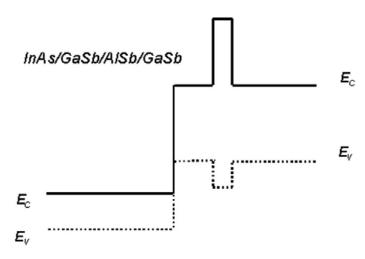

similar film thickness, the resistivity of poly-GaSb is more than one order of magnitude lower than that of poly-GaAs. This strongly suggests that poly-GaSb is an excellent candidate for the use as an extrinsic base material in InP HBTs. To further lower the resistivity of the polycrystalline extrinsic base layer, N-InAs/P-GaSb composite extrinsic base structure is proposed to exploit the very low bulk and metal contact resistivity of n-type polycrystalline InAs. The interfacial contact resistivity between n-type InAs and p-type GaSb layers, and its dependence on the doping densities on both sides of the heterostructure are also investigated.

Conclusions and suggested future work are presented in Chapter 5.

### References

- [1] H. Kroemer, 'Heterostructure bipolar transistors and integrated circuits', Proc. IEEE, Vol. 70, pp. 13-25, 1982

- [2] P. Asbeck, F. Chang, K.-C. Wang, G. Sullivan, and D. Cheung, 'GaAs-based heterojunction bipolar transistors for very high performance electronic circuits', Proc. IEEE, Vol. 81, pp. 1709-1726, 1993

- [3] M. Sokolich, D. P. Docter, Y. K. Brown, A. R. Kamer, J. F. Jensen, W. E. Stanchina, S. Thomas, III, C. H. Fields, D. A. Ahmari, M. Lui, R. Martinez, and J. Duvall, "A low power 52.9 GHz static frequency divider in a manufacturable 180 GHz AlInAs/InGaAs HBT IC technology," in Tech.Dig., IEEE GaAs IC Symp., Atlanta, GA, Nov. 1–4, pp. 117–120, 1998

- [4] D. C. Larson, "High speed direct digital synthesis techniques and applications," Tech. Dig., IEEE GaAs IC Symp., pp. 209–212, 1998

- [5] B. Agarwal, Q. Lee, R. Pullela, D. Mensa, J. Guthrie, and M.J.W. Rodwell, 'A transferred-substrate HBT wide-band differential amplifier to 50GHz', IEEE Microwave and Guided Wave Lett., Vol. 8, pp. 253-265, 1998

- [6] T. Mathew, H.-J. Kim, D. Scott, S. Jaganathan, S. Krishnan, Y. Wei, M. Urteaga, S. Long, and M.J.W. Rodwell, '75GHz ECL static frequency divider using InAlAs/InGaAs HBTs', Electronic Lett., Vol. 37, pp. 667-668, 2001

- [7] M. Dahlström, X.-M. Fang, D. Lubyshev, M. Urteaga, S. Krishnan, N. Parthasarathy, Y.M. Kim, Y. Wu, J.M. Fastenau, W.K. Liu, and M.J.W. Rodwell,

- 'Widebandgap DHBTs using a graded Carbon-Doped InGaAS Base', IEEE Electron Device Lett., Vol. 25, pp. 433-435, 2003

- [8] W. Hafez, J.-W. Lai, M. Feng, 'InP/InGaAs SHBTs with 75 nm collector and f/sub T/>500 GHz', Electronics Lett., Vol. 39, No. 20, pp.1475-6, 2003

- [9] Z. Griffith, M. Dahlström, M. Urteaga, M.J.W. Rodwell, X.-M. Fang, D. Lubyshev, Y. Wu, J.M. Fastenau, and W.K. Liu, 'InGaAs/InP mesa DHBTs with simultaneously high ft and fmax, and low Ccb/Ic ratio', submmitted to IEEE Electron Dev. Lett.

- [10] J. Song, M.R. Frei, J.R. Hayes, R. Bhat, and H.M. Cox, 'Self-aligned InAlAs/InGaAs heterojunction bipolar transistor with a buried subcollector grown by selective epitaxy', IEEE Electron Device Lett., Vol. 15, No. 4, pp. 123-125, 1994

- [11] M. Sokolich, M.Y. Chen, D.H. Chow, Y. Royter, S. Thomas III, C.H. Fields, D.A. Hitko, B. Shi, M. Montes, S.S. Bui, Y.K. Boegeman, A. Arthur, J. Duvall, R. Martinez, T. Hussain, R.D. Rajavel, K. Elliot, and J.D. Thompson, InP HBT integrated circuit technology with selectively implanted subcollector and regrown device layers, 25th IEEE GaAs IC Symposium, San Diego, CA, USA, Nov. 2003

- [12] K. Mochizuki, T. Tanoue, T. Oka, K. Ouchi, K. Hirata, and T. Nakamura, 'Highspeed InGaP/GaAs transistors with sidewall base contact structure', IEEE Electron Device Lett., Vol. 18, pp. 562-564, 1997

- [13] Y. Miyamoto, J.M.M. Rios, A.G. Dentai, S. Chandrasekhar, 'Reduction of base-collector capacitance by undercutting the collector in GaInAs/InP DHBTs', IEEE Electron Device Lett., Vol. 17, pp. 97-99, 1996

- [14] H.C. Tseng and Y.Z. Ye, 'High performance, graded-base AlGaAs/InGaAs collector-up heterojunction bipolar transistors using a novel selective area regrowth process', IEEE Electron Device Lett., Vol. 20, pp. 271-273, 1999

- [15] S. Yamahata, Y. Matsuoka, and T. Ishibashi, 'High fmax collector-up AlGaAs/GaAs heterojunction bipolar transistors with a heavily carbon-doped base fabricated using oxygen ion implantation', IEEE Electron Device Lett., Vol. 14, pp. 173-175, 1993

- [16] Q. Lee, B. Agarwal, R. Pullela, D. Mensa, J. Guthrie, L. Samoska, and M.J.W. Rodwell, 'A > 400 GHz fmax Transferred-Substrate Heterojunction Bipolar Transistor IC Technology', IEEE Electron Device Lett., Vol. 19 No. 3, pp. 77-79, 1997

# **Chapter 2**

# InP HBT with Extrinsic Base Laterally Overgrown on SiO<sub>2</sub>

### 2.1 Introduction

In InP heterojunction bipolar transistors (HBTs), the vertical layer optimization has led to very small intrinsic transit time. This has come about through the base and collector thinning as well as exploiting non-equilibrium carrier transport in the base and collector layers<sup>[1],[2],[3],[4]</sup>. It has hence become more important to reduce the parasitic elements such as series resistances and parasitic capacitances, which can limit the overall speed performance of HBTs. Among these parasitic elements, the base resistance ( $R_B$ ) and base-collector capacitance ( $R_B$ ) are the most critical.

Heavy doping in the base layer is an effective way to lower the base resistance. However, many related problems exist, such as reduced current gain

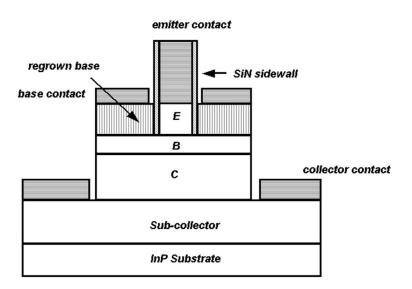

due to decreased emitter injection efficiency and higher base recombination<sup>[5]</sup>, lower device reliability, as well as dopant redistribution during epitaxial growth.<sup>[6]</sup> One promising way to avoid these difficulties is using heavily doped layer only in the extrinsic base region, since the extrinsic base resistance, including the base contact resistance, is usually the dominant part of the total base resistance. A selectively regrown extrinsic base structure is therefore effective in reducing the base resistance<sup>[7],[8]</sup>. In these regrown-base HBT structures, the extrinsic bases were heavily doped and were substantially thicker than the intrinsic base layer (Fig.2.1), and thus the extrinsic base resistance could be significantly reduced.

Fig.2.1 The schematic cross-section of the HBT with regrown-extrinsic base.

Although extrinsic base regrowth can effectively lower the base resistance, it cannot directly reduce the base-collector capacitance. It is therefore desirable to overgrow the heavily doped extrinsic base on buried SiO<sub>2</sub> surrounding the collector pedestal due to the low dielectric constant of SiO<sub>2</sub>, as illustrated in Fig.2.2. By doing this, simultaneous reduction of R<sub>B</sub> and C<sub>BC</sub> will become possible.

Polycrystalline extrinsic base regrown on buried SiO<sub>2</sub> have been applied to AlGaAs/GaAs HBTs by Mochizuki *et al.*<sup>[9]</sup> Polycrystalline materials, however, have much higher resistivity than single crystal materials<sup>[10],[11],[12]</sup>, since the carrier mobility in polycrystalline materials is usually one order of magnitude lower than that in crystalline materials with similar doping density. It is hence difficult to achieve low base resistance with polycrystalline materials. Single crystal extrinsic base overgrowth, on the other hand, can give much lower base sheet resistance and will be more effective in reducing the total base resistance.

The regrowth of single crystal extrinsic base on SiO<sub>2</sub> will be possible if large lateral overgrowth of InP/InGaAs materials can be realized. In this chapter, first selective growth of InP through SiO<sub>2</sub> openings by metal-organic chemical vapor deposition (MOCVD) is discussed and the dependence of lateral overgrowth on the opening width and orientation is presented and qualitatively explained. The lateral overgrowth technique is then applied to the fabrication of

regrown-base InP HBTs. Both DC and RF characteristics of the prototype devices are demonstrated.

Fig.2.2 The schematic cross-section of the HBT with extrinsic base overgrown on buried SiO<sub>2</sub>.

# 2.2 Epitaxial Techniques

# 2.2.1 Molecular Beam Epitaxy

Two growth techniques are pertinent to HBTs in this work. They are molecular beam epitaxy (MBE), the subject of this section, and metal-organic chemical vapor deposition (MOCVD), the subject of the next section.

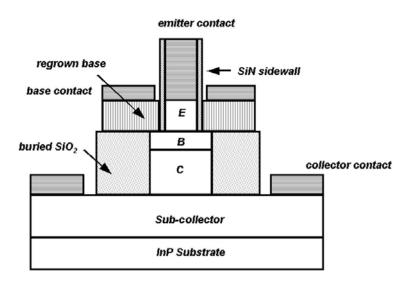

MBE is a growth technique by which a specific number of atomic layers can be precisely grown. It allows the growth of abrupt interfaces, both in material composition and in intentional impurity doping profiles. The epitaxial growth takes place in an ultra vacuum chamber whose base pressure is maintained at  $\sim 10^{-8}$  to  $10^{-10}$  torr. Fig.2.3 illustrates a schematic diagram of a high-vacuum MBE chamber.

Fig.2.3 Schematic diagram of a typical high-vacuum MBE chamber.

A total of typically eight effusion cells (also known as furnaces) containing different solid sources materials face the target substrate. A shutter is equipped on each diffusion cell. After the source material is heated to its melting temperature, it is emitted out of the effusion cell once the shutter is opened. Because the chamber is maintained at ultrahigh vacuum, the evaporated source molecules do not collide with each other but form a molecular beam that

impinges directly on the semiconductor substrate mounted on the heater. The high temperature promotes the movement (through diffusion) of the impinging molecules around the substrate surface, allowing them to arrange themselves into proper crystalline sites. Since the shutter's switching time is short compared to the growth time for a single atomic layer, the exact number of atomic layers to be grown is accurately controlled.

MBE growth takes advantage of the fact that Group V atoms impinging on the substrate surface immediately stick to the Group III atoms already present at the surface, until an atomic layer of Group V atoms is formed. Any additional Group V atoms that arrive after the formation of this atomic layer will not stick on the surface. This is not true for Group III atoms. If there are excess Group III atoms such as In atoms, the excess In atoms remain on the surface and eventually form an "In-rich" surface. The crystalline structure of InP is then lost. Therefore, a phosphorus overpressure is intentionally used during the growth of InP wherein both indium and phosphorus shutters are open. Since the adsorption of P atoms on a fresh In surface takes negligible time, the In flux determines the growth rate. The growth of InP results in successive completion of a layer of In, then a layer of P, as so on. The substrate for growth is normally in [100] orientation. In this direction, any particular single layer contains only either In or P atoms, consistent with the natural growth mechanism just described.

A calibration of growth rate can be done with a reflection-high-energy-diffraction (RHEED) assembly, which consists of an electron gun on one side of the chamber and a phosphorus screen on the opposite side. The RHEED intensity oscillates as monolayers of materials are grown. Each oscillation period indicates a completion of monolayer.

MBE growth at UCSB is done with computer-controlled furnace temperatures and shutter switching. The computer control allows reproducible growth of precise layer structures. Before each growth the flux of each source is measured with a beam flux monitor, which is located behind the substrate, as shown in Fig.2.3. The desired furnace temperatures are set in order to achieve the desired fluxes. This reduces the layer thickness error since as the source material is being consumed with time, the flux of a given source material changes for a specific furnace temperature.

# 2.2.2 Metal-Organic Chemical Vapor Deposition

The operation of MOCVD is more complicated than that of MBE, involving several complex chemical reactions. A basic chemical reaction in MOCVD is that between a metal-organic compound and a hydride. For example, when trimethyligallium vapor is mixed with arsine over a high-temperature substrate, GaAs is formed along with a gaseous by-product (methane)

$$(CH_3)_3Ga + AsH_3 \rightarrow GaAs + 3CH_4$$

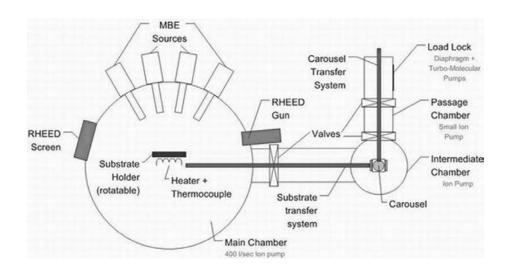

The substrate temperature in MOCVD is in the range of 550°C to 650°C. All constituents inside the growth chamber are in the vapor phase. A mass flow controller is used to regulate the gas slow and thereby control the growth rate. A horizontal MOCVD reactor is schematically shown in Fig.2.4.

Fig.2.4 Schematic diagram of a horizontal MOCVD reactor.

It is mentioned previously that in MBE growth, the P atoms impinging on the InP surface immediately stick to the InP atoms already there, until an atomic layer of P is formed. Having excess P fluxes ensures that MBE growth is determined solely by the In atom flux and prevents the growth surface from entering the In-enriched condition. Similarly, in MOCVD growth. The growth proceeds in an environment with excess PH<sub>3</sub>. The growth rate of InP within a

specified temperature range is limited by the diffusion of TMIn to the wafer surface and becomes linearly dependent on the TMIn concentration.

The usual p-type dopants include diethylzinc (DEZn), trimethylaresine (TMAs), and tetrachloride (CCl<sub>4</sub>). DEZn is the only p-type dopant available in the InP MOCVD system at UCSB. The zinc in DEZn is the element that actually dopes the semiconductor. Zinc, unlike carbon, has a relatively high diffusion coefficient, similar to Be used in MBE.

Just as in MBE, the preferred wafer orientation for MOCVD growth is along the [100] direction. In-situ growth monitors such as RHEED are not available in MOCVD. Calibration of the epitaxy growth rate in a MOCVD run typically requires wet etching of the calibration samples.

Many efforts have been made to investigate the feasibility to use MOCVD do selective growth in mask areas on GaAs or InP substrate. Compared with MOCVD, the selective growth by conventional MBE is very difficult due to the high sticking coefficient of Group III materials on the mask. Nevertheless, selectivity in MBE has been achieved by periodic supply molecular beam epitaxy (PSE/MBE)<sup>[13]</sup> and the lateral overgrowth has also been realized by using the low angle incidence microchannel epitaxy (LAIMCE) in MBE system.<sup>[14]</sup>

# 2.3 Epitaxial Lateral Overgrowth of InP on SiO<sub>2</sub>

#### 2.3.1 Overview

Almost all compound semiconductor devices consist of two or more of the suitable semiconductor layers grown on a substrate. A grown layer is refered to as an epitaxial layer if it has the same crystallographic lattice dimensions as the substrate. Usually the epitaxial layer is exactly lattice matched to the substrate, although layers with the deviation of their lattice parameters as large as 0.05% are generally refered to as lattice matched. A large lattice mismatch induces stress, which in turn causes strain especially in the grown layers. This leads to the generation of defects at the interface that can be mobile enough to reach the surface.

In standard definition, heteroepitaxy denotes the epitaxial growth of a material that is different from the substrate on which it is grown. E.g., epitaxy of In<sub>0.53</sub>Ga<sub>0.47</sub>As on InP is considered as heteroepitaxy since they are lattice matched but chemically different. Today the term heteroepitaxy is often instead employed to denote the growth of a material whose lattice parameter differs from that of the substrate, e.g. GaN on sapphire, InP on GaAs, InP on SiO<sub>2</sub> etc.

In heteroepitaxy one would expect material growth with high defect density. However, several defect-engineering approaches have been taken to suppress those defects. These include: 1) Growth of very thick layers – in this case the grown layer is sufficiently thick that the defects generated at the interface do not

propagate up to the surface and hence a part of the layer at the top is free of defects. 2) Epitaxial lateral overgrowth – in this case, the growth starts on the open surface, and when the layer reaches a particular thickness, the layer starts to grow laterally from the opening on the masked region. 3) Compliant substrate – compliant substrates offer a new approach to strain management in lattice-mismatched structures. The role of the compliant substrate is to reduce the strain in a mismatched overlayer by sharing the strain via deformation of the substrate, or by nucleating and confining defects in the substrate. This is done either by direct bonding or twist bonding of an appropriate layer on a substrate. In our work, the epitaxial lateral overgrowth approach has been adopted to grow InP on SiO<sub>2</sub>. The lattice mismatching in this system is ~8%.

Epitaxial lateral overgrowth has been studied and applied to various devices<sup>[15],[16],[17],[18],[19],[20],[21]</sup>. Selective area growth of InP and related materials is gaining importance in the fabrication of several advanced optoelectronic devices. However, few attempts have been made to investigate the selective growth of InP with a focus on fabricating electronic devices.

In our efforts to laterally overgrow an InP HBT's extrinsic base on buried SiO<sub>2</sub> layer, the seed area for the base lateral overgrowth is limited by the HBT's scaling requirements: the extrinsic base regrowth seed area needs to be narrower than normal base metal contact width for effective base-collector capacitance

reduction. For this reason, our studies on the InP lateral overgrowth are focused on the growth through very narrow seed area (less than 1µm wide).

Since the UCSB InP MOCVD system's susceptor rotational speed was only 200 rpm, the selective area growth of InGaAs is difficult. With low susceptor rotational speed, the gas-flow speed just above the susceptor is slow due to the smaller centrifugal force generated by the low-speed rotation. Therefore, the residence time of the material molecules adjacent to the susceptor is longer. This position also has the highest temperature in the gas phase. As a result, the pyrolysis of the source molecules in the gas phase is less restrained, which leads to low growth selectivity. Initial tests showed that many polycrystalline InGaAs particles were deposited on the SiO<sub>2</sub> regrowth mask even when high growth temperature was used. Selective growth tests of InP were much more successful. With InP growth, very few polycrystalline particles were found on the SiO<sub>2</sub> mask after the regrowth. This clean regrowth was mainly due to the higher mobility of In atoms than Ga atoms. To obtain better regrowth selectivity, InP was therefore selected to be the majority of the laterally regrown base. For the same reason, most of the selective growth experiments in this thesis use InP.

# 2.3.2 Crystallographic Structures of Zinc Blende

Knowledge of the crystallographic structure of semiconductor is essential for understanding the process of epitaxy during the lateral overgrowth. InP

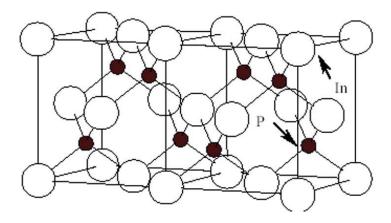

crystallizes in a zinc blende (sphalerite) lattice. The zinc blende structure consists of two interpenetrating, face centered cubic (fcc) sublattices consisting of only indium and phosphorous atoms in each sublattice. Each sublattice is shifted by a/4 [111] relative to the other fcc sublattice, where a is the length of the fcc lattice constant. The zinc blende structure of InP is shown in Fig.2.5, where open circles are indium atoms and solid circles are the phosphorus atoms.

Fig.2.5 Schematics of InP lattice structure.

The most common surface used for the growth of III-V's on InP and GaAs is (100). The {100}, {011}, and {111} basic planes in III-V compounds are of particular interest. The properties of these surfaces strongly influence III-V semiconductor growth. Other surfaces with higher Miller indices can be resolved on an atomic scale into stepped structures built up from combinations

of these three basic set of planes. Knowledge on the properties of these basic planes will facilitate the understanding of InP's lateral overgrowth behavior.

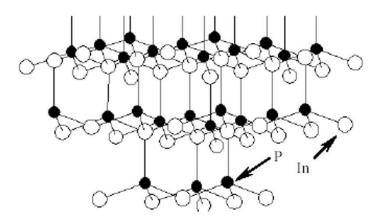

An ideal {100} plane is shown in Fig.2.6. It consists of alternating planes of indium and phosphorus atoms. The indium and phosphorus planes are geometrically equivalent and are equally spaced. Each In (P) atom in In (P) plane is bonded downward into the crystal to two P (In) atoms. Under typical growth conditions in MOCVD system, where V/III ratio is larger than unity, the growth can be treated as indium incorporation limited, since under the condition of excess PH<sub>3</sub>, total adsorption of phosphorus atoms takes place readily. The growth on {100} plane can be seen as layer-by-layer growth, and there is no substantial nucleation barrier for crystal growth on {100} planes.

Fig.2.6 Atomic structure of {100} planes in InP crystal.

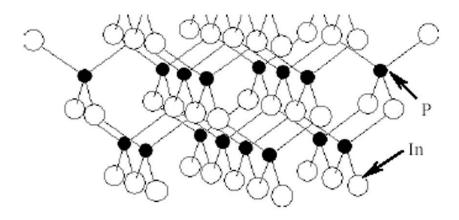

The atomic structure of the {011} planes is shown in Fig.2.7. The {011} planes contain equal number of In and P atoms. The atoms in {011} planes form zigzag chains, each atom being bonded to two adjacent atoms in the chain, with its other two bonds extending out on each side to the remaining tetragonal position. It can be difficult to nucleate growth of new atomic planes on {011} facets because incorporating each new indium atom can add two dangling bonds. Here the addition of indium atoms can be considered to control the growth, since under the conditions of excess PH<sub>3</sub>, total adsorption of phosphorous atoms takes place readily. Once the first atom is in place, atoms of the opposite type can be deposited adjacent to it without adding the dangling bonds.

Fig.2.7 Atomic structure of {011} planes in InP crystal.

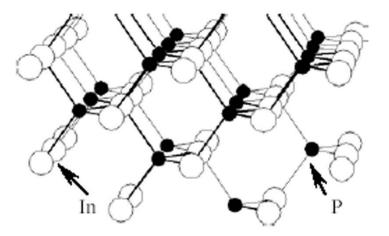

The structure of {111} planes is shown in Fig.2.8. This family of planes is significant for understanding the growth profile in the epitaxial lateral overgrowth of InP. The {111} double layer contains two closely spaced planes of In and P atoms which are denoted as {111}A and B planes, respectively. Each atom in a given plane has three bonds to atoms in the other plane. The fourth bond extends normal to the plane of the double layer to connect to an atom in the next such double layer. Since the two sides of the {111} layer are not chemically equivalent, a crystal bounded by such facets would be expected to show phosphorus polarization effects during the selective growth. Growth on {111}B planes is lethargic in a phosphorus rich vapor ambient, because further attachment of In atoms at {111}B planes will add two dangling bonds. It means that In atoms have to overcome high energy barrier in order to deposit on {111}B planes.

Fig.2.8 Atomic structure of {111} planes in InP crystal.

## 2.3.3 InP Lateral Overgrowth Experiments and Results

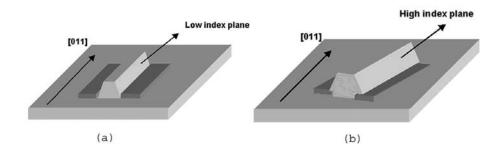

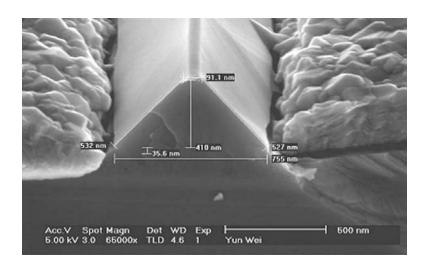

In our initial regrowth experiments, the regrown material showed strong faceting when the openings were aligned to the [011] direction, the direction along which the InP HBT emitters are usually aligned. It was observed that the growth facets were bounded by (1-11)B and (11-1)B planes and formed a pyramidal shape without any lateral overgrowth on SiO<sub>2</sub>. These behaviors strongly suggested that the lateral overgrowth had significant orientation dependence.

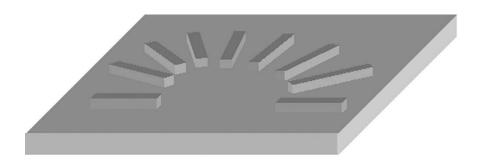

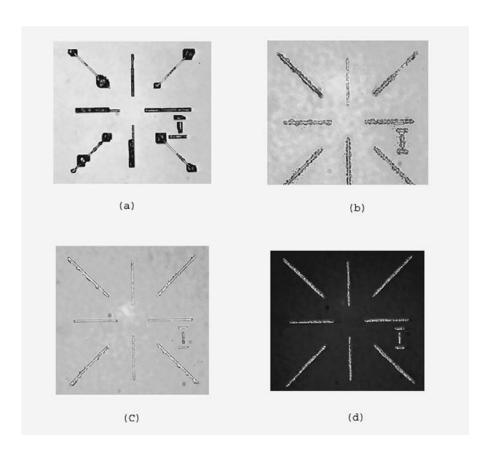

To investigate the lateral overgrowth's orientation dependence, test patterns of SiO<sub>2</sub> opening stripes at various rotations were used, as illustrated in Fig.2.9.

Fig.2.9 Schematic of growth angle patterns of SiO<sub>2</sub> stripes.

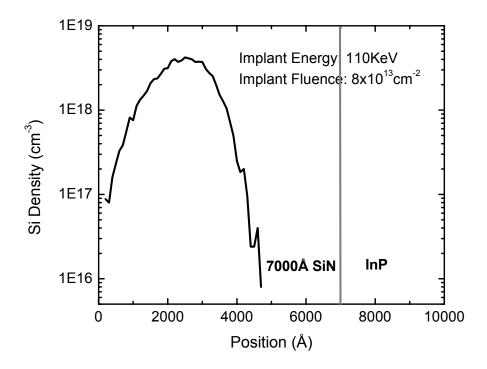

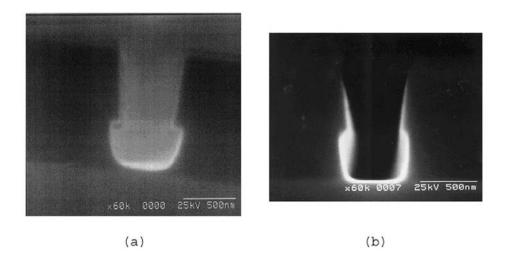

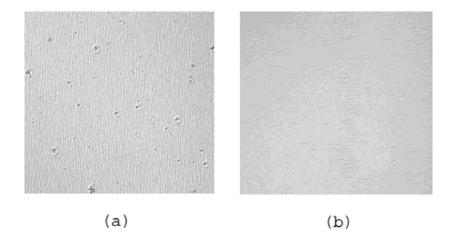

Growth experiments were performed using this pattern. First, radial stripes of  $SiO_2$  mesa stripes were formed on (100) InP substrate by plasma-enhanced chemical vapor deposition (PECVD) and subsequent reactive ion etching (RIE) with  $SF_6/Ar$  gases. The central mesa stripe in the test pattern was aligned perpendicular to the major flat. The mesas were  $0.8~\mu m$  tall,  $2~\mu m$  wide and were indexed at  $5^\circ$  intervals. A thin layer of  $SiO_2$  regrowth mask (1000Å) was then deposited and lifted-off on both sides of the tall  $SiO_2$  mesa. The opening width between the central mesa and regrowth mask was varied from 0.5 to  $4~\mu m$ . The central  $SiO_2$  mesa is designed to emulate the tall emitter mesa of an InP HBT, while the thin  $SiO_2$  regrowth mask emulates the buried  $SiO_2$  layer which would surround the collector pedestal. Projection lithography patterned the radiant stripes and the alignment accuracy between the tall  $SiO_2$  mesa and thin  $SiO_2$  regrowth mask was within  $\pm 0.1~\mu m$ .

The selective growth of InP was performed in a horizontal MOCVD reactor at 350 torr using trimethylindium and tertiarybutylphosphine as source materials. First 250 Å InP was grown at 550°C with V/III ratio of 100, then 2250Å InP was grown at 615°C with V/III ratio of 50. The first 250 Å InP layer was grown at a low temperature with high V/III ratio to help initiate the growth in the openings. It was found that the growth of this thin layer under such conditions helped improve the quality of the subsequent selective growth. Since our MOCVD system's susceptor rotational speed was only 200 rpm, relatively high growth

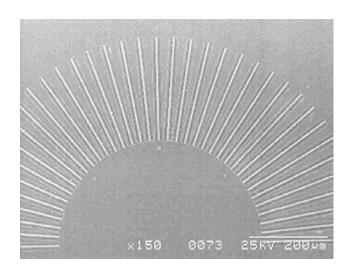

temperature (> 600°C) was chosen for the rest of the selective growth to suppress the generation of polycrystalline particles on the mask. Fig.2.10 shows the top view of the sample after growth.

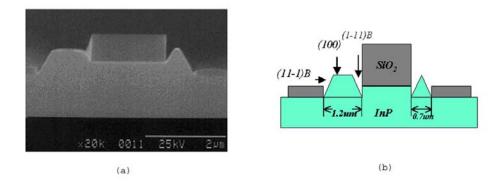

The sample was cleaved along [01-1] direction after growth. The scanning electron micrograph (SEM) image in Fig.2.11(a) shows the cross-section of the InP deposits grown through stripe openings aligned to [011] direction. As illustrated in Fig.2.11(b), the growth facets in Fig.2.11(a) are bounded by the low index planes: (100), (1-11)B and (11-1)B without any obvious overgrowth of InP on the SiO2 mask.

Fig.2.10 SEM image of the selective growth through the radial line openings on an InP substrate.

Fig.2.11 (a) SEM cross-section image the selective growth through opening along [011] direction. (b) Schematic of growth through [011] oriented opening.

Fig.2.12 shows the SEM cross-section image of the deposit through an opening aligned 30° from the [011] direction. Although the thin SiO<sub>2</sub> mask cannot be seen clearly, the width of the InP deposit through the opening is clearly larger than the opening width (0.5μm). This shows that there is lateral growth of InP over the SiO<sub>2</sub> mask even though no nucleation site exists on SiO<sub>2</sub>. From Fig.2.12 it is also clear that the boundary planes of the regrown InP are no longer {111}B planes.

Fig.2.12 SEM cross-section image of the selective growth through a 0.5 $\mu$ m opening 30° off [011] direction.

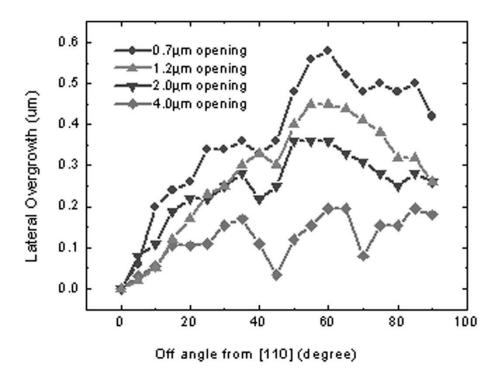

In order to systematically investigate the lateral overgrowth's orientation dependence, the lateral overgrowth length was measured at 5° intervals using SEM. The data, plotted as a function of the opening's orientation and width, is shown in Fig.2.13. The lateral overgrowth length, as expected, has strong dependence on opening orientation, with minima occurring at the major low-index directions: [001], [011] and [01-1]. This growth behavior agrees well with that reported for selective growth of thick InP through wide openings by HVPE<sup>[22]</sup>.

Fig.2.13 Dependence of lateral overgrowth length on opening orientation and width.

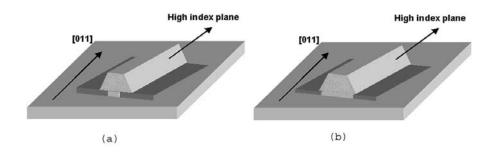

From Fig.2.13 it is also seen that the lateral overgrowth length increases with decreasing opening width. At  $60^{\circ}$  orientation of [110], the lateral overgrowth length through the  $0.7~\mu m$  wide opening is almost  $0.6~\mu m$ , while the lateral overgrowth length through the  $4\mu m$  wide opening is less than  $0.2~\mu m$ . Similar lateral overgrowth experiments were also performed on InGaAs surfaces. Very similar behaviors have been observed.

# 2.3.4 Qualitative Explanations for Lateral Overgrowth Behaviors

The dependence of lateral growth on mask opening width and orientation can be qualitatively explained by the Burton-Cabrera-Frank (BCF) growth model<sup>[23]</sup>. When the stripe opening is rotated away from the low index directions, as illustrated in Fig.2.14, the growth boundaries become high-index vicinal planes, which have high density of steps at the growth front over the SiO<sub>2</sub> mask. These crystallographic steps on boundary plane can supply the seed for continuous lateral growth over the SiO<sub>2</sub> mask, although there is no nucleation site on the mask. The high step density on the vicinal sidewall surface therefore increases the lateral growth rate if the mass transport rate from the gas phase is fast enough to support it.

Fig.2.14 Schematics of regrowth when the opening is (a) along [011] direction and (b) away from [011] direction.

The dependence of lateral overgrowth on mask opening width can be similarly explained. Through narrow openings, the vertical growth requires less mass transport. As a result, this allows more of the material arriving on the top surface and the mask area to migrate to the sidewall and be incorporated in the sidewall growth. As illustrated in Fig.2.15, this can result in increased lateral overgrowth on the SiO<sub>2</sub> mask.

Fig.2.15 Schematics of regrowth with (a) narrow and (b) wide opening aligned away from [011] direction.

# 2.4 InP HBT with Laterally Overgrown Base on Buried SiO<sub>2</sub>

As discussed earlier, for HBTs with a laterally overgrown extrinsic base it is desirable to keep the regrowth window between the emitter mesa and the buried SiO<sub>2</sub> as narrow as possible to reduce the base collector capacitance. Considering

this, the following device structure for extrinsic base regrowth was proposed. As shown in Fig.2.2, the base mesa can be etched down to the subcollector, leaving a narrow base shoulder. SiO<sub>2</sub> can then be deposited to surround the collector pedestal. This defines an intrinsic base-collector junction area only slightly larger than the emitter-base junction area, this bringing a significantly reduced C<sub>BC</sub>. The base shoulder also provides a narrow opening for the subsequent selective growth to facilitate the lateral overgrowth of the extrinsic base. To obtain the largest lateral overgrowth length for the extrinsic base, the emitter stripes can be aligned 60° off [011] direction.

The following sections discuss the growth and process steps used to realize this device structure.

#### 2.4.1 Intrinsic HBT Material Structure and Growth

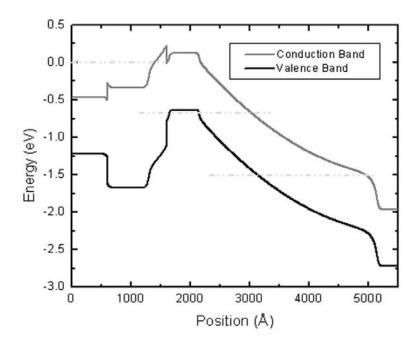

The intrinsic HBT structure was grown on a Fe-doped semi-insulating (100) InP substrate using solid-source MBE. The layer structure is listed in Table 2.1.

Since the base lateral regrowth process was still under heavy investigation and far from mature, a relatively simple HBT layer structure was adopted to avoid complicating the device fabrication to facilitate problem shooting.

The InGaAs base used in this structure was 550 Å thick, and was Be-doped at  $4x10^{19}$  cm<sup>-3</sup>. The top 50 Å InGaAs was undoped to alleviate the diffusion of

Be dopants into the emitter. From the hall measurements on the doping calibration samples, the hole mobility in the base layer was 55 cm<sup>2</sup>/VS.

| Layer        | Material  | Thickness (Å) | Doping (cm <sup>-3</sup> ) |

|--------------|-----------|---------------|----------------------------|

| Cap          | n+ InGaAs | 600           | Si: 2x10 <sup>19</sup>     |

| Emitter      | n+ InP    | 300           | Si: 2x10 <sup>19</sup>     |

|              | nInP      | 700           | Si: 2x10 <sup>17</sup>     |

| Base         | InG aAs   | 50            | Undoped                    |

|              | p+InGaAs  | 500           | Be: 4x10 <sup>19</sup>     |

| Collector    | n-InGaAs  | 3000          | Si: 1x10 <sup>14</sup>     |

| Subcollector | n+ InGaAs | 4000          | Si: 2x10 <sup>19</sup>     |

Table 2.1 Epitaxial layer parameters of the intrinsic HBT region.

The InGaAs emitter cap was N+ doped with Si at  $2x10^{19}$ cm<sup>-3</sup>, and 600 Å thick. The InP emitter was 1000 Å thick with the first 700 Å Si-doped at  $3x10^{17}$ cm<sup>-3</sup> and the remainder doped at  $1x10^{19}$  cm<sup>-3</sup>. The InGaAs collector was 3000Å thick and doped with Si at  $1x10^{16}$  cm<sup>-3</sup>. The N+ InGaAs subcollector was heavily doped at  $2x10^{19}$  cm<sup>-3</sup> to achieve low collector access resistance. Fig.2.16 shows the band diagram associated with the HBT layer structure under forward

bias. The bias conditions are: emitter-base voltage  $V_{BE}$  = 0.7 V, emitter-collector voltage  $V_{CE}$  = 1.5 V.

Fig.2.16 The band diagram of the HBT's layer structure under forward bias.

## 2.4.2 HBT Fabrication Process

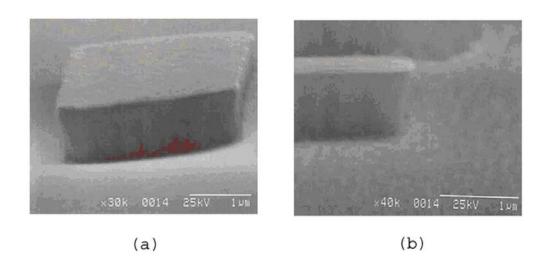

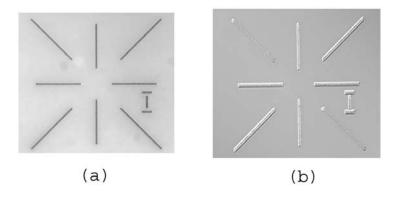

After the MBE epitaxial growth, tungsten was used as refractory emitter electrode by RF sputtering and subsequent reactive ion etching (RIE) with SF<sub>6</sub>:Ar gases. The tungsten thickness was 1.0  $\mu$ m. A 400 Å Ni layer was deposited and lifted-off on the tungsten layer to be used as the etching mask.

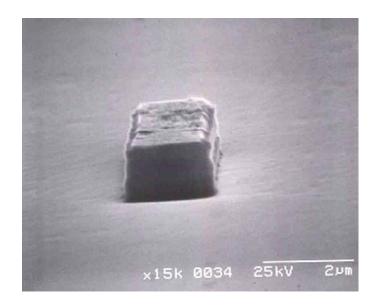

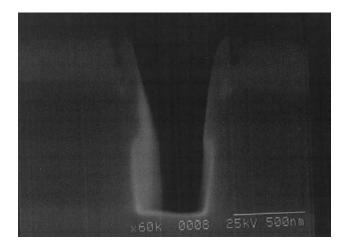

Relatively low gas pressure ( $10m\tau$ ) and high bias voltage (300V) were used during the tungsten RIE to reduce the etch undercut. From Fig.2.17 it can be seen that the tungsten emitter metal undercut was controlled within  $0.1\mu m$ .

Fig.2.17 SEM pictures of the emitter lateral profiles after tungsten dry etch.

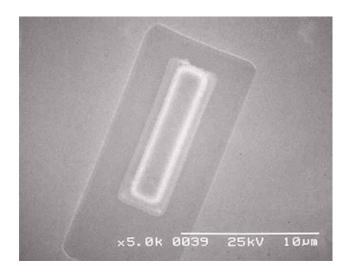

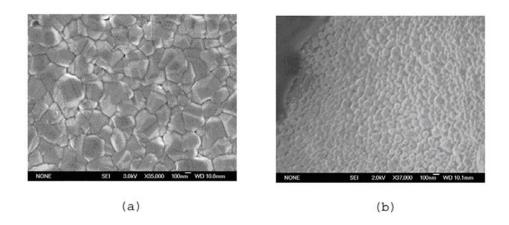

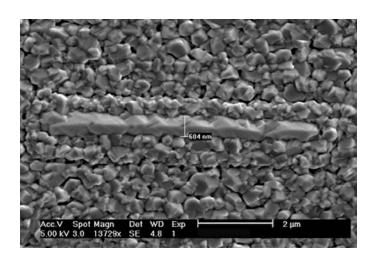

After the tungsten dry etch, the InGaAs emitter cap and InP emitter layers were wet etched and a SiN sidewall was formed around the emitter electrode and emitter layers to prevent short between regrown extrinsic base and emitter. The sidewall was formed by SiN PECVD deposition and subsequent reactive ion etching. Fig.2.18 shows the SEM picture of an emitter mesa covered by SiN sidewall.

Fig.2.18 SEM picture of an emitter mesa after SiN sidewall formation.

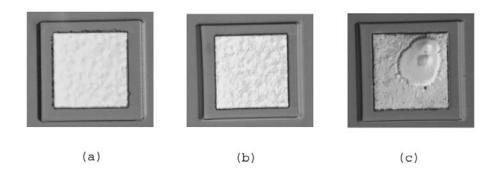

After the emitter sidewall formation, lithography was performed and the emitter was covered by photoresist 0.6 µm wider than the emitter mesa on both sides. The base mesa was then reactive-ion etched down to the subcollector. Following this 3500 Å SiO<sub>2</sub> regrowth mask was deposited by electron beam deposition and then lifted-off. A narrow base opening (the extrinsic base regrowth seed area) between the emitter mesa and the SiO<sub>2</sub> mask was therefore formed. The edge profile around the base opening was measured and the refilled SiO<sub>2</sub> surface was found to be smooth and aligned with the base opening surface very well. The height difference between the SiO<sub>2</sub> surface and the base opening

surface was within 200 Å. Fig.2.19 shows the SEM top view of a device after buried SiO<sub>2</sub> was deposited and lifted-off.

Fig.2.19 SEM top view picture of a device after buried SiO<sub>2</sub> deposition and liftoff.

The base selective regrowth was subsequently performed and the regrown layers consisted of a 250 Å InP layer grown at 550°C with a V/III ratio of 100, a 1500 Å InP layer grown at 615°C with a V/III ratio of 50 and a 250 Å InGaAs layer grown at 615°C. This extrinsic base was heavily doped with Zn to achieve low extrinsic base resistance. The extrinsic base's lateral overgrowth length was found to be  $\sim 0.5 \mu m$ , which was comparable to the result of a lateral overgrowth experiment using a  $0.7 \mu m$  mask opening oriented 60° from the [011] direction (Fig.2.13).

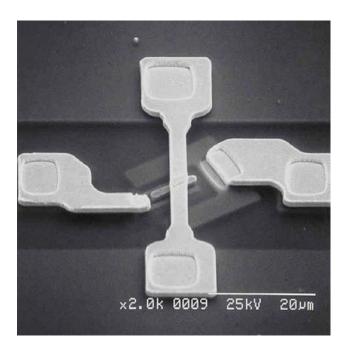

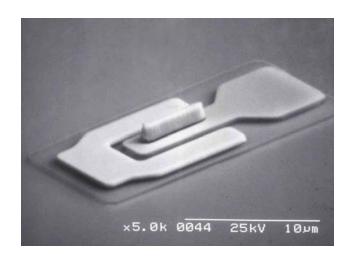

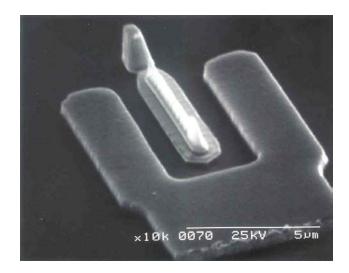

After forming Pd/Ti/Pd/Au base electrodes using the liftoff technique, the base collector mesa was formed by wet etching. The collector electrode of Ti/Pt/Au was then deposited, and finally the HBTs were isolated by wet etching down to the semi-insulating substrate. After passivating the device with polyimide and making contact holes through it, pad metals (Ti/Au) were fabricated by liftoff. The transmission line was aligned along the major flat direction, while the emitters were rotated 60° away from [011] direction. Fig.2.20 shows a SEM picture of the finished device.

Fig.2.20 SEM picture of the finished HBT with lateral base regrowth.

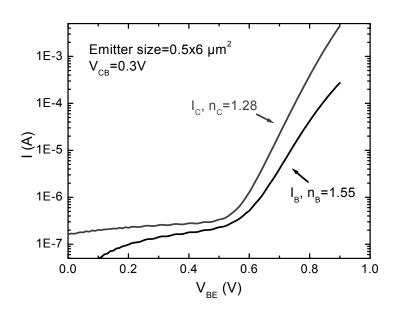

### 2.4.3 DC Measurements of the Regrown Base HBTs

DC characterization includes Gummel plots and DC common-emitter characteristics. These were measured by a semiconductor parameter analyzer using microwave probes, bias-T, and  $50\Omega$  transmission lines to prevent microwave device oscillation during DC measurements.

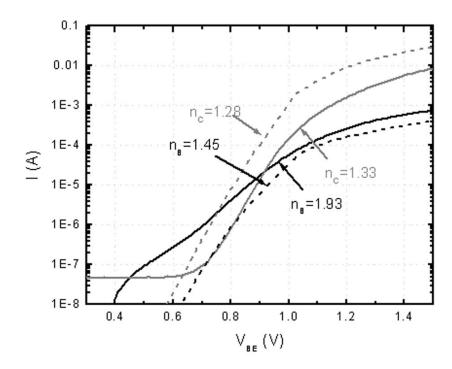

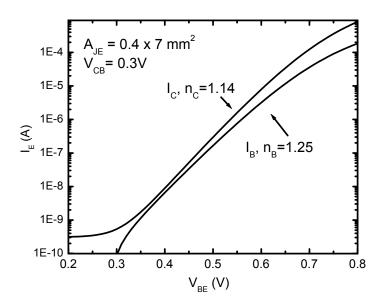

Shown in Fig.2.21 are the Gummel plots of a regrown-base HBT and a conventional HBT with the same layer structure and junction dimensions. Both HBTs have  $1x10~\mu m^2$  emitter area. The base and collector current ideality factors of the regrown-base HBT are 1.93 and 1.33, while the ideality factors of the conventional HBT are 1.45 and 1.28. When  $V_{CE}$  is 1.5V, the DC current gain is 15 for the regrown-base HBT and 48 for the conventional HBT

The large recombination current resulted in the low current gain and high base-current ideality factor for the regrown-base HBT. The origin of this excess base current at low current density could be attributed to the process-induced surface damages of the p-InGaAs prior to the regrowth, particularly the damages caused by the RIE etch during the SiN sidewall formation, and the interface degradation during the regrowth.

Fig.2.21 Gummel plots of the regrown-base HBT (solid line) and the conventional HBT (dashed line) with the emitter size of  $1x10~\mu m^2$ .

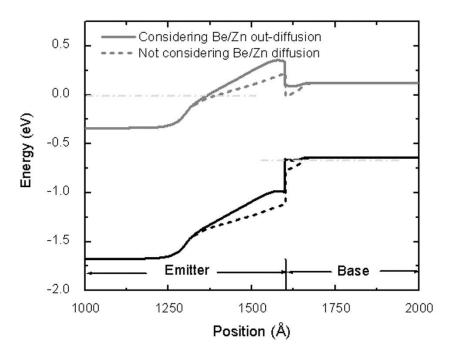

From the Gummel plots it was also found that  $V_{be}$  at a given  $I_C$  is  $\sim 100 \text{mV}$  larger for the regrown-base HBT. This larger turn-on voltage could be attributed to the Be and Zn out-diffusing into the emitter-base setback layer during the selective regrowth. To qualitatively estimate the influence of the Zn diffusion on the turn-on voltage, we numerically calculated the band diagrams using the simulation tool Bandprof. The results are shown in Fig.2.22. Our band diagram simulation was based on the assumption that Be and Zn atoms diffused into InP emitter layer and caused the 50 Å emitter layer immediately above the

emitter-base junction to become p-doped at  $1x10^{17} cm^{-3}$ . It is clear from Fig.2.22 that p-type dopant diffusion can induce an increase in the emitter-base conduction band potential barrier, which can explain the regrown base HBT 's increased  $V_{be}$ . To suppress this p-type dopant out-diffusion, the use less diffusive dopants for the intrinsic base layer, such as carbon, would be effective. More importantly, the setback layer could be eliminated if diffusive dopants are avoided.

Fig.2.22 Band diagram of emitter-base junction with and without considering the p-type dopant diffusion during the base regrowth.

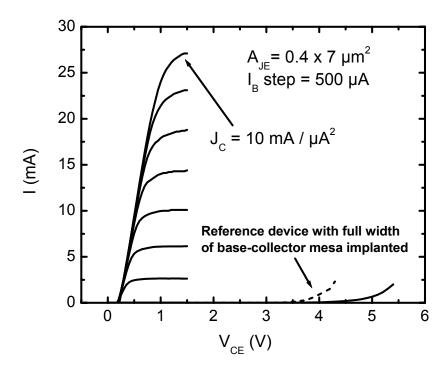

The common-emitter characteristics of the same regrown-base HBT are shown in Fig.2.23. It can be seen that the  $V_{CE}$  offset voltage is relatively high. This could be attributed to the device's single-heterojunction structure, abrupt emitter-base junction, as well as the larger base-emitter turn-on voltage caused by the p-type dopant out-diffusion.

Fig.2.23 Common-emitter characteristics for 1x10 μm<sup>2</sup> device.

# 2.4.4 RF Measurements of the Regrown Base HBTs

The microwave performance of the HBT was characterized by measuring S-parameters with on-wafer probing from 0.5 to 40 GHz. The total base-collector

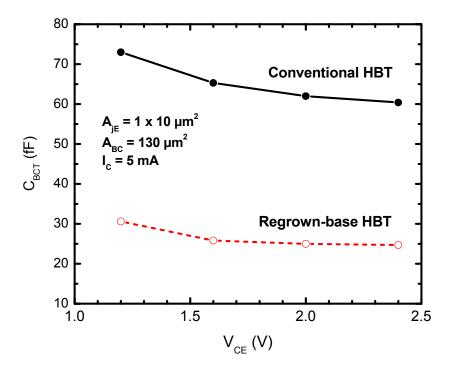

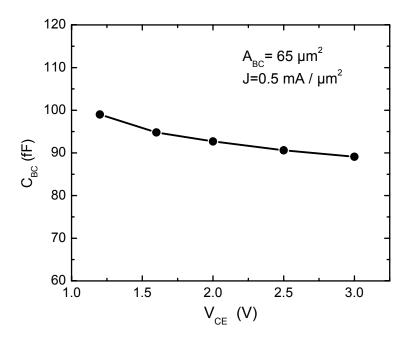

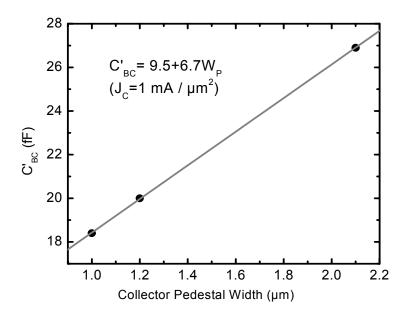

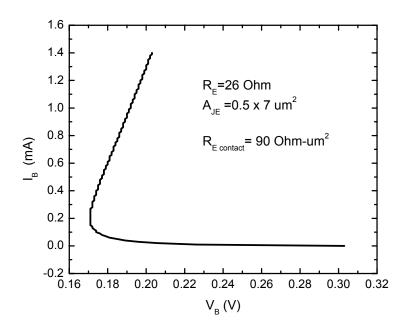

capacitance ( $C_{BC}$ ) was calculated from the imaginary part of the 2 port parameter  $Y_{12}$ . Fig.2.24 shows the measured  $C_{BC}$  as a function of  $V_{CE}$  at  $I_{C}$ =10mA. For the regrown-base HBT with 1x10  $\mu$ m<sup>2</sup> emitter size and 130  $\mu$ m<sup>2</sup> base-collector junction area, the value of  $C_{BC}$  saturated at the high voltage is 25fF. For conventional HBTs,  $C_{BC}$  was found to saturate at 60fF at the same current. Clearly a 60% reduction of  $C_{BC}$  has been achieved by reducing the base-collector junction width and overgrowing the extrinsic base on buried SiO<sub>2</sub>.

Fig.2.24 Bias dependence of the total base-collector capacitance of conventional and regrown-base HBTs.

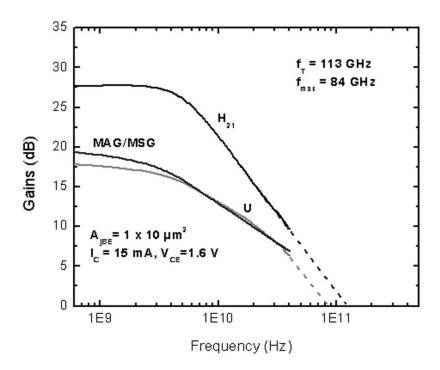

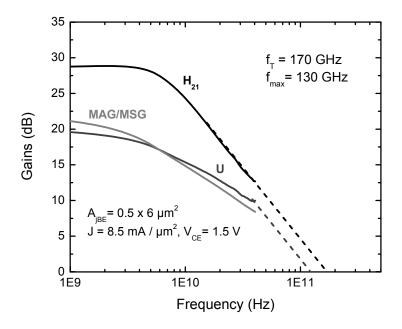

Fig. 2.25 shows the frequency-dependence of the current gain and Mason's unilateral gain for a 1x10  $\mu$ m<sup>2</sup> HBT with regrown base at I<sub>C</sub> = 10mA and V<sub>CE</sub> = 1.5V. The cutoff frequencies  $f_T = 113GHz$  and  $f_{max} = 84GHz$  were obtained through assuming a -20 dB/decade frequency-dependence of current gain and unilateral gain. At the same current and collector bias,  $f_T = 115 \text{GHz}$  and  $f_{\text{max}} =$ 95GHz were measured for the conventional HBT without base regrowth. It can be seen that the f<sub>T</sub> values for conventional and regrown-base HBTs are very close, while regrown-base HBT's f<sub>max</sub> is ~10% lower than conventional HBT's in spite of regrown-base HBT's significantly reduced base-collector capacitance. The f<sub>max</sub> value of the regrown-base HBT is mainly limited by its large base contact resistance. Table 2.2 lists the base sheet and contact resistivity values of both regrown and conventional HBTs from the transmission line model (TLM) analysis. As expected, the base regrowth significantly reduces the extrinsic base's sheet resistance. However, the contact resistivity on the regrown extrinsic base is much higher than that on the intrinsic base. This was caused by the low maximum p-level attainable with MOCVD when using Zn as acceptor dopant at relatively high growth temperature. In our regrown extrinsic base the p-type doping density was only 1x10<sup>19</sup>cm<sup>-3</sup>, which was obviously not high enough to achieve low base contact resistance. Due to the susceptor rotational speed limit of our MOCVD system, the growth temperature cannot be further lowered. Otherwise the selectivity of the base regrowth would be significantly reduced.

Under this circumstance, to obtain higher p-doping in the extrinsic base, especially near the extrinsic base surface, post-growth Zn diffusion can be a very effective and controllable technique<sup>[24]</sup>. Improved microwave performance is expected if post-growth Zn diffusion can be successfully applied to our base regrowth process.

Fig.2.25 Frequency dependence of current gain( $H_{21}$ ), Mason's unilateral gain(U) and maximum stable gain/maximum available gain (MSG/MAG) at Ic=10mA,  $V_{\text{CE}}$ =1.6V.

|                  | Sheet Resistance (Ω/□) | Contact Resistivity (Ω-cm²) |

|------------------|------------------------|-----------------------------|

| Conventional HBT | 550                    | 9.0x10 <sup>-7</sup>        |

| Regrown-base HBT | 340                    | 1.5x10 <sup>-5</sup>        |

Table 2.2TLM measurement results from the base layers of conventional and regrown-base HBTs.

# 2.5 Summary

To realize the InP HBT with extrinsic base laterally overgrown on buried SiO<sub>2</sub> for the simultaneous reduction of base-collector capacitance and base resistance, we have investigated the selective growth of InP by MOCVD through narrow mask openings by MOCVD. It is found that the lateral overgrowth of InP on SiO<sub>2</sub> is strongly dependent on both the opening width and orientation. The lateral overgrowth length reached the maximum at 60° off [011] direction and the minima along the major low index directions. The lateral

overgrowth also showed a increasing overgrowth length increasing with decreasing mask opening width.

Based on these results, HBTs employing extrinsic base laterally overgrown on buried  $SiO_2$  were fabricated. Emitters were aligned  $60^\circ$  off [011] direction to obtain the maximum lateral overgrowth length for the extrinsic base. The regrown-base HBTs exhibit acceptable DC performances with current gain  $\sim$ 15. Lower base recombination current and higher current gain can be expected after further efforts are made to improve the selective growth quality as to minimize e process related damage and contamination.

RF measurements demonstrate  $\sim 60\%$  base-collector capacitance reduction compared with conventional HBTs with the same layer structure and device layout.  $f_{max}$  of regrown base HBTs is lower than expected due to the high base contact resistance caused by the low Zn doping density in the extrinsic base, even though the extrinsic base sheet resistance is reduced through regrowth.

To substantially improve regrown-base HBT's bandwidth, a more advanced MOCVD system is necessary. If susceptor's rotational speed can be mechanically controlled and reach 1000 rpm, we will be able to use much lower temperature for the base regrowth. Significantly higher Zn doping density can then be obtained in the extrinsic base without compromising the regrowth selectivity. In addition, with higher susceptor rotational speed and better regrowth selectivity, InGaAs can be used as the extrinsic base material with

carbon doping. This can ultimately avoid the Zn doping limit problem in InP and provide much lower base resistance.

In our proto-type device demonstrations simple device layout and lay structure designs were adopted to minimize the device processing and fabrication difficulties, and they were far from mature. Significant improvements in regrown-base HBTs' performance can also be expected after further optimizing the device designs

#### References

- [1] H. Nakajima, 'Design and fabrication of high-speed InP-based heterojunction bipolar transistors', IEEE Proc. of the 5th International InP and Related Materials Conf., pp. 13-16, 1993

- [2] M. Ida, K. Kurishma, and N. Watanabe, 'Over 300GHz fT and fMAX InP/InGaAs double heterojunction bipolar transistors with a thin pseudomorphic base', IEEE Electron Device Lett., Vol. 23, pp. 694-696, 2002

- [3] M. Dahlström, X.-M. Fang, D. Lubyshev, M. Urteaga, S. Krishnan, N. Parthasarathy, Y.M. Kim, Y. Wu, J.M. Fastenau, W.K. Liu, and M.J.W. Rodwell, 'Widebandgap DHBTs using a graded Carbon-Doped InGaAS Base', IEEE Electron Device Lett., Vol. 25, pp. 433-435, 2003

- [4] Z. Griffith, M. Dahlström, M. Urteaga, M.J.W. Rodwell, X.-M. Fang, D. Lubyshev, Y. Wu, J.M. Fastenau, and W.K. Liu, 'InGaAs/InP mesa DHBTs with simultaneously high fT and fmax, and low Ccb/IC ratio', submmitted to IEEE Electron Dev. Lett.

- [5] O. Nakajima, H. Ito, T. Nittono, and K. Nagata, 'Current induced degradation of Bedoped AlGaAs/GaAs HBT's and its suppression by Zn diffusion into extrinsic base', Tech Dig. IEEE IEDM, pp. 673-676, 1990

- [6] D.L. Miller and P.M. Asbeck, 'Be redistribution during growth of GaAs and AlGaAs by molecular beam epitaxy', J. Appl. Phys., Vol.57, No.6, pp.1816-1822, 1985

- [7] H. Shimawaki, Y. Amamiya, N. Furuhata, and K. Honjo, 'High-fmax AlGaAs/InGaAs and AlGaAs/GaAs HBT's with p+/p Regrown base contacts', IEEE Trans. Electron Devices, Vol. 42, pp.1735-1744, 1985

- [8] M. Ida, S. Yamahata, K. Kurishima, H. Ita, T. Kobayashi, and Y. Matsuoka, 'Enhancement of fmax in InP/InGaAs HBT's by Selective MOCVD Growth of Heavily-doped Extrinsic Base Regions, IEEE Trans. Electron Devices', Vol. 43, No. 11, pp.1812-1818, 1996

- [9] K. Mochizuki, T. Nakamura, T. Tanoue and H. Masuda, 'AlGaAs/GaAs HBTs with buried SiO2 in the Extrinsic Collector, Solid State Electronics', Vol. 38, pp1619-1622, 1995

- [10] K. Mochizuki, T. Nakamura, T. Mishima, H. Masuda and T. Tanoue T, 'Molecular beam deposition of low-resistance polycrystalline GaAs', Journal of Electronic Materials, Vol 23, pp. 577-580, 1994

- [11] N.Y. Li, C.W. Tu, Journal of Crystal Growth, 'Low-resistance polycrystalline GaAs grown by gas-source molecular beam epitaxy using CBr4', Vol 188, pp. 45-49, 1998

- [12] Y. Dong, D.W. Scott, Y. Wei, A.C. Gossard and M.J.W. Rodwell, 'Low-resistance p-type polycrystalline GaSb grown by molecular beam epitaxy', Journal of Crystal Growth, Vol. 256, pp.223-229, 2003

- [13] G. Bacchin and T. Nishinaga, 'Fabrication of submicrometer structures by PSE/MBE', J. Crystal Growth, Vol. 211, pp. 389-394, 2000

- [14] G. Bacchin, A. Umeno and T. Nishinaga, 'Lateral growth in molecular beam epitaxy by low angle incidence microchannel epitaxy', Appl. Surf. Sci., Vol. 159, pp. 270-276, 2000

- [15] L. Jastrzebski, 'SOI by CVD: epitaxial lateral overgrowth (ELO) process-review', J. of Crystal Growth, Vol. 63, No. 3, pp. 493-526, 1983

- [16] C. Bozler, G. Alley, 'Fabrication and numerical simulation of the permeable base transistor', IEEE Trans. Electron Devices, ED-27, No. 6, pp. 1128-41, 1980

- [17] S. Naritsuka, T. Nishinaga, 'Spatially resolved photoluminescence of laterally overgrown InP on InP-coated Si substrates', J. Crystal Growth, Vol. 174, No.1-4, pp. 622-9, 1997

- [18] O. Parillaud, E. Gil-Lafon, B. Gerald, P. Etienne, D. Pribat, 'High quality InP on Si by conformal growth', Appl. Phys. Lett., Vol. 68, No.19, pp. 2654-6, 1996

- [19] T. Arai, Y. Harada, S. Yamagami, Y. Miyamoto and K. Furuka, 'CBC reduction in GaInAs/InP buried metal heterojunction bipolar transistor', Conference Proceedings, 2000 International Conference on Indium Phosphide and Related Materials, IEEE., pp. 254-257, 2000

- [20] J. Park, P. Barnes, C. Tin, and A. Allerman, 'Lateral overgrowth and epitaxial lift-off of InP by halide vapor-phase epitaxy', J. Crystal Growth, Vol.187, No.2, pp.185-193, 1998

- [21] L. Wernersson, M. Borgström, B. Gustafson, A. Gustafsson, J. Jarlskog, J. Malm, A. Litwin, L. Samuelson, W. Seifert, 'MOVPE overgrowth of metallic features for realisation of 3D metal-semiconductor quantum devices', J. Crystal Growth, Vol. 221, pp. 704-712, 2000

- [22] Y.T. Sun, E. Rodriguez Messmer, D. Soderstrom, D. Jajan, S. Lourdudoss, 'Temporally resolved selective area growth of InP in the openings off-oriented from 110 direction', J. Crystal Growth, Vol. 225, pp. 9-15, 2001

- [23] W. Burton, N. Cabrera, F. Frank, Phil. Trans. Roy. Soc. A 243, pp.299, 1951

- [24] D. Franke, F.W. Reier and N. Grote, 'Post-growth Zn diffusion into InGaAs/InP in a LP MOVPE, Journal of Crystal Growth', Vol.195, pp.112-116, 1998

# **Chapter 3**

# InP HBT with Selectively Implanted Collector

#### 3.1 Introduction

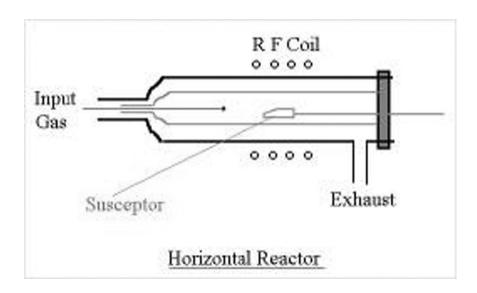

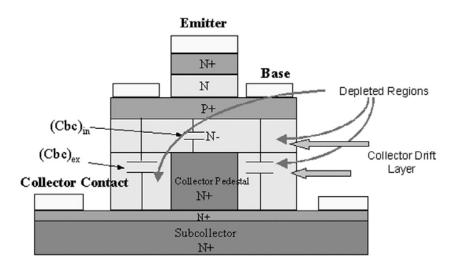

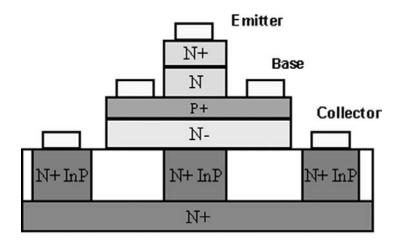

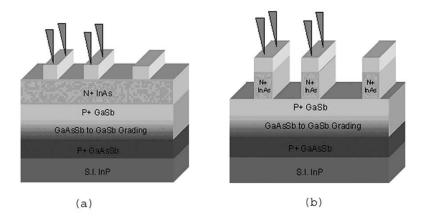

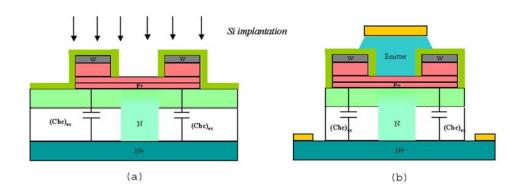

To increase the logic speed of heterojunction bipolar transistors, as discussed in the last chapter, the base–collector junction capacitance ( $C_{BC}$ ) should be reduced as much as possible. In a mesa structured HBT, a large portion of  $C_{BC}$  originates from the extrinsic base-collector region under the base contact. In this chapter, we propose and investigate another approach to reduce the base-collector capacitance. This new HBT structure has a collector pedestal under HBT's intrinsic region by using selective ion implantation and MBE regrowth, as illustrated in Fig.3.1. This structure parallels the widely used selectively implanted collector (SIC) structure in Si/SiGe HBT fabrication process, and is the first such reported structure in III-V HBT technology.

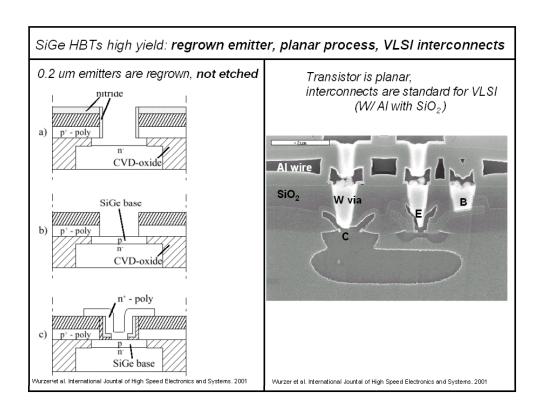

Compared to SiGe HBTs, InP HBTs with InP collectors have 20 times better intrinsic base sheet resistance, 4 times better collector electron velocity, and 6 times better breakdown x f<sub>T</sub> product. However, today InP HBT technology employs relatively crude fabrication processes which severely limit both its performance and integration scale. In contrast, the advanced fabrication processes of SiGe HBT technology bring superior yield and scales of integration, which overcomes the weakness in Si material properties. It is clear that one path to high performance InP HBT devices is to combine best features SiGe and InP HBT technologies. InP HBT with selectively implanted collector is part of our efforts in this direction.

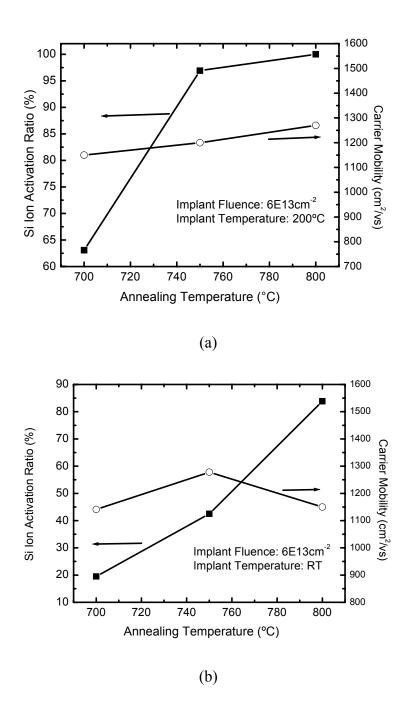

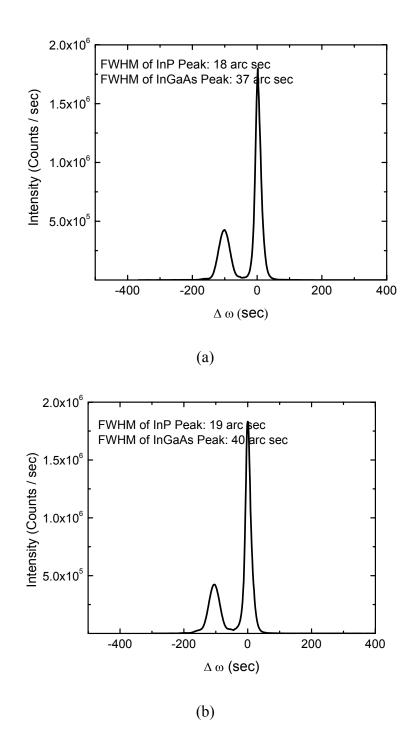

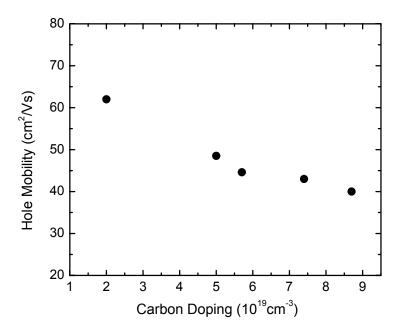

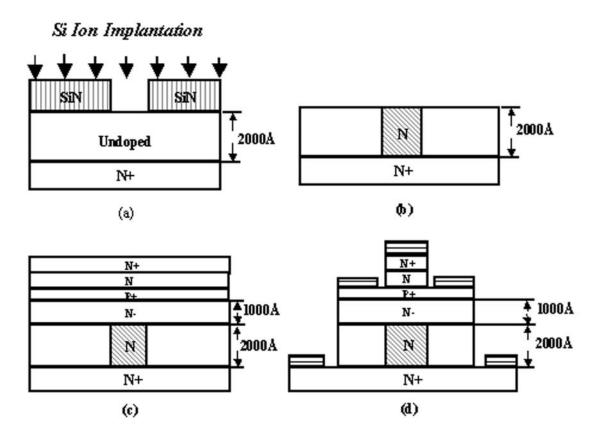

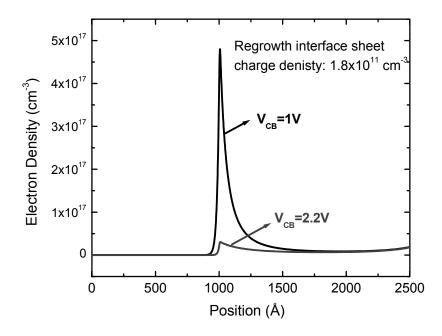

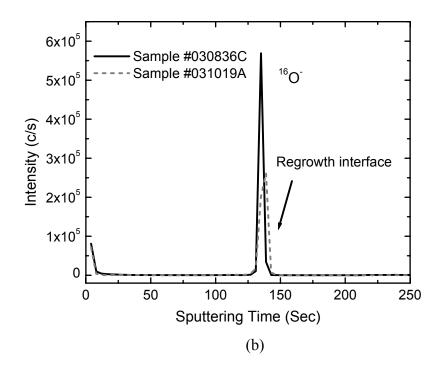

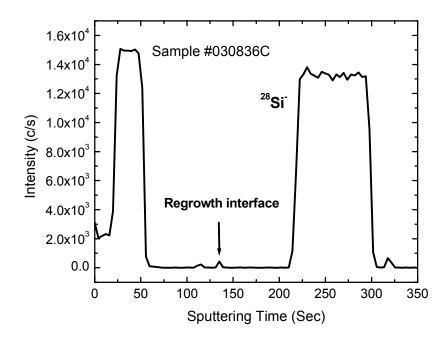

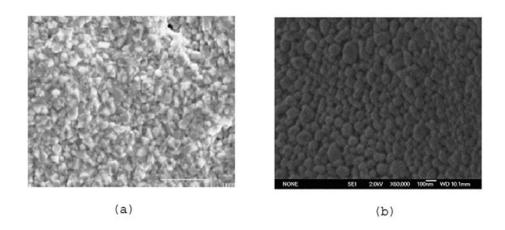

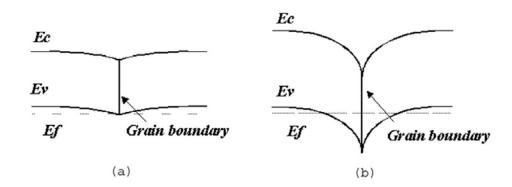

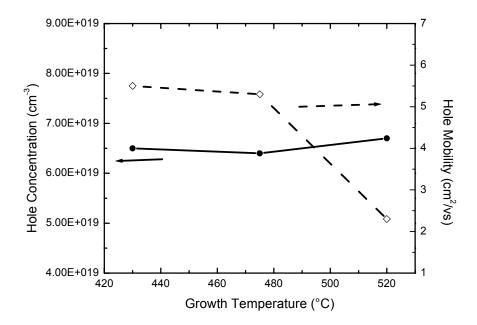

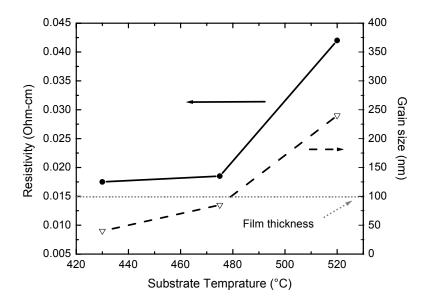

Fig.3.1 Schematic cross-section of the HBT with selectively implanted collector pedestal.