## UNIVERSITY of CALIFORNIA Santa Barbara

## Design and Fabrication of Sub-100 nm Base-Emitter Junctions of THz InP DHBTs

A Dissertation submitted in partial satisfaction of the requirements for the degree

$\begin{array}{c} {\rm Doctor~of~Philosophy}\\ {\rm in} \\ {\rm Electrical~and~Computer~Engineering} \end{array}$

by

Han-Wei Chiang

### Committee in Charge:

Professor Mark J. W. Rodwell, Chair Professor John E. Bowers Professor Umesh K. Mishra Professor Robert A. York

November 2014

| The Dissertation of Han-Wei Chiang is approved. |

|-------------------------------------------------|

|                                                 |

|                                                 |

| Professor John E. Bowers                        |

|                                                 |

| Professor Umesh K. Mishra                       |

|                                                 |

|                                                 |

| Professor Robert A. York                        |

|                                                 |

| Professor Mark I W Rodwell Committee Chair      |

October 2014

## Design and Fabrication of Sub-100 nm Base-Emitter Junctions of THz InP $$\operatorname{DHBTs}$$

Copyright © 2014

by

Han-Wei Chiang

Dedicated to my parents for their love and support.

謹獻給 我的父母

## Acknowledgements

It has been five amazing years since I joined Professor Rodwell's research group at UCSB. I can still vaguely recall the very first day I arrived at Los Angeles International Airport, where the adventure to doctorate degree began. Now, as I am moving towards the end of the expedition, I would like to express my gratitude to everyone who has helped me in this fantastic journey.

Trained as a Materials scientist during my undergraduate program, I decided to take the career path into the semiconductor industry. I am very grateful to my advisor, Prof. Mark Rodwell, for granting me the opportunity to join his research group and participate the development of the state-of-the-art DHBTs. I am very thankful for the valuable discussions with Prof. Rodwell, which have broadened my insight on Device Physics and Microwave Circuits. With his guidance, I have not only survived the transition from Materials Science to Electrical Engineering, but, more importantly, influenced by his way of thinking, in which everything must follow a logical path. I believe the latter is the essence in the training of a Ph. D. regardless the field.

I would also like to thank my committee members: Prof. Umesh Mishra, Prof. John Bowers, and Prof. Robert York. It is through Prof. Mishra's lectures as well as our discussions that I acquire the fundamental knowledge on electronic devices. Even now, several years after taking his class, I am still impressed by the depth of his knowledge. The discussion with Prof. Bowers and Prof. York have also been proven to be very worthwhile. Their inputs during my qualifying exam have partially motivated the effort in TCAD simulation in this thesis.

I intend to give my gratitude towards Dr. Brian Thibeault, who have shared

with me his experience and brilliant insight on III-V processing. Because of his input, I have been able to develop/refine new process flow more efficiently. Dr. William Mitchell is the expert on e-beam lithography. Without his effort, the fabrication of nano-scaled device would not be possible. In addition, the accomplishments reported in this dissertation would not be realized if there had not been a fabrication facility managed by a dedicated staff.

The HBT team in Rodwell group deserves my sincere acknowledgement. I am grateful towards Dr. Vibhor Jain and Dr. Evan Lobissor, who taught me in detail the entire DHBT process flow. I owe my colleague Johann Rode many thanks for his credit in developing the base contact process flow and for his help in both processing and measurement. I have enjoyed the time working with Prateek Choudhary, who always cheered me up after numerous failure in the cleanroom. Through my interaction with both former and current Rodwell group members: Andy, Ashish, Cheng-Ying, Doron, Eli, Greg, Hyunchul Kim, Hyunchul Park, Jeremy, Rob, Saeid, Sanghoon, Seong-Kyun, and Thomas, I have learned a lot, be it the professional knowledge or the philosophy in life.

It has been a long way to Ph.D., and I could not have made it to the very end if without the support from all my friends in Santa Barbara and in Taiwan. I will cherish every moment I shared with you.

Finally, my utmost gratitude shall belong to my family, especially my parents, who encouraged me to study abroad. None of these would be possible if it were not for the unconditional love and support of my family.

## Curriculum Vitæ Han-Wei Chiang

#### Personal

Jan. 1985 Born in Taipei, Taiwan.

versity.

#### Education

| 2014 | Ph.D. in Electrical and Computer Engineering, University of California, Santa Barbara. |

|------|----------------------------------------------------------------------------------------|

| 2011 | M.S. in Electrical and Computer Engineering, University of California, Santa Barbara . |

| 2007 | B.S. in Materials Science and Engineering, National Taiwan Uni-                        |

#### **Publications**

- [1] **H. W. Chiang**, J. C. Rode, P. Choudhary, and M. J. W. Rodwell, "Interfacial transport and current gain in InGaAs/InP DHBTs for THz applications," 72nd IEEE Device Research Conference, 2014.

- [2] **H. W. Chiang**, J. C. Rode, P. Choudhary, and M. J. W. Rodwell, "Lateral Carrier Diffusion and Current Gain in THz InGaAs/InP DHBTs," J. Appl. Phys., vol. 115, no. 3, pp. 034513, 2014.

- [3] D. C. Elias, A. Sivananthan, C. Zhang, S. Keller, **H. W. Chiang**, J. J. M. Law, B. J. Thibeault, W. J. Mitchell, S. Lee, A. D. Carter, C.-Y. Huang, V. Chobpattana, S. Stemmer, S. P. Denbaars, L. A. Coldren and M. J. W. Rodwell, "Formation of InGaAs fins by atomic layer epitaxy on InP sidewalls," Jpn. J. Appl. Phys., vol. 53, no. 6, pp. 065503, 2014.

- [4] D. C. Elias, J. J. M. Law, **H. W. Chiang**, A. Sivananthan, C. Zhang, B. J. Thibeault, W. J. Mitchell, S. Lee, A. D. Carter, C.-Y. Huang, V. Chobpattana, S. Stemmer, S. Keller, and M. J. W. Rodwell, "Formation of Sub-10 nm width InGaAs finFETs of 200 nm Height by Atomic Layer Epitaxy," 71st IEEE Device Research Conference, 2013.

- [5] M. J. W. Rodwell, M. Seo, J. Hacker, A. Young, Z. Griffith, R. Pierson, M. Urteaga, J. C. Rode, H. W. Chiang, V. Jain, E. Lobisser, T. Reed, A. Baraskar, J. J. M. Law, A. D. Carter, S. Lee, D. C. Elias, B. J. Thibeault, W. J. Mitchell, S. Stemmer, A. C. Gossard, S. Mehotra, M. Povolotskyi, G. Klimeck, "Transistor and IC design for Sub-mm-wave and THz ICs," 2012 European Microwave IC Conference, 2012.

- [6] M. J. W. Rodwell, J. C. Rode, H. W. Chiang, P. Choudhary, T. Reed, E. Bloch, S. Danesgar, H-C Park, A. C. Gossard, B. J. Thibeault, W. J. Mitchell, M. Urteaga, Z. Griffith, J. Hacker, M. Seo, B. Brar, "THz Indium Phosphide Bipolar Transistor Technology," 2012 IEEE Compound Semiconductor Integrated Circuit Symposium, 2012.

- [7] E. Lobisser, J. C. Rode, V. Jain, H. W. Chiang, A. Baraskar, W. J. Mitchell, B. J. Thibeault, Mark J. W. Rodwell, "InGaAs/InP DHBTs with Emitter and Base Defined through Electron-Beam Lithography for Reduced Ccb and Increased RF Cut-off Frequency," 39th International Symposium on Compound Semiconductors, 2012.

- [8] V. Jain, J. C. Rode, H. W. Chiang, A. Baraskar, E. Lobisser, B. J. Thibeault, M. J. W. Rodwell, M. Urteaga, D. Loubychev, A. Snyder, Y. Wu, J. M. Fastenau, W. K. Liu, "1.0 THz f<sub>max</sub> InP DHBTs in a refractory emitter and self-aligned base process for reduced base access resistance," 69th IEEE Device Research Conference, 2011.

#### Abstract

Design and Fabrication of Sub-100 nm Base-Emitter Junctions of THz InP  $$\operatorname{DHBTs}$$

by

### Han-Wei Chiang

Because of their wide RF bandwidth ( $\sim 1\,\mathrm{THz}$ ) and high breakdown voltages ( $BV_{\mathrm{CEO}} > 3\,\mathrm{V}$ ), npn-In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP double heterojunction bipolar transistors (DHBTs) have extensive applications in monolithic microwave integrated circuits (MMICs) such as high performance transceivers, near-terabit optical fiber link, and THz amplifiers in radar/imaging systems. The improvements in the performance of DHBTs were made possible because of device scaling. As the technology advances towards the next scaling generations, new challenges in the manufacturing techniques and the device designs are met. The purpose of this work is to provide solutions to the problems encountered in the fabrication and design of the base-emitter junction while scaling from 200 to sub-100 nm emitter width.

Two important issues regarding the base-emitter junction arises while scaling towards sub-100 nm emitter width. The process flow for the refractory emitter metal stack developed for 250-100 nm emitter width has already reached its limitation. In order to improve the transistor yield at a reduced linewidth without designing a new process flow, revisions have been made to the existing one. Employing the revised process flow, 75 nm-wide emitter is feasible. The overall transistor yield has also been improved. This increases the number of working

devices per sample, enabling thorough device analyses.

Experimentally, a reduction of current gain ( $\beta$ ) associated with device scaling has been observed. In order to assess the causes of the reduction, the electron transport in the base is emulated by a commercial simulator. A model for DC- $\beta$  at high injection current density ( $25\,\mathrm{mA}/\mu\mathrm{m}^2$ ) was constructed by the comparison between the experimental and the simulation results. The model allows the estimation of  $\beta$ , which benefits the design of the future scaling generations of DHBTs.

It has been deduced from the model that the current originated from Auger recombination and lateral electron diffusion (via the surface and the bulk base semiconductor) are the dominant components that limits DC- $\beta$ . To suppress the diffusion current via surface, a process flow is developed to form passivating sidewall onto the base surface. Such process flow has already been incorporated into DHBT fabrication. Moreover, new geometries for the base-emitter junction have been designed on the purpose of reducing the Auger recombination rate and lateral electron diffusion in the bulk base region. Using the model for  $\beta$ , the new designs could potentially improve DC- $\beta$  beyond 50 if the corresponding process flow could be adequately integrated.

## Contents

| A            | ckno   | wledge             | ements                                       | $\mathbf{v}$ |

|--------------|--------|--------------------|----------------------------------------------|--------------|

| $\mathbf{C}$ | urric  | ulum '             | Vitæ                                         | vii          |

|              |        |                    |                                              | vii          |

| $\mathbf{A}$ | bstra  | ct                 |                                              | ix           |

| Li           | ist of | Table              | $\mathbf{s}$                                 | xiv          |

| Li           | ist of | Figure             | es                                           | xv           |

| 1            |        | roducti<br>erences | ion<br>                                      | <b>1</b> 6   |

| <b>2</b>     | DH     | BT Tł              | neory                                        | 10           |

|              | 2.1    | Device             | e Structure                                  | 11           |

|              | 2.2    | RF Cl              | haracteristics and DHBT Scaling Laws         | 14           |

|              |        | 2.2.1              | Small-signal AC Equivalent Circuit           | 14           |

|              |        | 2.2.2              | Base and Collector Transit Time              | 15           |

|              |        | 2.2.3              | Emitter Charging Time                        | 18           |

|              |        | 2.2.4              | Collector Charging Time                      | 19           |

|              |        | 2.2.5              | Cutoff Frequencies                           | 21           |

|              |        | 2.2.6              | DHBT Scaling Law                             | 24           |

|              | 2.3    | DC C               | urrent Gain of DHBT                          | 25           |

|              |        | 2.3.1              | Bulk Base Current                            | 28           |

|              |        | 2.3.2              | Bulk Lateral Diffusion Current               | 33           |

|              |        | 2.3.3              | Surface Recombination and Conduction Current | 34           |

|              |        | 2.3.4              | DC Current Gain and DHBT Scaling             | 36           |

|              | Refe   | rences             |                                              | 38           |

| 3 | DH   | BT Pr  | rocess Improvement 4                                      | 12  |

|---|------|--------|-----------------------------------------------------------|-----|

|   | 3.1  | Refrac | etory Emitter Metal Stack                                 | 14  |

|   | 3.2  | Comp   | osite Dielectric Sidewall                                 | 52  |

|   | 3.3  | Interc | onnects Between Metal Layers                              | 56  |

|   | Refe | rences |                                                           | 31  |

| 4 | Exp  | erime  | ntal Results 6                                            | 3   |

|   | 4.1  | Measu  | $\alpha$ rement set up and calibration 6                  | 34  |

|   | 4.2  | DHBT   | Г63В                                                      | 37  |

|   |      | 4.2.1  | Device structure and process feature                      | 37  |

|   |      | 4.2.2  | TEM analysis                                              | 71  |

|   |      | 4.2.3  |                                                           | 73  |

|   |      | 4.2.4  | Transistor DC characteristics                             | 75  |

|   |      | 4.2.5  |                                                           | 77  |

|   | 4.3  | DHBT   | <del>-</del>                                              | 37  |

|   |      | 4.3.1  |                                                           | 37  |

|   |      | 4.3.2  |                                                           | 90  |

|   |      | 4.3.3  | · ·                                                       | 91  |

|   |      | 4.3.4  |                                                           | 92  |

|   |      | 4.3.5  |                                                           | )4  |

|   | 4.4  | Summ   | nary                                                      | )2  |

|   | Refe |        |                                                           | )4  |

| 5 | DC   | Curre  | ent Gain of DHBTs: TCAD Simulation 10                     | )6  |

|   | 5.1  |        | ation Setup                                               | )8  |

|   |      | 5.1.1  | Carrier Mobility and Velocity Saturation                  |     |

|   |      | 5.1.2  | Band Structure                                            |     |

|   |      | 5.1.3  | Carrier Recombination                                     |     |

|   |      | 5.1.4  | Surface Conduction and Recombination                      |     |

|   | 5.2  | Simula | ation and Experimental Results                            | ١7  |

|   |      | 5.2.1  | Bulk Recombination and Lateral Diffusion Current 11       | ۱7  |

|   |      | 5.2.2  | Surface Recombination and Conduction Current 12           |     |

|   |      | 5.2.3  | Model Verification                                        |     |

|   | 5.3  |        | Base-Emitter Junction Designs                             |     |

|   | 2.0  | 5.3.1  | Epitaxy Design: Graded Base with a Pulse-doped Layer . 12 |     |

|   |      | 5.3.2  | Supplement Process Flow: Trench in Extrinsic Base 13      |     |

|   |      | 5.3.3  | New Process Flow: Recessed B-E Junction and Emitter Re-   | - 4 |

|   |      | 0.0.0  | growth                                                    | 3.3 |

|   | Rofe | roncos | 19                                                        |     |

| 6            | Con  | clusion  | 1                                                         | 140 |

|--------------|------|----------|-----------------------------------------------------------|-----|

|              | 6.1  | Achiev   | ements                                                    | 141 |

|              |      | 6.1.1    | Process Improvements                                      | 141 |

|              |      | 6.1.2    | Device Performance                                        | 142 |

|              |      | 6.1.3    | Simulation Results                                        | 143 |

|              | 6.2  | Future   | Work                                                      | 144 |

|              |      | 6.2.1    | Refractory Base Contact                                   | 144 |

|              |      | 6.2.2    | Extrinsic Base Passivation                                | 144 |

|              |      | 6.2.3    | Emitter Width Scaling and Emitter Regrowth                | 145 |

|              | Refe | rences . |                                                           | 147 |

| $\mathbf{A}$ | DH   | BT Pro   | ocess Flow                                                | 149 |

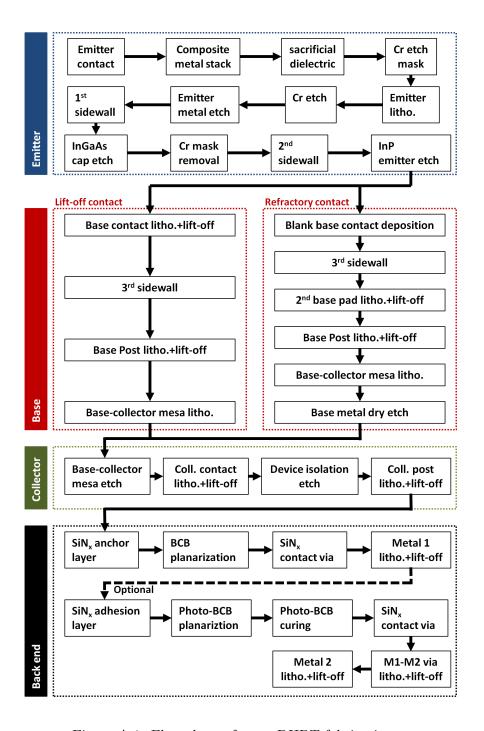

|              | A.1  | Overvi   | ew                                                        | 151 |

|              | A.2  | Emitte   | er Process Flow                                           | 151 |

|              |      | A.2.1    | Emitter Contact and Composite Metal Stack                 | 151 |

|              |      | A.2.2    | Sacrificial Dielectric Layer and Chromium Mask Deposition | 153 |

|              |      | A.2.3    | Emitter Lithography                                       | 153 |

|              |      | A.2.4    | Chromium Mask Dry Etch                                    | 154 |

|              |      | A.2.5    | Emitter Composite Stack Dry Etch                          | 154 |

|              |      | A.2.6    | First $SiN_x$ Sidewall Formation                          | 155 |

|              |      | A.2.7    | InGaAs Emitter Cap Wet Etch                               | 156 |

|              |      | A.2.8    | Chromium Mask Removal                                     | 156 |

|              |      | A.2.9    | Second $SiN_x$ Sidewall Formation                         | 157 |

|              |      | A.2.10   | InP Emitter Wet Etch (LO)                                 | 157 |

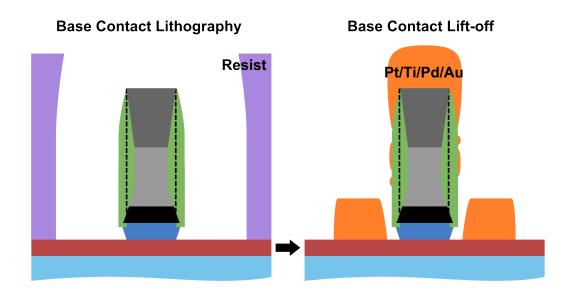

|              |      | A.2.11   | Base Contact Lithography and Lift-off(LO)                 | 157 |

|              |      |          | Third Sidewall Formation (LO/RB)                          | 158 |

|              |      |          | Base Post Lithography and Lift-off (LO/RB)                | 159 |

|              |      |          | Base-collector Mesa Lithography (LO/RB)                   | 160 |

|              |      |          | InP Emitter Wet Etch (RB)                                 | 160 |

|              |      |          | First Base Metalization (RB)                              | 161 |

|              |      |          | Second Base Metal Lithography and Lift-off (RB)           | 161 |

|              |      |          | Refractory Metal Dry Etch (RB)                            | 162 |

|              |      |          | Base-collector Mesa Wet Etch                              | 162 |

|              |      |          | Collector Contact Lithography and Lift-off                | 163 |

|              |      |          | Device Isolation Lithography and Wet Etch                 | 164 |

|              |      |          | Collector Post Lithography and Lift-off                   | 165 |

|              |      |          | $SiN_x$ Anchor Layer Deposition                           | 166 |

|              |      |          | BCB Planarization                                         | 167 |

|              |      |          | Dielectric Contact Via                                    | 168 |

|              |      | A 2 26   | Metal 1 Lithography and Lift-off                          | 169 |

## List of Tables

| 2.1                      | Scaling laws of DHBTs: the required change for improving $f_{\tau}$ and $f_{\text{max}}$ by a factor of $\gamma$                                                            | 26  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1<br>4.2<br>4.3<br>4.4 | Epitaxial structure of DHBT63                                                                                                                                               | 88  |

| 5.1                      | $In_{0.53}Ga_{0.47}As$ parameter values used in simulation and corresponding references. The coefficients for Auger recombination are usually reported as a combined value. | 116 |

| 6.1                      | A summary of device performance of DHBT63B and DHBT58H $$                                                                                                                   | 143 |

| A.1                      | List of tools involved in DHBT fabrication                                                                                                                                  | 150 |

## List of Figures

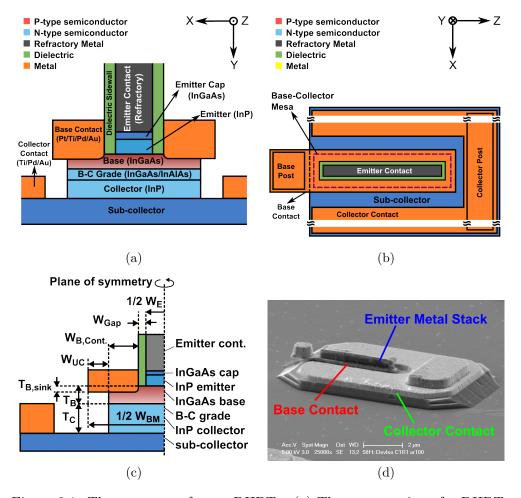

| 2.1 | The structure of mesa-DHBTs. (a) The cross-section of a DHBT.                                                          |    |

|-----|------------------------------------------------------------------------------------------------------------------------|----|

|     | (b) The top-down view of a DHBT. (c) The schematic showing the                                                         |    |

|     | important dimensions in DHBTs. Only half of the device is shown                                                        |    |

|     | due to symmetry. (d) The SEM of a experimental device after the                                                        |    |

|     | front end process                                                                                                      | 13 |

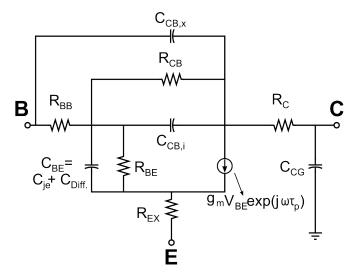

| 2.2 | The small-signal equivalent circuit of a DHBT approximated by the                                                      |    |

|     | hybrid- $\pi$ model                                                                                                    | 15 |

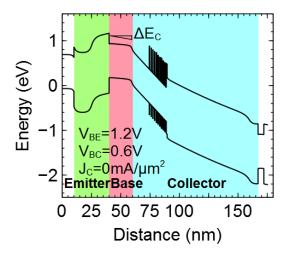

| 2.3 | The band diagram of a DHBT in the forward active mode. The                                                             |    |

|     | band gap narrowing effect and the space charge region in the col-                                                      |    |

|     | lector are neglected                                                                                                   | 16 |

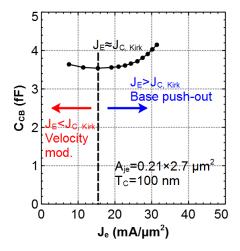

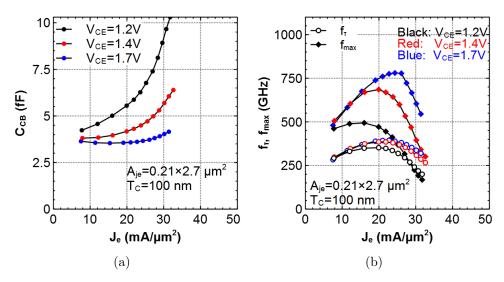

| 2.4 | Experimental $C_{\text{CB}}$ vs. $J_{\text{E}}$ measured from a device with $W_{\text{E}}{=}210\text{nm}$              |    |

|     | and $T_{\rm C}$ =100 nm (DHBT58H)                                                                                      | 21 |

| 2.5 | The schematic of the distributed R-C network in the base-collector                                                     |    |

|     | mesa in a DHBT                                                                                                         | 23 |

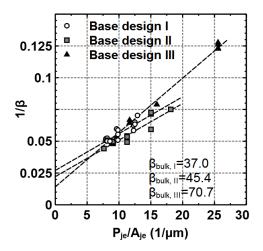

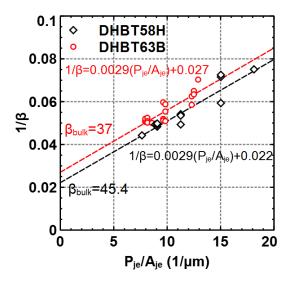

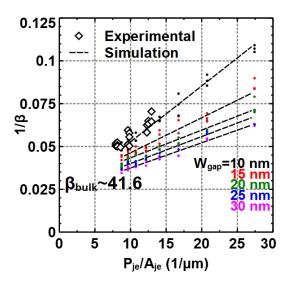

| 2.6 | Inverse DC current gain $(1/\beta)$ vs. HBT emitter periphery to area                                                  |    |

|     | ratio $(P_{\rm ie}/A_{\rm ie} \approx 2/W_{\rm E})$ of experimental DHBTs with distance be-                            |    |

|     | tween base and emitter contacts $(W_{\rm gap}) \approx 10  \rm nm$ and different base                                  |    |

|     | designs. The values of $\beta$ are measured at emitter current density                                                 |    |

|     | $J_{\rm E} \stackrel{\circ}{pprox} 25 { m mA}/\mu { m m}^2$                                                            | 27 |

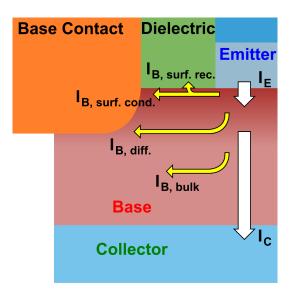

| 2.7 | A schematic of the current components in the base of DHBTs                                                             | 28 |

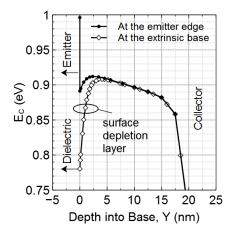

| 2.8 | Simulated conduction band energy $(E_{\rm C})$ at $V_{\rm BE} \approx 1.2  {\rm V}$ vs. depth                          |    |

|     | into the base semiconductor at the edge of the emitter and in the                                                      |    |

|     | extrinsic base. The simulation assumes a 20 nm thick base with                                                         |    |

|     | doping varying from $1.2 \times 10^{20}  \mathrm{cm}^{-3}$ at the emitter side to $8 \times 10^{20}  \mathrm{cm}^{-3}$ |    |

|     | $10^{19} \mathrm{cm}^{-3}$ at the collector side [18]. The energy is relative to the                                   |    |

|     | base Fermi level.                                                                                                      | 29 |

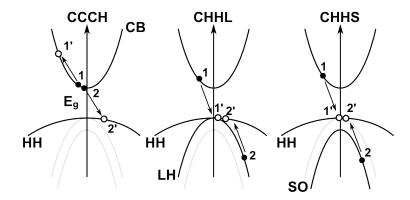

| <ul><li>2.9</li><li>2.10</li></ul> | Three Auger processes in III-V semiconductors. [20]. The solid circles represent the occupied states, and the empty circles represent the empty states                                                                                                  | 30                   |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

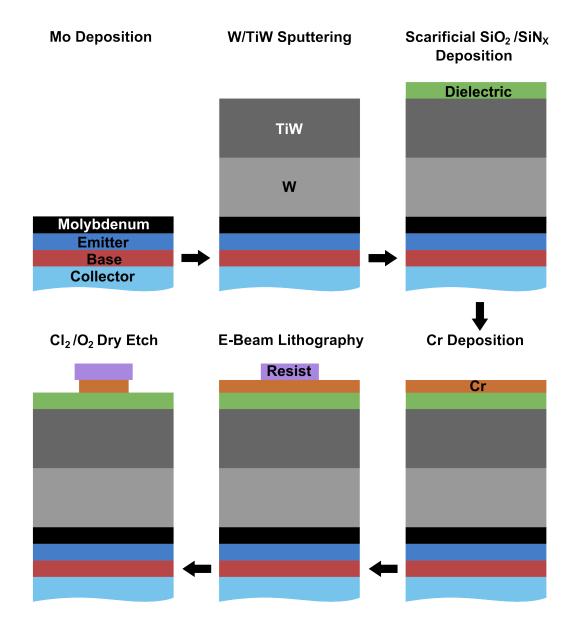

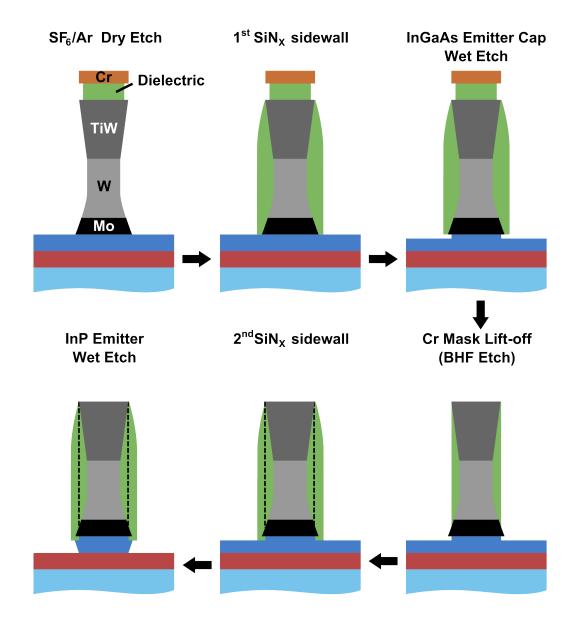

| 3.1<br>3.2<br>3.3<br>3.4           | The schematics of UCSB DHBT emitter process flow                                                                                                                                                                                                        | 47<br>48<br>49<br>50 |

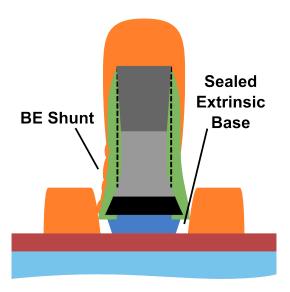

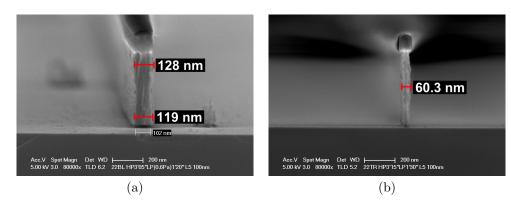

| 3.5                                | SEM of 1:1 W:TiW metal stack on an InP test sample after SF <sub>6</sub> /Ar ICP etch. (a) Cross-section of the stack with $W_{\rm E\approx}250{\rm nm}$ . (b) A stack with $W_{\rm E}\approx75{\rm nm}$                                                | 52                   |

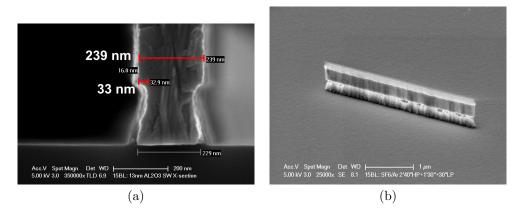

| 3.6                                | Schematics of 256, 128, and 64 nm wide emitter metal stacks after SF <sub>6</sub> /Ar ICP etch. Upper row: 1:1 W:TiW. Bottom row: 1:2.5 W:TiW                                                                                                           | 53                   |

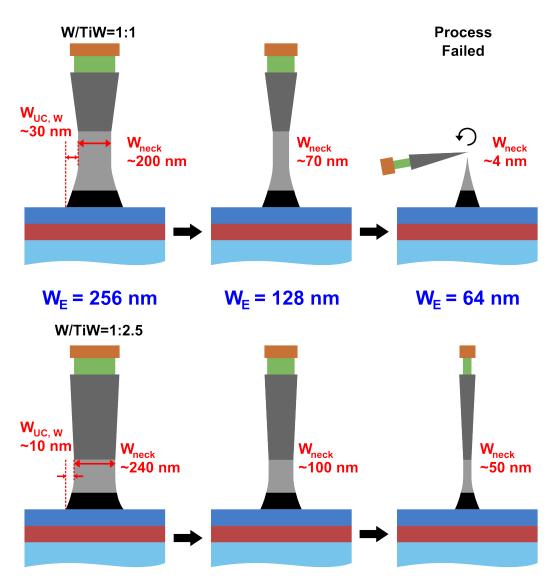

| 3.7                                | SEM cross-sections of 1:2.5 W:TiW metal stack on an InP test sample after recalibrated SF <sub>6</sub> /Ar ICP etch. (a) $W_{\rm E}$ =128 nm. (b) $W_{\rm E}$ =64 nm                                                                                    | 54                   |

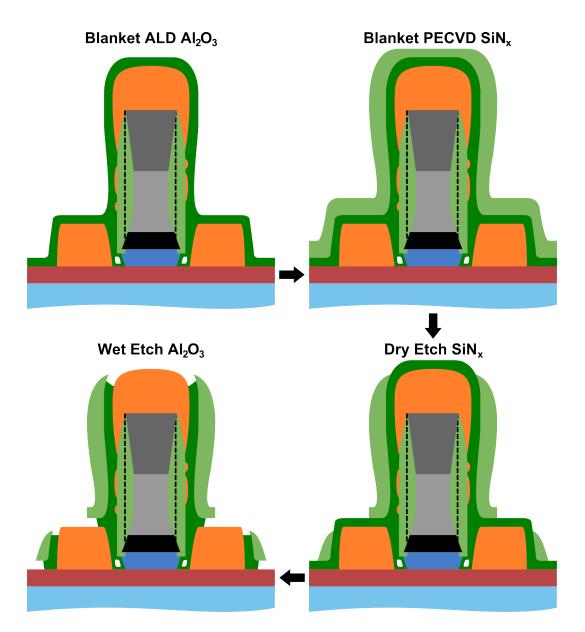

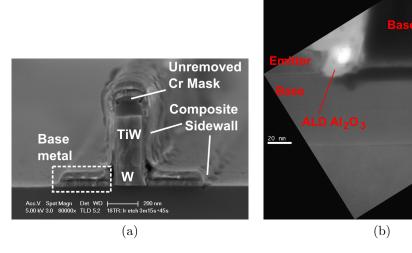

| 3.8<br>3.9                         | Process flow for the composite $Al_2O_3/SiN_x$ sidewall                                                                                                                                                                                                 | 55                   |

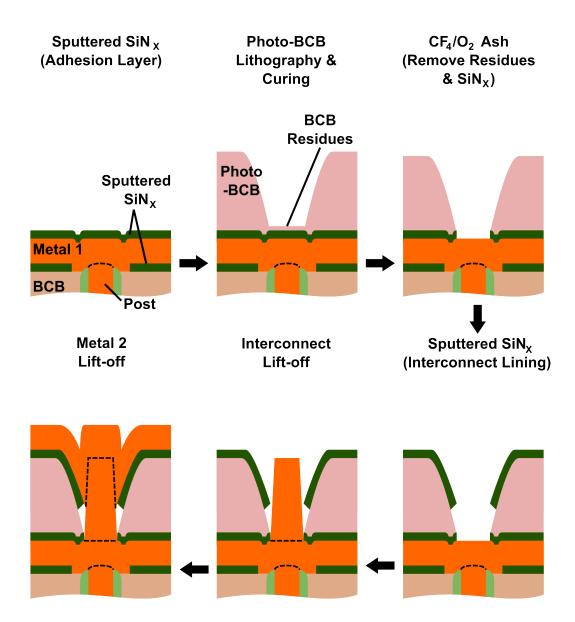

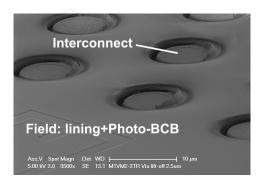

|                                    | Process flow for interconnects between metal layers SEM of interconnects between metal layers on a test sample                                                                                                                                          | 59<br>60             |

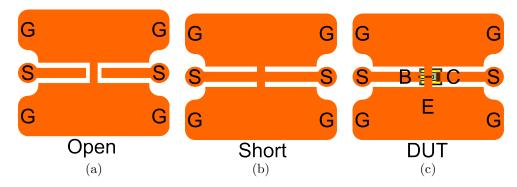

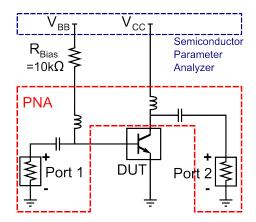

| 4.1<br>4.2                         | Top-down schematics of (a) open and (b) short calibration structures, and (c) CPW interconnect with device under test (DUT) RF measurement set up. The delay associated with semi-rigid waveguides were removed after calibration. Hence the waveguides | 65                   |

|                                    | are neglected in the diagram.                                                                                                                                                                                                                           | 68                   |

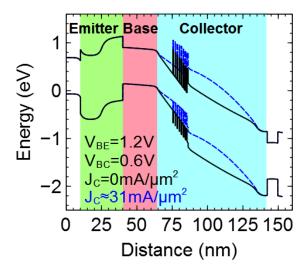

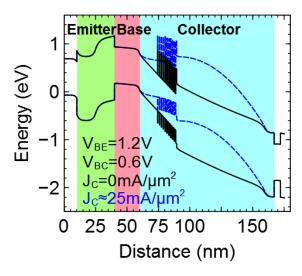

| 4.3   | Computed band diagram of DHBT63 under $V_{\rm BE}$ =1.2 V and $V_{\rm CB}$ =0.6 V. The solid lines are the conduction and valance bands when               |     |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|       | $J_{\rm C} = 0{\rm mA}/\mu{\rm m}^2$ , i.e. ignoring the space charge in the collector re-                                                                 |     |

|       | gion. The dashed line represent the conduction and valance bands                                                                                           |     |

|       | considering the space charge region in the collector at $J_{\rm C} \approx 31 \mathrm{mA}/\mu\mathrm{m}^2$ .                                               | 69  |

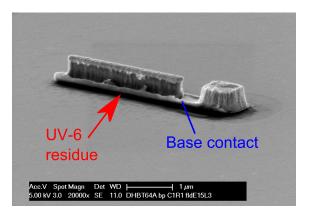

| 4.4   | An SEM image of an HBT sample after base post lift-off. Residues                                                                                           |     |

|       | of UV-6 were found around the base contact, possibly due to the                                                                                            |     |

|       | damaged resist sidewall                                                                                                                                    | 70  |

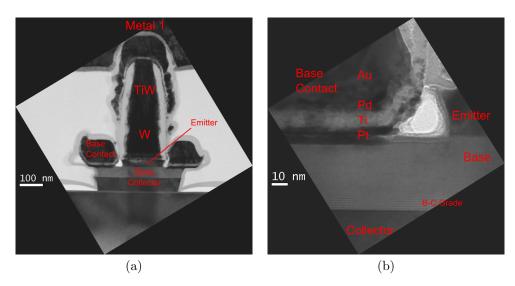

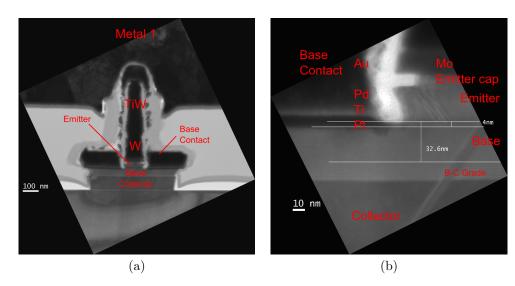

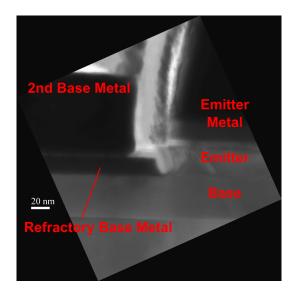

| 4.5   | TEM cross-section normal to the emitter stripe of a device on                                                                                              | • • |

|       | DHBT63B with $W_{\rm E,design}$ =100 nm, $W_{\rm BM,design}$ =500 nm. (a) An overview                                                                      | J   |

|       | of the device. (b) zoomed in at the vicinity of the base contact and                                                                                       | •   |

|       | emitter                                                                                                                                                    | 72  |

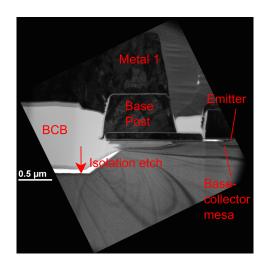

| 4.6   | TEM cross-section parallel to the emitter stripe of a device on                                                                                            | . 2 |

| 1.0   | DHBT63B with $L_{\rm E,design}=3\mu{\rm m}$ . The image is zoomed in at the                                                                                |     |

|       | vicinity of the base post                                                                                                                                  | 73  |

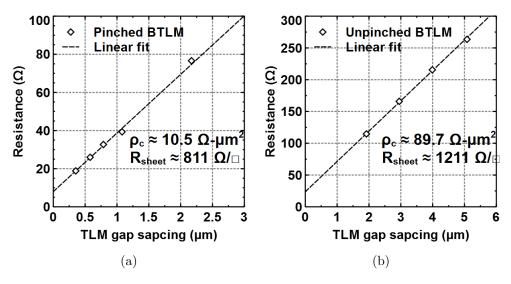

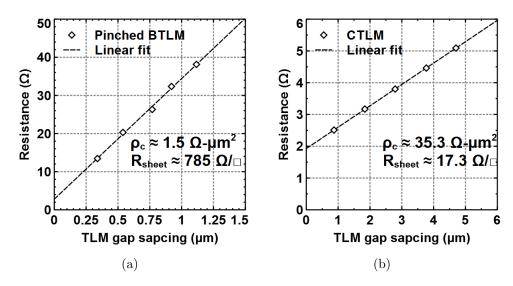

| 4.7   | (a) Pinched and (b) Unpinched base TLM data of DHBT63B. The                                                                                                | 10  |

| 4.1   | width of TLM structure and the distances between metal pads (gap                                                                                           |     |

|       | spacing) were measured with SEM                                                                                                                            | 74  |

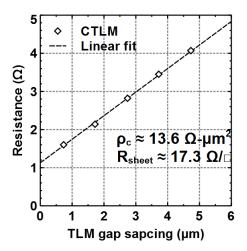

| 4.8   | Collector TLM result of DHBT63B. The width of TLM structure                                                                                                | 14  |

| 4.0   | and the distances between metal pads (gap spacing) were measured                                                                                           |     |

|       | with SEM                                                                                                                                                   | 74  |

| 4.0   |                                                                                                                                                            | 14  |

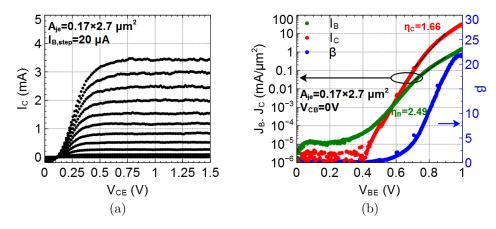

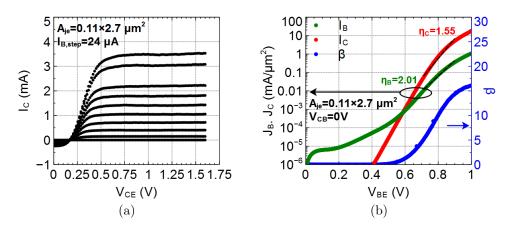

| 4.9   | DC characteristics of the device with $W_{\rm E,design}$ =100 nm, $W_{\rm BM,design}$                                                                      |     |

|       | = 500 nm, and $L_{\rm E,design}$ = 3 $\mu$ m.(a) Common emitter output characteristics. The increase of the base remark ( $L_{\rm E}$ ) is 20 $\mu$ A. (b) |     |

|       | teristics. The increment of the base current $(I_{B,\text{step}})$ is $20 \mu\text{A}$ . (b)                                                               | 76  |

| 4.10  | I-V characteristics of B-E and B-C diodes (Gummel plot)                                                                                                    | 76  |

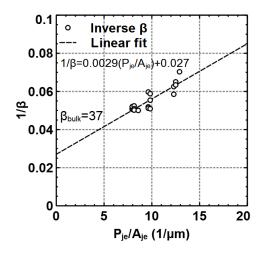

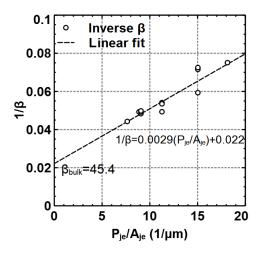

| 4.10  | Inverse DC- $\beta$ vs. base-emitter junction periphery to area ratio                                                                                      |     |

| 4 1 1 | $(P_{\rm je}/A_{\rm je})$ of the devices on DHBT63B                                                                                                        | 77  |

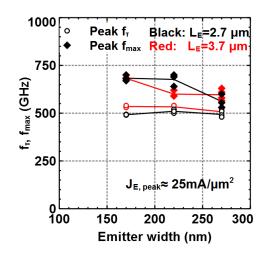

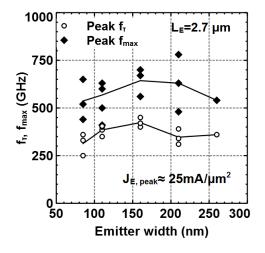

| 4.11  | Peak $f_{\tau}$ and $f_{\text{max}}$ vs. base-emitter junction width of the devices                                                                        |     |

| 4.10  | with emitter length $(L_{\rm E})$ of 2.7 and 3.7 $\mu{\rm m}$ on DHBT63B                                                                                   | 78  |

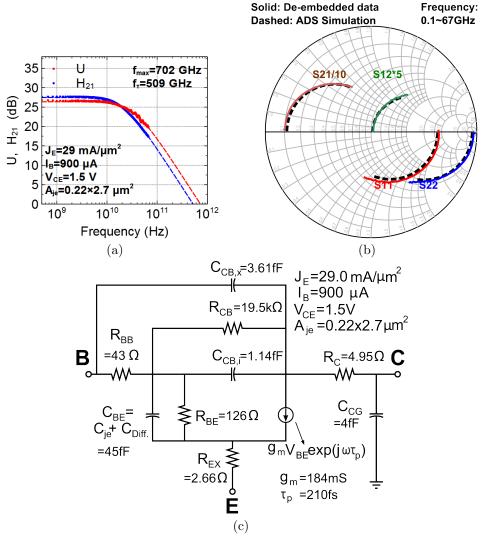

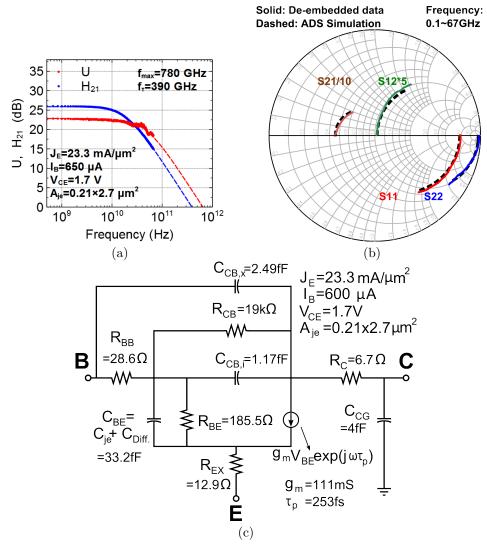

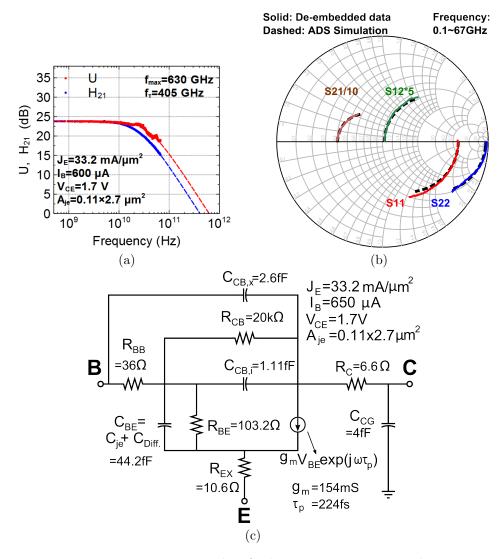

| 4.12  | RF measurement results of a device DHBT63B with $W_{\rm E,design} =$                                                                                       |     |

|       | 150 nm, $W_{\rm BM,design} = 750$ nm, and $L_{\rm E,design} = 3 \mu{\rm m}$ : (a) unilateral Ma-                                                           |     |

|       | son's gain and $H_{21}$ vs. frequency, (b) Two-port S-parameters vs.                                                                                       |     |

|       | frequency, and (c) small-signal equivalent circuit. In both (a) and                                                                                        |     |

|       | (b), the solid lines represent the experimental data, and the dashed                                                                                       |     |

|       | lines are the ADS simulation results                                                                                                                       | 80  |

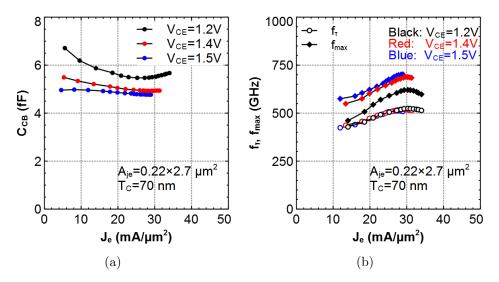

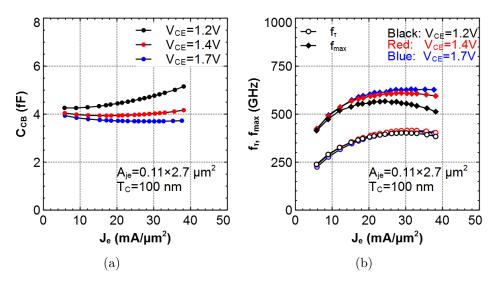

| 4.13  | Current dependency of $C_{\rm CB}$ and cut-off frequencies extracted from                                                                                  |     |

|       | the device on DHBT63B with $W_{\rm E,design}=150$ nm, $W_{\rm BM,design}=750$ nm,                                                                          |     |

|       | and $L_{\rm E,design}$ =3 $\mu$ m at $V_{\rm CE}$ =1.2, 1.4, and 1.5 V.(a) $C_{\rm CB}$ vs. $J_{\rm E}$ . (b) $f_{\tau}$                                   |     |

|       | and $f_{\text{max}}$ vs. $J_{\text{E}}$                                                                                                                    | 81  |

| 4.14 | RF measurement results of a device on DHBT63B with $W_{\rm E,design}$                                                        |    |

|------|------------------------------------------------------------------------------------------------------------------------------|----|

|      | = 100 nm, $W_{\rm BM,design}$ =500 nm, and $L_{\rm E,design}$ =3 $\mu$ m: (a) unilateral                                     |    |

|      | Mason's gain and $H_{21}$ vs. frequency, (b) Two-port S-parameters                                                           |    |

|      | vs. frequency, and (c) small-signal equivalent circuit. In both (a)                                                          |    |

|      | and (b), the solid lines represent the experimental data, and the                                                            |    |

|      | dashed lines are the ADS simulation results                                                                                  | 83 |

| 4.15 | Current dependency of $C_{\rm CB}$ and cut-off frequencies extracted from                                                    |    |

|      | the device on DHBT63B with $W_{\rm E,design}=100{\rm nm},W_{\rm BM,design}=500{\rm nm},$                                     |    |

|      | and $L_{\rm E,design}=3\mu{\rm m}$ at $V_{\rm CB}=0.2,0.4,{\rm and}0.6{\rm V.(a)}C_{\rm CB}$ vs. $J_{\rm E.}$ (b) $f_{\tau}$ |    |

|      | and $f_{\text{max}}$ vs. $J_{\text{E}}$                                                                                      | 84 |

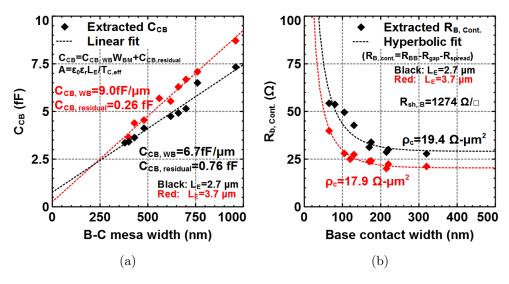

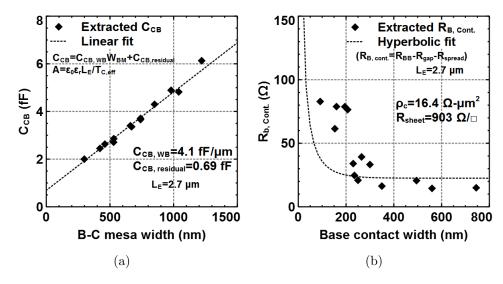

| 4.16 | Dimension dependence of (a) $C_{\rm CB}$ (vs. $W_{\rm BM,design}$ ) and (b) $R_{\rm B,cont.}$                                |    |

|      | (vs. $W_{\rm B,cont.}$ ) from device with $L_{\rm E}$ =2.7 and 3.7 $\mu \rm m$ biased at $V_{\rm CB}$                        |    |

|      | $= 0.5 \sim 0.6 \text{V} \text{ and } J_{\text{E}} = 25 \sim 30 \text{mA}/\mu\text{m}^2$                                     | 85 |

| 4.17 | Computed band diagram of DHBT58 under $V_{\rm BE}$ =1.2 V and $V_{\rm CB}$ =0.6 V.                                           |    |

|      | The solid lines are the conduction and valance bands when $J_{\rm C}=0~{\rm mA}/\mu{\rm r}$                                  | _  |

|      | The dashed line represent the conduction and valance bands con-                                                              |    |

|      | sidering the space charge region in the collector at $J_{\rm C} \approx 25 \mathrm{mA}/\mu\mathrm{m}^2$ .                    | 89 |

| 4.18 | TEM cross-section normal to the emitter stripe of a device on                                                                |    |

|      | DHBT58H with $W_{\rm E,design}$ =100 nm, $W_{\rm BM,design}$ =450 nm. (a) An overview                                        | V  |

|      | of the device. (b) zoomed in at the vicinity of the base contact and                                                         |    |

|      | emitter                                                                                                                      | 91 |

| 4.19 | (a) Pinched base TLM and (b) Collector TLM data of DHBT58H.                                                                  |    |

|      | The width of TLM structure and the distances between metal pads                                                              |    |

|      | (gap spacing) were measured with SEM                                                                                         | 92 |

| 4.20 | DC characteristics of the device with $W_{\rm E,design}$ =100 nm, $W_{\rm BM,design}$                                        |    |

|      | = 600 nm, and $L_{\rm E,design}$ =3 $\mu$ m.(a) Common emitter output charac-                                                |    |

|      | teristics. The increment of the base current $(I_{B,\text{step}})$ is $24 \mu\text{A}$ . (b)                                 |    |

|      | I-V characteristics of B-E and B-C diodes (Gummel plot)                                                                      | 93 |

| 4.21 | Inverse DC- $\beta$ vs. base-emitter junction periphery to area ratio                                                        |    |

|      | $(P_{\rm ie}/A_{\rm je})$ of the devices on DHBT58H                                                                          | 94 |

| 4.22 | Peak $f_{\tau}$ and $f_{\text{max}}$ vs. base-emitter junction width of the devices                                          |    |

|      | with emitter length, $L_{\rm E}$ =2.7 $\mu{\rm m}$ on DHBT58H                                                                | 95 |

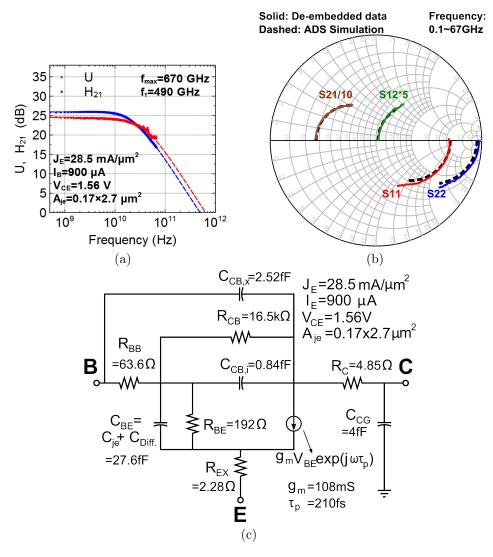

| 4.23 | RF measurement results of a device on DHBT58H with $W_{\rm E,design}$                                                        |    |

|      | = 200 nm, $W_{\rm BM,design}$ =700 nm, and $L_{\rm E,design}$ =3 $\mu$ m: (a) unilateral                                     |    |

|      | Mason's gain and $H_{21}$ vs. frequency, (b) Two-port S-parameters                                                           |    |

|      | vs. frequency, and (c) small-signal equivalent circuit. In (a) and                                                           |    |

|      | (b), the solid lines represent the experimental data, and the dashed                                                         |    |

|      | lines are the ADS simulation results                                                                                         | 97 |

| 4.24       | Current dependency of $C_{\rm CB}$ and cut-off frequencies extracted from the device on DHBT58H with $W_{\rm E,design}$ =200 nm, $W_{\rm BM,design}$ =700 nm, and $L_{\rm E,design}$ =3 $\mu$ m at $V_{\rm CE}$ =1.2, 1.4, and 1.7 V.(a) $C_{\rm CB}$ vs. $J_{\rm E}$ . (b) $f_{\tau}$                                                                                                                                                                                                                                                                                | 98                                |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

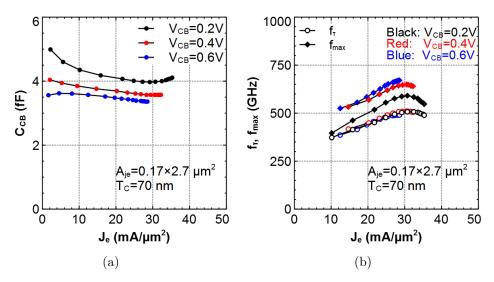

| 4.25       | and $f_{\text{max}}$ vs. $J_{\text{E}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 90                                |

| 4.26       | dashed lines are the ADS simulation results Current dependency of $C_{\rm CB}$ and cut-off frequencies extracted from the device on DHBT58H with $W_{\rm E,design}$ =100 nm, $W_{\rm BM,design}$ =600 nm, and $L_{\rm E,design}$ =3 $\mu$ m at $V_{\rm CB}$ =1.2, 1.4, and 1.7 V.(a) $C_{\rm CB}$ vs. $J_{\rm E}$ . (b) $f_{\tau}$                                                                                                                                                                                                                                    | 100                               |

| 4.27       | and $f_{\rm max}$ vs. $J_{\rm E}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul><li>101</li><li>102</li></ul> |

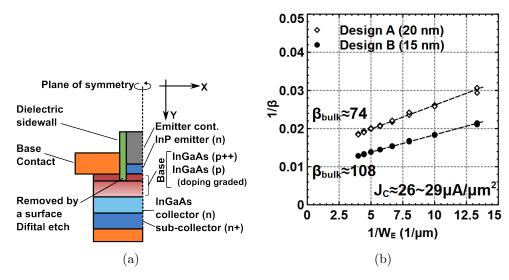

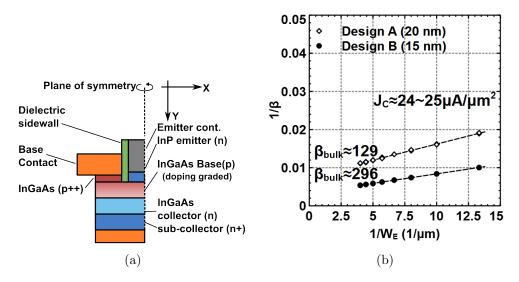

| 5.1<br>5.2 | The cross-section of the SHBT structure simulated by Sentaurus. Inverse DC current gain $(1/\beta)$ vs. HBT emitter periphery to area ratio $(P_{\rm je}/A_{\rm je})$ of DHBT58H and DHBT63B at $J_{\rm E}\approx 25{\rm mA}/\mu{\rm m}^2$ . DHBT58H employs a 20 nm base with doping concentration of 12-8×10 <sup>19</sup> cm <sup>-3</sup> varying from the emitter side to the collector side. DHBT63B has a 25 nm base with lower doping concentration varying from 9 to $5\times10^{19}$ cm <sup>-3</sup> . For both samples $W_{\rm gap}$ ) $\approx10$ nm ac- | 109                               |

| 5.3        | cording to TEM analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ul><li>118</li><li>120</li></ul> |

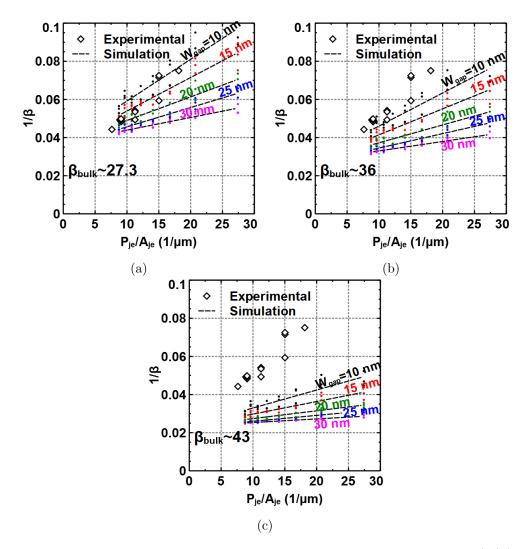

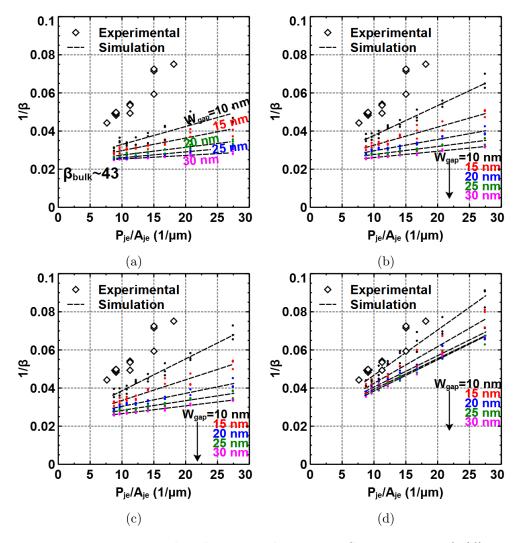

| 5.4        | Experimental and computed inverse DC current gain $(1/\beta)$ vs. $P_{\rm je}/A_{\rm je}$ of DHBT58H at $J_{\rm E}\approx 25{\rm mA}/\mu{\rm m}^2$ . In (a), the simulation assumed zero $D_{\rm it}$ and $v_{\rm surf.rec.}$ . In the rest of the figures, The simulation assumed $v_{\rm surf.rec.}$ =5000 cm/s and $D_{\rm it}$ of (b) $5\times10^{12}$ , (c) $1\times10^{13}$ , and (d) $5\times10^{13}$ cm <sup>-2</sup> eV <sup>-1</sup>                                                                                                                        | 123                               |

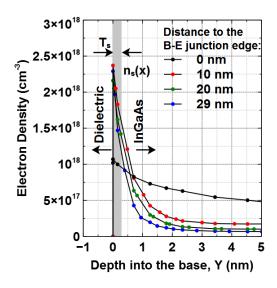

| 5.5        | The computed electron density near the dielectric/InGaAs interface vs. the depth into the base, at different distance to the edge of the B-E junction. The simulation is base on the base design of DHBT58H with $W_{\rm gap}$ =30 nm and assumed $D_{\rm it}$ =5×10 <sup>13</sup> cm <sup>-2</sup> eV <sup>-1</sup> .                                                                                                                                                                                                                                                | 126                               |

| 5.6  | Experimental and computed inverse DC current gain $(1/\beta)$ vs. $P_{\rm je}/A_{\rm je}$ of DHBT63B design at $J_{\rm E}\approx 25{\rm mA}/\mu{\rm m}^2$ . The simulation assumed $v_{\rm surf.rec.}=5000{\rm cm/s},~D_{\rm it}=5\times10^{13}{\rm cm}^{-2}{\rm eV}^{-1},~C_{\rm Auger,p}=4\times10^{-29}{\rm cm}^6/{\rm s},$ and ignored the BGN effect | 127 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

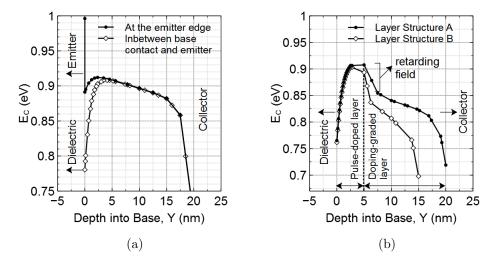

| 5.7  | The conduction-band energy vs. the depth into the base at the extrinsic base of (a) a 20 nm base doping-graded from 12 to 8 $\times 10^{19}  \mathrm{cm}^{-3}$ , and (b) designs with a 5 nm pulse-doped $(1.2 \times 10^{20}  \mathrm{cm}^{-3})$                                                                                                         | 121 |

|      | layer followed by a doping-graded base. Layer structure A has a 15 nm InGaAs graded from 7 to $4 \times 10^{19} \mathrm{cm}^{-3}$ . Layer structure B has a 10 nm InGaAs graded from 5 to $3 \times 10^{19} \mathrm{cm}^{-3}$                                                                                                                             | 130 |

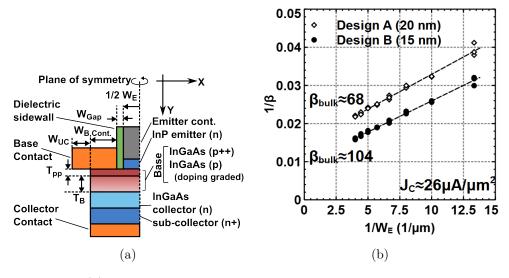

| 5.8  | (a) The Schematic of the simulated SHBTs with a pulse-doped layer. (b) Computed $1/\beta$ vs. $P_{\rm je}/A_{\rm je}$ of the designs at $J_{\rm E} \approx 26{\rm mA}/\mu{\rm m}^2$ . The simulation retained the parameters ( $v_{\rm surf.rec.}$ , $D_{\rm it}$ ,                                                                                       |     |

| 5.9  | $C_{\text{Auger,p}}$ , etc.) of DHBT58H and assumed $W_{\text{gap}}=10 \text{ nm.}$ (a) The Schematic of the simulated SHBTs with the pulse-doped layer removed from the extrinsic base region. (b) Computed $1/\beta$ vs.                                                                                                                                | 130 |

| 5.10 | $P_{\rm je}/A_{\rm je}$ of the designs at $J_{\rm E}\approx 26\sim 29{\rm mA}/\mu{\rm m}^2$ . The simulation retained the parameters ( $v_{\rm surf.rec.}$ , $D_{\rm it}$ , $C_{\rm Auger,p}$ , etc.) of DHBT58H and assumed $W_{\rm gap}=10{\rm nm.}$                                                                                                    | 132 |

|      | $25 \mathrm{mA}/\mu\mathrm{m}^2$ . The simulation retained the parameters ( $v_{\mathrm{surf.rec.}}$ , $D_{\mathrm{it}}$ , $C_{\mathrm{Auger,p}}$ , etc.) of DHBT58H and assumed $W_{\mathrm{gap}}{=}10 \mathrm{nm.}$                                                                                                                                     | 135 |

| 6.1  | The TEM cross-section of a DHBT in bi-layer refractory base contact process flow; device courtesy of J. C. Rode                                                                                                                                                                                                                                           | 145 |

| A.1  | Flow chart of mesa DHBT fabrication.                                                                                                                                                                                                                                                                                                                      | 152 |

## Chapter 1 Introduction

Because of the escalating need for high-speed and low-power wireless communication systems at the radio-frequency (RF), high-performance transistors has been in rising demand for the past few decades. Among various transistor technologies, double-heterojunction bipolar transistors (DHBTs) offers number of advantages over its competitors. Being a vertical device, the key dimensions which determine the transit times are defined by epitaxy, whereas in planar devices such as the field-effect transistors (FETs), the dimensions are defined by lithography, which is limited by the wavelength of the photons or electrons. As a result, the current gain cut-off frequency ( $f_{\tau}$ ) of DHBTs has been rapidly improved over the years [1,2]. Because the current in DHBTs is conducted in the bulk semiconductor rather than in the surface inversion layer of a FET, the carriers are less subjected to scattering due to surface traps. This reduces the trap-induced frequency dispersion and results in lower 1/f noise [3].

Among the materials selections of DHBTs, npn-DHBTs based on the system of In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP has demonstrated superior performance at the near-THz regime [2]. InP DHBTs with the record current/power gain cut-off frequencies  $(f_{\tau}/f_{\rm max})$  of  $\sim 0.5/1$  THz has been reported [4,5], which is higher than the value reported from competing material systems such as GaAs/AlGaAs (< 0.1 THz [6]), and SiGe ( $\sim 0.3/0.4$  THz [7–10]). Comparing with the FET approaches on RF technology, which is dominated by the high electron mobility transistors (HEMTs), InP DHBT gives higher  $f_{\tau}/f_{\rm max}$  than GaN-based HEMT ( $\sim 0.2/0.4$  THz [11,12]). InP-based HEMTs attains similar  $f_{\tau}/f_{\rm max}$  ( $\sim 0.6/1.0$  THz [13, 14]) as InP DHBTs, though InP DHBTs demonstrate higher open-circuit breakdown voltage,  $BV_{\rm CEO}$  [4, 5, 15, 16]. The superior temporal response of InP

system can be attributed to the material properties. Because of high electron mobility and and large  $\Gamma$ -L valley separation in the conduction band of the InP collector [17], the electron could traverse at high velocity, reducing the transit times. Due to the low effective masses in both n- and p-InGaAs [17], the tunnelling probability of carriers is high, which in returns gives lower specific contact resistivity [18], decreasing the parasitic RC delays [2,3]. In addition to high  $f_{\tau}/f_{\text{max}}$ , the wide band gap (1.4 eV) InP collector enables high  $BV_{\text{CEO}}$ , which is crucial for microwave power amplifiers [2]. Moreover, since it is based on the In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP system, DHBTs are compatible with the 1.3 to 1.55  $\mu$ m lightwave communication systems, which makes DHBTs favorable for optical fiber applications [19].

Because of the advantageous RF performance and the compatibility with other InP-base devices, several high performance MMICs utilizing InP DHBTs have been reported to demonstrated the potential of this technology [20,21]. For high-resolution radar/imaging systems, power amplifiers oscillating at ~220 GHz with high output power has been reported [22,23]. For applications in fiber optical communication, a 1-20 GHz phase lock loops (PLLs) has been reported [24] and photonic-electronic integration for wavelength division de-multiplexing (WDM) optical communication systems has been demonstrated [25]. Such architecture has the potential to be scaled beyond the capacity of 1 Tbps [26].

In order to achieve high  $f_{\tau}/f_{\rm max}$ , DHBTs must be scaled epitaxially and lithographically to reduce transit times and RC delays. In addition, because the dimensions of emitter and base contact are nano-scaled, both n- and p-InGaAs are heavily doped to retain low access resistance [2]. Prior to the work reported in this dissertation, the emitter width of InP DHBTs has been successfully scaled to

sub-200 nm [27–29]. Based on this technology, half of this dissertation is dedicated to a reliable device scaling to sub-100 nm emitter width. In response to scaling, the reduction of the DC-current gain ( $\beta = I_{\rm C}/I_{\rm B}$ ) has been observed experimentally among the devices at different scaling nodes [4, 30, 31]. Low  $\beta$  would result in a higher noise figure at the transistor level, causing more noise in microwave amplifiers and high error rate in analog ICs. In order to improve DC- $\beta$  in the future scaling generations of DHBTs, another half of this dissertation is devoted to the modeling of DC- $\beta$  in scaled DHBTs.

In the first half of chapter 2, the theory regarding DHBT scaling will be described. The reduction of DC- $\beta$  accompanying with the scaling will be explained in the second half of chapter 2. Chapter 3 will cover the improvements in DHBT process flow which enable a reliable device scaling to 100 nm emitter width and an environments for enhanced accuracy in RF measurements. The experimental results of two samples, DHBT63B and DHBT58H, will be presented in chapter 4. TEM analysis verified the more controllable emitter process flow at the sub-100 nm emitter width node. DC characteristics of both devices shows that  $\beta$  reduces from 20 to 15 as the emitter width scales from 200 nm to 100 nm. According to this trend, a  $\beta$  <10 can be extrapolated at 75 nm emitter width assuming the current DHBT design process flow is unchanged. The devices reported in this work exhibit  $f_{\tau}/f_{\text{max}}$  of  $\sim$ 500/700 GHz according to RF measurements, which is lower than expected. The parasitic resistance and capacitance will be analyzed to explain the discrepancy between the designed and experimental RF performance.

Using a commercial simulator, the 2-D electron transport in the base of a DHBT has been emulated, allowing the model for DC- $\beta$  in DHBTs to be con-

structed [31, 32]. In chapter 5, the details regarding the current gain model will be addressed. The assumptions and parameters used in the simulation will be justified base on experimental data obtained from DHBT samples. The model indicates that DC- $\beta$  in scaled DHBTs is limited by base current originated from bulk recombination and lateral electron diffusion. In order to suppress the base current and improve  $\beta$ , modifications to the design of base-emitter junction are proposed. The current gain in devices with the modified base-emitter junction has been computed using the established model, and will be presented at the end of chapter 5. If the modifications could be adequately integrated into DHBT fabrication, a device at sub-100 nm emitter node with simultaneously  $\beta$  of 50 [33] and  $f_{\text{max}}$  of 1 THz should be plausible.

## References

- [1] M. J. W. Rodwell, M. Urteaga, T. Mathew, D. Scotts, D. Mensa, Q. Lee, J. Guthrie, Y. Betser, S. C. Martin, R. P. Simth, S. Jaganathan, S. Krishnan, S. I. Long, L. Pullela, B. Agarwal, U. Bhattacharya, L. Samoska, and M. Dahlström, "Submicron scaling of HBTs," *IEEE Trans. Electron Devices*, vol. 48, p. 2606, Nov. 2001.

- [2] M. J. W. Rodwell, M. Le, and B. Brar, "InP Bipolar ICs: Scaling Roadmaps, Frequency Limits, Manufacturable Technologies," *Proc. IEEE*, vol. 92, pp. 271–286, Feb. 2008.

- [3] J. S. Yuan, SiGe, GaAs, and InP Heterojunction Bipolar Transistors. Wiley, 1999.

- [4] V. Jain, J. C. Rode, H. W. Chiang, A. Baraskar, E. Lobisser, B. J. Thibeault, M. J. W. Rodwell, M. Urteaga, D. Loubychev, A. Snyder, Y. Wu, J. M. Fastenau, and W. Liu, "1.0 THz  $f_{\rm max}$  InP DHBTs in a refractory emitter and self-aligned base process for reduced base access resistance," in 69th IEEE Device Research Conference, Jun. 2011.

- [5] M. Urteaga, R. Pierson, P. Rowell, V. Jain, E. Lobissor, and M. J. W. Rodwell, "130 nm InP DHBTs with  $f_{\tau} > 0.52 \,\text{THz}$  and  $f_{\text{max}} > 1.1 \,\text{THz}$ ," in 69th IEEE Device Research Conference, Jun. 2011.

- [6] P. M. Asbeck, M. F. Chang, W. K. C., D. L. Miller, G. J. Sullivan, N. H. Sheng, E. Sovero, and J. A. Higgins, "Heterojunction Bipolar Transistors for Microwave and Millimeter-wave Integrated Circuits," *IEEE Trans. Microw. Theory Techn.*, vol. 35, p. 1462, Dec. 1987.

- [7] J.-S. Rieh, B. Jagannathan, H. Chen, K. Schonenberg, S.-J. Jeng, M. Khater, D. Ahlgren, G. Freeman, and S. Subbanna, "Performance and design considerations for high speed SiGe HBTs of  $f_{\tau}/f_{\rm max}$ =375 GHz/210 GHz," in 15th International Conference on Indium Phosphide and Related Materials, May. 2003.

- [8] P. Chevalier, F. Pourchon, T. Lacave, G. Avenier, Y. Campidelli, L. Depoyan, G. Troillard, M. Buczko, D. Gloria, D. Celi, C. Gaquiere, and A. Chantre, "A Conventional double-polysilicon FSA-SEG Si/SiGe:C HBT reaching 400 GHz f<sub>max</sub>," in 2009 Bipolar/BiCMOS Circuits and Technology Meeting, Oct. 2009.

- [9] S. Van Huylenbroeck, A. Sibaja-Hernandez, R. Venegas, S. You, G. Winderickx, D. Radisic, W. Lee, P. Ong, T. Vandeweyer, N. Nguyen, K. De Meyer,

- and S. Decoutere, "A 400 GHz  $f_{\text{max}}$  fully self-aligned SiGe:C HBT architecture," in 2009 Bipolar/BiCMOS Circuits and Technology Meeting, Oct. 2009.

- [10] R. A. Camillo-Castillo, Q. Z. Liu, J. W. Adkisson, M. H. Khater, P. B. Gray, V. Jain, R. K. Leidy, J. J. Pekarik, J. P. Gambino, B. Zetterlund, C. Willets, C. Parrish, S. U. Engelmann, A. M. Pyzyna, P. Cheng, and D. L. Harame, "SiGe HBTs in 90 nm BiCMOS Technology demonstrating 300 GHz/420 GHz  $f_{\tau}/f_{\rm max}$  through reduced  $R_{\rm b}$  and  $C_{\rm cb}$  parasitics," in 2013 Bipolar/BiCMOS Circuits and Technology Meeting, Oct. 2013.

- [11] K. Shinohara, A. Corrion, D. Regan, I. Milosavljevic, D. Brown, S. Burnham, P. Willadsen, C. Butler, A. Schmitz, D. Wheeler, A. Fung, and M. Micovic, "220 GHz  $f_{\tau}$  and 400 GHz  $f_{\text{max}}$  in 40-nm GaN DH-HEMTs with regrown ohmic,," in 2010 International Electron Devices Meeting, Dec. 2010.

- [12] D. Denninghoff, J. Lu, E. Ahmadi, S. Keller, and U. K. Mishra, "N-polar GaN/InAlN/AlGaN MIS-HEMTs with 1.89 S/mm extrinsic transconductance, 4 A/mm drain current, 204 GHz  $f_{\tau}$  and 405 GHz  $f_{\text{max}}$ ," in 71th IEEE Device Research Conference, Jun. 2013.

- [13] D.-H. Kim, J. del Alamo, P. Chen, W. Ha, M. Urteaga, and B. Brar, "50-nm E-mode  $In_{0.7}Ga_{0.3}As$  PHEMTs on 100-mm InP substrate with  $f_{max} > 1$  THz," in 2010 International Electron Devices Meeting, Dec. 2010.

- [14] D.-H. Kim, B. Brar, and J. del Alamo, " $f_{\tau} = 688\,\mathrm{GHz}$  and  $f_{\mathrm{max}} = 800\,\mathrm{GHz}$  in  $L_{\mathrm{g}} = 40\,\mathrm{nm}\,\,\mathrm{In_{0.7}Ga_{0.3}As}$  MHEMTs with  $g_{\mathrm{m_{max}}} > 2.7\,\mathrm{mS}/\mu\mathrm{m}$ ," in 2011 International Electron Devices Meeting, Dec. 2011.

- [15] M. Feng and W. Snodgrass, "InP Pseudormorphic Heterojunction Bipolar Transistor (PHBT) With  $f_{\tau} > 750 \, \mathrm{GHz}$ ," in 19th International Conference on Indium Phosphide and Related Materials, May. 2007.

- [16] W. Snodgrass and M. Feng, "Nano-scale Type-II InP/GaAsSb DHBTs to Reach THz Cutoff Frequencies," in 2008 International Conference on Compund Semoconductor Manufacturing Technology, Apr. 2008.

- [17] I. Vurgaftman, J. Meyer, and L. Ram-Mohan, "Band parameters for III V compound semiconductors and their alloys," J. Appl. Phys., vol. 89, p. 5815, Jun. 2001.

- [18] A. Baraskar, A. C. Gossard, and M. J. W. Rodwell, "Lower limits to metal-semiconductor contact resistance: Theoretical models and experimental data," J. Appl. Phys., vol. 114, p. 154516, Oct. 2013.

- [19] T. Enoki, E. Sano, and T. Ishibashi, Prospects of InP-based IC technologies for 100-Gbit/s-class lightwave communications systems. World Scientific, 2001.

- [20] J. Hacker, M. Seo, A. Young, Z. Griffith, M. Urteaga, T. B. Reed, M. J. W. Rodwell, and M. Field, "THz MMICs based on InP HBT Technology," in 2010 MTT-S International Microwave Symposium Digest (MTT), May 2010.

- [21] L. A. Coldren, M. Lu, H.-C. Park, E. Bloch, J. S. Parker, L. A. Johansson, and M. J. W. Rodwell, "New Opportunities for Optical Phase-locked Loops in Coherent Photonics," in 2013 Conference on Optical Fiber Communication, Mar. 2013.

- [22] Z. Griffith, T. B. Reed, M. J. W. Rodwell, and M. Field, "A 220 GHz Solid-State Power Amplifier MMIC with 26.8 dB  $S_{21}$  Gain, and 55.5 mW  $P_{\rm out}$  at 17.0 dB Compressed Gain ," in 2013 International Microwave Symposium, Jun. 2013.

- [23] T. B. Reed, Z. Griffith, P. Rowell, M. Field, and M. J. W. Rodwell, "A 180mW InP HBT Power Amplifier MMIC at 214 GHz," in *IEEE Compound Semiconductor IC Symposium*, Oct. 2013.

- [24] E. Bloch, H.-C. Park, T. B. Lu, M. Reed, Z. Griffith, L. A. Johansson, L. A. Coldren, D. Ritter, and M. J. W. Rodwell, "A 120 GHz InP HBT phase-lock-loop IC for optical wavelength synthesis," in 2012 MTT-S International Microwave Symposium Digest (MTT), Jun. 2012.

- [25] M. Lu, J. S. Park, H.-C.and Parker, E. Bloch, A. Sivananthan, Z. Griffith, L. A. Johansson, M. J. W. Rodwell, and L. A. Coldren, "A Heterodyne Optical Phase-locked Loop for Multiple Applications," in 2013 Conference on Optical Fiber Communication, Mar. 2013.

- [26] H.-C. Park, M. Piels, E. Bloch, M. Lu, A. Sivananthan, Z. Griffith, L. Johansson, J. E. Bowers, L. A. Coldren, and M. J. W. Rodwell, "Integrated Circuits for Wavelength Division De-multiplexing in the Electrical Domain," in *European Conference on Optical Fiber Communication*, Sep. 2013.

- [27] V. Jain, E. Lobisser, A. Baraskar, B. J. , Thibeault, M. J. W. Rodwell, Z. Griffith, M. Urteaga, D. Loubychev, A. Snyder, Y. Wu, J. M. Fastenau, and W. K. Liu, "InGaAs/InP DHBTs in a Dry-Etched Refractory Metal Emitter Process Demonstrating Simultaneous  $f\tau/f\max \sim 430/800\,\mathrm{GHz}$ ," *IEEE Electron Device Lett.*, vol. 32, pp. 24–26, Jan. 2011.

- [28] E. Lind, A. M. Crook, Z. Griffith, M. J. W. Rodwell, X.-M. Fang, D. Loubychev, Y. Wu, J. M. Fastenau, and W. Liu, "560 GHz  $f_{\tau}$ ,  $f_{\text{max}}$  InGaAs/InP DHBT in a novel dry-etched emitter process," in 65th IEEE Device Research Conference, Jun. 2007.

- [29] E. Lobisser, J. C. Rode, V. Jain, H. Chiang, A. Baraskar, W. J. Mitchell, B. J. Thibeault, and M. J. W. Rodwell, "InGaAs/InP DHBTs with Emitter and Base Defined through Electron-Beam Lithography for Reduced C<sub>cb</sub> and Increased RF Cut-off Frequency," in 39th International Symposium on Compound Semiconductors, Aug. 2012.

- [30] Z. Griffith, E. Lind, and M. J. W. Rodwell, "Sub-300nm InGaAs/InP Type-I DHBTs with a 150 nm collector, 30 nm base demonstrating 755 GHz  $f_{\text{max}}$  and 416 GHz  $f_{\tau}$ ," in 19th International Conference on Indium Phosphide and Related Materials, May. 2007.

- [31] H. W. Chiang, J. C. Rode, P. Choudhary, and M. J. W. Rodwell, "Lateral Carrier Diffusion and Current Gain in THz InGaAs/InP DHBTs," J. Appl. Phys., vol. 115, p. 034513, Jan. 2014.

- [32] H. W. Chiang, J. C. Rode, P. Choudhary, and M. J. W. Rodwell, "Interfacial transport and current gain in InGaAs/InP DHBTs for THz applications," in 72nd IEEE Device Research Conference, Jun. 2014.

- [33] H. W. Chiang, J. C. Rode, P. Choudhary, and M. J. W. Rodwell, "Optimization of DC performance in terahertz InGaAs/InP double-heterojunction bipolar transistors," *J. Appl. Phys.*, submitted.

# Chapter 2 DHBT Theory

In this chapter, the theory and the designs of mesa-DHBTs for THz applications will be examined from two aspects: RF and DC characteristics. The structure of the state of the art mesa-DHBT will be briefly described. The transit times and RC delays associated with the parasitic resistance and capacitance will be discussed. The expressions of two important figures of merit, current gain  $(H_{21})$  cut-off frequency,  $f_{\tau}$ , and the power gain (unilateral Mason's gain, U) cut-off frequency,  $f_{\text{max}}$ ), will be given. From the expressions, the scaling law of DHBTs to achieve higher  $f_{\tau}$  and  $f_{\text{max}}$  will be defined. As the transistor scales, the DC-current gain  $(\beta)$  decreases. To investigate the decrease of  $\beta$ , various source of the base current will be examined.

## 2.1 Device Structure

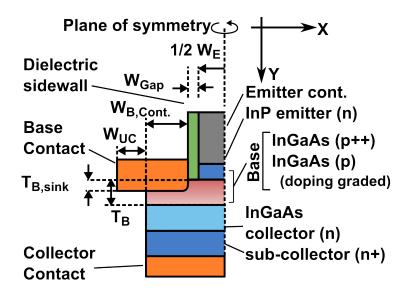

A cross-section of a mesa-DHBT is shown in fig. 2.1a. The refractory metal contact, which defines the base-emitter (B-E) junction, is formed on a heavily doped n-In<sub>0.53</sub>Ga<sub>0.47</sub>As emitter cap. The emitter cap and the n-InP emitter, encapsulated by SiN<sub>x</sub> sidewall, are formed by a wet etch stopped at the doping graded p-In<sub>x</sub>Ga<sub>1-x</sub>As base, after which a self-aligned base contact is deposited on top of the base. Starting from the bottom of the base, the lightly doped n-type collector region is composed of the In<sub>0.53</sub>Ga<sub>0.47</sub>As setback, the In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As superlattice B-C grade, a  $\delta$ -doping, and the InP collector. The setback beneath the base region supplies enough kinetic energy to the electrons for them to cross the B-C grade. The base-collector (B-C) junction, whose area defined by the base

contact, is formed by a wet etch terminated at the heavily doped n-type subcollector. Finally, the collector contact are deposited on the sub-collector.

Fig. 2.1b is the top-down view a mesa-DHBTs. To isolate the devices, the sub-collector and a portion of the semi-insulating substrate in the field are wet etched. To avoid oscillation modes due to the InP substrate, the base ans the collector terminals are raised to the same plane as the emitter via metal posts on the contact pad, after which a transmission line structure is built on top of the device. Fig. 2.1d is the SEM of a device after the front end process.

The important dimensions of a DHBT is shown in fig. 2.1c. Due to symmetry, only half of the cross-section is shown.  $W_{\rm E}$  and  $L_{\rm E}$  is the B-E junction width and length defined by the emitter metal stack. The self-aligned base metals with a width of  $(W_{\rm B,cont.} + W_{\rm UC})$  are deposited on both sides of the emitter. Because of the SiN<sub>x</sub> sidewall, a gap (extrinsic base) is formed between the emitter and the self-aligned base contact. The distance between the emitter and the base contact is  $W_{\rm gap}$ . The base contact penetrates the base semiconductor for a depth of  $T_{\rm B,sink}$  due to the reaction between the base metal and InGaAs [1]. The width of the B-C mesa  $(W_{\rm BM})$  is defined by the widths of the base metal and the emitter. Due to the wet etch undercut  $(W_{\rm UC})$ , the actual width of the base mesa is  $(W_{\rm BM} - 2W_{\rm UC})$ , and the base contact width is  $W_{\rm B,cont.}$ .  $T_{\rm B}$  and  $T_{\rm c}$  are the thickness of base and collector semiconductors, respectively.

Figure 2.1: The structure of mesa-DHBTs. (a) The cross-section of a DHBT. (b) The top-down view of a DHBT. (c) The schematic showing the important dimensions in DHBTs. Only half of the device is shown due to symmetry. (d) The SEM of a experimental device after the front end process.

## 2.2 RF Characteristics and DHBT Scaling Laws

In this section, the design and scaling laws of THz DHBTs will be covered [2]. To understand the scaling laws, the RF characteristics of DHBTs must be addressed. The small-signal equivalent circuit of HBT based on the hybrid- $\pi$  model [3] will be presented. Each delay term will be described, and the expressions of  $f_{\tau}$  and  $f_{\text{max}}$  will be derived using these terms. By reducing the delays through device scaling, the cut-off frequencies of a DHBT can be increased.

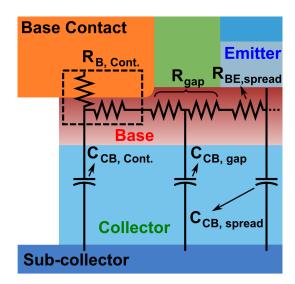

## 2.2.1 Small-signal AC Equivalent Circuit

Fig. 2.2 is the small-signal equivalent circuit of a DHBT in the common emitter configuration approximated by hybrid- $\pi$  model.  $R_{\rm EX}$ ,  $R_{\rm BB}$ , and  $R_{\rm C}$  are the access resistances of the emitter, base, and collector terminals.  $R_{\rm BE}$  and  $C_{\rm BE}$  are the input resistance and capacitance associated with the B-E junction. The feed back components,  $R_{\rm CB}$  and  $C_{\rm CB}$ , are the resistance and capacitance associated with the B-C junction.  $C_{\rm CB}$  is separated into the intrinsic term ( $C_{\rm CB,i}$ ), which is the component in the active region (beneath the B-E junction), and the extrinsic term ( $C_{\rm CB,x}$ ), which accounts for the capacitance of the rest of the B-C mesa.  $g_{\rm m}$  is the device transconductance.  $\tau_{\rm p}$  is the sum of the base transit time ( $\tau_{\rm B}$ ) and collector transit time ( $\tau_{\rm C}$ ).  $C_{\rm CG}$  is the parasitic capacitance of the low-k dielectric resin (BCB) between the ground plane and the collector contact. The aforementioned parasitic terms and the delay associated with them will be discussed in the rest of the section.

Figure 2.2: The small-signal equivalent circuit of a DHBT approximated by the hybrid- $\pi$  model.

## 2.2.2 Base and Collector Transit Time

The base transit time ( $\tau_{\rm B}$ ) and collector transit time ( $\tau_{\rm C}$ ) are critical terms in determining the  $f_{\tau}$ . Because  $f_{\rm max}$  is determined by  $f_{\tau}$ , it is also affected. The transit times depend on the designs of base and collector region. In this section, the relation between the base/collector transit times and the base/collector designs will be discussed.

In DHBTs, the base is usually graded (either via doping or alloy composition), causing an potential difference in the conduction band ( $\Delta E_{\rm C}$ ) between the emitter side and the collector sides of the base, as shown in the band diagram in fig. 2.3. Thus, a quasi-electric field is generated, accelerating the electrons towards the collector region. In the presence of such electric field, the electron transit time in

Figure 2.3: The band diagram of a DHBT in the forward active mode. The band gap narrowing effect and the space charge region in the collector are neglected.

the base region is given by [4]:

$$\tau_{\rm B} = \frac{T_{\rm B}^2}{D_{\rm p}} \frac{kT}{\Delta E_{\rm C}} \left[ 1 - \frac{kT}{\Delta E_{\rm C}} (1 - exp(-\frac{\Delta E_{\rm C}}{kT})) + \frac{T_{\rm B}}{v_{\rm exit}} \frac{kT}{\Delta E_{\rm C}} (1 - exp(\frac{\Delta E_{\rm C}}{kT})), \quad (2.1)$$

where  $D_n = \mu_n kT/q$  is the electron diffusivity, k is the Boltzmann constant, and T is the temperature.  $v_{\text{exit}}$  is the velocity of the electrons leaving the base and entering the collector.

Increasing  $\Delta E_{\rm C}$  reduces  $\tau_{\rm B}$ , and hence improves  $f_{\tau}$  and  $f_{\rm max}$ . The UCSB DHBT designs employ the doping graded base, which generates  $\Delta E_{\rm C} \approx 60 \,\mathrm{meV}$  if the band gap narrowing effect at high doping concentration is ignored. In reality, the band gap narrowing (BGN) effect cannot be neglected [5], which decreases the  $\Delta E_{\rm C}$  induced by the doping grade. As a result,  $\tau_{\rm B}$  is underestimated. Therefore, for base designs with high doping concentration, band gap narrowing effect should

be taken into consideration when calculating  $\tau_{\rm B}$ . Decreasing the base thickness,  $T_{\rm B}$ , also reduces  $\tau_{\rm B}$ . However, the base metal penetrates the InGaAs base for certain depth  $(T_{\rm B,sink})$  [1], as shown in fig. 2.1c. Thus, the B-C junction could be shorted if the base is too thin, i.e. when  $T_{\rm B} \approx T_{\rm B,sink}$ . According to the TEM analysis in chapter 4,  $T_{\rm B,sink} > 5\,\mathrm{nm}$  for Pt/Ti/Pd/Au base contact. In order to decrease  $T_{\rm B}$  without a shunt B-C junction, refractory metal should be used to replace Pt/Ti/Pd/Au for a shorter  $T_{\rm B,sink}$ .

The collector transit time ( $\tau_{\rm C}$ ) can be obtained using the charge control analysis. As more electrons are being injected into the collector due to an increase in the collector current ( $\Delta I_{\rm C}$ ), a sheet of charge is induced at the collector side of the base ( $\Delta Q_{\rm C}$ ).  $\tau_{\rm C}$  is defined as the amount of time required for  $\Delta I_{\rm C}$  to charge this induced  $\Delta Q_{\rm C}$ , i.e.

$$\tau_{\rm C} = \frac{\Delta Q_{\rm C}}{\Delta I_{\rm C}} = \int_0^{T_{\rm C}} \frac{1 - x/T_{\rm C}}{v(x)} dx = \frac{T_{\rm C}}{2v_{\rm eff}} ,$$

(2.2)

where v(x) and  $v_{\rm eff.}$  are the position-dependent and effective velocities in the collector. If electrons accumulates enough kinetic energy as they traverse through the collector, they may scatter from the  $\Gamma$ -valley into the L-valley in the conduction band. Because the velocity in the L-valley is lower,  $v_{\rm eff.}$  decreases and  $\tau_{\rm C}$  increases. For InGaAs and InP, the energy differences between the  $\Gamma$ - and the L-valleys, are 0.55 and 0.6 eV, respectively. Because of the large separations, the  $\Gamma$ -L scattering is less likely to occur in InP DHBTs [6].

## 2.2.3 Emitter Charging Time

The input capacitance,  $C_{\rm BE}$ , in fig. 2.2 can be separated into two terms: the diffusion capacitance,  $C_{\rm Diff.} = g\tau_{\rm p}$ , and the depletion capacitance of the B-E junction,  $C_{\rm je}$ . Because the base is heavily doped, the depletion region in the base can be neglected. The depletion term is given by:

$$C_{\rm je} = \frac{\epsilon_0 \epsilon_{\rm r} A_{\rm je}}{T_{\rm E,dep.}} , \qquad (2.3)$$

where  $\epsilon_0$  and  $\epsilon_r$  are the vacuum permittivity and the relative permittivity of InP ( $\epsilon_r \approx 13$  [7]).  $T_{\rm E,dep.}$  is the depletion region depth in the InP emitter.

The device transconductance,  $g_{\rm m}$ , is defined as:

$$g_{\rm m} = \frac{\partial I_{\rm C}}{\partial V_{\rm BE}} = \frac{qI_{\rm E}}{\eta kT} ,$$

(2.4)

where  $\eta$  is the ideality factor. The values of  $g_{\rm m}$  and  $\eta$  are usually obtained from the real part of the network expression,  $Y_{21}$ , measured at low frequency, which can be written as [8]:

$$\frac{1}{Re(Y_{21})} = R_{\rm EX} + \frac{R_{\rm BB}}{\beta} + \frac{\eta kT}{qI_{\rm E}} , \qquad (2.5)$$

where  $\beta$  is obtained from DC measurements. From the slope of inverse  $Re(Y_{21})$  vs. inverse  $I_{\rm E}$ ,  $\eta$  can be extrapolated.

The charging delay associated with  $C_{je}$  and g is

$$\frac{C_{\rm je}}{g_{\rm m}} = \frac{\eta kT}{qI_{\rm E}}C_{\rm je} \ . \tag{2.6}$$

## 2.2.4 Collector Charging Time

There is also the delay  $(R_{\rm EX} + R_{\rm C} + 1/g_{\rm m})C_{\rm CB}$ , in order to charge the feedback capacitance,  $C_{\rm CB}$ . The value of  $C_{\rm CB}$  is obtained from the imaginary part of  $Y_{12}$  in the network expression [9], i.e.

$$Im(Y_{21}) = \omega(C_{CB,i} + C_{CB,x})$$

(2.7)

$C_{\rm CB}$  includes terms associated with the static and the mobile (space) charge in depletion region of the base-collector junction, which can be written as

$$C_{\text{CB}} = \frac{dQ_{\text{C}}}{dV_{\text{CB}}} = \frac{\epsilon_0 \epsilon_{\text{r}} A_{\text{C}}}{T_{\text{C,eff}}} - \frac{\partial (I_{\text{C}} \tau_{\text{C}})}{\partial V_{\text{CB}}}$$

$$= \frac{\epsilon_0 \epsilon_{\text{r}} A_{\text{C}}}{T_{\text{C,dep.}}} - I_{\text{C}} \frac{\partial \tau_{\text{C}}}{\partial V_{\text{CB}}} - \tau_{\text{C}} \frac{\partial I_{\text{C}}}{\partial V_{\text{CB}}}$$

$$\approx \frac{\epsilon_0 \epsilon_{\text{r}} A_{\text{C}}}{T_{\text{C,dep.}}} - I_{\text{C}} \frac{\partial \tau_{\text{C}}}{\partial V_{\text{CB}}},$$

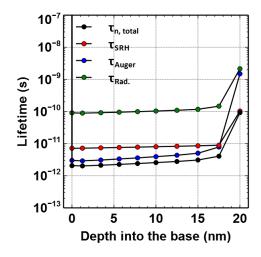

(2.8)