## UNIVERSITY OF CALIFORNIA

### Santa Barbara

## High-Speed Digital ICs in Transferred-Substrate HBT Technology

A Dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Thomas Mathew

Committee in charge:

Professor Stephen I. Long, Chair

Professor Mark J. W. Rodwell

Professor Umesh K. Mishra

Professor Steve E. Butner

August 2001

| Mark J. W. Rodwell               |  |

|----------------------------------|--|

| Umesh K. Mishra                  |  |

| Stave E. Dutman                  |  |

| Steve E. Butner                  |  |

| Stephen I. Long, Committee Chair |  |

The dissertation of Thomas Mathew is approved.

August 2001

High-Speed Digital ICs in Transferred-Substrate HBT Technology

Copyright © 2001

by

Thomas Mathew

#### **ACKNOWLEDGEMENTS**

I would like to thank Prof. Long and Prof. Rodwell for their guidance and support during the course of my graduate school career. The ability of Prof. Long to get to the crux of the problem and his never ending patience has helped me a lot to stay focussed during the course of this work. The energy and enthusiasm of Prof. Rodwell has never ceased to amaze me. I would also like to thank my committee members Prof. Umesh Mishra and Prof. Steve Butner for their patience, encouragement and support. I am also grateful for the opportunity to attend the various courses offered by the faculty members at UCSB. They really helped during the various phases of my research and also made my stay at UCSB a very rewarding experience.

Sharing of information was made possible by the cordial atmosphere maintained in the lab by my colleagues. Special thanks are due to Michelle, Dino, James, Shri, Karthik, David, PK, Yoram, Yun, Dennis, Miguel, Mattias, Navin and Paidi for their suggestions and support during this work. The excellent support received from Jack Whaley, Mike Anzlowar, Bob Hill, and Neil Baker led to the successful fabrication of the ICs described in this work.

My friends at home – Shri, Rahul, Ashish, Karthik, Kamlesh, Anil and Venkat made my stay in Santa Barbara a very memorable one.

This dream was made possible only by the love, support, and sacrifices made by my parents and brothers in India. Words cannot express my gratitude to my wife Manju for being there, and bearing my odd work schedules with a smile.

## VITA OF Thomas Mathew August 2001

#### **EDUCATION**

Doctor of Philosophy (Ph.D) in Electrical and Computer Engineering, University of California, Santa Barbara, 2001 (Expected).

Master of Technology (M.Tech), Electrical and Electronics Engineering, Indian Institute of Technology, Mumbai (Bombay), India, 1996.

Bachelor of Technology (B.Tech), Electronics Engineering, Regional Engineering College, Calicut, Kerala, India, 1992.

#### PROFESSIONAL EMPLOYMENT

1998-2001: Graduate researcher, Department of Electrical and Computer Engineering, University of California, Santa Barbara.

Fall 1997: Teaching Assistant, Department of Electrical and Computer Engineering, University of California, Santa Barbara.

1996-1997: Research Assistant, Department of Electrical and Electronics Engineering, Indian Institute of Technology, Mumbai (Bombay), India

#### **PUBLICATIONS**

- T. Mathew, S. Jagannathan, D. Scott, S. Krishnan, Y. Wei, M. Urteaga, M. Rodwell and S. Long, "2-Bit Adder Carry and Sum Logic Circuits Clocking at 19 GHz Clock frequency in Transferred Substrate HBT Technology" *IEEE Conference on Indium Phosphide and Related Materials*, May 2001.

- 2) T. Mathew, H-J. Kim, D. Scott, S. Jagannathan, S. Krishnan, Y.Wei, M. Urteaga, S. Long and M. J. W. Rodwell, "75 GHz static frequency divider using InAlAs/InGaAs HBTs", *IEE Electronics Letters*, Vol. 37, No. 11, May 2001

- 3) T. Mathew, S. Jagannathan, D. Scott, S. Krishnan, Y. Wei, M. Urteaga, M. Rodwell and S. Long, "2 bit adder: Carry and sum logic circuits at 19 GHz clock frequency in InAlAs/InGaAs HBT technology", Accepted by *IEE Electronics Letters*, August, 2001.

- 4) T. Mathew, H-J. Kim, D. Scott, S. Jagannathan, S. Krishnan, Y.Wei, M. Urteaga, S. Long and M. J. W. Rodwell, "75 GHz static frequency divider in InAlAs/InGaAs transferred-substrate HBT technology", post deadline submission, *IEEE Conference on Indium Phosphide and Related Materials*, May 2001.

- 5) S. Krishnan, M. Dahlstrom, T. Mathew, Y.Wei, D.Scott, M. Urteaga, M. J. W. Rodwell, W.K. Liu, D. Lubyshev, X. M. Fang, Y. Wu, "InP/InGaAs/Inp Double Heterojunction Bipolar Transistors with 300 GHz f<sub>max</sub>", IEEE Conference on Indium Phosphide and Related Materials, May 2001.

- 6) M. Urteaga, D.Scott, T. Mathew, S. Krishnan, Y. Wei, and M. J. W. Rodwell, "185 GHz Monolithic Amplifier in InGaAs/InAlAs Transferred-Substrate HBT Technology", *IEEE MTT-S International Microwave Symposium*, May, 2001

- S. Jagannathan, D. Mensa, T. Mathew, Y. Betser, S. Krishnan, Y.Wei, D. Scott, M. Urteaga, M.Rodwell, "An 18GHz continuous time Σ-Δ modulator implemented in InP transferred-substrate HBT Technology", *IEEE GaAs IC Symposium*, Nov. 2000.

- 8) S. Krishnan, D. Mensa, J. Guthrie, S. Jagannathan, T. Mathew, R. Girish, Y. Wei, M. J. W. Rodwell, "Broadband lumped HBT amplifiers", *IEE Electronics Letters*, March 2000.

- 9) Q. Lee, D. Mensa, J. Guthrie, S. Jagannathan, T. Mathew, Y. Betser, S. Krishnan, S. Ceran, M. J. W. Rodwell, "66 GHz static frequency divider in transferred-substrate HBT technology", *IEEE Radio Frequency Integrated Circuits Symposium*, June 1999

- 10) J. Guthrie, D. Mensa, T. Mathew, Q. Lee, S. Krishnan, S. Jagannathan, S. Ceran, Y. Betser, M. J. W. Rodwell, "A 50 mm copper polymer substrate HBT technology for > 100 GHz MMICs", *IEEE Conference on Indium Phosphide and Related Materials*, May 1999.

- 11) M. Rodwell, Q. Lee, D. Mensa, R. Pullela, J. Guthrie, S. C. Martin, R. P. Smith, S. Jagannathan, T. Mathew, B. Agarwal, S. Long, "48 GHz digital ICs using transferred-substrate HBTs", *IEEE GaAs IC Symposium*, Nov 1998.

#### **ABSTRACT**

### High-Speed Digital ICs in Transferred-Substrate HBT technology

by

#### Thomas Mathew

One of the key electronic component needed for next generation naval radars is the direct digital frequency synthesis (DDFS) block, that is used for signal generation. A key building block in a DDFS system is the phase accumulator (adder-accumulator). The maximum clock rate ( $f_{ck}$ ) of the various building blocks in a DDFS system determines its frequency resolution and tuning range. The frequency tuning range of the DDFS system is from DC to ~ ( $f_{ck}/3$ ) and the frequency resolution is given by  $\Delta f = f_{ck}/2^N$ , where N is the bit length of the phase-accumulator word.

This work presents the design techniques used to improve the clock rate of a 2-bit adder-accumulator circuit, which is used as the building block in an 8-bit pipelined adder accumulator. The first generation design used a wired OR/AND approach in the carry logic (AND-OR) circuit to increase the clock rate. The carry and sum logic circuit of the 2-bit adder was fabricated and tested. Measurements indicated a maximum clock rate of 8 GHz for the carry logic circuit and 14 GHz for the sum logic circuit. The second generation design used a new single 3-level seriesgated logic gate that performed the AND-OR operation needed to realize the carry

logic of a full adder. This carry logic circuit was then merged with the latches to realize a merged AND-OR-Latch circuit. Simulations indicated that this 4-level series-gated structure was 1.8:1 faster when compared to the wired-OR/AND approach. The carry and sum logic of the second-generation 2-bit adder designs were fabricated and tested. Measurements indicated a maximum clock rate of 19 GHz for the carry logic circuit and 24 GHz for the sum logic circuit. A 75 GHz ECL static frequency divider was also fabricated as part of this work.

Attempts to extend a technology, which demonstrated circuits having tens of transistors, to realize circuits having hundreds of transistors, brings forth a new set of failure mechanisms. This work also presents the test structures designed to identify the various failure mechanisms and the statistical data collected from these structures.

## TABLE OF CONTENTS

| I. Introduct | tion                                                             | .1  |

|--------------|------------------------------------------------------------------|-----|

|              | 1.1Motivation                                                    | . 4 |

|              | 1.2 HBT Technology to realize 100 GHz logic: the challenges      | . 6 |

|              | 1.3 Nature and scope of this work                                | . 9 |

|              | 1.4 Thesis organization                                          | 11  |

| II. Synchro  | onous adder architectures                                        | 13  |

|              | 2.1 A full adder (FA)                                            | 14  |

|              | 2.2 Ripple carry adder architecture (RCA)                        | 17  |

|              | 2.3 Carry lookahead adder architecture (CLA)                     | 18  |

|              | 2.4 Pipelined adder architecture                                 | 22  |

|              | 2.5 Initial 8-bit pipelined adder-accumulator design             | 26  |

| III. Design  | of 2-bit adder block                                             | 30  |

|              | 3.1 Design choice for 2-bit adder                                | 31  |

|              | 3.2 Wired-OR approach                                            | 32  |

|              | 3.3 Circuit implementation of Wired-OR and Wired-AND             | 34  |

|              | 3.4 Evaluating maximum clock rate: Test approach                 | 37  |

|              | 3.5 Comparison of Full adder and wired OR approach               | 41  |

|              | 3.6 Gate design considerations                                   | 43  |

|              | 3.7 Measurements and results: first-generation 2-bit adder       | 48  |

|              | 3.8 Design modifications: New 3-level logic gate for carry logic | 56  |

|            | 3.9 Merging the logic evaluation and latching operation          | . 59 |

|------------|------------------------------------------------------------------|------|

|            | 3.10 Final 2-bit adder accumulator design                        | . 64 |

|            | 3.11 Choice of transistor geometry and circuit parameters        | . 65 |

|            | 3.12 Measurements and results: second-generation 2-bit adder     | . 70 |

| IV. Static | frequency divider                                                | . 79 |

|            | 4.1 Static frequency divider: (Method of time constant analysis) | . 80 |

|            | 4.2 Static frequency divider: circuit design                     | . 84 |

|            | 4.3 Results and discussion                                       | . 88 |

| V. Process | sing issues and yield limiting mechanisms                        | . 96 |

|            | 5.1 Emitter lithography and metal deposition                     | . 96 |

|            | 5.2 Base emitter etch and base metal deposition                  | . 97 |

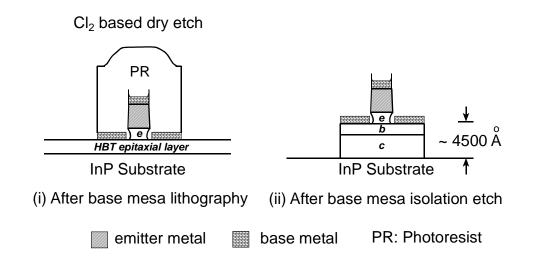

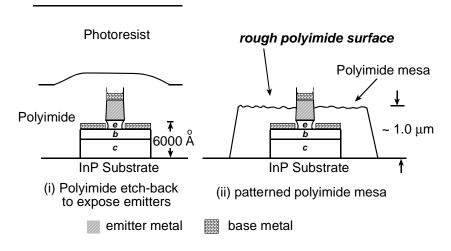

|            | 5.3 Base mesa isolation and polyimide passivation.               | . 99 |

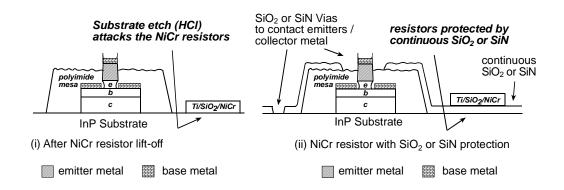

|            | 5.4 Nickel-chromium (NiCr) thin film deposition                  | 100  |

|            | 5.5 First Interconnect level (metal-1) metallization             | 103  |

|            | 5.6 Silicon nitride (SiN) dielectric deposition                  | 106  |

|            | 5.7 Second interconnect level metallization (metal-2)            | 107  |

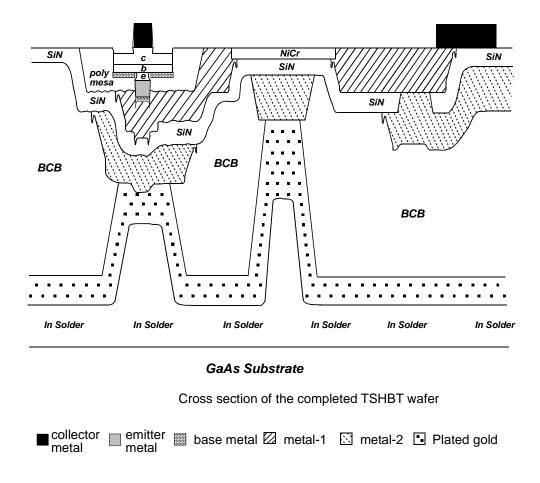

|            | 5.8 Benzocyclobutene etch and substrate transfer                 | 109  |

|            | 5.9 Substrate removal and collector deposition                   | 112  |

|            | 5.10 Possible failure mechanisms                                 | 114  |

|            | 5.11 Conclusions from the yield test structures                  | 125  |

| VI. Conclu | usion                                                            | 127  |

|            | 6.1. Summary of achievements                                     | 127  |

| 6.2 Suggestions for future work | 131 |

|---------------------------------|-----|

| Appendices                      | 134 |

| Bibliography                    | 203 |

## LIST OF FIGURES

| Fig. 1.1: Shown above is the $f_t$ and $f_{\text{max}}$ regime of different HBT technologies |

|----------------------------------------------------------------------------------------------|

| reported in literature [1,2,3,4,5]                                                           |

| Fig. 1.2: Block diagram showing the direct digital frequency synthesis approach 5            |

| Fig. 1.3: The structure of a triple-mesa HBT indicating the relevant intrinsic and           |

| extrinsic device parameters that contribute to device performance                            |

| Fig. 1.4: Approaches used to reduce the extrinsic base-collector capacitance                 |

| $(C_{cbx})$ are shown above. Shown on the left is the selective removal of                   |

| collector region by wet etching. On the right is the transferred-substrate                   |

| approach10                                                                                   |

| Fig. 2.1: Shown in figure above is the addition of two decimal numbers and the               |

| corresponding addition of their binary equivalent. The 'carry over'                          |

| digit/bit is shown encircled                                                                 |

| Fig. 2.2: Logic gate realization of a full adder                                             |

| Fig. 2.3: 4-bit ripple carry adder (RCA) implemented using full adders. The                  |

| worst-case propagation delay path is along the dashed lines                                  |

| Fig. 2.4: A 4-bit carry lookahead adder (CLA) architecture is shown above.                   |

| The gate delays that determine the maximum clock rate is indicated                           |

| on the left hand side. The carry-in bit $C_0 = 0$ because in the first 4-bit                 |

| adder block there is no carry-in from the previous adder block                               |

| Fig. 2.5: A 4-bit pipelined adder realized using full adder logic blocks                     |

| Fig. 2.6: An 8-bit pipelined adder-accumulator realized using 2-bit adder       |

|---------------------------------------------------------------------------------|

| blocks. To configure the adder as an accumulator, the sum output                |

| S is fed back as one of the inputs i.e. $B_i = S_i$                             |

| Fig. 2.7: Chip photograph of the fabricated 8-bit adder-accumulator             |

| (2000 HBTs, non-functional circuit) is shown above                              |

| Fig. 3.1: Shown on the left is the 2-bit adder implemented as 2 cascaded        |

| full adders and on the right is the 2-bit adder implemented as a                |

| carry lookahead adder (CLA). Also shown is the propagation                      |

| delay involved for both schemes                                                 |

| Fig. 3.2: 2-bit adder implementation using wired-OR gate is shown above.        |

| The wired-OR operation is shown within the dashed boxes. The                    |

| details of wired-OR implementation are shown in Fig. 3.3                        |

| Fig. 3.3: The wired OR and wired AND implementation are shown above.            |

| Also shown are the voltage levels for the specific case, $A_i = B_i = High$ ,   |

| $C_i = Low$                                                                     |

| Fig. 3.4: Evaluating the propagation delay of a combinatorial logic block by    |

| configuring it as a frequency divider. Shown on the left is an MS               |

| flip-flop configured as a frequency divider                                     |

| Fig. 3.5: Evaluating the maximum clock rates of the carry and sum logic circuit |

| by configuring them as frequency dividers. Frequency divider operation          |

| is achieved in carry logic circuit by setting the inputs $A_i = A_{i+1} = 1$    |

| and $B_i = B_{i+1} = 0$ and in sum logic circuit by setting $A_i = C_i = 1$ 39  |

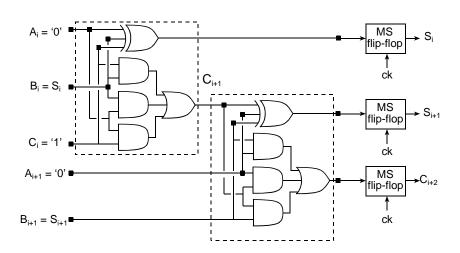

| Fig. 3.6: 2-bit adder-accumulator configured as a binary counter by setting                       |

|---------------------------------------------------------------------------------------------------|

| $A_i = A_{i+1} = \text{`0'}$ and $C_i = \text{`1'}$ . The corresponding simulated output is       |

| shown in Fig. 3.7                                                                                 |

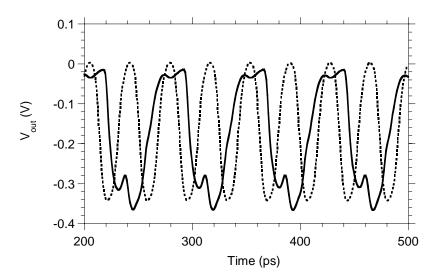

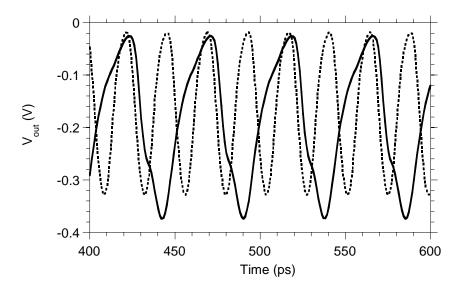

| Fig. 3.7: Simulated sum output waveforms $(S_{i+1},S_i)$ of a 2-bit adder for 19 GHz              |

| clock ( $f_{ck}$ ) input. $S_i$ (dotted line) is at $f_{ck}$ /2, and $S_{i+2}$ (solid line) is at |

| $f_{ck}/4$ . Also shown is the binary output sequence corresponding to the                        |

| output waveforms41                                                                                |

| Fig. 3.8: Simulated output waveform at 12.5 GHz of the carry logic circuit                        |

| configured as a static frequency divider. The clock input (broken line)                           |

| is at 25 GHz                                                                                      |

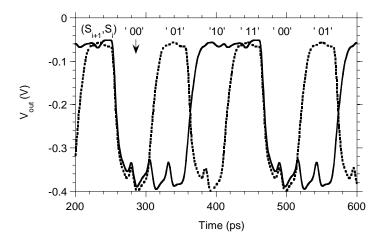

| Fig. 3.9: Simulated output waveform of the 2-bit adder-accumulator circuit                        |

| when configured as a binary counter (setting $A_i = A_{i+1} = \text{`0'}$ and                     |

| $C_i$ = '1'). The input clock frequency is at 24 GHz. $S_i$ (dotted line)                         |

| is at $f_{ck}$ /2, and $S_{i+2}$ (solid line) is at $f_{ck}$ /4                                   |

| Fig. 3.10: Design features of a 2-level logic gate including gate to gate                         |

| interconnects, run as terminated microstrip line is shown above                                   |

| Fig. 3.11: Device geometry of the transistors used in the differential pair.                      |

| Shown shaded is the base-collector area that contributes to the                                   |

| extrinsic base-collector capacitance                                                              |

| Fig. 3.12: Epitaxial layer structure used in this process run is shown above 50                   |

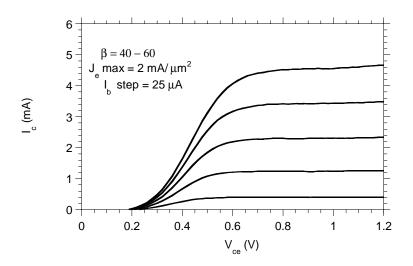

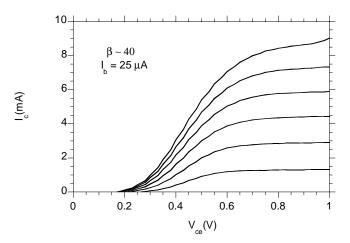

| Fig. 3.13: Common emitter $I_c$ – $V_{ce}$ characteristics of a HBT with emitter dimension        |

| of 4.0 x 0.6 $\mu$ m <sup>2</sup> and collector dimension of 5.0 x 3.0 $\mu$ m <sup>2</sup>       |

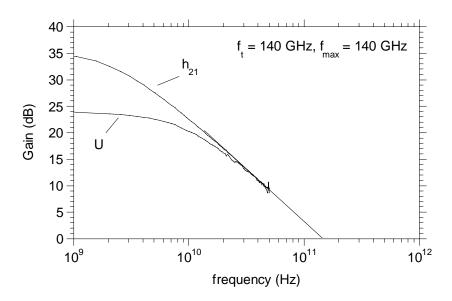

| Fig. 3.14: RF measurement results on a device with emitter dimension                 |

|--------------------------------------------------------------------------------------|

| $4.0~x~0.6~\mu m^2,$ and collector dimension $5.0~x~3.0~\mu m^2$ at $V_{ce}=1.0V$    |

| and $I_c = 5.0 \text{ mA}$                                                           |

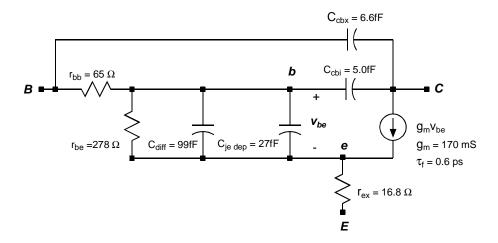

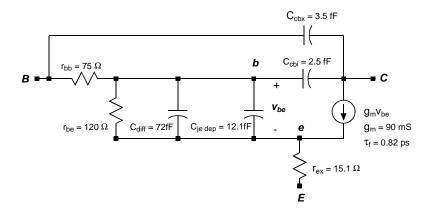

| Fig. 3.15: Hybrid-pi equivalent circuit model of the device The device had           |

| emitter dimension 4.0 x 0.6 $\mu m^2$ and collector dimension of 5.0 x 3.0 $\mu m^2$ |

| and was biased at a $V_{ce}$ of 1.0V and $I_c$ of 5.0 mA                             |

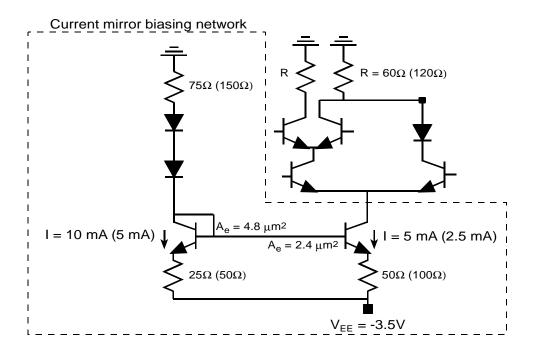

| Fig. 3.16: Current mirror biasing network of the logic gate is shown inside          |

| the dashed box. The measured values of resistors are also shown, with the            |

| design values indicated in parenthesis                                               |

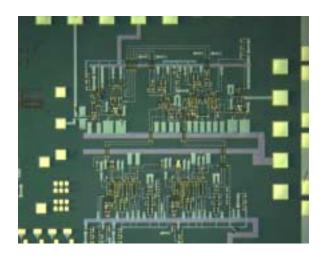

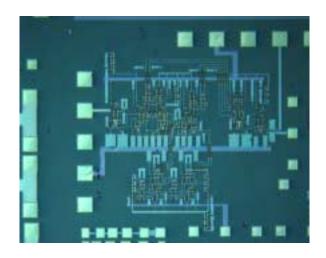

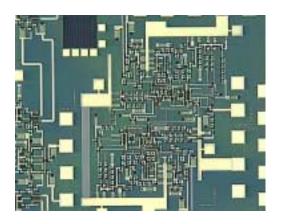

| Fig. 3.17: Chip photograph of the fabricated 2-bit carry logic circuit.              |

| The IC had approximately 250 transistors                                             |

| Fig. 3.18: Chip photograph of the sum logic circuit (approximately 150 HBTs) 54      |

| Fig. 3.19: Measured output waveform of the carry logic circuit of a                  |

| 2-bit adder configured as a frequency divider. The input clock frequency             |

| is 8 GHz, and the output waveform shown above is at 4 GHz55                          |

| Fig. 3.20: Measured output waveform of the sum logic circuit. The input              |

| clock frequency is 14.6 GHz and the output waveform shown above is at                |

| 7.3 GHz55                                                                            |

| Fig. 3.21: A new 3-level series-gated logic gate implementation of the               |

| AND-OR logic to generate the carry-out of a full adder 57                            |

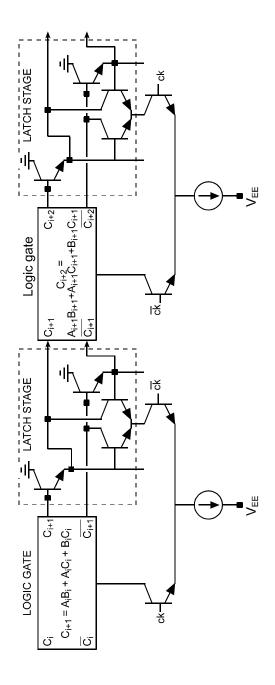

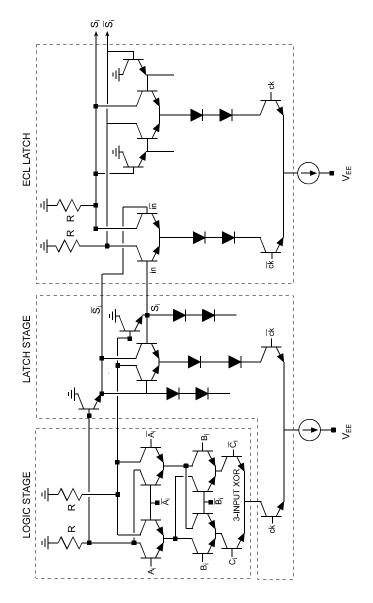

| Fig. 3.22: Carry logic circuit of the 2-bit adder is shown above. To evaluate the                 |   |

|---------------------------------------------------------------------------------------------------|---|

| propagation delay of the carry logic circuit its configured as a frequency                        |   |

| divider by setting $A_i = A_{i+1} = '1'$ , $B_i = B_{i+1} = '0'$ , and $C_i = \overline{C_{i+2}}$ | 8 |

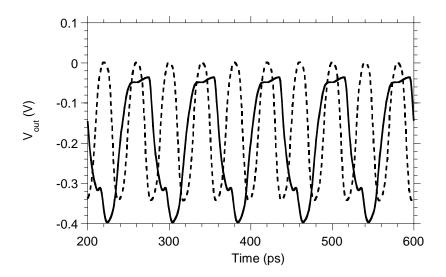

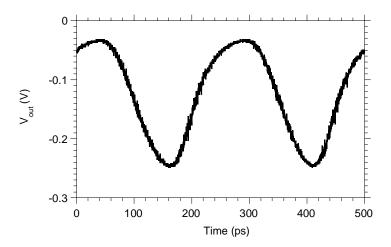

| Fig. 3.23: Simulated output waveform of the 2-bit carry logic circuit when                        |   |

| configured as a frequency divider. The input clock frequency is 27 GHz,                           |   |

| and the output frequency is 13.5 GHz59                                                            | 9 |

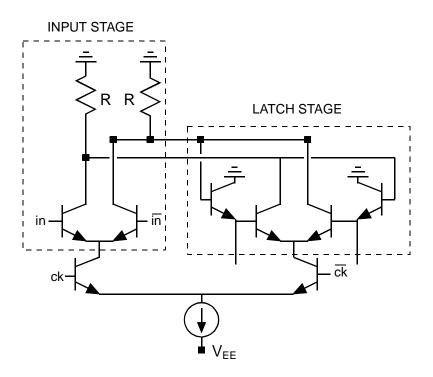

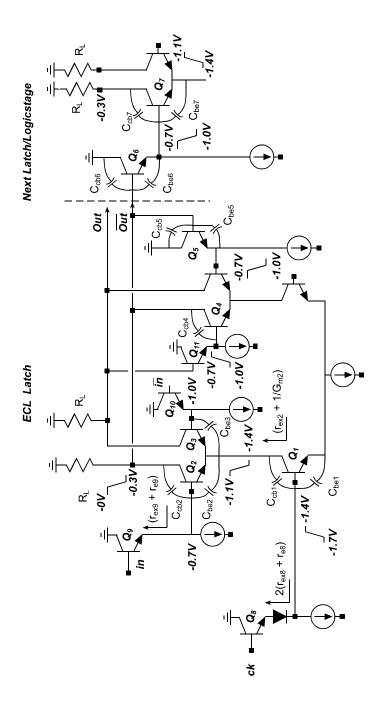

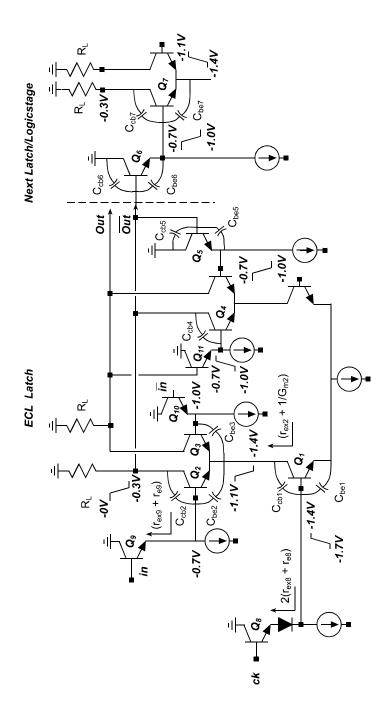

| Fig. 3.24: Circuit diagram of the ECL latch showing the input stage and the                       |   |

| latching stage. The pull-down current sources of the emitter followers are                        |   |

| not shown in the above figure61                                                                   | 1 |

| Fig. 3.25: Merging the AND-OR logic gate (Fig.3.21) with the ECL latch in                         |   |

| the carry logic circuit of the 2-bit adder                                                        | 2 |

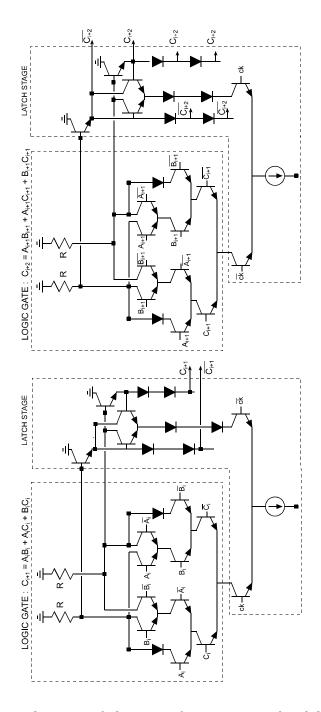

| Fig. 3.26: Circuit diagram of the carry logic circuit of a 2-bit adder using the                  |   |

| merged AND-OR-Latch approach63                                                                    | 3 |

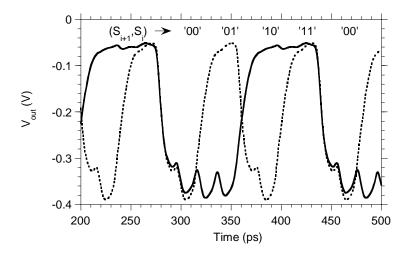

| Fig. 3.27: Simulated output waveform at 42 GHz for the 2-bit carry logic                          |   |

| circuit when configured as a frequency divider                                                    | 4 |

| Fig. 3.28: Circuit diagram of the sum logic circuit by merging the XOR                            |   |

| logic gate with the MS flip-flop                                                                  | 5 |

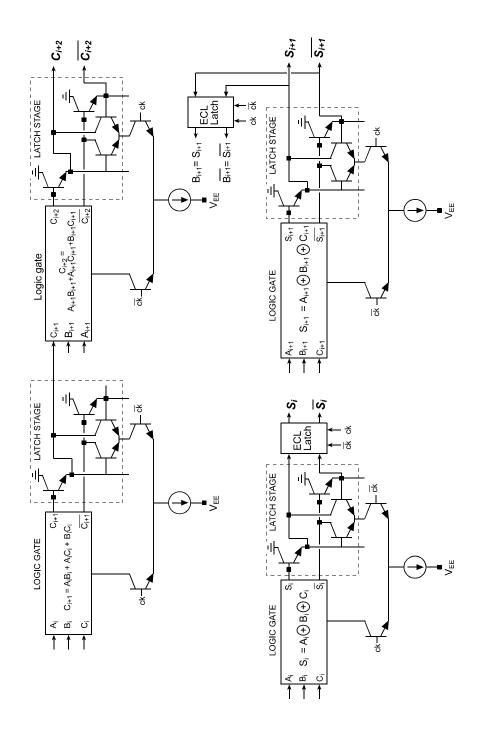

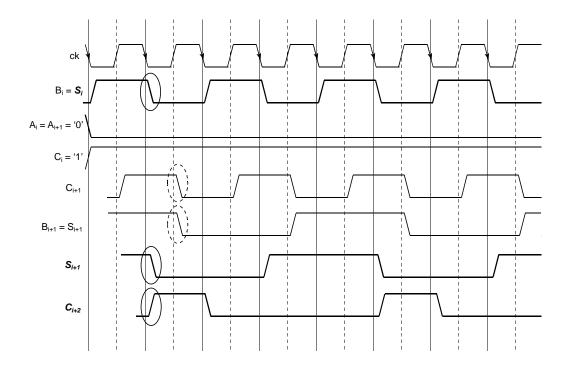

| Fig. 3.29: Block diagram of the final 2-bit adder design                                          | 7 |

| Fig. 3.30: Timing diagram of the 2-bit adder circuit                                              | 8 |

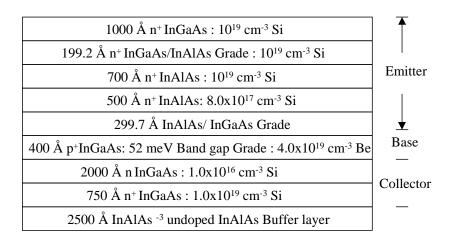

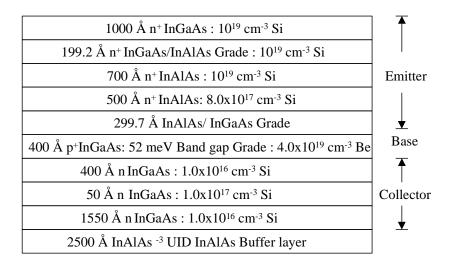

| Fig. 3.31: Epitaxial layer structure used in this work                                            | 2 |

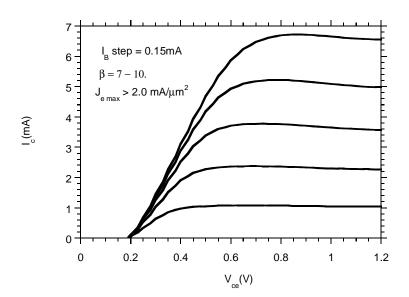

| Fig. 3.32: Common emitter DC I-V curves for a 3.0 x 1.0 μm <sup>2</sup> emitter and     |

|-----------------------------------------------------------------------------------------|

| $5.0~x~2.0~\mu\text{m}^2$ collector device. The current gain $\beta$ is between 5 to 10 |

| across the wafer                                                                        |

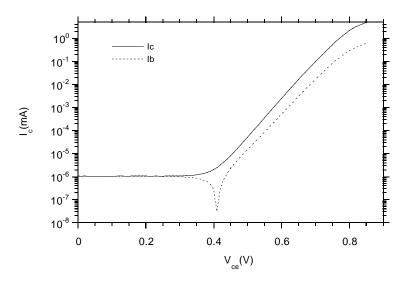

| Fig. 3.33: Gummel plot of a 3.0 x 1.0 $\mu m^2$ emitter and 5.0 x 2.0 $\mu m^2$         |

| collector device                                                                        |

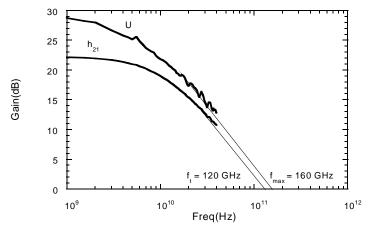

| Fig. 3.34: RF measurements of a 3.0 x 1.0 $\mu m^2$ emitter and 5.0 x 2.0 $\mu m^2$     |

| collector device biased at $V_{ce} = 1.0 \text{ V}$ and $I_c = 3 \text{ mA}$            |

| Fig. 3.35: Hybrid-pi equivalent circuit of the device. The device had emitter           |

| dimension 3.0 x 1.0 $\mu m^2$ and collector dimension of 5.0 x 2.0 $\mu m^2$ and was    |

| biased at a V <sub>ce</sub> of 1.0V and I <sub>c</sub> of 3.0mA74                       |

| Fig. 3:36: Effect of low current gain $\beta$ on the current source biasing circuitry.  |

| The low $\beta$ results in a significant base current component that reduces the        |

| value of I <sub>cs</sub> from its designed value                                        |

| Fig. 3.37: Chip photograph of the fabricated 2-bit carry logic circuit (200 HBTs) 76    |

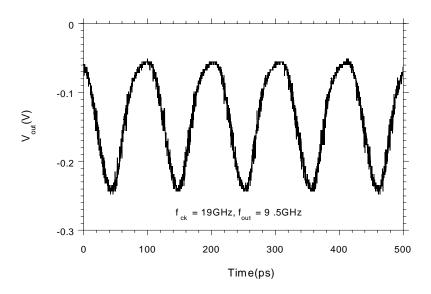

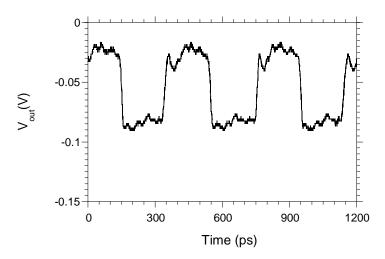

| Fig. 3.38: Measured output waveform of the 2-bit carry logic circuit                    |

| for 19 GHz clock input. The output waveform is at 9.5 GHz76                             |

| Fig. 3.39: Chip photograph of the fabricated sum logic circuit (150 HBTs)77             |

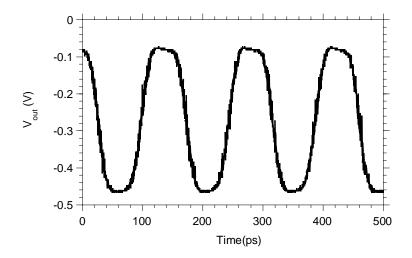

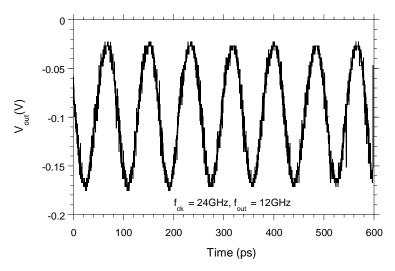

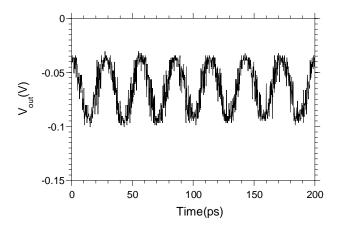

| Fig. 3.40: Measured output waveform of the sum logic circuit for 24 GHz                 |

| clock input. The output waveform is at 12 GHz77                                         |

| Fig. 3.41: Chip photograph of a fabricated (non-functional) 2-bit adder circuit 78      |

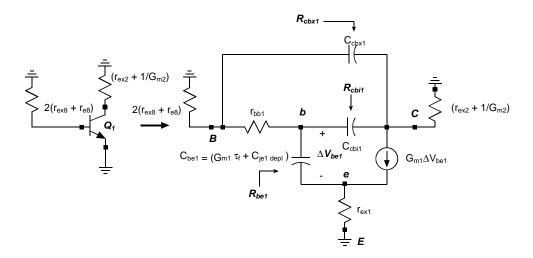

| Fig. 4.1: Circuit diagram of an ECL latch showing the relevant capacitances             |

| in the signal propagation path. The base emitter and base-collector                     |

| capacitances contributing to the signal propagation delay are shown                             |

|-------------------------------------------------------------------------------------------------|

| external to the transistor                                                                      |

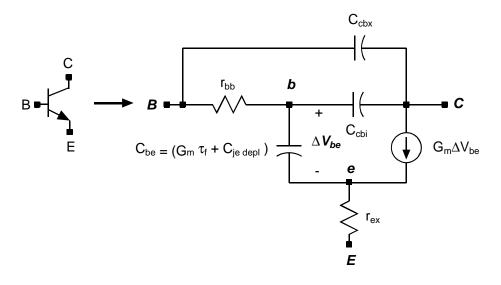

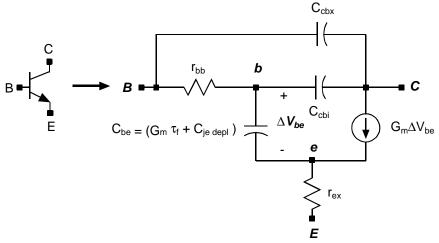

| Fig. 4.2: Hybrid-pi equivalent circuit used to represent the HBTs                               |

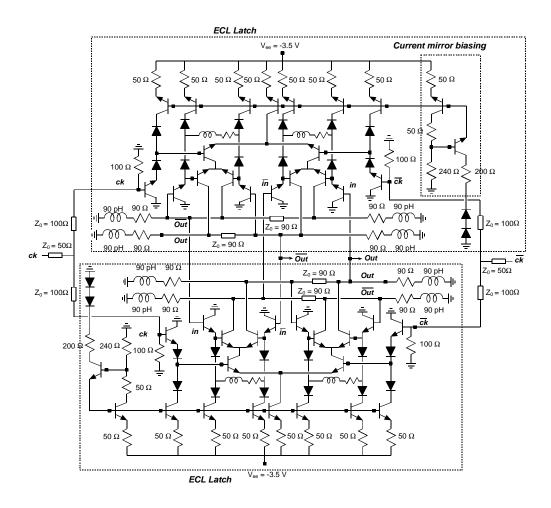

| Fig. 4.3: Circuit diagram of the static frequency divider circuit                               |

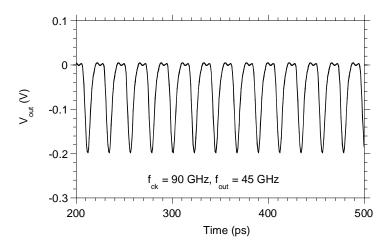

| Fig. 4.4: Simulated output waveform of the static frequency divider for                         |

| 90 GHz clock input88                                                                            |

| Fig. 4.5: Epitaxial layer structure used to fabricate the static frequency divider 89           |

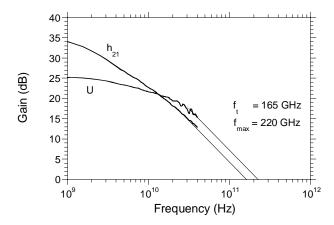

| Fig. 4.6: Common emitter I – V curves for a transistor with emitter dimension                   |

| of 6.0 x 1.0 $\mu$ m <sup>2</sup> , and collector geometry of 7.0 x 2.0 $\mu$ m <sup>2</sup> 90 |

| Fig. 4.7: RF measurements of a transistor biased at a $V_{ce}$ of 1.0 V and                     |

| $I_c$ of 6 mA (emitter dimension of 6.0 x 1.0 $\mu m^2$ , and collector                         |

| dimension of 7.0 x 2.0 µm <sup>2</sup> )90                                                      |

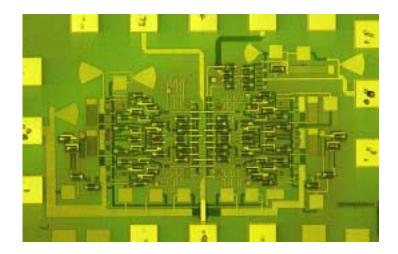

| Fig. 4.8: Chip photograph of the fabricated static frequency divider circuit91                  |

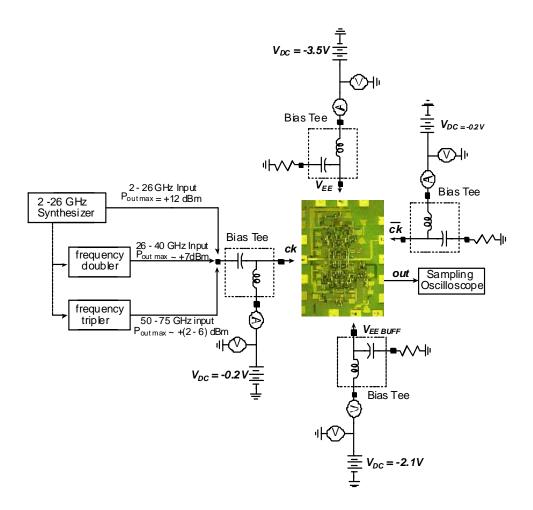

| Fig. 4.9: Measurement set-up of the static frequency divider circuit                            |

| Fig. 4.10: Measured output waveform for a 5 GHz clock input. The output                         |

| waveform is at 2.5 GHz94                                                                        |

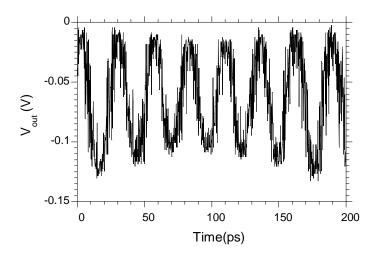

| Fig. 4.11: Measured output waveform for 69 GHz clock input.                                     |

| The output waveform is at 34.5 GHz94                                                            |

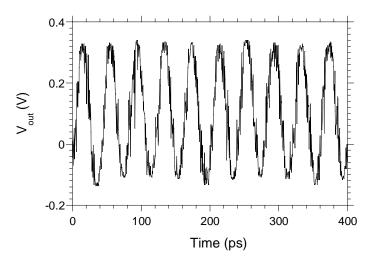

| Fig. 4.12: Measured output waveform at 37.5 GHz for a 75 GHz clock input 95                     |

| Fig. 4.13: Measured RF output waveform of the 2-26 GHz synthesizer at 25 GHz.                   |

| Note the presence of the 6.0 GHz modulation of the waveform                                     |

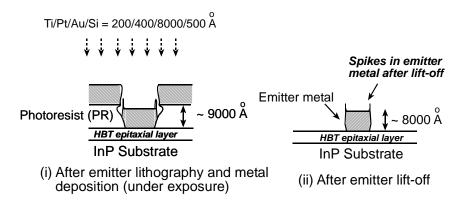

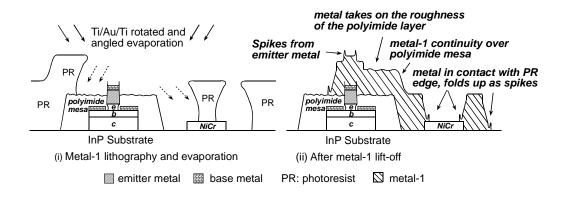

| Fig. 5.1: Cross section of the wafer during and after emitter metal                  |

|--------------------------------------------------------------------------------------|

| deposition. Note the presence of emitter spikes. This is the result                  |

| of an underexposed photoresist profile                                               |

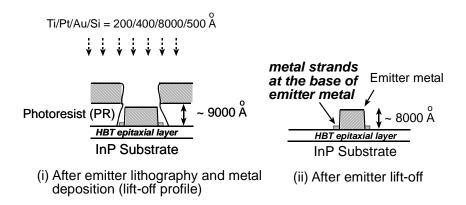

| Fig. 5.2: Cross section of the wafer during and after emitter metal                  |

| deposition. Note the presence of metal strands at the base of the                    |

| emitter metal due to the lift-off profile                                            |

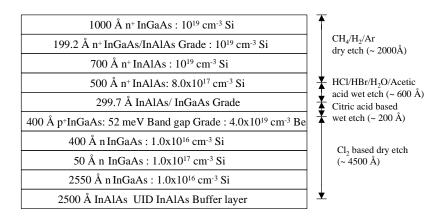

| Fig. 5.3: The HBT epitaxial layer structure showing the various etch stop points 100 |

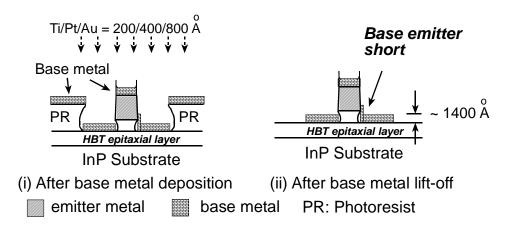

| Fig. 5.4: Self-aligned base metallization and the possibility of                     |

| base-emitter shorts                                                                  |

| Fig. 5.5: Cross section of the wafer after the base mesa isolation etch              |

| Fig. 5.6: Device cross section after the base mesa isolation and                     |

| polyimide device passivation step                                                    |

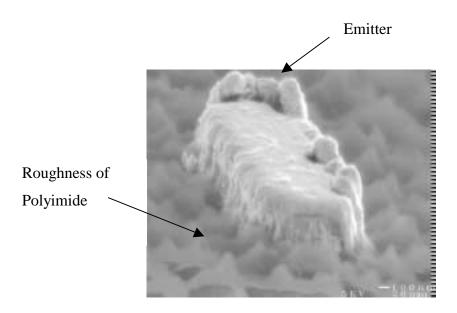

| Fig. 5.7: SEM picture showing the roughness of the polyimide layer 102               |

| Fig. 5.8: Wafer cross section after NiCr resistor deposition and lift-off.           |

| Shown on the right side is how the cross section looks if a resistor                 |

| protection layer is added prior to resistor deposition                               |

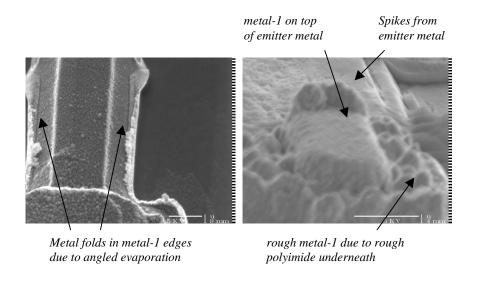

| Fig. 5.9: Device cross section during and after metal-1 deposition and lift-off 105  |

| Fig. 5.10: SEM pictures showing the features on metal-1 after lift-off 105           |

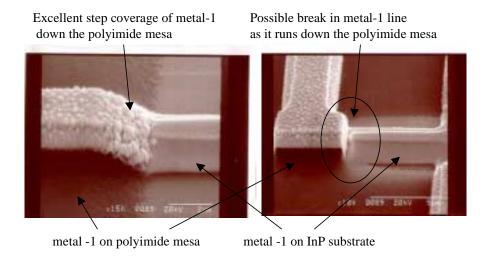

| Fig. 5.11: SEM picture showing both continuous as well as possible                   |

| discontinuous metal-1 step coverage over polyimide mesa                              |

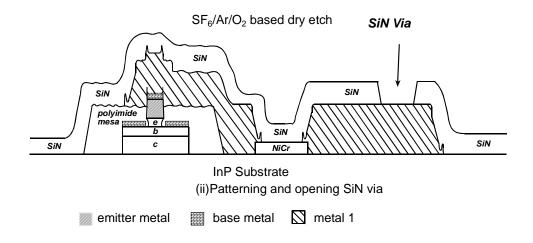

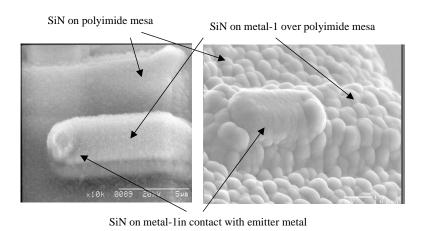

| Fig. 5.12: Wafer cross section after SiN deposition and patterning                   |

| Fig. 5.13: SEM picture taken after SiN deposition. The SEM picture shown           |

|------------------------------------------------------------------------------------|

| on the right has a thin layer of gold (~ $100 \text{ Å}$ ) deposited on top of the |

| SiN to improve the contrast and resolution (compared to the picture                |

| on the left side)                                                                  |

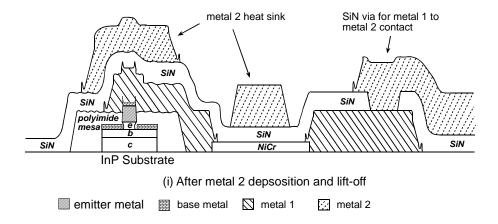

| Fig. 5.14: Cross section of the wafer after metal-2 lift-off                       |

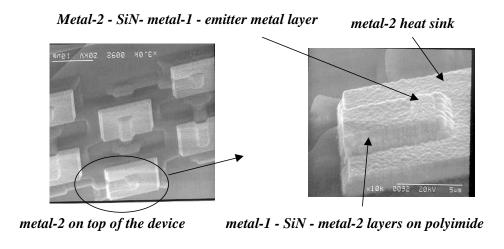

| Fig. 5.15: SEM picture after metal-2 deposition on top of the device.              |

| Shown on the left side is the SEM picture of the metal-2 heat sink of a            |

| number of transistors, and on the right side is an enlarged SEM picture            |

| of a transistor                                                                    |

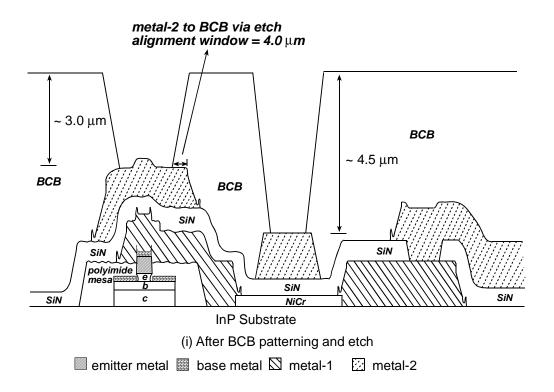

| Fig. 5.16: Cross section of the wafer after the BCB etch is shown above.           |

| Note that the thickness of BCB on top of the metal-2 heat sink is                  |

| $1.5\ \mu m$ less than the thickness of BCB on top of the resistor. Hence          |

| to open the BCB via on top of the resistor the BCB via on top of the               |

| device needs to be over-etched                                                     |

| Fig. 5.17: Cross section of the wafer after the completion of the process          |

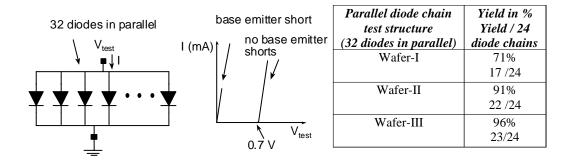

| Fig. 5.18: Parallel base-emitter diode chain used to identify and obtain the       |

| failure rate due to base-emitter shorts. Also shown are the expected I-V           |

| curves of the diode chain in the presence and absence of the base-                 |

| emitter shorts                                                                     |

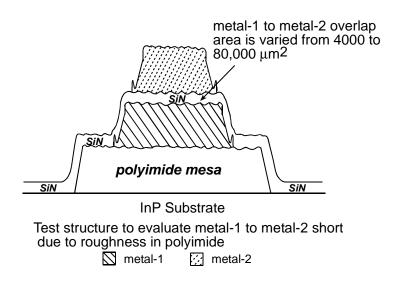

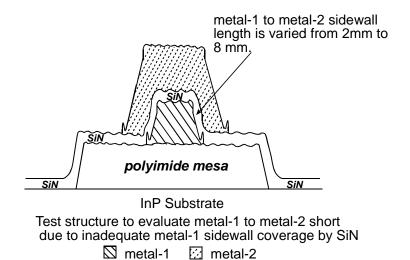

| Fig. 5.19: Test structure used to evaluate the effect of polyimide roughness       |

| on metal-1 to metal-2 electrical isolation                                         |

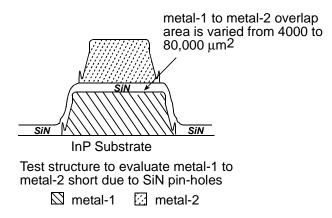

| Fig. 5.20: Shown in the figure above is the test structure used to evaluate |     |

|-----------------------------------------------------------------------------|-----|

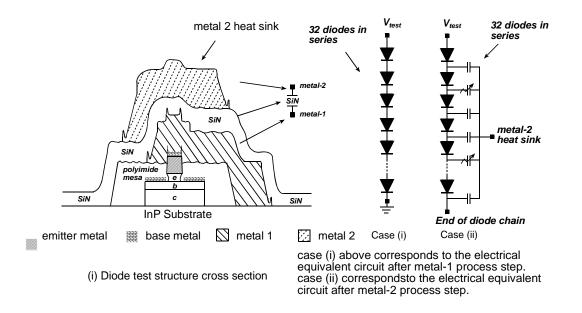

| the presence of pin-holes in SiN                                            | 118 |

| Fig. 5.21: Shown above is the test structure used to evaluate the quality   |     |

| of sidewall coverage of metal-1 by SiN                                      | 120 |

| Fig. 5.22: Cross section of a diode in the diode test structure and the     |     |

| electrical equivalent circuit of the diode test structure at metal-1 step   |     |

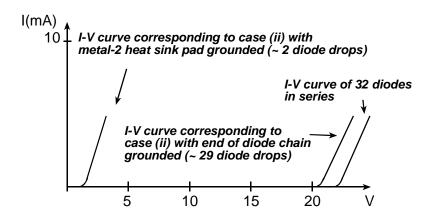

| and after metal-2 process step                                              | 123 |

| Fig. 5.23: I-V curve corresponding to multiple metal-1 to metal-2 shorts    |     |

| for the case shown in Fig. 5.22                                             | 123 |

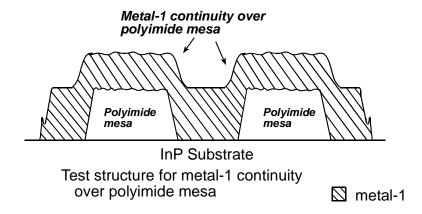

| Fig. 5.24: metal-1 step coverage of polyimide test structure and results    | 124 |

| Fig. 5.25 Test structure used to measure the uniformity of SiN via          |     |

| etching process                                                             | 125 |

## LIST OF TABLES

| Table 1.1: Static frequency divider performance in different technologies          |

|------------------------------------------------------------------------------------|

| Table 2.1 : Truth table of a full adder                                            |

| Table 5.1: Measured failure statistics from the test structure (Fig. 5.19)         |

| used to evaluate the effect of polyimide roughness                                 |

| Table 5.2: Measured failure statistics from the test structure (Fig. 5.20) used to |

| evaluate the effect of SiN pin-holes                                               |

| Table 5.3: Measured failure statistics from the test structure (Fig. 5.21)         |

| used to evaluate the quality of sidewall coverage of metal-1 by SiN 120            |

| Table 5.4: Measured yield statistics from the series diode test structure          |

| (Fig. 5.21)                                                                        |

| Table 6.1: Table shows the simulated clock rates for the various adder             |

| design approaches discussed in chapter 3. The measured performance                 |

| for the designs fabricated are also listed                                         |

# Chapter 1

# Introduction

Heterojunction bipolar transistor (HBT) based integrated circuits (ICs) are finding applications in commercial, military, and satellite communication systems. The commercial applications are mainly driven by CATV, wireless and fiber-optic communication systems while the military applications include electronics for naval radars and military communication systems. The demands placed by these applications have led to the development and commercial production of a number of HBT technologies. Current HBT technologies in commercial production include GaAs and InP based HBTs. Also significant progress has been made in Silicon-Germanium (SiGe) HBT technology, enhancing the frequency range of operation of Si bipolar transistor technology. The potential uses of these technologies in high-speed applications depend on their microwave (RF) as well as logic speed performance. Current gain cut-off frequency ( $f_{t}$ ) and power gain cut-off frequency ( $f_{max}$ ) are the two common figures of merit used to evaluate the analog/RF performance of an HBT technology.

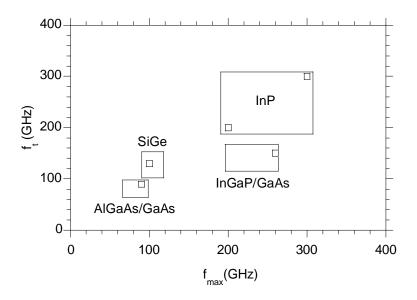

Shown in Fig. 1.1 are the  $f_t$ ,  $f_{max}$  of different HBT technologies. AlGaAs/GaAs HBTs have lower cut-off frequencies [1] compared to InP or SiGe

HBTs and find applications in ICs operating around 10 - 20 GHz. Advances in SiGe technology over the last few years have resulted in commercial production of SiGe transistors with  $f_t$  and  $f_{max}$  over 100 GHz [2]. InGaP/GaAs HBTs have demonstrated peak  $f_t$  and  $f_{max}$  of 150 GHz and 260 GHz respectively [3]. Commercial InP HBTs have reported  $f_t$  and  $f_{max}$  close to 200 GHz [4] and the transferred substrate HBT technology has demonstrated simultaneous  $f_t$  and  $f_{max}$  close to 300 GHz [5].

The Master-slave latch (Flip-flop) is a key building block used in digital circuits. The maximum clocking rate of the Master-slave flip-flop is most easily evaluated by configuring it as a static frequency divider. This is achieved by feeding the inverted output back as the input. The maximum clock rate of static frequency divider (SFD) operation is used to compare the logic speed of different semiconductor technologies. The best reported SFD clock rates are in HBT technologies and are shown in Table 1.1.

Static frequency divider operation has been measured up to 30 GHz [8] in Si Bipolar transistor technology and up to 34.8 GHz [9] in AlGaAs/GaAs HBT technology. Hitachi has reported a 67 GHz frequency divider in SiGe technology [10]. In InP based HBTs, Hughes research labs (HRL) has reported a 72.8 GHz divider [11]. The highest reported clock rate to date for SFD is 75 GHz, realized in InAlAs/InGaAs transferred-substrate HBT (TSHBT) technology [12]. The power dissipation of the dividers is shown in Table 1.1.

Fig. 1.1: Shown above is the  $f_t$  and  $f_{max}$  regime of different HBT technologies reported in literature [1,2,3,4,5].

Table 1.1: Static frequency divider performance in different technologies.

| Ref. | Technology       | Maximum  | Power  |

|------|------------------|----------|--------|

| [6]  | Si MOSFET        | 16.8 GHz | 3 mW   |

| [7]  | HEMTs            | 49.2 GHz | 290 mW |

| [8]  | Si BJT           | 30 GHz   | 630 mW |

| [9]  | AlGaAs/ GaAs HBT | 34.8 GHz | 495 mW |

| [10] | SiGe HBT         | 67 GHz   | 175 mW |

| [11] | InAlAs/InGaAs    | 72.8 GHz | 55 mW  |

| [12] | InAlAs/InGaAs    | 75 GHz   | 800 mW |

InP and SiGe HBT technology offer excellent RF as well as logic speed performance making them a good technology choice for building amplifiers as well as digital and mixed signal ICs for high-speed applications. InP HBTs offer superior RF performance when compared to SiGe HBTs, but in digital applications SiGe circuits have done nearly as well as InP circuits. This has been attributed to the advanced and mature silicon processing capabilities which enables increased current density (J<sub>e</sub>) of operation, highly scaled device geometry (0.18 µm emitter width) and interconnect density, higher transistor count and reduced device as well as interconnect parasitics [2]. These technologies have been used to demonstrate transimpedance and power amplifiers [13,14], as well as flip-flops operating over 66 GHz.

The office of naval research (ONR) is currently engaged in the process of designing the next generation of electronic systems for naval radars. The enabling technology needs to provide logic-speeds up to 100 GHz and RF performance in the 300 - 400 GHz range. Such high frequency performance requires major advances in both InP and SiGe HBT technologies. The next section examines the approaches used to extend the frequency range of InP HBTs. The transferred-substrate approach is presented as a potential technology to realize logic-speeds above 100 GHz.

#### 1.1 Motivation

One of the key electronic components needed for the next generation of naval radars is the direct digital frequency synthesis (DDFS) block that is used for signal

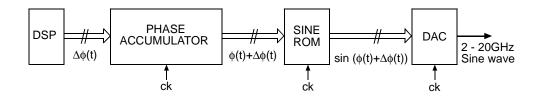

generation. This work was part of a bigger project aimed at demonstrating the basic building blocks of a DDFS system operating at high frequencies. The block diagram of a DDFS system is shown in Fig. 1.2. The digital signal processor outputs a digital word corresponding to the phase increment ( $\Delta \phi$ ). This phase increment is added to the digital word corresponding to the stored value of the phase ( $\phi$ ) in the phase-accumulator. The output digital word ( $\phi + \Delta \phi$ ) of the phase-accumulator (adderaccumulator) serves as the address of a Sine ROM. The Sine ROM is a look-up table and outputs the digital word corresponding to sin ( $\phi + \Delta \phi$ ). This digital word is converted by the digital to analog converter (DAC) to analog sine wave.

The frequency tuning range of the DDFS system is from DC to  $\sim$  ( $f_{ck}/3$ ) and the frequency resolution is given by  $\Delta f = f_{ck}/2^N$ , where N is the bit length of the phase-accumulator word [15]. The design of phase-accumulator, Sine ROM, and DAC clocking above 40 GHz are all significant design challenges. This work focuses on the design challenges in building high-speed adder-accumulators.

Fig. 1.2: Block diagram showing the direct digital frequency synthesis approach.

## 1.2 HBT Technology to realize 100 GHz logic: the challenges

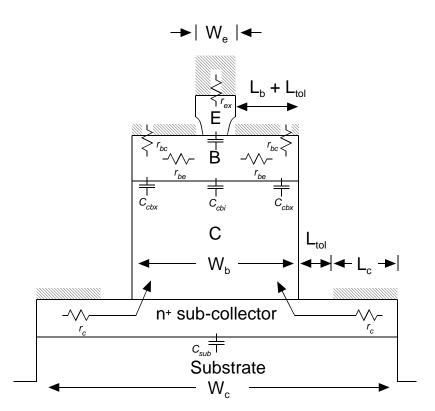

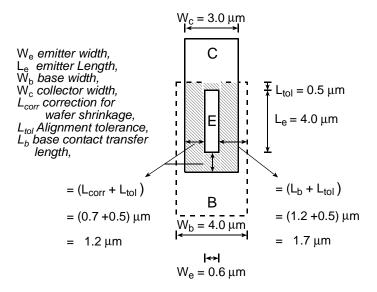

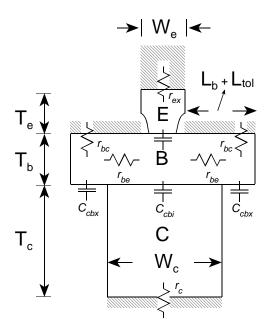

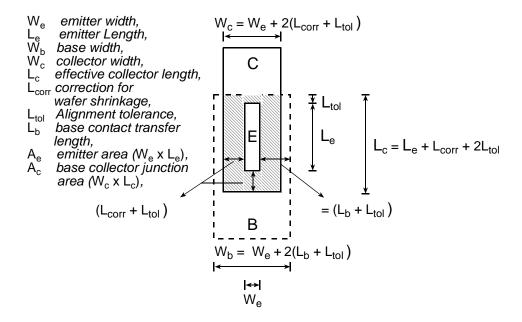

A typical HBT structure is shown in Fig. 1.3.  $W_e$  is the width of the emitter and is normally determined by the minimum definable feature size. High frequency HBT technologies use a self-aligned base to reduce extrinsic base resistance  $(r_{be})$ . The base mesa width  $(W_b)$  is determined by the transfer length  $(L_b)$  of the base contacts. The base width also determines the area of the base-collector junction, which contributes to the base-collector capacitance  $(C_{cb})$ . The base-collector capacitance  $C_{cb}$  has 2 components, the intrinsic component  $C_{cbi}$ , and the extrinsic component  $C_{cbx}$  as shown in Fig. 1.3. The transfer length of the collector contacts  $(L_c)$  and any alignment tolerance  $(L_{tol})$  determine the collector mesa width  $(W_c)$ . This HBT structure is referred to as the triple-mesa HBT structure. The emitter mesa isolates the emitter-base junction and the base mesa isolates the base-collector junction. The collector mesa provides device to device isolation.

The logic-speed of an HBT technology depends on a number of device parameter [16]. The most significant parameters include forward transit time  $\tau_f$ , base-collector capacitance  $C_{cb}$ , base resistance  $r_{bb}$ , maximum current density of operation  $J_e$ , base-emitter capacitance  $(C_{be})$  and extrinsic emitter resistance  $(r_{ex})$  [16]. The extent to which the logic-speed depends on the device parameters is specific to the technology under consideration. In triple mesa HBT structures the base-collector capacitance has significant effect on the logic speed [17]. Scaling of the emitter finger width  $(W_e)$  has been used to reduce the intrinsic base-collector capacitance  $C_{cbi}$ . But, the reduction in the total base-collector capacitance  $(C_{cb} = C_{cbi})$

+  $C_{cbx}$ ) with the scaling of emitter width  $W_e$  becomes negligible when the emitter width becomes smaller than the base contact width  $\{W_e < (L_b + L_{tol})\}$ . Thus, in submicron HBTs the extrinsic base-collector capacitance  $C_{cbx}$  is higher than the intrinsic base-collector capacitance  $C_{cbi}$  [17].

Fig. 1.3: The structure of a triple-mesa HBT indicating the relevant intrinsic and extrinsic device parameters that contribute to device performance.

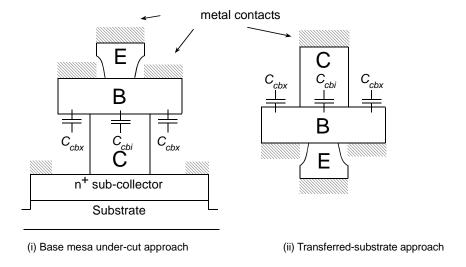

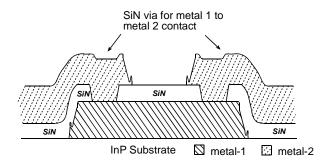

A number of approaches have been put forward to reduce the extrinsic basecollector capacitance. These include the selective wet etch based under-cut of the base mesa [18] and the transferred-substrate HBT approach [19]. The basic approach employed to reduce  $C_{cb}$  in both the transferred-substrate approach and selective wet etch undercut approach are shown in Fig. 1.4. Though excellent RF results [18] have been obtained by undercutting the base mesa, the issue of passivation of the base mesa under-cut remains to be addressed. The transferred-substrate HBT (TSHBT) approach involves flipping and bonding the processed InP wafer onto a GaAs wafer and etching away the InP substrate to expose the collector epitaxial layer. The collectors are then defined directly opposite to the emitter. Significant reduction in  $C_{cbx}$  is achieved by the use of Schottky collector contacts. The extrinsic collector region is partly removed by a collector recess etch [19]. Transferred-substrate HBTs have demonstrated excellent RF performances with  $f_t$  of 300 GHz [20] and extrapolated  $f_{max}$  of over 1 THz [21]. To date, a number of circuits have been fabricated in TSHBT process which include small signal amplifiers [22], static frequency dividers [12], analog to digital converters [23] and the carry and sum logic circuit for a 2-bit adder-accumulator [24].

There are also a number of other process and technological challenges that need to be addressed to realize 100 GHz logic technology. Increased base doping levels would lead to lower base contact resistance ( $r_{bc}$ ) and base contact transfer length ( $L_b$ ). Attempts to achieve base doping levels in excess of  $10^{20}$  cm<sup>-3</sup> using carbon dopants are already underway. Current transferred-substrate HBT digital circuits are fabricated in InAlAs/InGaAs single heterojunction bipolar transistors (SHBT). These transistors have low breakdown voltage ( $V_{br}$  <1.2V at  $J_e$  = 1 mA/ $\mu$ m<sup>2</sup>) and poor thermal conductivity due to the use of InGaAs collectors and

InAlAs emitters. Improved heat sinking techniques are required to increase the current density  $(J_e)$  of operation. The emitter extrinsic resistance  $(r_{ex})$  and forward transit time  $(\tau_f)$  also need to be reduced. These requirements translate to careful design of epitaxial layer structure, the choice of doping levels, as well as appropriate ohmic contact metallurgy [16]. The effect of the various device parameters on circuit performance depends on the circuit under consideration. In most cases a trade-off among the various device parameters need to be made in the device design to obtain optimum circuit speed.

## 1.3 Nature and scope of this work

This work presents the design techniques used to improve the clock rate of a 2-bit adder-accumulator circuit. The 2-bit adder-accumulator circuit is to be used as the building block in an 8-bit pipelined adder-accumulator scheme. The first generation design used a wired-OR/AND approach in the carry logic (AND-OR) circuit to increase the clock rate. The second generation design used a new single 3-level series-gated logic gate that perform AND-OR operation needed to realize the carry logic of a full adder. This carry logic circuit is then merged with the latches to realize a merged AND-OR-Latch circuit. Simulations indicate that this 4-level series-gated structure is 1.8:1 faster compared to the wired-OR/AND implementation. A 75 GHz ECL static frequency divider was also fabricated as part of this work. This is the highest reported clock rate for divider operation.

Fig. 1.4: Approaches used to reduce the extrinsic base-collector capacitance ( $C_{cbx}$ ) are shown above. Shown on the left is the selective removal of collector region by wet etching. On the right is the transferred-substrate approach.

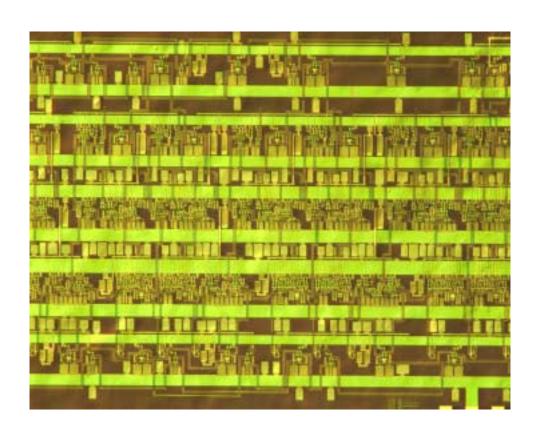

At the start of this work in fall 1997, transferred-substrate HBT technology had demonstrated small signal amplifiers as well as static frequency dividers. The static frequency divider was the largest digital circuit that was fabricated and had about 50 HBTs and operated up to 48 GHz [25]. Subsequent work by Q. Lee led to static frequency dividers clocking at 66 GHz in 1999 [26]. This circuit had about 76 transistors. S. Jagannathan realized a first order  $\Sigma$ - $\Delta$  analog to digital converter [23] clocking at 18 GHz with 150 HBT complexity in 2000. In this work we have demonstrated working circuits up to 250 HBT complexity.

Attempts to extend a technology, which demonstrated circuits having tens of transistors, to realize circuits having hundreds of transistors, brings forth a new set of failure mechanisms. To address these, one needs to define a set of test structures to identify and isolate the failure mechanisms. In addition to this, we also need to gather statistical information about these failure mechanisms which tells us the extent of integration that is possible. This work also presents the test structures designed to identify the various failure mechanisms and the statistical data collected from these structures.

## 1.4 Thesis organization

A number of adder-accumulator architectures have been reported in the literature. A brief review of the different adder-accumulators is undertaken in chapter 2. These include ripple carry adders (RCA), carry lookahead adders (CLA) and pipelined adders. This chapter also explains the choice of pipelined adderaccumulators for high clock rate applications.

The various approaches for increasing the clock rate of 2-bit adders is then discussed. Two generations of adder designs were carried out. These are described in chapter 3. The measurement results of the fabricated adder circuits are also presented in this chapter. The design and results of a 75 GHz static frequency divider circuit is presented in chapter 4.

Chapter 5 describes the various processing issues in the transferred-substrate HBT process (TSHBT). The TSHBT process is presented in a step-by-step manner.

The relevant processing issues at each step are presented with the help of wafer cross section figures and SEM pictures. The possible failure mechanisms are highlighted and test structures that identify these failure mechanisms are presented. The results of the various process and yield characterization test structures are also presented in chapter 5. The conclusions are presented in chapter 6.

# Chapter 2

# Synchronous adder architectures

Adders are key building blocks in a number of applications including Direct digital frequency synthesis (DDFS) and Arithmetic and logic unit (ALU) of a computer. There exist two classes of adders, namely the asynchronous adders and the synchronous adders. In general, asynchronous adders [27] perform the addition and then generate a control signal indicating the completion of an add operation. In such adders, the time to complete the addition depends on the input bits and the addition algorithm used. In synchronous adders, the input bits are available at the start of each clock cycle, and the sum output bits are generated at the end of each clock period. As the adder-accumulators used in DDFS systems are synchronous adders, a review of the different synchronous adder-architectures is presented in the following section.

Binary adders perform the function of adding two numbers, where each number is represented as a binary word. The addition operation in digital domain is represented by a set of logic operations that generate the output sum word. The next section details the logic operations involved in the addition of two binary words.

## 2.1 A full adder (FA).

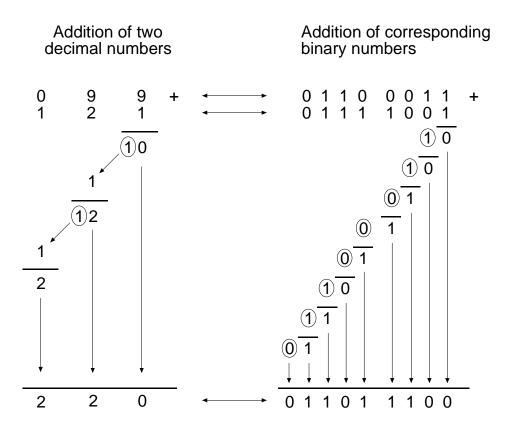

The addition of two binary words is shown in Fig. 2.1. Also shown alongside, is the addition of the corresponding decimal numbers. In the decimal number system when you add 2 digits, if the sum is '10' or higher, then you 'carry over 1' to the next higher digit. Thus, the addition of each digit also includes the 'carryover' from the summing operation of the adjacent lower digit, and can also result in a 'carry over' to the next higher digit. These 'carrys' to the next higher digit are shown encircled in Fig. 2.1. Also shown in Fig. 2.1 is the addition of these two numbers, as represented by their binary equivalents. The addition of two binary bits also includes a 'carry-in' from the adjacent lower significant bit and a 'carry-out' to the adjacent higher significant bit. Thus, a 1-bit full adder has 3 inputs ( $A_i$ ,  $B_i$ , and carry-in  $C_i$ ) and two outputs (sum  $S_i$ , and carry-out  $C_{i+1}$ ). This 1-bit adder is referred to in literature as a full adder.

The truth table of a full adder is shown in Table 2.1. The logic equation for the sum  $(S_i)$  and the carry-out  $(C_{i+1})$  can be written as the sum of products (Eq. 2.1). The carry logic equation can be further reduced using Boolean logic identities as shown below.

$$\begin{aligned} \mathbf{S}_{i} &= \overline{\mathbf{A}_{i}} \cdot \overline{\mathbf{B}_{i}} \cdot \mathbf{C}_{i} + \overline{\mathbf{A}_{i}} \cdot \mathbf{B}_{i} \cdot \overline{\mathbf{C}_{i}} + \mathbf{A}_{i} \cdot \overline{\mathbf{B}_{i}} \cdot \overline{\mathbf{C}_{i}} + \mathbf{A}_{i} \cdot \mathbf{B}_{i} \cdot \mathbf{C}_{i} \\ \mathbf{C}_{i+1} &= \overline{\mathbf{A}_{i}} \cdot \mathbf{B}_{i} \cdot \mathbf{C}_{i} + \mathbf{A}_{i} \cdot \mathbf{B}_{i} \cdot \overline{\mathbf{C}_{i}} + \mathbf{A}_{i} \cdot \overline{\mathbf{B}_{i}} \cdot \mathbf{C}_{i} + \mathbf{A}_{i} \cdot \mathbf{B}_{i} \cdot \mathbf{C}_{i} \\ &= \mathbf{B}_{i} \cdot \mathbf{C}_{i} + \mathbf{A}_{i} \cdot \mathbf{B}_{i} + \mathbf{A}_{i} \cdot \mathbf{C}_{i} \end{aligned} \tag{2.1}$$

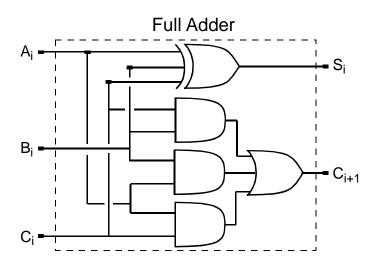

The sum logic  $(S_i)$ , is generated using a 3-input XOR gate whose inputs are  $A_i$ ,  $B_i$ , and  $C_i$ . The generation of carry logic  $(C_{i+1})$  involves realizing the minterms

using AND gates, followed by the OR operation. This is shown in Fig. 2.2. Note that the propagation delay  $(T_{pd})$  of a full adder is equal to the two gate delays needed to realize the carry logic.

Fig. 2.1: Shown in figure above is the addition of two decimal numbers and the corresponding addition of their binary equivalent. The 'carry over' digit/bit is shown encircled.

Table  $2.1: Truth\ table\ of\ a\ full\ adder.$

| Ai | B <sub>i</sub> | Ci | $S_{i}$ | $C_{i+1}$ |

|----|----------------|----|---------|-----------|

| 0  | 0              | 0  | 0       | 0         |

| 0  | 0              | 1  | 1       | 0         |

| 0  | 1              | 0  | 1       | 0         |

| 0  | 1              | 1  | 0       | 1         |

| 1  | 0              | 0  | 1       | 0         |

| 1  | 0              | 1  | 0       | 1         |

| 1  | 1              | 0  | 0       | 1         |

| 1  | 1              | 1  | 1       | 1         |

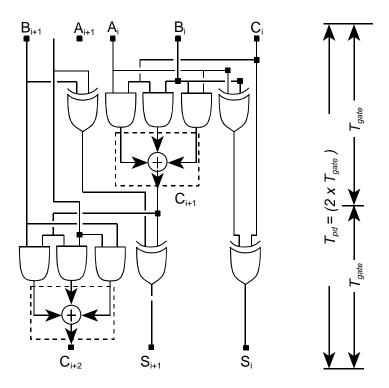

Fig. 2.2: Logic gate realization of a full adder.

## 2.2 Ripple carry adder architecture (RCA)

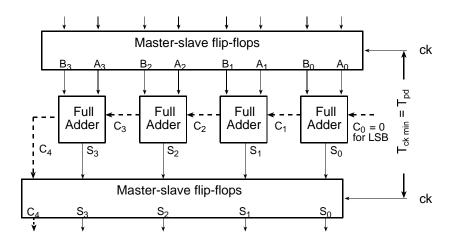

The ripple carry adder [27] is the simplest adder architecture and is shown in Fig. 2.3. The 4-bit adder shown in Fig 2.3 is made up of full adders that perform the addition for individual bits. In this architecture, the carry-out  $(C_{i+1})$  of each full adder goes as the carry-in to the next significant bit full adder. Thus, to complete the addition you need to wait for the carry bits to propagate from the least significant bit (LSB) to the most significant bit (MSB). The worst case propagation delay to complete the addition  $\{T_{pd} (4\text{-bit adder})\}$  for this 4-bit adder is shown below.

$$T_{pd} (4 - bit adder) = 4 * T_{pd} (full adder) + T_{MSFF}$$

$$= 4 * (2 * T_{gate}) + T_{MSFF}$$

$$T_{ck min} = T_{pd} (4 - bit adder)$$

$$f_{ck max} = \frac{1}{T_{ck min}} = \left(\frac{1}{4 * (2 * T_{gate}) + T_{MSFF}}\right)$$

(2.2)

The factor of '4' appears because the carry has to ripple through from the LSB to MSB, through 4 full adder blocks. The "(2  $T_{gate}$ )" term accounts for the gate delay involved in generating the carry-out of a full adder, and the  $T_{MSFF}$  accounts for the delay in the output master-slave flip-flop. The minimum possible clock period ( $T_{ck}$  min) must allow for this worst case delay for correct adder operation. Thus, the maximum clock frequency ( $f_{ck}$  max) is limited by the worst-case propagation delay as shown for a ripple carry adder. This can be extended for N-bit adder case also as shown below.

$$f_{ck max} = \frac{1}{T_{ck min}} = \left(\frac{1}{N*(2*T_{gate}) + T_{MSFF}}\right)$$

(2.3)

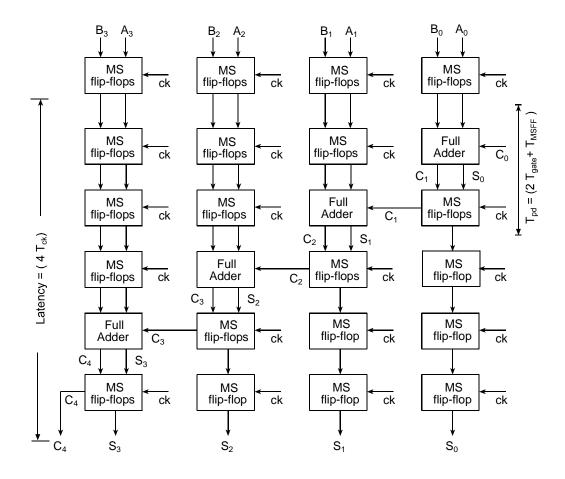

Fig. 2.3: 4-bit ripple carry adder (RCA) implemented using full adders. The worst-case propagation delay path is along the dashed lines.

## 2.3 Carry lookahead adder architecture (CLA)

The carry lookahead adder [27] increases the clock rate by generating the carry-in of the various full adder blocks in 'parallel' using additional logic circuitry. This approach does away with the delay involved in the propagation of the carry-out from the LSB to the MSB as is the case with ripple carry adder. The carry lookahead approach is explained below.

Let  $A=A_{n-1}$ .... $A_1$   $A_0$ , and  $B=B_{n-1}$ ..... $B_1$   $B_0$ , be the augend and the addend inputs to a N-bit adder.  $C_i$  refers to the carry-in for the  $i^{th}$  bit and  $C_{i+1}$  refers to the

carry-out from the  $i^{th}$  bit. The subscript 'i' refers to any arbitrary bit. We define two additional variables called carry-generate  $(G_i)$  and carry-propagate  $(P_i)$  given by

$$G_{i} = A_{i} \cdot B_{i}$$

$$P_{i} = A_{i} \oplus B_{i}$$

(2.4)

It is possible to express both the carry and sum output bits in terms of the carry-generate and carry-propagate bit as shown below.

$$S_{i} = (A_{i} \oplus B_{i}) \oplus C_{i}$$

$$= P_{i} \oplus C_{i}$$

$$C_{i+1} = (A_{i} \cdot B_{i} \cdot \overline{C_{i}} + A_{i} \cdot B_{i} \cdot C_{i}) + \overline{A_{i}} \cdot B_{i} \cdot C_{i} + A_{i} \cdot \overline{B_{i}} \cdot C_{i}$$

$$= A_{i} \cdot B_{i} + (\overline{A_{i}} \cdot B_{i} + A_{i} \cdot \overline{B_{i}}) \cdot C_{i}$$

$$= G_{i} + (A_{i} \oplus B_{i}) \cdot C_{i}$$

$$= G_{i} + P_{i} \cdot C_{i}$$

$$(2.5)$$

Starting from the least significant bit (LSB) (i = 0) we can recursively apply the above equation to generate the various carry-out bits as shown below.

$$\begin{split} &C_{1} = G_{0} + C_{0} \cdot P_{0} \\ &C_{2} = G_{1} + C_{1} \cdot P_{1} \\ &= G_{1} + G_{0} \cdot P_{1} + C_{0} \cdot P_{0} \cdot P_{1} \\ &C_{3} = G_{2} + C_{2} \cdot P_{2} \\ &= G_{2} + G_{1} \cdot P_{2} + G_{0} \cdot P_{1} \cdot P_{2} + C_{0} \cdot P_{0} \cdot P_{1} \cdot P_{2} \\ &C_{4} = G_{3} + C_{3} \cdot P_{3} \\ &= G_{3} + G_{2} \cdot P_{3} + G_{1} \cdot P_{2} \cdot P_{3} + G_{0} \cdot P_{1} \cdot P_{2} \cdot P_{3} + C_{0} \cdot P_{0} \cdot P_{1} \cdot P_{2} \cdot P_{3} \\ \vdots \\ &C_{n} = G_{n} + G_{n-1} \cdot P_{n} + G_{n-2} \cdot P_{n-1} \cdot P_{n} + \dots + G_{0} \cdot P_{1} \cdot P_{2} \cdot P_{3} \dots P_{n-1} \\ &+ C_{0} \cdot P_{0} \cdot P_{1} \cdot P_{2} \dots P_{n-1} \end{split}$$

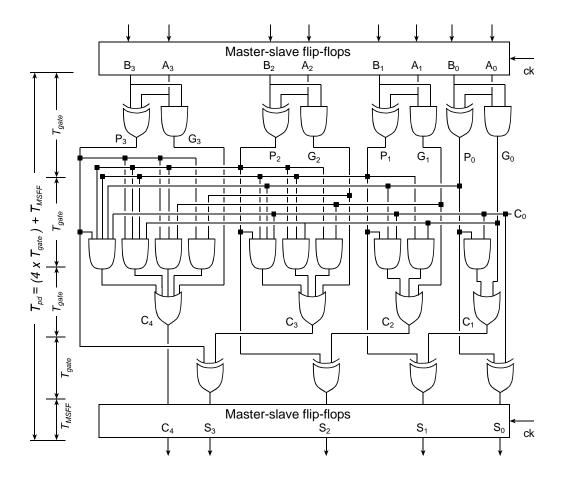

Fig. 2.4: A 4-bit carry lookahead adder (CLA) architecture is shown above. The gate delays that determine the maximum clock rate is indicated on the left hand side. The carry-in bit  $C_0 = 0$  because in the first 4-bit adder block there is no carry-in from the previous adder block.

This set of equations is realized using the combinatorial logic circuit called the carry lookahead logic unit. In Fig. 2.4 is shown a 4-bit carry lookahead adder. The key features of this approach are shown in Fig. 2.4 and are listed below.

- (i) From Eq. 2.4 we see that all the carry-generate bits  $(G_i)$  and carry-propagate bits  $(P_i)$  can be generated simultaneously within a single gate (2-input AND or XOR gate) delay after the input words A and B are available.

- (ii) Once the carry-generate bits  $(G_i)$  and carry-propagate bits  $(P_i)$  are available, the carry-out bits  $(C_i)$  are generated within 2 gate delays corresponding to Eq. 2.6. The first gate delay corresponds to the multiple AND gates needed to generate the minterms in Eq. 2.6. (Fig. 2.4) The second gate delay corresponds to the OR gate that realizes the OR operation of the AND gate outputs to generate the carry bits  $(C_i)$ .

- (iii) The addition operation is completed within 4 gate delays irrespective of the bit length N of the adder. The maximum clocking frequency of such an architecture (Fig. 2.4) is given by,

$$f_{ck max} = \frac{1}{T_{ck min}} = \left(\frac{1}{(4 * T_{gate}) + T_{MSFF}}\right)$$

(2.7)

and is independent of the bit length N of the adder. This calculation neglects the effect of fan-in and fan-out on the gate delay ( $T_{\text{gate}}$ ).

(iv) As the number of bits 'N' increases, the gate count as well as the fan-in and fan-out of the gates increase drastically. The gate count of the carry

lookahead logic unit increases as N + (N - 1) + (N - 2)....+ 0. Similarly, the fan-in and fan-out increases as N, making the gate delays larger as N increases.

Though faster than the ripple carry adder, the significant fan-in and fan-out requirement of CLA architecture leads to lower clock rate as the bit length N increases. The pipelined adder-accumulator offers significant speed improvement compared to the CLA architecture and is discussed in the next section.

#### 2.4 Pipelined adder architecture

The pipelined adder approach [27,28] is illustrated with the example of a 4-bit adder. Let  $A = A_3...A_0$ , and  $B = B_3...B_0$ , be the inputs to the adder. The output sum and carry-out bits are given by  $S = S_3...S_0$ , and  $C = C_4...C_1$  respectively. The carry-out  $(C_1)$  and the sum output  $(S_0)$  of the least significant bit (LSB) are generated by a full adder as shown in the upper right corner of Fig. 2.5. These outputs are latched to synchronize the output bits with the next instance of clock. The next higher input bits  $A_1$  and  $B_1$  are delayed by one clock period using latches and arrive at the input of the next full adder at the same instant as the carry-out  $(C_1)$  generated from the previous stage. The corresponding sum  $(S_1)$  and carry  $(C_2)$  output bits are generated and latched. The above process is then repeated for the higher bits. Thus, as you go higher towards the most significant bit (MSB), the inputs  $A_i$  and  $B_i$  get progressively delayed by one period through the use of MS flip-flops. Similarly, the sum output

Fig: 2.5: A 4-bit pipelined adder realized using full adder logic blocks.

bits  $S_0...S_3$  are skewed in time by one clock period each as you go from the LSB to the MSB.

The key features of the general pipelined approach can be summarized as follows.

- (i) The total propagation delay  $(T_{tot})$  involved in evaluating the outputs of a series of cascaded logic gates, is divided into N number of nearly equal logic propagation delay  $(T_{pd})$  elements or blocks (ie  $T_{tot} \sim N T_{pd}$ ). In the case of the 4-bit adder discussed above, N=4, and the basic logic element or block is the full adder.

- (ii) The output bits of each of these logic blocks are latched to synchronize them with the clock edge. Some of the output bits of the logic blocks are inputs to the next logic block. In the case of the 4-bit adder, the carry-out bit (C<sub>i</sub>) is an input to the next logic block.

- (iii) If some of the inputs are available at earlier clock instances, MS flip-flops are used to provide delays for these inputs, thus ensuring that all the inputs to a logic block are synchronized to the clock edge and arrive during the correct clock instance. This is very pronounced in the case of 4-bit pipelined adder where the input bits A<sub>3</sub> and B<sub>3</sub> get delayed by 3 clock cycles and arrive at the same time as the carry-bit C<sub>3</sub>.

- (iv) Similarly, the sum-output bits from the full adders are generated at different clock instances, and they need to be realigned back so as to appear as a parallel output. This again is achieved by MS flip-flops.

- (v) The maximum clocking frequency of the pipelined logic is determined by the propagation delay through the individual logic blocks ( $T_{pd}$ ) and the MS flip-flop set-up and propagation delay times. In the pipelined architecture shown in Fig. 2.5, the propagation delay  $T_{pd}$ (full adder) corresponds to the two gate delays associated with the full adder (Eq. 2.1). The maximum clock frequency is given by,

$$f_{ck \max} = \left(\frac{1}{T_{pd}(full adder) + T_{MSFF}}\right)$$

(2.8)

This maximum clock rate is much higher than the maximum clock rate of the non-pipelined ripple carry adder (Eq. 2.2).

(vi) Latency of a circuit is defined as the time required to generate the output once the inputs are available. In the case of non-pipelined 4-bit ripple carry adder the minimum latency is given by the total propagation delay  $T_{pd}(4\text{-bit}$  adder) (Eq. 2.2). This is because the output corresponding to a input arrives after one clock period. In the case of the 4-bit pipelined adder architecture shown in Fig. 2.5, the output corresponding to a set of inputs arrives after 4 clock cycles. Thus the minimum latency of the 4-bit pipelined adder is given by,

Latency =

$$4 * T_{ck max} = 4 * (T_{pd} (full adder) + T_{MSFF})$$

(2.9)

The minimum latency of the 4-bit pipelined adder (Eq. 2.9) is higher than the minimum latency of the 4-bit ripple carry adder (Eq. 2.2) due to the presence of additional flip-flops used for data synchronization.

(vii) The draw back of this approach is the increased circuit complexity as N increases. The number of input and output synchronizing MS latches increase as (N<sup>2</sup>+N). Thus depending on the application, a trade-off between the clock speed and circuit complexity is necessary for a given value of N.

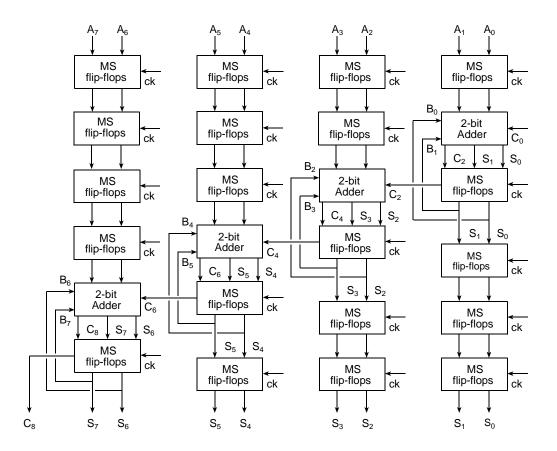

#### 2.5 Initial 8-bit pipelined adder-accumulator design

An 8-bit pipelined adder-accumulator was designed during the initial phase of this work. For the adder to function as an accumulator, the sum output is fed back as one of the inputs (ie.  $B_i = S_i$ ). This is shown in Fig. 2.6. As discussed in the earlier sections, the choice of pipelined adder-architecture was primarily dictated by the need for high clock rate adder-accumulators in DDFS systems. The 8-bit adder is realized using 2-bit adder blocks as shown in Fig. 2.6. The choice of 2-bit adder blocks allows for high clock rates while keeping the circuit complexity (resulting from synchronizing MS flip-flops) low enough that it can be realized in an HBT technology.

As discussed in Sec. 2.4, the maximum clock rate of a pipelined adder is limited by the propagation delay of the basic adder block used in the design. In the

case of the 8-bit adder shown in Fig. 2.6, this corresponds to the propagation delay associated with the 2-bit adder block. The main goal of this work was to evaluate circuit design techniques that would allow increased clock rate of operation of the 2-bit adder. The results from the design iterations carried out for the carry and sum logic circuits of a 2-bit adder are presented in Chapter 3.

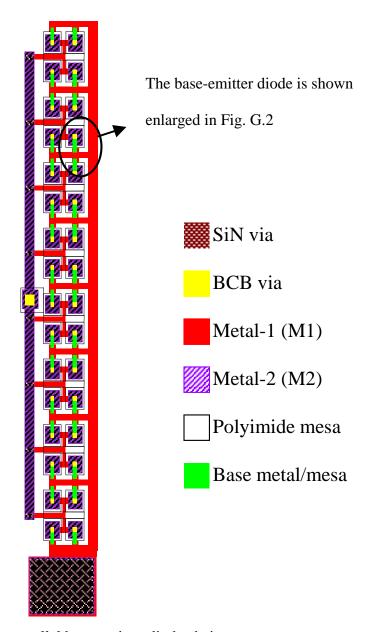

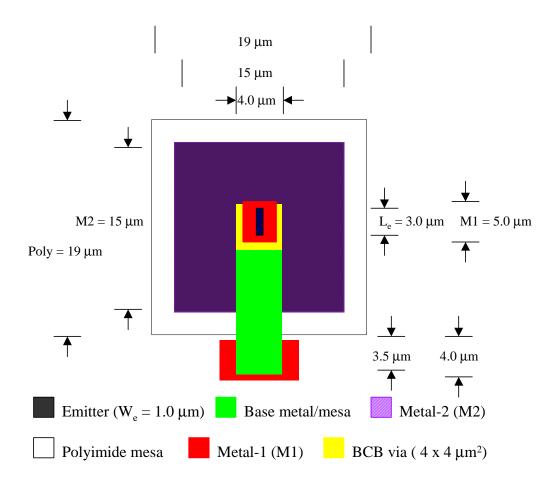

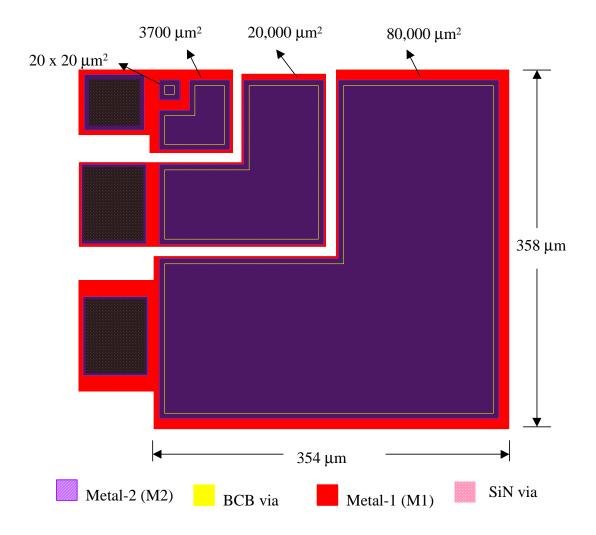

An attempt was made to fabricate the 8-bit adder-accumulator in the transferred-substrate HBT process during the initial part of this work. The logic gates were realized using series-gated ECL logic. For testing purposes, the adder was configured as a binary counter by setting all the input bits  $A_i$  = '0' ( $B_i$  =  $S_i$  for accumulator operation) except for the least significant bit carry input  $C_0$  = '1'. The completed chip photograph is shown in Fig. 2.7. The adder circuit had approximately 2000 HBTs. The fabrication of this IC brought forth a number of processing issues that significantly affects the yield of integrated circuits in TSHBT process. These are discussed later in chapter 5.

Fig. 2.6: An 8-bit pipelined adder-accumulator realized using 2-bit adder blocks. To configure the adder as an accumulator, the sum output S is fed back as one of the inputs i.e.  $B_i = S_i$ .

Fig. 2.7: Chip photograph of the fabricated 8-bit adder-accumulator (2000 HBTs, non-functional circuit) is shown above.

# Chapter 3

## Design of 2-bit adder block.

The design of the 2-bit adder is critical since its propagation delay  $(T_{pd})$  determines the maximum clock speed of the 8-bit pipelined adder-accumulator. This was discussed in section 2.4 (Eq. 2.8). In this work, a number of design techniques are presented to improve the clock rate of the 2-bit adder block. These techniques are further discussed in this chapter. The maximum clock rate of operation of the different design techniques was evaluated by carrying out circuit simulations. Two different design versions were fabricated and tested. The measurement results from these wafers are also presented in this chapter.

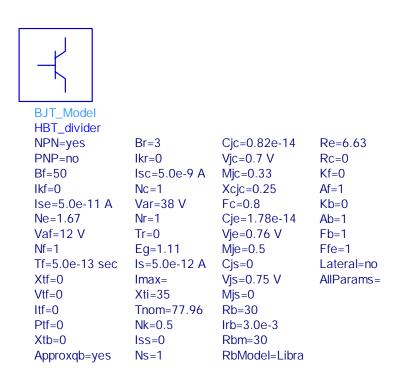

The circuit simulation results presented here for the different circuit design approaches were carried out using the same HBT large signal model (shown in Appendix. D). This helps in identifying the improvements in the circuit performance stemming from better circuit design approaches as compared to better device design. A good device design is necessary to realize the full potential of the IC technology. The effect of the various device parameters on the propagation delay of an ECL latch is shown in Appendix C. These will be further discussed in chapter 4. The design approaches used to improve the clock rate of a 2-bit adder are presented below.

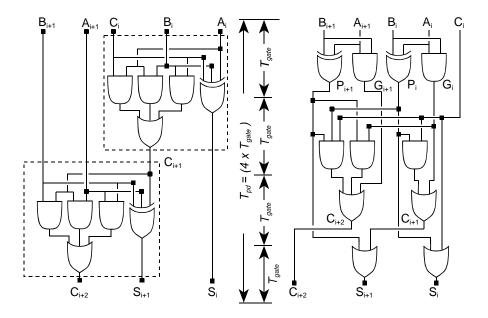

## 3.1 Design choice for 2-bit adder

Based on the discussions in chapter 2, there are two possible designs that can be used to realize a 2-bit adder. The 2-bit adder can be realized as a cascade of two full adders like in a ripple carry adder (Fig. 3.1) or as a 2-bit carry lookahead adder (CLA, Fig. 3.1). The critical delay path (i.e. worst-case propagation delay) for both the schemes involve four gate delays ( $T_{gate}$ ). In the case of 2-bit CLA, this corresponds to the delay involved in generating  $S_{i+1}$  from the inputs  $A_{i+1}$ ,  $B_{i+1}$ , and  $C_{i+1}$ . In the case of two cascaded full adders the critical delay path is the generation of  $C_{i+2}$ , from  $A_{i+1}$ ,  $B_{i+1}$ , and  $C_{i+1}$ . Thus the maximum clock rate of operation of the 2-bit adder block (with output master-slave flip-flips (MSFF) as in Fig. 2.6) is given by,

$$f_{ck max} = \left(\frac{1}{T_{pd}(2 - bit adder) + T_{MSFF}}\right) = \left(\frac{1}{(4 * T_{gate}) + T_{MSFF}}\right)$$

(3.1)

The set-up time and propagation delay associated with the master-slave flip-flop is given by  $T_{MSFF}$  and is given by Eq. 3.4.

The critical path in the 2-bit CLA involves only 2-input logic gates as compared to the presence of 3-input OR gates in the case of 2 cascaded full adders. This makes the 2-bit CLA implementation marginally faster than the full adder implementation. There is no significant difference in both approaches in terms of the gate count.

Fig. 3.1: Shown on the left is the 2-bit adder implemented as 2 cascaded full adders and on the right is the 2-bit adder implemented as a carry lookahead adder (CLA). Also shown is the propagation delay involved for both schemes.

## 3.2 Wired-OR approach

It is possible to increase the clock rate of the 2-bit adder block by realizing the OR gate using wired-OR implementation. The circuit implementation of the wired-OR approach is discussed later in this section. The wired-OR does away with the gate delay required for realizing the OR gates in the 2-bit adder implementations shown in Fig. 3.1. Full adder based realization of the 2-bit adder block has two OR gates in the critical delay path as compared to one OR gate in the critical path of the 2-bit CLA block. Thus the full adder based implementation (Fig. 3.2) of the 2-bit

adder is faster than the 2-bit CLA based approach, with maximum clock rate given by Eq. 3.2. Also, the use of wired-OR gate makes it possible to realize the 2-bit adder block using 2-input logic gates, rather than a set of 2 and 3-input logic gates.

$$f_{ck max} = \left(\frac{1}{(2*T_{gate}) + T_{MSFF}}\right)$$

(3.2)

Fig. 3.2: 2-bit adder implementation using wired-OR gate is shown above. The wired-OR operation is shown within the dashed boxes. The details of wired-OR implementation are shown in Fig. 3.3.

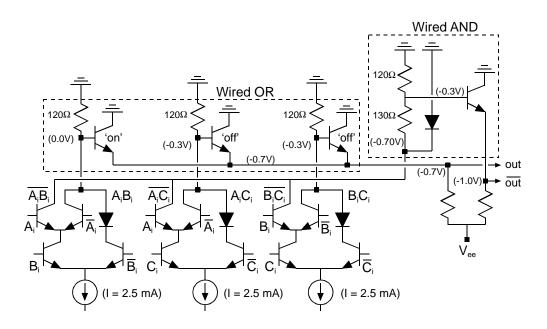

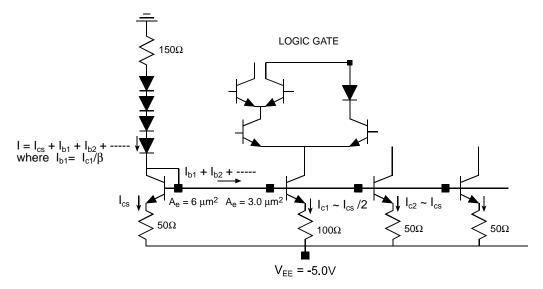

## 3.3 Circuit implementation of Wired-OR and Wired-AND

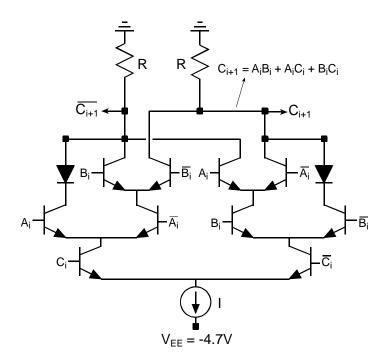

The details of the wired-OR implementation are discussed here. ECL logic employs differential inputs and outputs. This requires that the wired-OR operation must generate not only the correct output but also simultaneously generate the inverted output. Applying this to the full adder case means that the wired OR output must not only generate  $C_{i+1}$  but also generate  $\overline{C_{i+1}}$ . The logic equation for  $C_{i+1}$  is given by Eq. 2.1. Shown below are the logic equation for both  $C_{i+1}$  and  $\overline{C_{i+1}}$ . De-Morgan's law has been applied to simplify the  $\overline{C_{i+1}}$  term in Eq. 3.3.

$$\frac{\mathbf{C}_{i+1} = \mathbf{B}_{i} \cdot \mathbf{C}_{i} + \mathbf{A}_{i} \cdot \mathbf{B}_{i} + \mathbf{A}_{i} \cdot \mathbf{C}_{i}}{\mathbf{C}_{i+1} = \mathbf{B}_{i} \cdot \mathbf{C}_{i} + \mathbf{A}_{i} \cdot \mathbf{B}_{i} + \mathbf{A}_{i} \cdot \mathbf{C}_{i}}

= \mathbf{B}_{i} \cdot \mathbf{C}_{i} \cdot \overline{\mathbf{A}_{i} \cdot \mathbf{B}_{i}} \cdot \overline{\mathbf{A}_{i} \cdot \mathbf{C}_{i}}$$

(3.3)

As can be seen from Eq. 3.3,  $C_{i+1}$  can be generated by doing a wired-OR operation. But, to generate  $\overline{C_{i+1}}$ , one needs to AND (wired-AND) the inverted outputs of the AND gates. Thus in order to replace the OR gate you need to accomplish wired-OR/AND of the 3 AND gate outputs as shown in Fig. 3.3. In ECL logic circuit it is relatively easy to do wired-OR by connecting together the outputs of the emitter followers of the logic gates (shown in Fig. 3.3).

To realize wired-AND logic is more difficult. Shown in Fig. 3.3 is the wired-AND gate realization to generate  $\overline{C_{i+1}}$ . This involves tying the collector node of the inverted output of the AND gates to a common resistor. A diode is placed across the

pull-up resistor to clamp the voltage to  $\sim 0.7 V$ . The value of this pull-up resistor is chosen such that the collector node swings  $\sim 0.7 V$  (i. e. I  $R_{pull\ up} = 700\ mV$  as against 300 mV). It is also important to maintain output swings (300 mV) compatible with the rest of the logic gates. For this purpose the common pull up resistor is utilized as a resistive voltage divider network so as to maintain compatible output voltage levels. This is shown in Fig. 3.3. Also note that diodes are used in the logic gate structure to ensure that the  $V_{ce}$  of all the transistors are below the breakdown limit ( $\sim 1.2\ V$ ). These diodes are realized using transistors that have their bases shorted to the collector.

Throughout the above discussion it was assumed that there is negligible gate delay due to the wired-OR/AND approach outlined above. But that is not strictly true. In typical ECL logic, the emitter followers are always 'on' and see only small signal voltage swings across the base emitter terminals. Because of this, they provide a low impedance path for charging the base emitter capacitance C<sub>be</sub> of the differential pair. But when you do wired-OR implementation, the emitter followers turn on and off depending on the output of the AND gates. An example of this is shown in Fig. 3.3. The switching on and off of the emitter followers not only introduces additional propagation delay in the emitter followers, but also affects the switching speed of the next logic gate that they drive.

Similarly in the case of wired-AND implementation, the large voltage swing (~ 0.7V) at the inverted output of the AND gates requires a larger than usual resistor value, which increases the gate delay of the AND gates. Also the presence of the

diode across the pull-up resistor adds parasitic capacitance to the collector node of the AND gate. Before presenting the simulation results, the approach used for evaluating the propagation delay and the maximum clock rate of the 2-bit carry and sum logic circuits are presented. Also discussed in the next section is a simple testing approach to evaluate the clock speed of a complete 2-bit adder. All subsequent simulation results presented are based on this testing approach.

Fig. 3.3: The wired OR and wired AND implementation are shown above. Also shown are the voltage levels for the specific case,  $A_i = B_i = High$ ,  $C_i = Low$ .

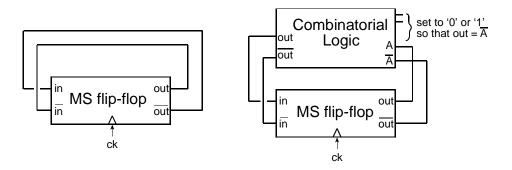

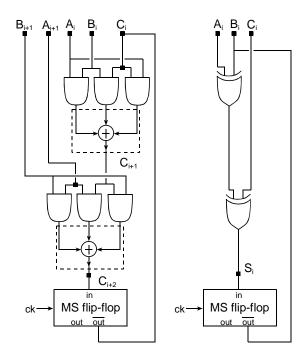

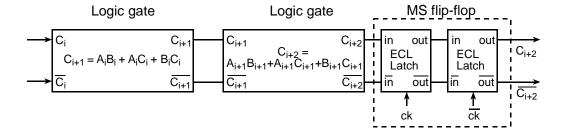

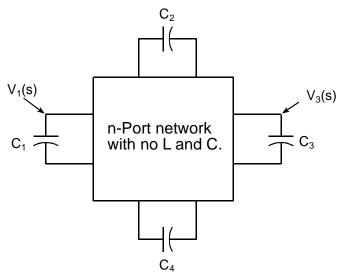

## 3.4 Evaluating maximum clock rate: Test approach

This section outlines the approach used to measure the propagation delay of both the sum and carry logic of the 2-bit adder. This approach is shown in Fig. 3.4. This is a general approach and can be used to measure the propagation delay of any combinatorial logic block. First a master-slave flip-flop (MS flip-flop) is configured as a divide by 2 and the maximum clock rate of operation is measured. The maximum clock rate of the divider is related to the propagation delay of the MS flip-flop ( $T_{MSFF}$ ) and is given below.

$$f_{ck \max}(divider) = \frac{1}{(T_{MSFF})}$$

(3.4)

Fig. 3.4: Evaluating the propagation delay of a combinatorial logic block by configuring it as a frequency divider. Shown on the left is an MS flip-flop configured as a frequency divider.

To evaluate the propagation delay of a combinatorial logic circuit, the logic block is introduced in the feedback loop of the static frequency divider. The output of the MS flip-flop is connected as one of the input to the logic block. The other

inputs of the logic block are set either high or low to enable frequency divider operation. Thus, when a new input value arrives at the input of the logic block it should propagate through the series of logic gates in the most critical delay path causing the output of the logic block to toggle. The feedback from the output of the flip-flop through the logic block to the input of the flip-flop must be out of phase to sustain frequency divider operation. The maximum clock frequency in this case is given by,

$$f_{ck \max}(logic block) = \frac{1}{T_{MSFF} + T_{pd}(logic)}$$

(3.5)

Thus, a measurement of the maximum clock frequency with and without the logic block in the feedback loop can be used to evaluate the propagation delay in the logic block. Therefore, from Eq. 3.4, and Eq. 3.5, the propagation delay in the logic block is given by,

$$T_{\text{pd logic}} = \frac{1}{f_{\text{ck max}} (\text{logic block})} - \frac{1}{f_{\text{ck max}} (\text{divider})}$$

(3.6)

The above approach is used to evaluate the propagation delay in the carry and sum logic circuit of the 2-bit adder. The logic block is replaced by the carry and sum logic circuits as shown in Fig. 3.5. The carry and sum logic circuit of the 2-bit adder used in the pipelined architecture uses MS flip-flops to synchronize the outputs (Fig. 2.6). Thus the clock rate as measured above (Eq. 3.5) is the maximum possible clock rate for the 2-bit adder circuit when used in pipelined adder architectures. Since the carry logic circuit is the most critical delay path, it has a

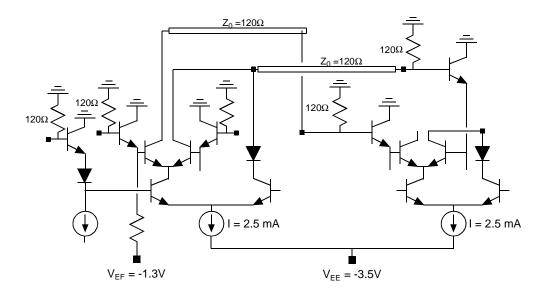

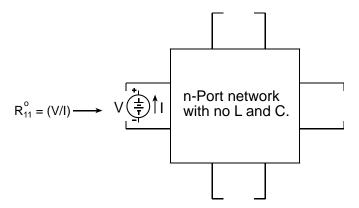

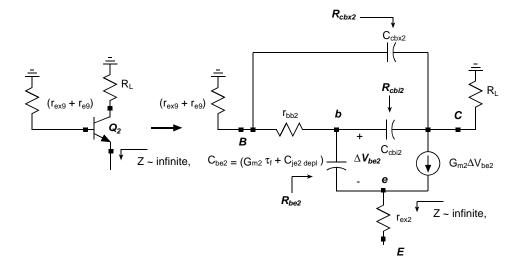

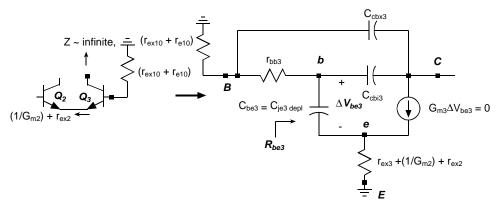

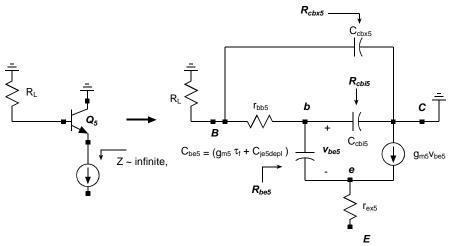

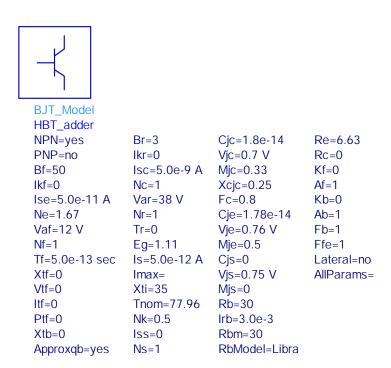

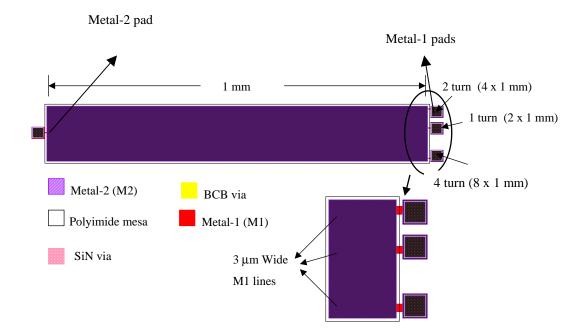

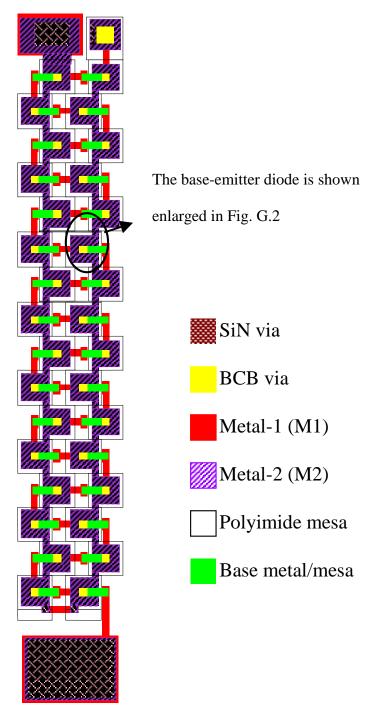

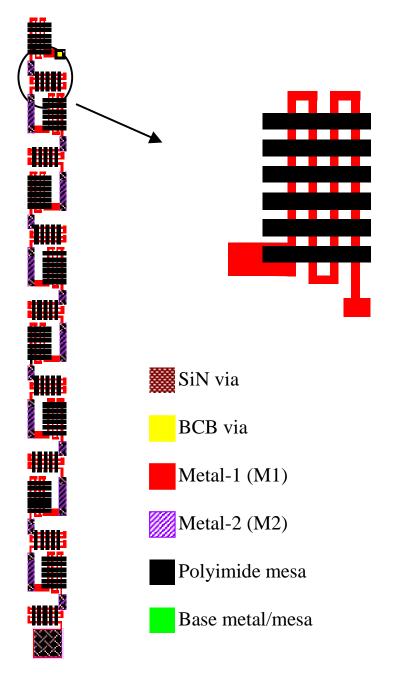

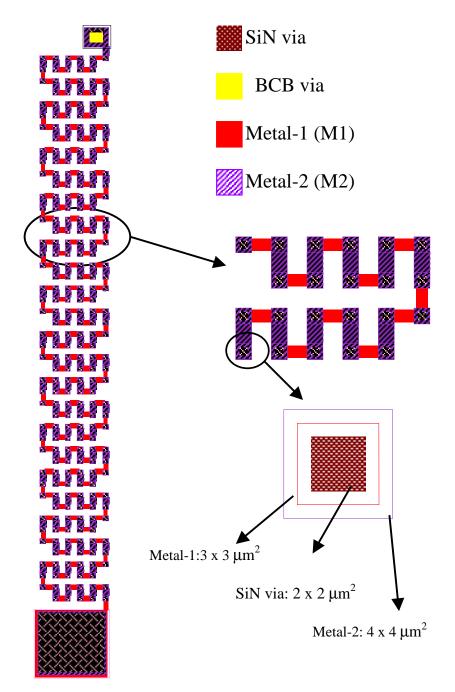

lower clocking frequency than the sum logic circuit and limits the clocking frequency of the 2-bit adder.