#### UNIVERSITY OF CALIFORNIA

#### Santa Barbara

# Analog Integrated Circuits with AlInAs/GaInAs Transferred-Substrate HBTs

A Dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering by

Bipul Agarwal

Committee in charge:

Professor Mark Rodwell, Chairperson Professor John Bowers Professor Stephen Long Professor Umesh Mishra

March 1998

| The dissertation of Bipul Agarwal is approved: |

|------------------------------------------------|

|                                                |

|                                                |

|                                                |

|                                                |

| Committee Chairperson                          |

March 1998

Copyright by

Bipul Agarwal

1998

to my

parents

## Acknowledgments

I would like to thank my advisor Prof. Mark Rodwell for his constant encouragement, interest, assistance and suggestions during the course of this project. I am very grateful to him for being so caring and understanding, and always being available.

My committee members have been very helpful and nice to me and I am honored to have them on my committee. I would like to thank the excellent faculty at UCSB for making graduate study very intellectually stimulating and satisfying.

Having knowledgeable, perseverant and sociable group-mates have made working jointly on this project very rewarding, challenging and fun. The efforts of the clean room staff in maintaining the equipment and supplies is commendable. Without their sincere dedication, this project would have taken much longer. Thanks are due to the ECE Department staff for their constant and continued support and assistance.

My roommates and friends have made my stay away from home in beautiful Santa Barbara an experience to be cherished for a lifetime.

My parents and my sisters have been my inspiration through this odyssey called "Ph. D.". Their generous blessings and prayers have enabled me to succeed in all my endeavors.

## Vita

- December 15, 1969: born in Cuttack, India.

- July 1988 June 1992 : B. Tech., Electronics and Communication Engineering, Indian Institute of Technology, Madras, India.

- 1992 1993 : Research Assistant, Department of Electrical Engineering, Indian Institute of Technology, Madras, India.

- September 1993 May 1995 : M. S., Electrical Engineering (Solid State), University of California, Santa Barbara.

- September 1993 February 1998 : Ph. D., Department of Electrical and Computer Engineering (Solid State), University of California, Santa Barbara.

### **Publications**

- B. Agarwal, D. Mensa, R. Pullela, Q. Lee, U. Bhattacharya, L. Samoska, J. Guthrie and M. J. W. Rodwell, "A 277 GHz f<sub>max</sub> transferredsubstrate heterojunction bipolar transistor", International Conference on Indium Phosphide and Related Materials Technical Digest, 1997, pp. 633-636.

- 2. B. Agarwal, D. Mensa, Q. Lee, R. Pullela, J. Guthrie, L. Samoska and M. J. W. Rodwell "A 50 GHz feedback amplifier with AlInAs/GaInAs transferred-substrate HBT", *International Electron Devices Meeting Technical Digest*, 1997, pp. 743-746.

- 3. B. Agarwal, R. Pullela, U. Bhattacharya, D. Mensa, Q. Lee, L. Samoska, J. Guthrie and M. J. W. Rodwell, "Ultrahigh  $f_{max}$  AlInAs/GaInAs transferred-substrate heterojunction bipolar transistors for integrated circuit applications", to appear, International Journal of High Speed Electronics and Systems, 1998, (invited paper).

- B. Agarwal, D. Mensa, R. Pullela, Q. Lee, U. Bhattacharya, L. Samoska, J. Guthrie and M. J. W. Rodwell, "A 277 GHz f<sub>max</sub> transferredsubstrate heterojunction bipolar transistor", IEEE Electron Device Letters, vol. 18, no. 4, pp. 228-231, 1997.

- 5. B. Agarwal, R. Pullela, U. Bhattacharya, D. Mensa, Q. Lee, L. Samoska, J. Guthrie and M. J. W. Rodwell, "Ultrahigh f<sub>max</sub> AlInAs/GaInAs transferred-substrate heterojunction bipolar transistors for integrated circuit applications", to appear, Current Trends in Heterojunction Bipolar Transistors, 1998, (book chapter).

- 6. B. Agarwal, A. E. Schmitz, J. J. Brown, M. Le, M. Lui and M. J. W. Rodwell, "A 1-157 GHz InP HEMT traveling-wave amplifier", to be presented, 1998 MTT-S RFIC Symposium.

- 7. B. Agarwal, R. Pullela, Q. Lee, D. Mensa, J. Guthrie and M. J. W. Rodwell, "80 GHz distributed amplifiers with transferred-substrate heterojunction bipolar transistors", to be presented, 1998 MTT-S International Microwave Symposium.

- 8. B. Agarwal, Q. Lee, R. Pullela, D. Mensa, J. Guthrie and M. J. W. Rodwell, "A 50 GHz broadband differential amplifier with transferred-substrate HBTs", submitted, International Conference on Indium Phosphide and Related Materials, 1998.

- 9. B. Agarwal, Q. Lee, R. Pullela, D. Mensa, J. Guthrie and M. J. W. Rodwell, "Broadband feedback amplifiers with AlInAs/GaInAs transferred-substrate HBTs", submitted, IEEE Microwave and Guided Wave Letters, 1998.

- B. Agarwal, Q. Lee, R. Pullela, D. Mensa, J. Guthrie and M. J. W. Rodwell, "A transferred-substrate HBT wideband differential amplifier to 50 GHz", submitted, IEEE Microwave and Guided Wave Letters, 1998.

- 11. B. Agarwal, Q. Lee, R. Pullela, D. Mensa, J. Guthrie and M. J. W. Rodwell, "80 GHz distributed amplifiers with transferred-substrate heterojunction bipolar transistors", submitted, IEEE Trans. MTT, Special Issue 1998 MTT-S International Microwave Symposium.

- 12. B. Agarwal, A. E. Schmitz, J. J. Brown, M. Le, M. Lui and M. J. W. Rodwell, "A 1-157 GHz InP HEMT traveling-wave amplifier", submitted, IEEE Trans. on MTT, Special Issue IEEE 1998 MTT-S RFIC Symposium.

- 13. B. Agarwal, E. Sovero, D. Deakin and M. J. W. Rodwell, "A distributed modulator driver for 40 Gbit/s fiber-optic transmission implemented in GaAs PHEMT technology", submitted, IEEE GaAs IC Symposium, 1998.

- B. Agarwal, J. Guthrie, Q. Lee, D. Mensa, R. Pullela and M. J. W. Rodwell, "Recent results of transferred-substrate HBTs", Workshop on Compound Semiconductors, Materials and Devices (WOC-SEMAD), Monterrey, California, February 16-18, 1998.

- 15. Q. Lee, B. Agarwal, D. Mensa, R. Pullela, J. Guthrie, L. Samoska and M. J. W. Rodwell, "A > 400 GHz  $f_{max}$  transferred-substrate heterojunction bipolar transistor IC technology", *IEEE Electron Device Letters*, vol. 19, pp. 77-79, 1998.

- 16. J. Pusl, B. Agarwal, R. Pullela, L. D. Nguyen, M. V. Le, M. J. W. Rodwell, L. Larson, J. F. Jensen, R. Y. Yu and M. G. case, "Capacitive-division traveling-wave amplifier with 340 GHz gain-bandwidth product", *IEEE Microwave and Millimeter-Wave Monolithic Circuits Symposium Digest*, 1995, pp. 175-178.

- 17. R. Pullela, B. Agarwal, Q. Lee, D. Mensa, J. Guthrie, L. Samoska and M. J. W. Rodwell, "Ultrafast transferred-substrate heterojunction bipolar transistor ICs for high-speed fiber-optic transmission", to be presented, Optical Fiber Conference, 1998, (invited paper).

- 18. R. Pullela, Q. Lee, B. Agarwal, D. Mensa, J. Guthrie, L. Samoska, and M. Rodwell, "A > 400 GHz  $f_{max}$  transferred-substrate HBT integrated circuit technology", *Device Research Conference Technical Digest*, 1997, pp. IIIB-2.

- J. Guthrie, D. Mensa, B. Agarwal, Q. Lee, R. Pullela and M. J. W. Rodwell, "HBT IC process with a copper substrate", submitted, Electronics Letters, 1998.

- 20. R. Pullela, D. Mensa, B. Agarwal, J. Guthrie, M. Rodwell, "47 GHz static frequency divider in ultrafast transferred-substrate heterojunction bipolar transistor technology", to be presented, International Conference on Indium Phosphide and Related Materials, 1998.

- 21. M. J. W. Rodwell, R. Pullela, B. Agarwal, M. Reddy, Q. Lee, J. Guthrie, D. Mensa, L. Samoska, S. C. Martin and R. P. Smith, "Submicron lateral scaling of vertical-transport devices: transferred-substrate bipolar transistors and Schottky-collector tunnel diodes", *Ultrafast Electronics and Optoelectronics Technical Digest*, 1997, pp. 192-194, (invited paper).

- L. Samoska, R. Pullela, B. Agarwal, D. Mensa, Q. Lee, V. Kaman, J. Guthrie, and M. J. W. Rodwell, "InP heterojunction bipolar transistor decision circuits", to be presented, MTT-S International Microwave Symposium, 1998.

- 23. M. J. W. Rodwell, J. E. Bowers, R. Pullela, K. Giboney, J. Pusl, B. Agarwal, and L. D. Nguyen, "Electronic & optoelectronic components for fiber transmission at bandwidths approaching 100 GHz",

- LEOS Summer Topical Meeting on RF Optoelectronics Technical Digest, 1995, (invited paper).

- 24. U. Bhattacharya, L. Samoska, R. Pullela, J. Guthrie, Q. Lee, B. Agarwal, D. Mensa and M. J. W. Rodwell, "170 GHz transferred-substrate heterojunction bipolar transistor", *Electronics Letters*, vol. 32, pp. 1405-1406, 1996.

## Awards

- 1. Best Student Paper Award at the 1997 International Conference on Indium Phosphide and Related Materials.

- 2. Gold Medal at the Indian Association of Physics Teachers National Standard Examination in Physics, 1988.

- 3. Merit Certificate at the 1988 Indian National Mathematics Olympiad.

- 4. Indian Institute of Technology Merit Scholarship, 1988-1992.

#### Abstract

# Analog Integrated Circuits with AlInAs/GaInAs Transferred-Substrate HBTs

by Bipul Agarwal

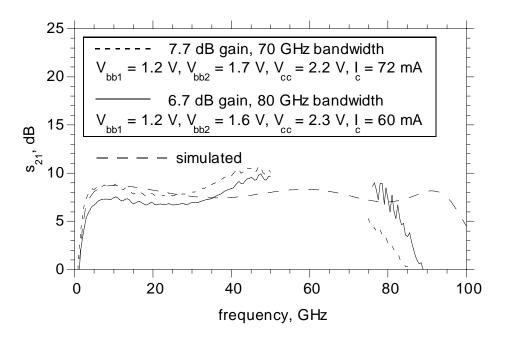

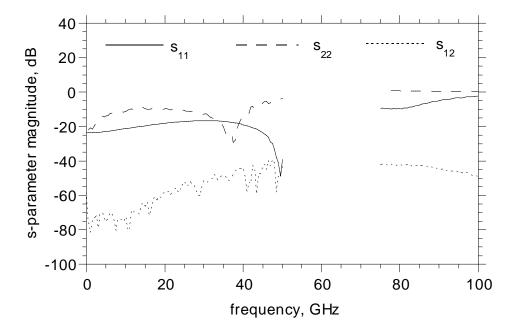

A variety of analog integrated circuits for wideband systems including fiber-optic communication systems have been designed and fabricated in the transferred-substrate heterojunction bipolar transistors integrated circuit technology. Transferred-substrate HBTs have demonstrated very high  $f_{max}$  (>400 GHz), and are thus potential candidates for future, veryhigh speed integrated circuits. The high bandwidth of transferred-substrate HBTs is due to the process of substrate transfer, which allows lithographically defined, narrow and aligned collector and emitter stripes on opposite sides of the base epitaxial layer. Transistor bandwidth then becomes inversely proportional to the stripe width, increasing rapidly with scaling. An IC fabrication process has been developed, incorporating transferredsubstrate HBTs, nichrome resistors, silicon nitride metal-insulator-metal capacitors, low-loss microstrip transmission lines, and three levels of interconnect metallization. The interconnects, microstrip on Benzocyclobutene (low dielectric constant), provide a low-capacitance wiring environment. A gold ground plane and short ground vias through the thin Benzocyclobutene substrate provide low ground-return inductance. Electroplated gold thermal vias provide transistor heat-sinking. These unique features of the transferred-substrate HBT IC process have enabled very high performance ICs. Four different integrated circuits with varying levels of integration were designed and fabricated. The first demonstration IC, a Darlington feedback amplifier, with two transistors, had 13 dB gain, 50 GHz bandwidth. An improvement on this basic design, a Darlington-cascode amplifier with three transistors had 11 dB gain and greater than 50 GHz bandwidth. A traveling-wave amplifier with six transistors had 6.7 dB gain, 85 GHz bandwidth. A differential amplifier with twenty-two transistors had 50 GHz bandwidth, 11 dB gain. These amplifiers, the first integrated circuits fabricated in the transferred-substrate technology, exhibit record performance and good yield. Higher scales of integration and high-performance ICs for future high-speed systems should soon be possible.

# Contents

| 1 | Introduction 1.1 ICs for Fiber-Optic Systems          | 1<br>2<br>4                        |

|---|-------------------------------------------------------|------------------------------------|

| 2 | Transferred-Substrate HBTs : Theory                   | 7                                  |

| 3 | Fabrication3.1 MBE layer structure3.2 Fabrication     | 25<br>25<br>27                     |

| 4 | Device Results 4.1 Test structures                    | 43<br>45<br>49<br>56               |

| 5 | Integrated Circuits 5.1 Darlington feedback amplifier | 77<br>78<br>93<br>97<br>102<br>109 |

| 6 | Conclusions                                           | 115                                |

| A | A.1 Emitter Contacts                                  |                                    |

| A.4  | Mesa Isolation          |

|------|-------------------------|

| A.5  | Resistors               |

| A.6  | Polyimide Planarization |

| A.7  | Metal 1                 |

| A.8  | Silicon Nitride         |

| A.9  | Metal 2                 |

| A.10 | Substrate transfer      |

| A 11 | Collector 14            |

# List of Figures

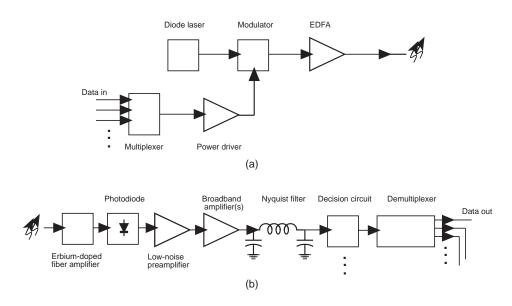

| 1.1 | Block diagram of a typical fiber-optic system showing a) transmitter and b) receiver.                                                                                                                                                      | 2               |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

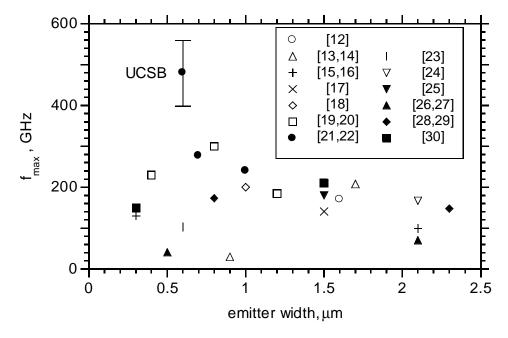

| 2.1 | Comparison of $f_{max}$ and emitter width for some HBTs in the literature.                                                                                                                                                                 | 8               |

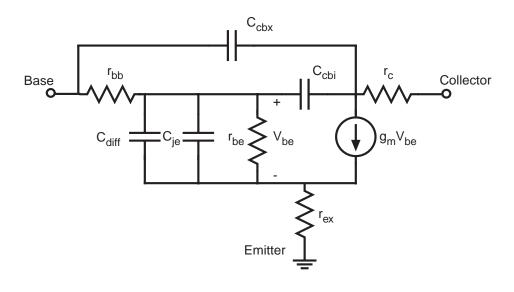

| 2.2 | Hybrid- $\pi$ model of a HBT for calculation of the short-circuit current gain.                                                                                                                                                            | 9               |

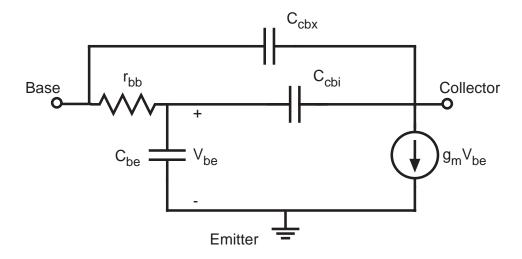

| 2.3 | Simplified hybrid- $\pi$ model of a HBT for calculation of power gain                                                                                                                                                                      | 11              |

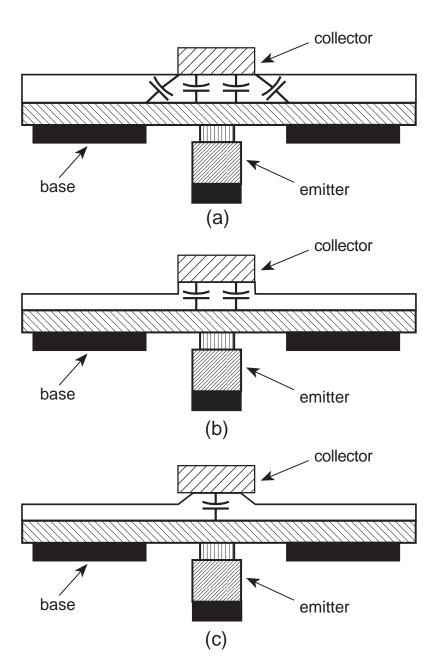

| 2.4 | Schematic cross-section of a double-mesa HBT                                                                                                                                                                                               | 13              |

| 2.5 | Schematic cross-section of a transferred-substrate HBT                                                                                                                                                                                     | 15              |

| 2.6 | The first transferred-substrate HBT                                                                                                                                                                                                        | 18              |

| 2.7 | Schematic cross-section of device structure reported in this thesis. While (a) the emitter or (b) the collector could be the top electrode in this figure, the text explains the motivation for using the collector as the upper electrode | 21              |

| 2.8 | Recess etching the collector to reduce fringing collector-base capacitance.                                                                                                                                                                | 23              |

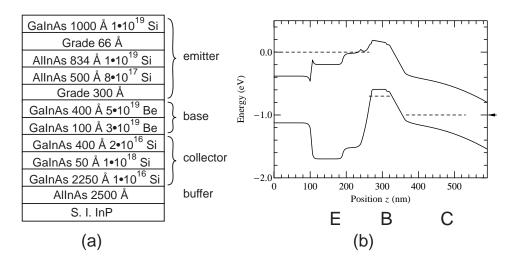

| 3.1 | (a) MBE layer structure and (b) Band diagram under forward bias                                                                                                                                                                            | 26              |

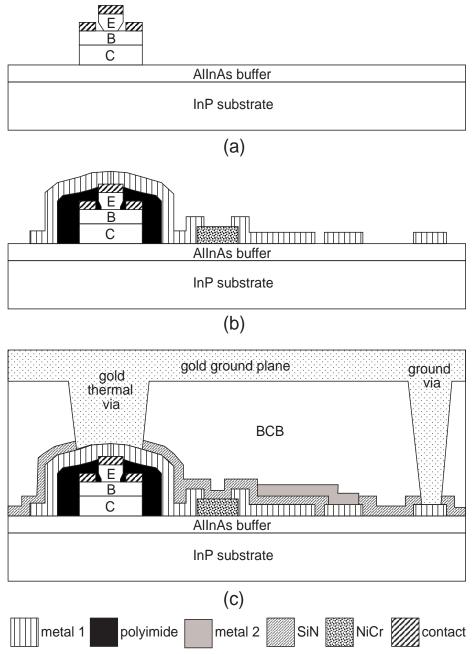

| 3.2 | ward bias.  Fabrication process for transferred-substrate HBTs.                                                                                                                                                                            | $\frac{20}{28}$ |

| 3.3 | Fabrication process for transferred-substrate HBTs (contd.).                                                                                                                                                                               | $\frac{20}{29}$ |

| 3.4 | SEM cross-section of device after emitter-base etch                                                                                                                                                                                        | $\frac{20}{30}$ |

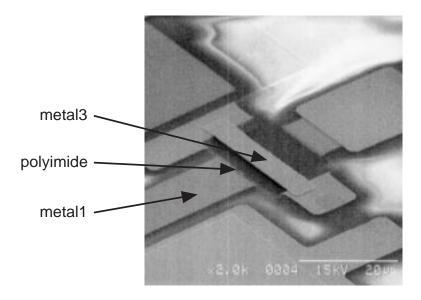

| 3.5 | Polyimide planarization of the emitter finger                                                                                                                                                                                              | 31              |

| 3.6 | Wafer after polyimide etching                                                                                                                                                                                                              | 31              |

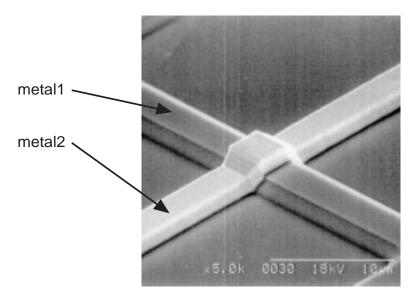

| 3.7 | Wafer after the first level of metallization.                                                                                                                                                                                              | 32              |

| 3.8 | Wafer after second level of metallization                                                                                                                                                                                                  | 33              |

|     |                                                                                                                                                                                                                                            |                 |

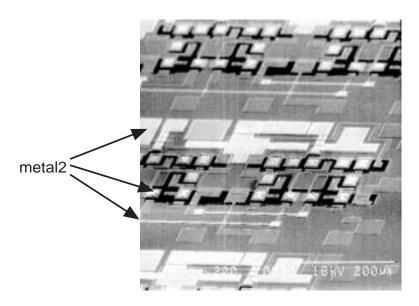

| 3.9  | Wafer after M2 evaporation                                                                               | 34  |

|------|----------------------------------------------------------------------------------------------------------|-----|

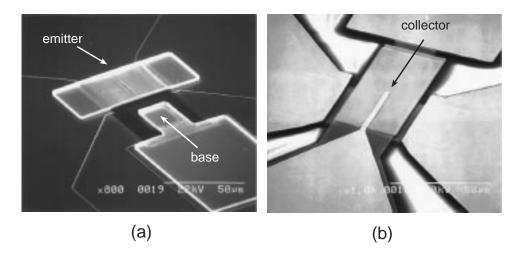

| 3.10 | SEM photomicrograph of device after (a) partial fabrication                                              |     |

|      | and (b) complete fabrication                                                                             | 34  |

| 3.11 | Wafer after InP substrate removal.                                                                       | 35  |

| 3.12 | Wafer after collector (M3) evaporation                                                                   | 36  |

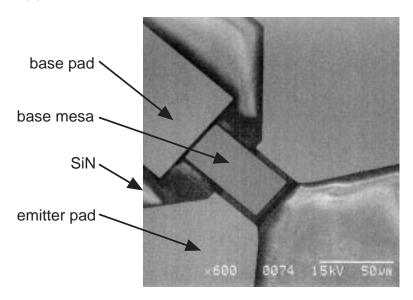

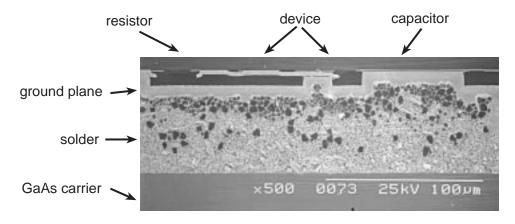

|      | SEM photomicrograph of cross-section through an IC                                                       | 37  |

| 3.14 | Fabrication process for devices with non-grounded emitters.                                              | 38  |

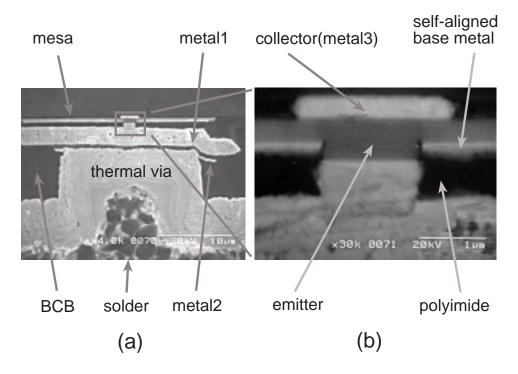

| 3.15 | SEM photomicrograph of (a) cross-section through a device                                                |     |

|      | and (b) close-up of intrinsic device                                                                     | 39  |

| 3.16 | Photomicrograph of part of a wafer with ICs and discrete                                                 |     |

|      | devices.                                                                                                 | 40  |

| 4.1  | MBE layer structures of wafers A, B & C                                                                  | 44  |

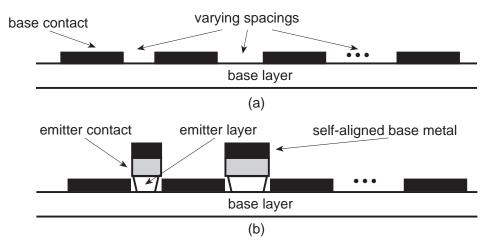

| 4.2  | TLM patterns (a) normal and (b) with emitters                                                            | 45  |

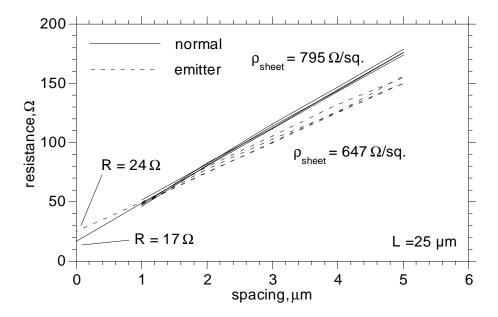

| 4.3  | TLM measurements for normal and pinched TLMs across a                                                    |     |

|      | quarter of a 2-inch wafer with a 400 Å thick base doped at                                               |     |

|      | $5 \times 10^{19}/cm^2$                                                                                  | 47  |

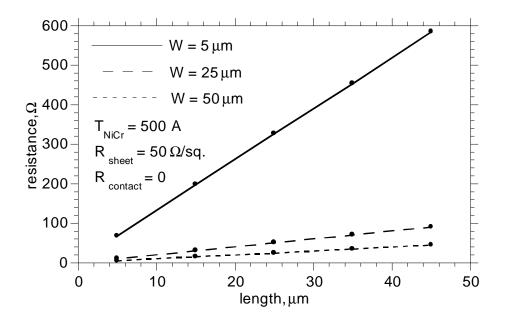

| 4.4  | Variation of resistance with length and width for NiCr resistors.                                        | 48  |

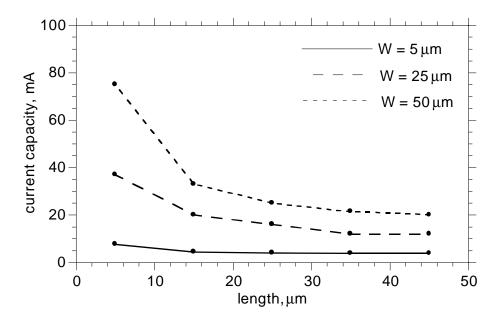

| 4.5  | Current capacity of NiCr resistors for varying geometry                                                  | 48  |

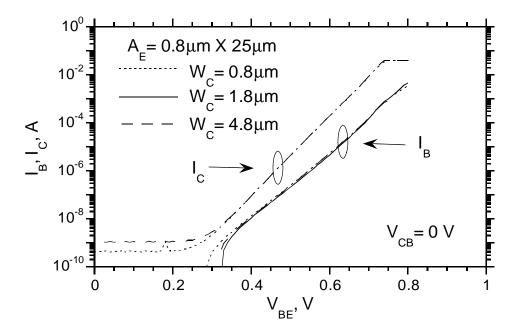

| 4.6  | Gummel plots of transferred-substrate HBTs with 0.8 $\mu$ m ×                                            | 0   |

|      | $25 \mu \text{m}$ emitters and $29 \mu \text{m}$ long collectors of different widths.                    | 50  |

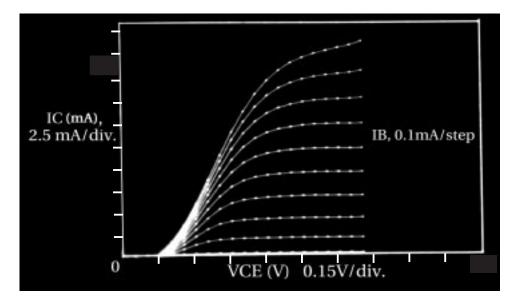

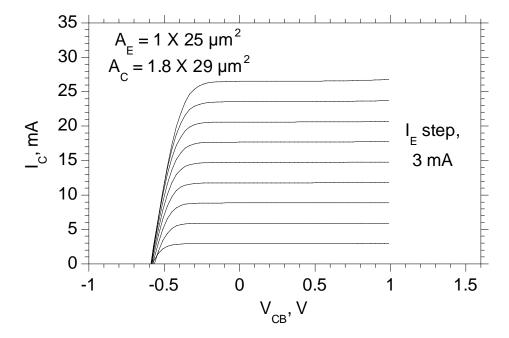

| 4.7  | DC common-emitter characteristics of devices on wafer A                                                  | -0  |

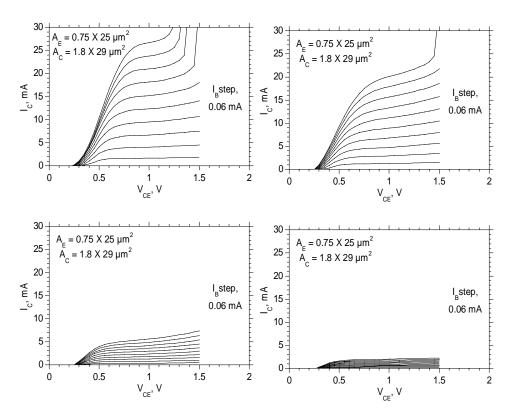

| 4.0  | with 0.7 $\mu$ m × 25 $\mu$ m emitters and 1.6 $\mu$ m × 29 $\mu$ m collectors.                          | 50  |

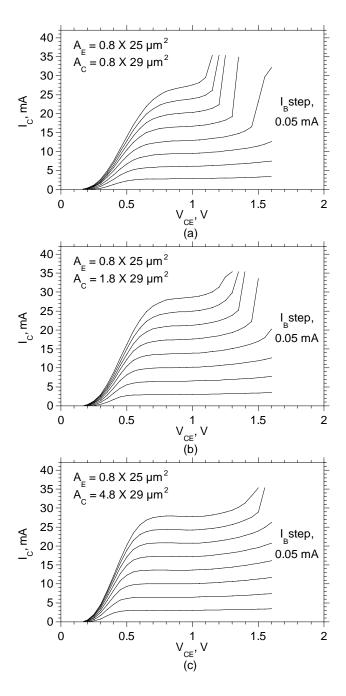

| 4.8  | DC common-emitter characteristics of devices on wafer B                                                  |     |

|      | with 0.8 $\mu$ m × 25 $\mu$ m emitters and (a) 0.8 $\mu$ m × 29 $\mu$ m                                  |     |

|      | collectors, (b) 1.8 $\mu$ m × 29 $\mu$ m collectors and (c) 4.8 $\mu$ m × 29 $\mu$ m collectors          | 52  |

| 4.9  | DC common-base characteristics of devices with 0.8 $\mu$ m ×                                             | UZ. |

| 4.3  | 25 $\mu$ m emitters and 1.8 $\mu$ m × 29 $\mu$ m collectors                                              | 54  |

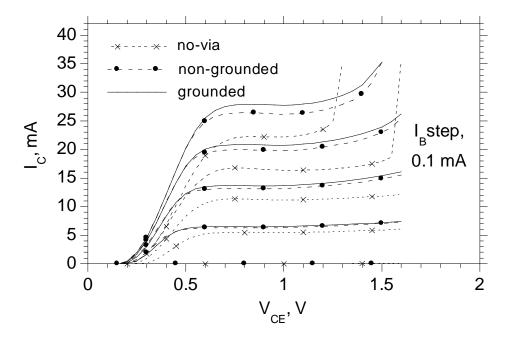

| 4 10 | DC common-emitter characteristics of device with different                                               | 01  |

| 1,10 | heat-sink structures; emitter and collector dimensions are 0.8                                           |     |

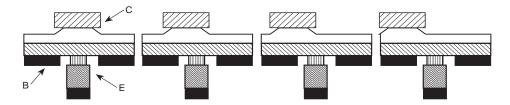

|      | $\mu \mathrm{m} \times 25~\mu \mathrm{m}$ and $4.8~\mu \mathrm{m} \times 29~\mu \mathrm{m}$ respectively | 55  |

| 4.11 | An array of devices with the collector offset from the emitter                                           |     |

|      | in steps of $0.5~\mu\mathrm{m}$ .                                                                        | 56  |

| 4.12 |                                                                                                          |     |

|      | collector on DC common-emitter characteristics of devices                                                | 57  |

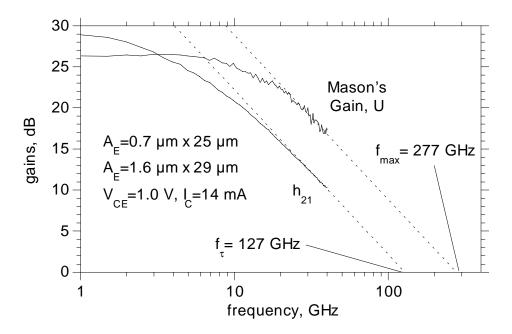

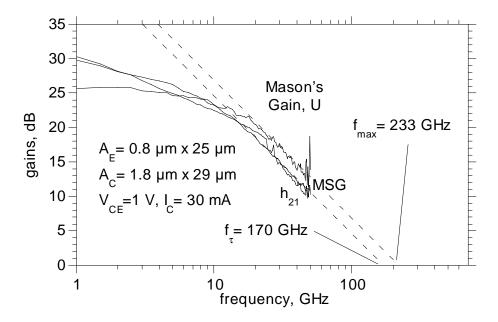

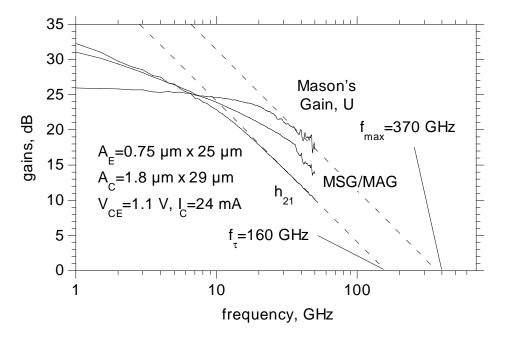

| 4.13 | RF characteristics of devices from wafer A with 0.7 $\mu$ m × 25                                                                    |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | $\mu$ m emitters and 1.6 $\mu$ m × 29 $\mu$ m collectors                                                                            | 58  |

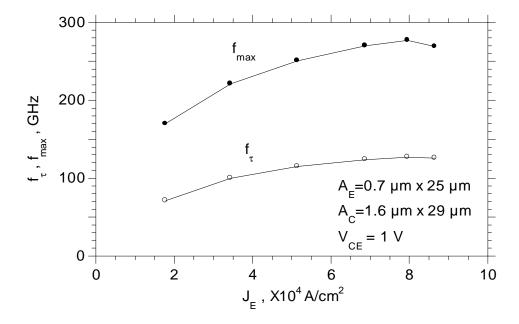

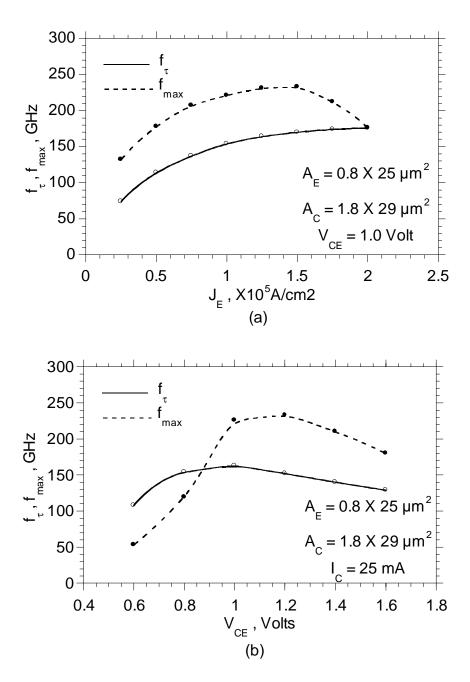

| 4.14 | Variation of $f_{\tau}$ and $f_{max}$ with emitter current density for                                                              |     |

|      | devices on wafer A                                                                                                                  | 59  |

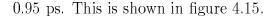

| 4.15 | Extraction of forward transit time for devices on wafer A                                                                           | 60  |

| 4.16 | RF characteristics of devices from wafer B with 0.8 $\mu m \times 25$                                                               |     |

|      | $\mu$ m emitters and 1.8 $\mu$ m × 29 $\mu$ m collectors                                                                            | 61  |

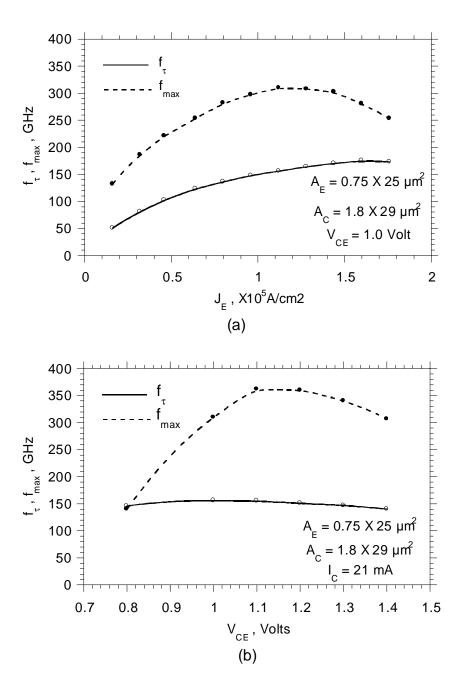

| 4.17 | Variation of $f_{\tau}$ and $f_{max}$ with (a) emitter current density and                                                          | 0.0 |

|      | (b) collector-emitter voltage for devices from wafer B                                                                              | 63  |

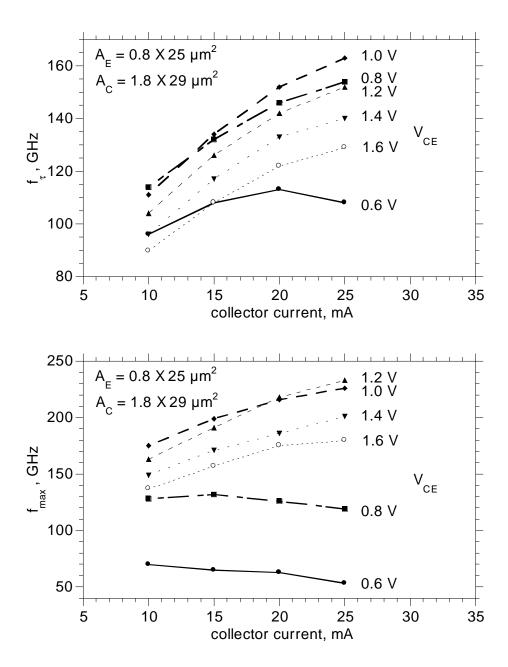

| 4.18 | Variation of $f_{\tau}$ and $f_{max}$ with collector current for various                                                            | 0.4 |

| 1 10 | collector-emitter voltages for devices from wafer B                                                                                 | 64  |

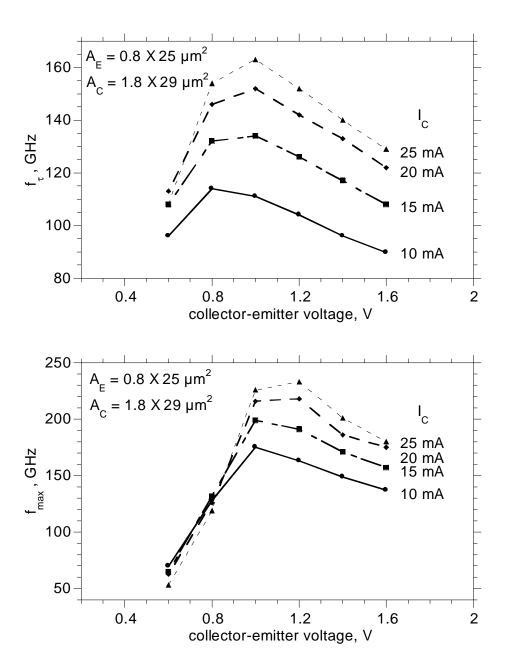

| 4.19 | Variation of $f_{\tau}$ and $f_{max}$ with collector-emitter voltage for                                                            | C F |

| 4.00 | various collector currents for devices from wafer B                                                                                 | 65  |

| 4.20 | RF characteristics of devices from wafer C with 0.75 $\mu$ m ×                                                                      | 66  |

| 4.01 | 25 $\mu$ m emitters and 1.8 $\mu$ m × 29 $\mu$ m collectors                                                                         | 00  |

| 4.21 | Variation of $f_{\tau}$ and $f_{max}$ with (a) emitter current density and (b) collector emitter valtage for devices from wafer $C$ | 67  |

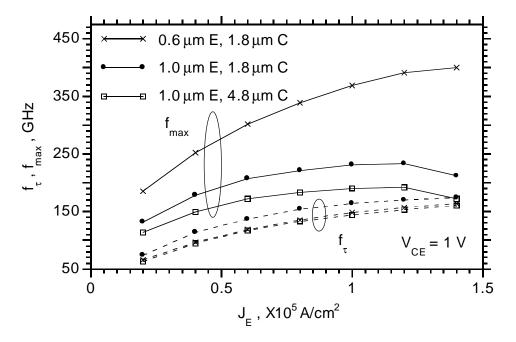

| 4 99 | (b) collector-emitter voltage for devices from wafer C Variation of $f_{\tau}$ and $f_{max}$ with $J_E$ for devices with different  | 07  |

| 4.22 | geometry                                                                                                                            | 68  |

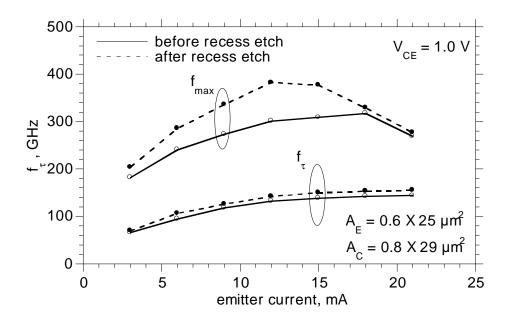

| A 23 | Effect of collector recess etch on RF performance                                                                                   | 70  |

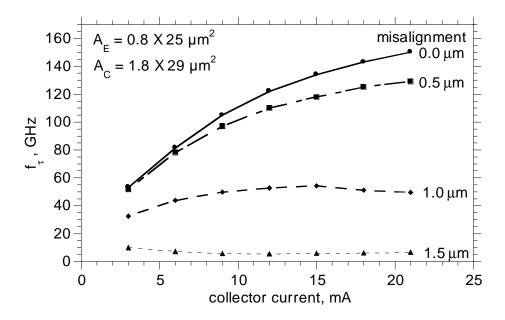

|      | Effect of misalignment between emitter and collector on $f_{\tau}$ .                                                                | 70  |

|      |                                                                                                                                     | 71  |

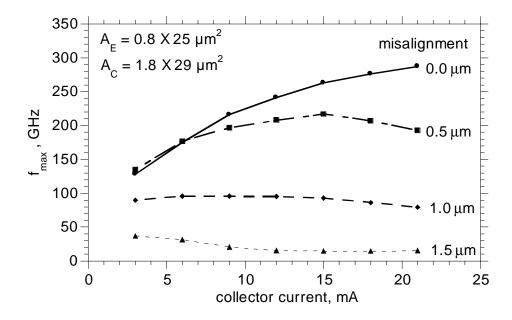

|      | Effect of misalignment between emitter and collector on $f_{\text{max}}$ .                                                          | 11  |

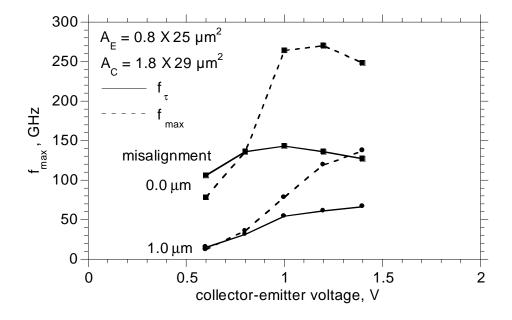

| 4.20 | Effect of misalignment between emitter and collector on $f_{\tau}$ and $f_{\text{max}}$ .                                           | 71  |

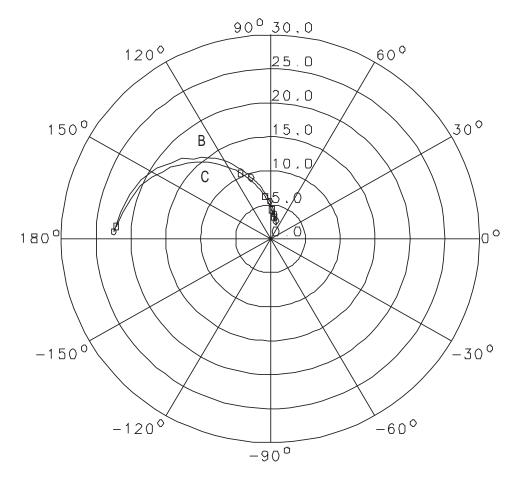

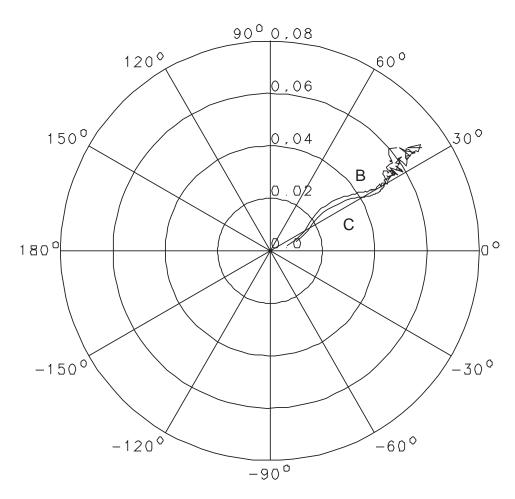

| 4 97 | Measured $s_{21}$ of devices from wafers B and C                                                                                    | 72  |

|      | Measured $s_{12}$ of devices from wafers B and C                                                                                    | 73  |

|      | Measured $s_{12}$ of devices from wafers B and C                                                                                    | 74  |

|      |                                                                                                                                     |     |

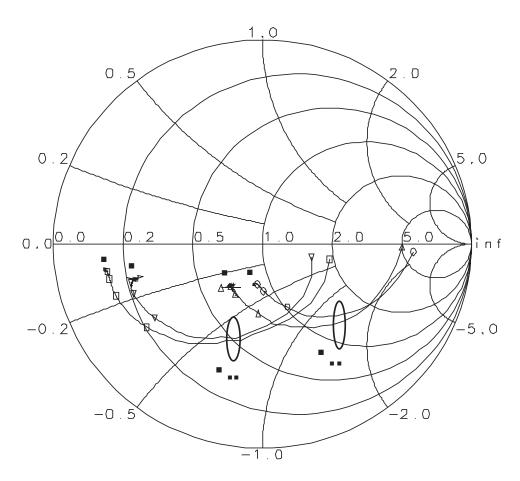

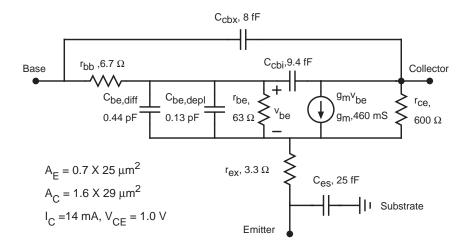

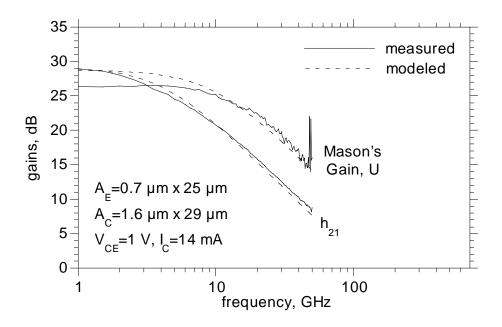

|      | Small-signal hybrid-pi model of devices from wafer A                                                                                | 75  |

| 4.01 | Comparison of measured and hybrid- $\pi$ modeled RF characteristics of devices from wafer A                                         | 76  |

|      | teristics of devices from water 11.                                                                                                 | 10  |

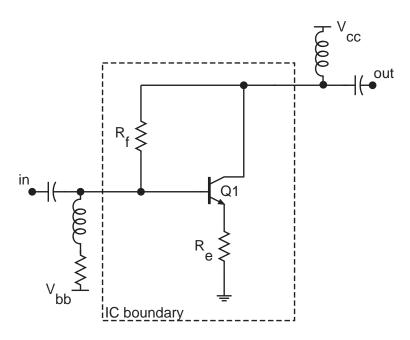

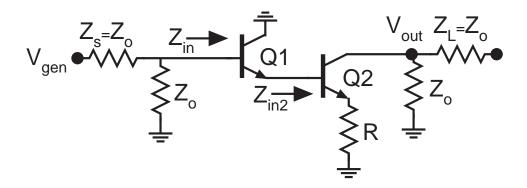

| 5.1  | Schematic circuit diagram of common-emitter resistive feed-                                                                         |     |

|      | back amplifier                                                                                                                      | 79  |

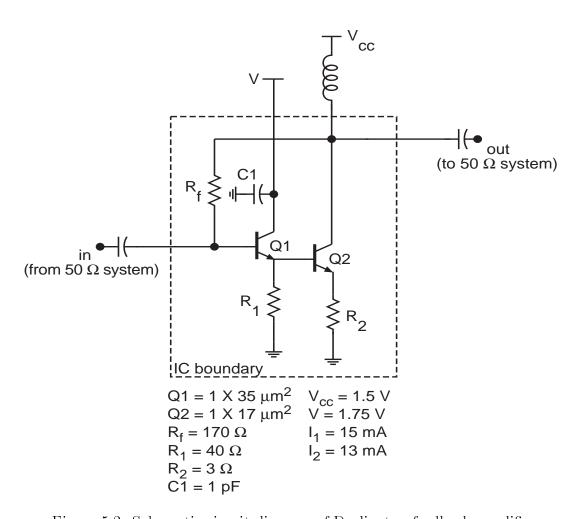

| 5.2  | Schematic circuit diagram of Darlington feedback amplifier                                                                          | 81  |

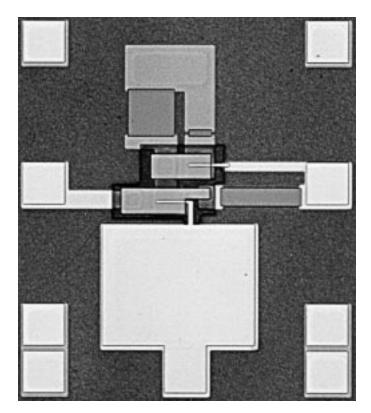

| 5.3  | Photomicrograph of the Darlington feedback amplifier                                                                                | 83  |

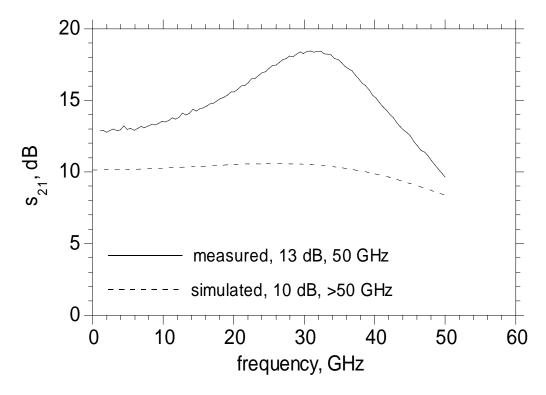

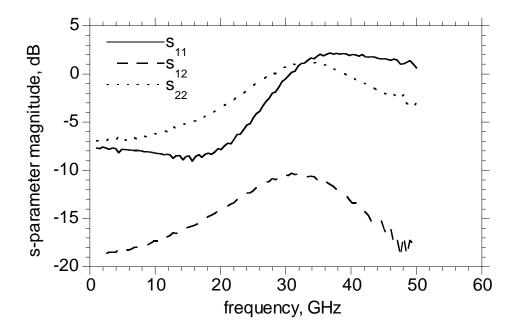

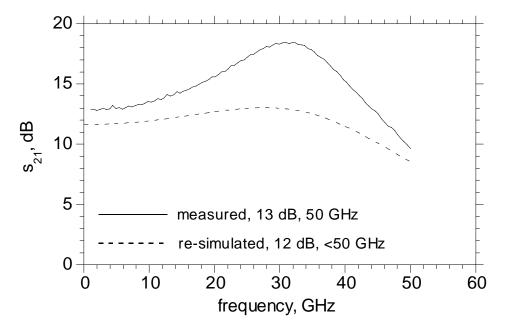

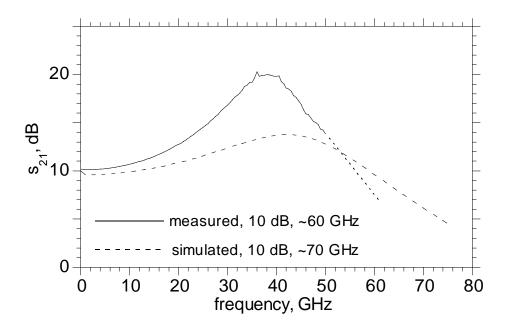

| 5.4           | Measured and simulated forward gain $s_{21}$ of the amplifier           |              |

|---------------|-------------------------------------------------------------------------|--------------|

|               | (wafer B). The simulation assumes the original model pa-                |              |

|               | rameters                                                                | 84           |

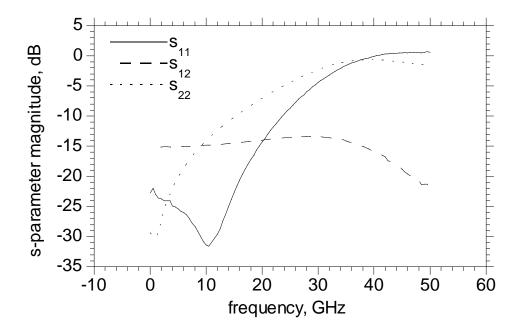

| 5.5           | Measured input return loss $s_{11}$ , output return loss $s_{22}$ , and |              |

|               | reverse isolation $s_{12}$ of the amplifier                             | 85           |

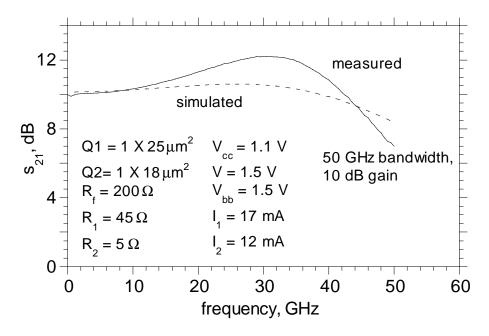

| 5.6           | Comparison of measured gain and simulated gain with new                 |              |

|               | transistor parameters.                                                  | 86           |

| 5.7           | Measured forward gain $s_{21}$ of the amplifier (wafer C)               | 87           |

| 5.8           | Measured input return loss $s_{11}$ , output return loss $s_{22}$ , and |              |

|               | reverse isolation $s_{12}$ of the amplifier                             | 88           |

| 5.9           | Simplified equivalent circuit of transistor for calculation of          |              |

|               | Darlington input impedance at high frequencies                          | 89           |

| 5.10          | A HBT Darlington feedback amplifier.                                    | 90           |

|               | A HBT mirror-Darlington feedback amplifier.                             | 92           |

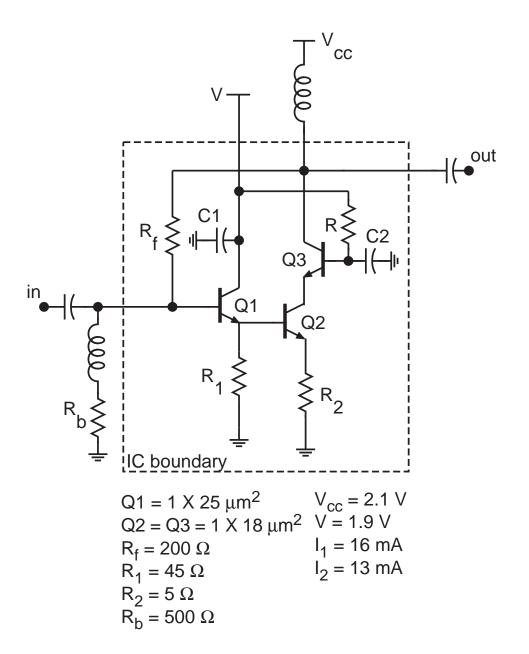

|               | Schematic circuit diagram of the Darlington-cascode feed-               | -            |

| J.11 <u>2</u> | back amplifier                                                          | 94           |

| 5 13          | Photomicrograph of the Darlington-cascode amplifier                     | 95           |

|               | Measured forward gain $s_{21}$ of the amplifier                         | 96           |

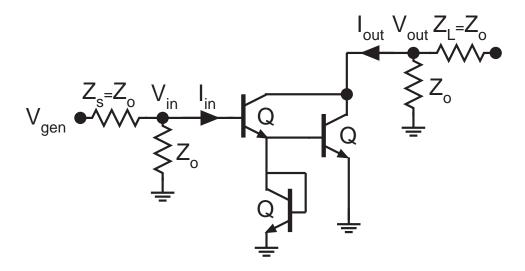

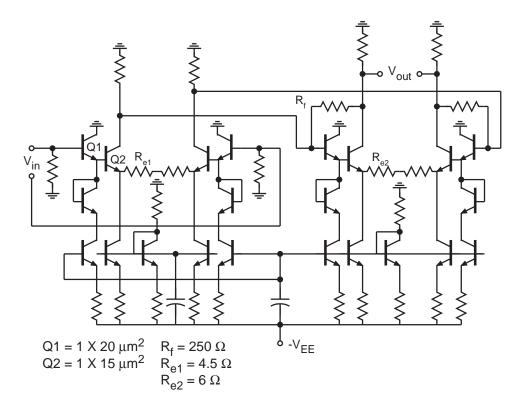

|               | Schematic circuit diagram of the differential amplifier                 | 97           |

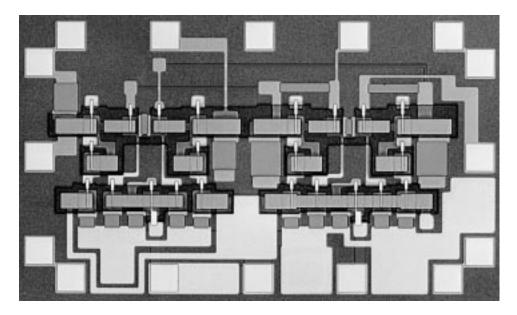

|               | Photograph of the differential amplifier IC (0.75 mm $\times$ 0.44      | 31           |

| 0.10          | mm)                                                                     | 99           |

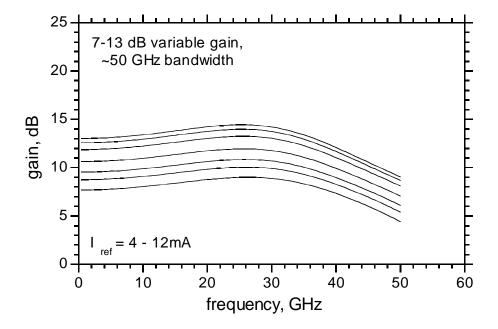

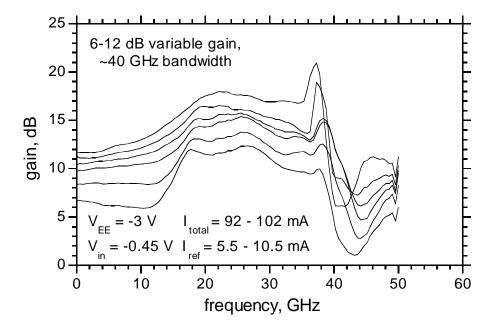

| 5 17          | Simulated variable forward gain $s_{21}$ of the amplifier. $I_{ref}$ is | 55           |

| 0.11          | the current through the reference transistor in the amplifier           |              |

|               | first stage                                                             | 100          |

| 5 18          | Measured variable forward gain $s_{21}$ of the amplifier. $I_{ref}$ is  | 100          |

| 0.10          | the current through the reference transistor in the amplifier           |              |

|               | first stage                                                             | 101          |

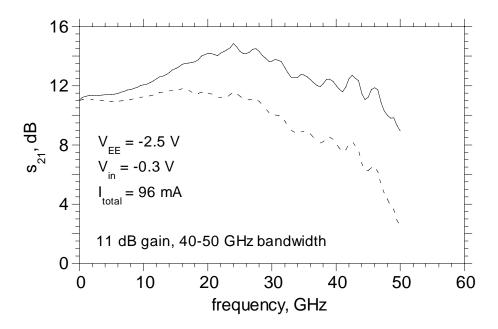

| 5 10          | Measured forward gain $s_{21}$ of the amplifier                         | 102          |

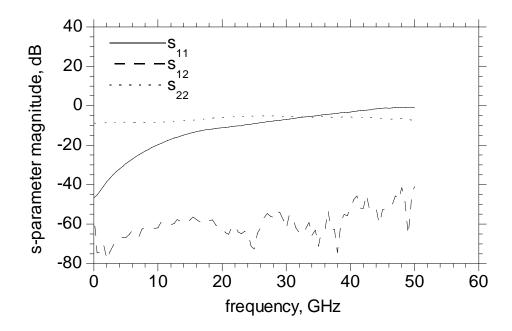

|               | Measured input return loss $s_{11}$ , output return loss $s_{22}$ , and | 102          |

| 0.20          | reverse isolation $s_{12}$ of the amplifier                             | 103          |

| 5.21          | (a) Small-signal equivalent circuit of the HBT and (b) sim-             | 100          |

| 0.21          | plified model                                                           | 104          |

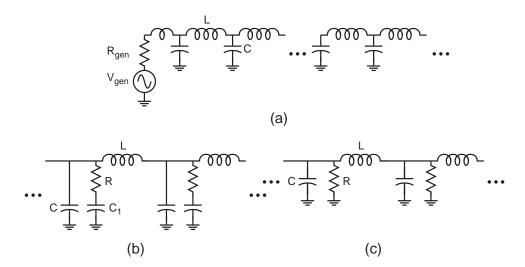

| 5 22          | Periodic synthetic transmission lines (a) without loss, (b)             | 104          |

| 0.22          | with frequency-dependent loss and (c) with frequency-independent        | lont         |

|               |                                                                         | 105          |

| 5 92          | loss                                                                    | 106          |

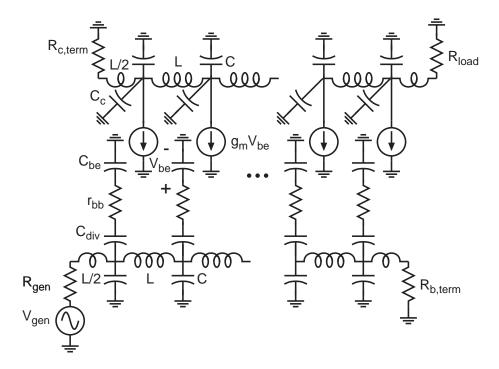

|               | Small signal model of the traveling-wave amplifier                      | $100 \\ 107$ |

| 0.24          | oman signal model of the traveling-wave ampliner                        | TOT          |

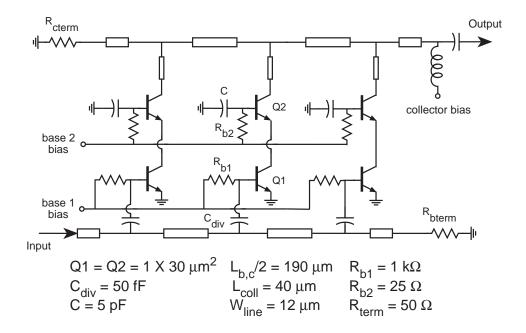

| 5.25 | Schematic circuit diagram of the HBT TWA                                | 111 |

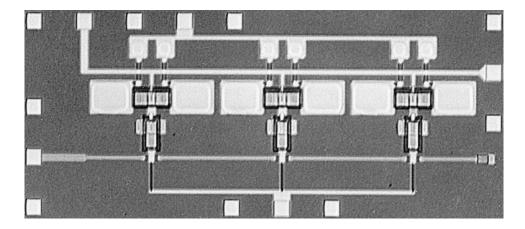

|------|-------------------------------------------------------------------------|-----|

| 5.26 | Photomicrograph of the HBT TWA                                          | 111 |

| 5.27 | Measured forward gain $s_{21}$ of the amplifier                         | 112 |

| 5.28 | Measured input return loss $s_{11}$ , output return loss $s_{22}$ , and |     |

|      | reverse isolation $s_{12}$ of the amplifier                             | 114 |

## Chapter 1

## Introduction

Fiber-optic communication systems are being used to transmit vast amounts of data at high speeds. They are employed in virtually all areas of telecommunication including trans-oceanic cables, long-haul terrestrial networks between cities, trunk-lines within metropolitan areas and subscriber loop systems. Recently, optical-fiber systems are being used for distribution of cable television and in local area networks for high-speed computer networking. The demand for higher bit-rate communication is rapidly growing as broadband integrated services involving multimedia become increasingly popular. 10 Gbit/s systems are being deployed and extensive research and development is being done for future 40 and 160 Gbit/s systems [1, 2, 3, 4, 5, 6]. Often, the transmission bit-rate of such systems is limited by the bandwidth of component electronic circuits in the transmitter and receiver. Circuit bandwidth is directly related to the device bandwidth, and is also influenced by circuit design and physical layout, power and cost budget, and communication strategies used. To meet the ever-increasing demand for higher bit-rates, circuit speed, and hence, device bandwidth must be continuously increased. Typically, device bandwidth is improved by scaling critical lithographic dimensions of the device, as well as by improvements in epitaxial growth and fabrication processes. The aim of this thesis was to develop a integrated circuit (IC) process incorporating a scalable device, and to demonstrate some first-generation ICs for future high-speed fiber-optic systems.

This chapter describes a typical fiber-optic communication system and the specific ICs of the system that have been examined in this thesis. Implementation technologies (HEMT/HBT) are briefly discussed. The second chapter describes the important theoretical aspects of transferred-substrate HBTs. Chapter 3 deals with the device and IC technology in detail, including material growth and IC fabrication process. Electrical characteristics and device modeling are covered in chapter 4. Circuit design, simulations and circuit results are dealt with in chapter 5. Finally, chapter 6 draws conclusions from this work and projects future directions.

#### 1.1 ICs for Fiber-Optic Systems

Figure 1.1: Block diagram of a typical fiber-optic system showing a) transmitter and b) receiver.

Figure 1.1 shows the block diagram of a typical fiber-optic communication system. The transmitter consists of a multiplexer (MUX) which combines several channels of digital data into one data stream at a higher bit-rate. This electrical data is then converted into a optical signal through a laser. The electrical signal could directly modulate the laser intensity, but is limited by laser bandwidth and chirp for data rates above 10 Gbit/s. At higher data rates, an external electro-optic modulator with a driver is used as shown. The modulated signal is transmitted via a optical fiber to

its destination. Post-amplification through erbium-doped fiber amplifiers (EDFAs) may be used to boost transmitter power. During transmission, the signal may be amplified or regenerated using optoelectronic repeaters, especially for long distances. At the receiver end, more EDFAs may be used to pre-amplify the signal. The optical signal is converted back to an electrical signal using a photodiode. A low-noise transimpedance preamplifier converts the small signal current generated by the photodiode into a signal voltage. The signal voltage is amplified by the main amplifier. Decision circuits then regenerate the actual transmitted digital data. This recovered data is then demultiplexed (DEMUXed) into the individual lower bit-rate data channels. A clock recovery circuit (not shown) extracts the clock (required by the DEMUX and decision circuits) from the amplified signal from the main amplifier. The positions of the DEMUX and the decision circuits in the link are interchanged in some cases. If the decision circuit is after the DEMUX, it needs to operate only at the single channel bitrate, but one circuit is needed for each data channel. As we can see, there are several important analog and digital circuits in the system which will determine the overall speed of the system. This thesis concentrates on the analog circuits within the fiber link. These include the laser driver, the transimpedance preamplifier, and the main amplifier. The performance requirements of each of these ICs will now be examined in more detail.

Modulator drivers are among the more difficult ICs to implement, as their output waveform must be large in amplitude and directly determines the shape of the transmitted optical signal. A wide bandwidth ( $\sim 0.7 \times$  bit-rate) is required at absolute minimum. High modulator driver output power is required because of the modulator's typical  $V_{\pi}$  of  $\sim 10$  V and its  $\sim 50~\Omega$  impedance. In-band gain flatness is important to preserve the shape of the incoming signal. The driver should have a low low-frequency cut-off for acceptable eye closure with long data sequences.

The transimpedance preamplifier determines the receiver signal-to-noise ratio and hence sensitivity. This stage must have a low input-referred noise current and flat gain over the signal bandwidth. Transimpedance (feedback) loading is often used to aid in simultaneously meeting noise and bandwidth constraints. The preamplifier frequently must also act as a single-end-to-differential converter if the subsequent gain stages are designed for differential operation.

Fiber-optic receivers require substantial amplification between the tran-

simpedance preamplifier stage output and the decision circuit input. The main amplifier, referred to as the linear channel provides this gain. Because there are many cascaded stages, the gain and group delay must be substantially flat over a bandwidth extending from a few KHz up to about 70% of the data rate. AGC or *symmetric* limiting characteristics are also required. To meet these requirements, broadband multistage differential amplifiers are generally employed. As mentioned earlier, differential or single-ended operation can be employed. The advantages of differential operation compared to single-ended are improved immunity to electromagnetic crosstalk, good common mode suppression, ease of dc biasing and symmetric nonsaturating limiting characteristics. The amplifiers could be implemented in either lumped or distributed configuration. Distributed amplifiers generally obtain a higher bandwidth in a given transistor technology. However, good low-frequency response is difficult to achieve, in-band gain ripple is often present and die areas are large. Lumped amplifiers can be DC coupled, have smaller die areas and smooth gain-frequency characteristics.

#### 1.2 Technology

High-speed fiber-optic systems require wideband circuits, which in turn require very high device bandwidths. Device bandwidth is indicated by two common figures of merit:  $f_{\tau}$ , the current gain cut-off frequency, and  $f_{max}$ , the power gain cut-off frequency. For 100 Gbit/s fiber-optic communication ICs, circuit bandwidths must be  $\sim 70$  GHz, and devices having  $f_{\tau}$ and  $f_{max}$  in excess of 200-250 GHz are required [7]. Future, higher bit-rate systems will require even higher device bandwidths. The two dominant high frequency transistors are high electron mobility transistors (HEMTs) and heterojunction bipolar transistors (HBTs), both based on compound semiconductors. Early work in this thesis concentrated on ICs using Al-GaAs/InGaAs PHEMTs. HEMT-based IC processes are generally simpler than HBT-based processes, and hence are easy to develop. Also,  $0.1 \mu m$ AlGaAs/InGaAs HEMTs have sufficient bandwidth and breakdown voltage for 40 Gbit/s applications. A HEMT IC process was developed at UCSB, and devices with 1  $\mu$ m gate lengths were successfully fabricated. However, HEMTs with sufficient  $f_{\tau}$  for 40 Gbit/s require gate lengths with < 0.25  $\mu$ m dimensions, necessitating the use of advanced lithographic tools like e-beam lithography or projection lithography systems. Unavailability of these tools

5

at the time, at UCSB, prevented fabrication of circuits designed in this process. Some designs were successfully fabricated in advanced HEMT processes in collaboration with industrial research laboratories.

An on-going demonstration HBT device technology [8] was then adapted and developed (jointly with R. Pullela and Q. Lee) into an IC process. The existent device technology was capable of yielding only discrete devices and the device performance was not adequate for the target integrated circuits. Several changes were made in the material layer structure and the physical device layout and structure. Key IC elements like resistors, capacitors and transmission lines were added. Multiple wiring levels, thermal vias and a low  $\epsilon$  BCB substrate were incorporated, bringing the technology to a level where complex high-performance ICs could be fabricated. A variety of ICs were then fabricated in this technology. This is the primary focus of this thesis.

While some integrated circuits for 40 Gbit/s fiber-optic links have been demonstrated with both HEMTs and HBTs, the performance is limited by several factors including intrinsic device bandwidth, wiring capacitance for dense circuits and efficient heat-sinking for HBTs operating at high current densities. For very similar reasons, circuits for 160 Gbit/s systems will be more difficult to develop. This thesis concentrates on HBTs and addresses the aforementioned problems at once. A scalable HBT is developed which can be scaled to achieve high bandwidths for high-speed systems. Typically, HBTs are not scalable devices. A fundamental change is made in the device structure which renders these devices scalable and achieves record bandwidths. The problem of wiring parasities is addressed by the use of BCB. Thermal vias provide heat-sinking. The transferred-substrate HBT IC process is developed and high-performance devices and the first integrated circuits in this technology with record performance are demonstrated. IC demonstration in this thesis paves the way for future very high-speed, very high-performance integrated circuits.

## Chapter 2

# Transferred-Substrate HBTs: Theory

Heterojunction bipolar transistors (HBTs) [9] have applications in mediumscale integrated circuits operating at GHz frequencies. HBTs have several advantages over Si-based devices and HEMTs including high bandwidth, high transconductance, high power density, low output conductance, low 1/f noise and very reproducible dc parameters. Target applications include digital phase-locked loops for microwave frequency synthesis, chip-sets for gigabit fiber-optic transmission, and wideband analog-digital converters. High circuit bandwidths are desirable; in  $\Delta$ - $\Sigma$  analog-digital converters, increased clock frequencies provide increased signal-noise ratios, while future optical transmission systems will require multiplexers, PLLs, and decision circuits with  $\sim 100$  GHz clock rates. In these applications, both the transistor current gain cut-off frequency  $f_{\tau}$ , and the power gain cut-off frequency  $f_{max}$  must be considerably higher than the signal frequencies involved. 100 Gbps optical-fiber transmission ICs will require HBTs having  $f_{\tau}$  and  $f_{max}$ greater than 200-250 GHz. A second-order  $\Sigma$ - $\Delta$  analog-digital converter having a 50 GHz sample rate would require HBTs with  $f_{\tau}$  and  $f_{max} \sim 200$ -300 GHz, but might provide 12 bits resolution at 1 GHz bandwidth. Broadband amplifiers for 40 & 100 Gbps communication would require HBTs with similar performance. HBTs with bandwidths of several hundred GHz will benefit many similar applications.

Progressive improvements in device bandwidths are needed to keep pace with the demand for integrated circuits operating at higher frequencies.

Device bandwidths are generally increased by scaling the device. Reducing the lithographic dimensions (lateral) and/or the semiconductor layer thicknesses (vertical) of a device is termed device scaling. With several important semiconductor devices, the device bandwidth increases as critical lithographic dimensions and layer thicknesses are reduced. Examples of highly scaled devices with large bandwidths are 0.1  $\mu$ m gate length HEMTs, 0.25  $\mu$ m gate length complementary metal-oxide-semiconductor (CMOS) transistors, 0.1  $\mu$ m Schottky-collector resonant tunnel diodes (SRTDs)[10] and submicron Schottky diodes used as sub-millimeter wave mixers. HEMTs with short gate lengths ( $\sim 0.1~\mu$ m) are presently the largest bandwidth three terminal devices. HEMTs with a power gain cutoff frequency ( $f_{max}$ ) of 450 GHz have been reported [11]. The superior bandwidths of HEMTs is a result of the rapid improvement in HEMT bandwidth with deep submicron scaling. HBTs are usually fabricated with  $\simeq 1~\mu$ m lithography and do not lend themselves to scaling as easily as other devices.

Figure 2.1: Comparison of  $f_{max}$  and emitter width for some HBTs in the literature.

Figure 2.1 shows  $f_{max}$  vs. emitter width for some HBTs reported in the literature. It can be seen that there is no strong correlation between  $f_{max}$

and emitter width, at least for narrow emitters. Consequently, HBTs are not fabricated with deep submicron dimensions except where bias currents have to be limited for low power operation.

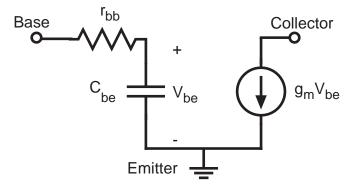

$\begin{array}{lll} r_{bb} & \text{base resistance} & & C_{je} & \text{emitter-base junction capacitance} \\ r_{c} & \text{collector contact resistance} & & C_{diff} & \text{emitter-base diffusion capacitance} & g_{m}\tau_{f} \\ r_{ex} & \text{emitter contact resistance} & & \tau_{f} & \text{forward transit time} & \tau_{b} + \tau_{c} \\ r_{be} & = \beta/g_{m} & & C_{cbi} & \text{intrinsic collector-base capacitance} \\ g_{m} & = qI_{c}/kT & & C_{cbx} & \text{extrinsic collector-base capacitance} \\ \end{array}$

Figure 2.2: Hybrid- $\pi$  model of a HBT for calculation of the short-circuit current gain.

The relationship between  $f_{max}$  and emitter and collector widths will now be explored. Parts of this theoretical discussion were presented in [31], and are repeated here for the sake of completeness. A simple hybrid- $\pi$  model of a HBT is shown in figure 2.2 with the model components related to the device parameters and biasing conditions. The expression for short circuit current gain corresponding to this device model is

$$A_{I} = \frac{-\beta}{1 + j\omega\beta \left[ (1/g_{m}) \left( C_{be} + C_{cb} \right) + (r_{ex} + r_{c})C_{cb} \right]}$$

(2.1)

under the following conditions: DC short circuit current gain  $\beta \gg 1$ ,  $\omega C_{cb} \ll g_m/(1+g_m r_{ex})$ , only first order terms in angular frequency  $\omega$  considered and the extrinsic  $C_{cb}$  charging time is small.

The short circuit current gain cutoff frequency  $f_{\tau}$  corresponds to the frequency at which the magnitude of  $A_I$  is unity. Near this frequency, the imaginary part of the denominator in Eq. (2.1) is much larger than unity. The expression for  $f_{\tau}$  as a function of device parameters and biasing conditions is therefore approximately

$$\frac{1}{2\pi f_{\tau}} = \tau_b + \tau_c + \frac{kT}{qI_c}(C_{je} + C_{cb}) + (r_{ex} + r_c)C_{cb}.$$

(2.2)

Here  $\tau_b$  is the base transit time,  $\tau_c$  the collector transit time, kT/q the thermal voltage,  $I_c$  the collector current,  $C_{je}$  the emitter-base junction capacitance,  $C_{cb}$  the collector-base capacitance,  $r_{ex}$  the emitter contact resistance, and  $r_c$  the collector contact resistance. At a given current density, all terms except  $r_cC_{cb}$  in the above equation are independent of lateral scaling. The base and collector transit times can be reduced by reducing the appropriate semiconductor layer thicknesses. Hence,  $f_{\tau}$  can be improved by vertical scaling of the device, but is independent of lateral scaling.

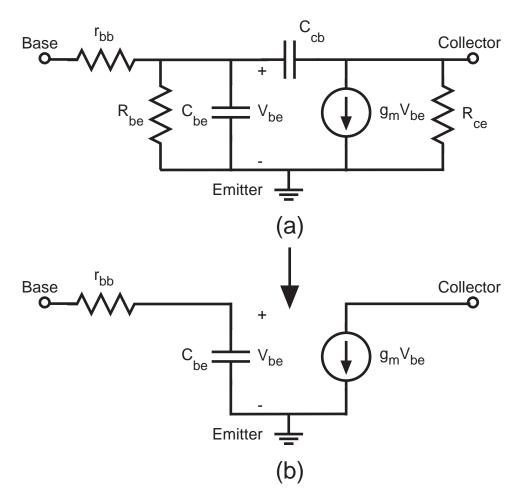

The power gain cutoff frequency  $f_{max}$  is another important figure-of-merit of high-frequency HBT performance.  $F_{max}$  defines the maximum frequency at which a device can provide power gain.  $F_{max}$  not only depends on  $f_{\tau}$ , but also on the base-resistance-collector-base-capacitance time constant as we shall now derive.  $F_{max}$  is the frequency at which the maximum available power gain  $G_{max}$  or Mason's unilateral power gain U [32] is unity. If the small signal equivalent circuit that was used for the derivation of  $f_{\tau}$  is used, the derivation is extremely complicated and a simple usable expression does not result. A simplified model will be used which will yield a result that estimates  $f_{max}$  quite accurately. This has been verified in the literature [33].

Figure 2.3 shows a simplified small-signal hybrid- $\pi$  model of a HBT. The input base-emitter resistance  $R_{be}$ , the output resistance  $r_{ce}$  and the collector resistance  $r_c$  are neglected. The extrinsic emitter resistance  $r_{ex}$  is assumed to be absorbed into the element values by applying emitter degeneration

$\rm r_{bb}\,$  base resistance  $\rm ~C_{be}\,$  total emitter-base capacitance

$\mathbf{g_{m}} = \mathbf{qI_{c}} \, / \, \mathbf{kT} \hspace{1cm} \mathbf{C_{cbi}} \hspace{0.3cm} \text{intrinsic collector-base capacitance}$

$C_{cbx}$  extrinsic collector-base capacitance

Figure 2.3: Simplified hybrid- $\pi$  model of a HBT for calculation of power gain.

to the model elements. The base-emitter capacitance  $C_{be}$  is the sum of the junction and diffusion capacitances. Mason's unilateral power gain U is given in terms of two-port y-parameters as

$$U = |y_{21} - y_{12}|^2 / 4(Re(y_{11})Re(y_{22}) - Re(y_{12})Re(y_{21})).$$

(2.3)

For the HBT model shown above, the four y-parameters can be derived from simple network theory and are given below in terms of the element model values.

$$y_{11} = 1/r_{bb} + j\omega C_{cbx} + j\omega C_{cbi}/\omega^{2} C_{be}^{2} r_{bb}^{2}$$

$$y_{12} = -C_{cbi}/C_{be} r_{bb} - j\omega C_{cbx} - j\omega C_{cbi}/\omega^{2} C_{be}^{2} r_{bb}^{2}$$

$$y_{21} = g_{m}/j\omega C_{be} r_{bb} - j\omega C_{cbx} - j\omega C_{cbi}/\omega^{2} C_{be}^{2} r_{bb}^{2}$$

$$y_{22} = g_{m} C_{cbi}/C_{be} + j\omega C_{cbx} + j\omega C_{cbi}/\omega^{2} C_{be}^{2} r_{bb}^{2}$$

(2.4)

Using Eq. 2.4 in Eq. 2.3, U can be derived as a function of frequency and is given below.

$$U = (g_m^2 + \omega^2 C_{cbi}^2)/4\omega^2 C_{be} C_{cbi} r_{bb} g_m$$

(2.5)

By setting the unilateral gain equal to unity, the expression for  $f_{max}$  is derived and is given below.

$$f_{max} = \sqrt{f_{\tau}/8\pi r_{bb}C_{cbi}} \tag{2.6}$$

with the assumption that  $\omega C_{be}r_{bb}\gg 1$ ,  $C_{cbi}< C_{be}$  and  $f_{\tau}=g_m/2\pi C_{be}$ . As we can see from Eq. 2.6, no matter how large the value of  $f_{\tau}$  is, power gain is available only at frequencies below  $f_{max}$ . Hence, to improve device bandwidth, is it important to improve  $f_{\tau}$  as well as the  $r_{bb}C_{cbi}$  time constant. Note that while the extrinsic collector-base capacitance has no impact on  $f_{max}$ , it does impact the performance of many circuits, and should be minimized.

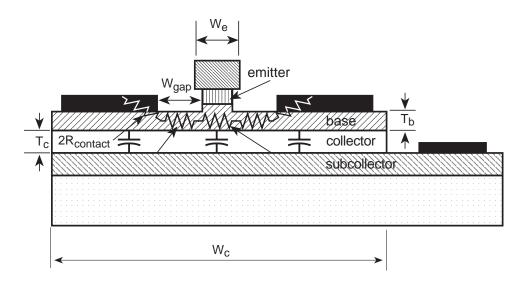

We will now see what determines the  $r_{bb}C_{cbi}$  charging time constant for HBTs. The cross section of a double-mesa HBT is shown in figure 2.4. The base resistance  $r_{bb}$  has three components. These are: the contact resistance from the base Ohmic contact, the sheet resistance from the gap between the emitter mesa and the base Ohmic contact, and the spreading resistance

Figure 2.4: Schematic cross-section of a double-mesa HBT.

of the base layer underneath the emitter mesa. The contact resistance is given by

$$R_{contact} = \sqrt{\rho_{bc}\rho_{bs}}/2l \tag{2.7}$$

where  $\rho_{bc}$  is the specific contact resistance per unit area of the metalsemiconductor interface (units of  $\Omega$ -cm<sup>2</sup>),  $\rho_{bs}$  is the base sheet resistivity (units of  $\Omega/\square$ ) and l is the transverse length of the emitter stripe (units of  $\mu$ m). The gap resistance is given by

$$R_{gap} = \rho_{bs} W_{gap} / 2l \tag{2.8}$$

where  $W_{\text{gap}}$  is the separation between the emitter mesa and the base Ohmic contact. The spreading resistance is given by

$$R_{spread} = \rho_{bs} W_e / 12l \tag{2.9}$$

where  $W_e$  is the emitter width. For HBTs fabricated with a self-aligned base-emitter process,  $W_{\rm gap} \simeq 0.1~\mu{\rm m}$  and  $R_{\rm gap}$  is negligible. We note also that  $R_{\rm spread}$  is proportional to the emitter width  $W_e$ , but that  $R_{\rm contact}$  is independent of  $W_e$ . Hence, for narrow-emitter devices, the base resistance tends to be dominated by  $R_{\rm contact}$  and is only weakly dependent upon  $W_e$ . The total collector-base capacitance is given by

$$C_{cb} = \epsilon l W_c / T_c \tag{2.10}$$

where,  $W_c$  is the width of the collector (= width of the base mesa), l is the length of the emitter stripe and  $T_c$  is the thickness of the collector depletion region. Hence,  $C_{cb}$  is proportional to the width of the base mesa which in turn is much wider than, and, independent of  $W_c$ . Note that only a fraction  $C_{cbi}$  of  $C_{cb}$  is charged through the base resistance  $r_{bb}$ . Determination of the  $C_{cbi}/C_{cb}$  ratio from the HBT physical dimensions has been mentioned [33] but has not been fully explored in the literature. We estimate that

$$C_{cbi} \simeq \epsilon l(W_e + 2W_{gap} + 2l_{contact})/T_c$$

(2.11)

where

$$l_{contact} = \sqrt{\rho_{bc}/\rho_{bs}} \tag{2.12}$$

is the transfer length of the base Ohmic contact. This approximation is based upon taking the fraction of  $C_{cb}$  whose charging current shares a common path through the base with the currents associated with charging  $C_{be}$ . We note that the collector-base junction area of double-mesa HBTs is further increased by the presence of a base contact pad area necessary to bring interconnect metallization onto the base Ohmic metal. Lateral scaling below  $\sim 1~\mu m$  does not substantially improve the bandwidth of double-mesa HBTs.

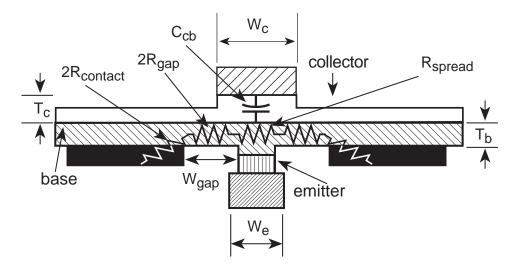

A transferred-substrate HBT can be scaled laterally to improve bandwidth. The cross-section of a transferred-substrate HBT is shown in figure 2.5. Transferred-substrate HBTs have lithographically defined narrow emitter and collector stripes aligned to each other on opposite sides of the base epitaxial layer [34]. This is the special feature of the transferred-substrate HBT in contrast to the double-mesa HBT. The fabrication of transferred-substrate HBTs requires access to the emitter and the collector sides of the epitaxial film. The process of substrate transfer allows this access and is an essential step in the fabrication process. The base resistance is dominated by  $R_{\rm contact}$  and is independent of  $W_e$ , as for the double-mesa HBTs. The collector-base capacitance  $C_{cb}$  is proportional to the width of the collector stripe  $W_c$ , if fringing capacitance is negligible (figure 2.5);  $C_{cb} = \epsilon l W_c/T_c$ , where l is the length of the collector or the emitter stripe and  $T_c$  is the thickness of the collector depletion region. If a constant ratio

Figure 2.5: Schematic cross-section of a transferred-substrate HBT.

is maintained between the emitter and the collector widths,  $C_{cb}$  is proportional to the emitter width  $W_e$ . Noting that  $r_{bb} \simeq R_{\rm contact} = \sqrt{\rho_{bc}\rho_{bs}}/2l$ , and  $C_{cb} = \epsilon lW_c/T_c$  (where  $W_c \propto W_e$ ), the  $r_{bb}C_{cb}$  time constant is proportional to  $W_e$ . This, when used in Eq. (2.6) shows that the maximum frequency of oscillation  $f_{max}$  depends on  $W_e$  as

$$f_{max} \propto \frac{1}{\sqrt{W_e}}. (2.13)$$

Hence,  $f_{max}$  rapidly improves with submicron lateral scaling of the device. The cross-section of the transferred-substrate HBT in figure 2.5 shows a direct Schottky contact to the collector depletion layer. An Ohmic collector with a heavily doped subcollector, with the subcollector semiconductor material etched away outside the Ohmic metal contact, could also be used. An Ohmic collector contact having the same width as the Schottky contact will also show the same variation of  $f_{max}$  with scaling. The two devices are almost identical except for an extra potential drop across the collector-base junction of the Schottky-collector device. This potential drop, due to the Schottky contact, is the difference between the work function of the metal Schottky contact and the electron affinity of the collector semiconductor. A Schottky collector contact provides a slight improvement in  $f_{\tau}$  because of the absence of a collector contact resistance (Eq. (2.2)). It is also easier to

fabricate deep submicron Schottky collector contacts (e.g.  $0.1~\mu\mathrm{m}$  T-gate) than deep submicron Ohmic contacts. On the other hand, a Ohmic collector might improve transistor performance at low collector-emitter biases  $V_{CE}$ , as we will see later. This is due to the extra potential drop at the Schottky contact as compared to the Ohmic contact.

The scaling law of Eq. (2.13) suggests that the operating bandwidth of HBTs can be increased without bounds by lithographic scaling alone. In fact, to obtain usable devices, vertical scaling of the epitaxial layer thicknesses must accompany the lithographic scaling. Except in the case of reactively- matched amplifiers and distributed circuits where  $f_{max}$  is the sole determinant of circuit bandwidth, both  $f_{\tau}$  and  $f_{max}$  are generally important for optimum circuit performance in a given technology. Devices with  $f_{max} \ll f_{\tau}$ , obtained by thinning the epitaxial layers without lateral lithographic scaling will show circuit bandwidth determined by  $r_{bb}$  and  $C_{cb}$ . Devices with  $f_{max} \gg f_{\tau}$  (e.g. devices with relatively thick epitaxial layers and significant lateral lithographic scaling) will show circuit bandwidth dominated by  $(\tau_b + \tau_c)$ . Reduction of  $(\tau_b + \tau_c)$  is obtained by thinning the epitaxial layers, which unfortunately increases  $r_{bb}C_{cb}$ . The transferred-substrate HBT allows for the subsequent reduction of  $r_{bb}C_{cb}$ . A device having high values for both  $f_{\tau}$  and  $f_{max}$  is thus possible.

Several approaches have been reported for reducing the collector-base capacitance of HBTs, and thereby improving  $f_{max}$ . One approach is the reduction of the width of the base mesa [20]. This relies on improvements in base contact technology because a narrow base mesa results in a smaller base Ohmic contact area. The base contact width must be at least one transfer length if the contact resistance is to be kept small. In contrast, the transferred-substrate technique provides independent control of the base and collector contact widths. There have been other approaches to make the collector contact width independent of the size of the base mesa, such as selective etching to undercut the collector [35], collector isolation implant [36], contacting the base with a very narrow L-shaped contact [37], selective lateral oxidation of the emitter [38] for a collector-up growth, burying SiO<sub>2</sub> in the extrinsic collector [39], selectively regrowing the extrinsic collector [40], and, patterning and regrowing a narrow subcollector followed by regrowth of the other layers [41]. However, in almost all cases, minimal improvement in device  $f_{max}$  was obtained. Moreover, the scalability of these approaches has not been demonstrated. Transferred-substrate HBTs can

be scaled to deep submicron dimensions with the use of powerful fine-line lithography for fabricating narrow emitter and collector stripes leading to dramatic improvement in device  $f_{max}$ .

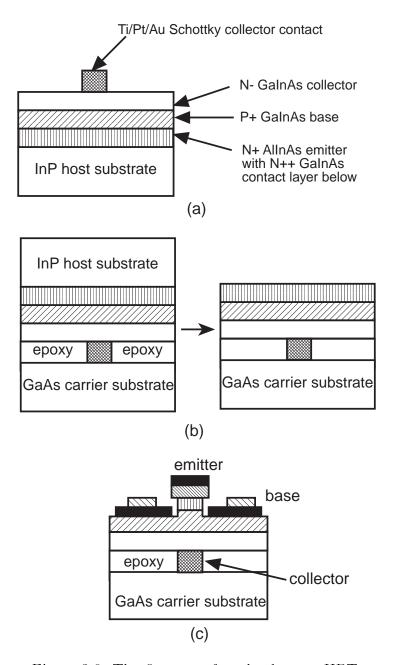

The first transferred-substrate HBT was demonstrated by U. Bhattacharya [31]. The device structure used there is shown in figure 2.6.

In this early work, a collector-up growth was used. The first step was formation of Ti/Pt/Au Schottky collector contacts. Epoxy was then used to bond the wafer to a carrier substrate using an in-house mechanical bonding fixture. After removal of the InP substrate, a infra-red based backside aligner was used to align to the collector alignment marks which were buried under the epitaxial layers. Emitter-base fabrication was then done. The process was completed with the formation of electroplated airbridge contacts to the base and emitter. This process required considerable development, especially in base-emitter processing and substrate transfer. The epitaxial material growth also evolved significantly as experiments were done to study every aspect of the layer structure. The concept of transferred-substrate HBTs was demonstrated. Peak  $f_{\tau}$  and  $f_{max}$  obtained were 140 GHz and 170 GHz respectively.

The aim of the epoxy-bonded HBT reported above was to demonstrate transferred-substrate HBTs. In this, it was successful. Discrete devices with moderate yield were fabricated. Furthermore, these efforts built UCSB's general expertise in HBT technology. However, the ultimate goal of HBT development is to build integrated circuits. To this end, the epoxy-bonding technology is far from being suitable or adequate. First, the device performance was much poorer than is needed for high-performance integrated circuits. Device bandwidth in the range of 200-300 GHz or above is essential for circuit bandwidths in the range of 100 GHz. Improvements in the epitaxial layer structure and the physical device structure and transistor scaling are required to increase bandwidth. Second, essential elements of integrated circuits like resistors and capacitors need to be incorporated.

Third, transmission lines and interconnect wiring would be on a epoxy substrate. Epoxy is not known to be a good microwave substrate and hence would produce lossy transmission lines. Also, the high dielectric constant of epoxy would lead to significant interconnect capacitance. Microstrip transmission lines are not possible because of the absence of a ground plane and ground vias. Coplanar waveguide lines have to be used, which can be problematic with packaging. Fourth, HBTs operate at high current

Figure 2.6: The first transferred-substrate HBT.

densities for high-speed operation. Effective heat-sinking is then vital. Heat dissipation in the epoxy process is through the epoxy substrate which has poor thermal conductivity. This prevents IC fabrication. Fifth, integrated circuits require high yield over large areas with good uniformity. The use of epoxy and the in-house bonding fixture is unsuitable for this purpose. The epoxy thickness was quite non-uniform, which led to poor device uniformity and less than adequate yield. The uncalibrated bonding pressure was also a problem, leading to wafer cracking. Sixth, only small substrates (about 1 cm  $\times$  1 cm) were used. While this was acceptable for discrete devices, ICs occupy larger areas, and larger substrates are needed. The epoxy process had not been demonstrated for large substrates. The bonding procedure would be a problem.

Seventh, the collector was buried in epoxy and this had two disadvantages. The collector recess etch, which is very important for reducing the fringing capacitance, had to be done before the process of substrate transfer. Hence the effect of recess etch could only be studied by processing two identical growth in the exact same way. Second, the effect of successive etches on a particular wafer could not be determined. There is strong evidence that the epoxy-bonded devices had excess parasitic collector-base capacitance, this because the collector-base junction is buried in epoxy.

These limitations of the epoxy-bonded transferred-substrate HBTs are removed by (first) eliminating the epoxy bonding step and (second) developing a collector-up structure fabricated from a emitter-up MBE growth. If a emitter-up growth is used, the collector contact is the last fabrication step and successive recess etches can be done to determine the best etch parameters with respect to device performance. The parasitic capacitance would be through air dielectric which has a lower dielectric constant compared to epoxy. In summary, the process is unsuitable for fabricating integrated circuits.

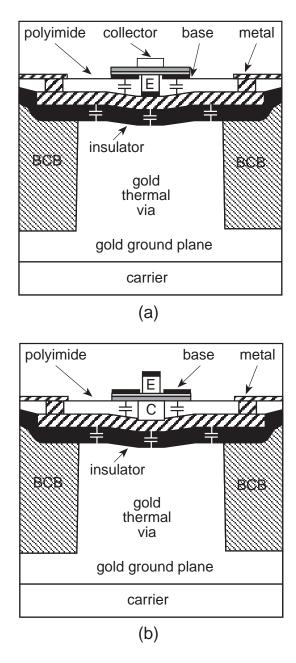

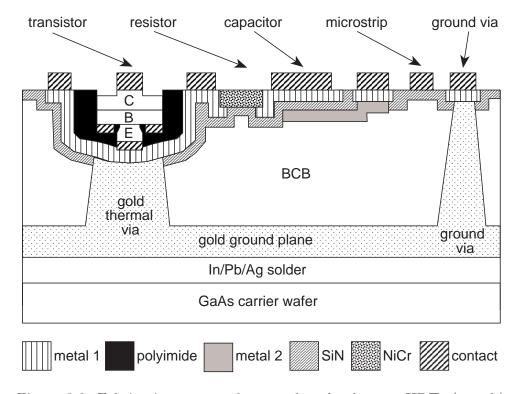

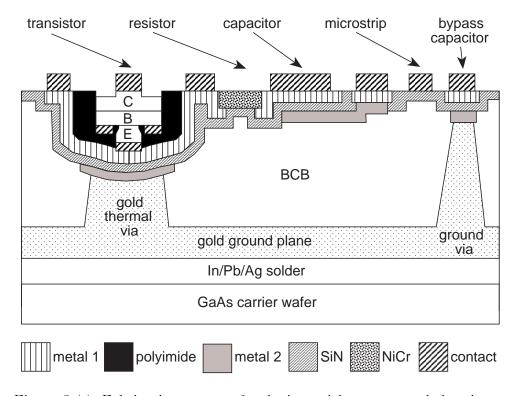

The proposed device structure and process addresses the problems discussed above. In addition to high device bandwidths, high frequency integrated circuit processes must incorporate a low capacitance wiring environment and low ground return inductance. For dense ICs, wire lengths, and hence transistor spacings must be small. Given that fast HBTs operate at  $\sim 10^5$  A/cm<sup>2</sup> current density, efficient heat sinking is then vital. The transferred-substrate HBT IC process uses Benzocyclobutene (BCB), a low-loss, low dielectric-constant ( $\epsilon_r = 2.7$ ), spin-on dielectric as the sub-

strate for microstrip interconnects, thus providing low capacitance. The thin ( $\simeq 10 \ \mu m$ ) BCB substrate with a gold ground plane underneath the entire IC also provides low inductance ground vias. Transistor heat-sinking is through electroplated gold thermal vias. Transmission lines for microwave circuits are microstrip lines on a BCB substrate. These lines have very low loss even at several tens of GHz and do not have the multimode propagation problems associated with coplanar waveguide lines (modes propagating between the frontside and backside ground planes). Three independent levels of wiring facilitate easy interconnection for dense circuits. Resistors are formed with thin-film nichrome (NiCr) and capacitors are metal-insulatormetal with PECVD SiN as the dielectric. The process of substrate-transfer is done using a automated flip-chip bonding machine with controlled temperature and pressure cycles. Epoxy is replaced with a In/Pb/Ag solder, with much better thermal performance and thickness uniformity. The use of standard IC materials like BCB and solder and a sophisticated bonding tool lead to high device uniformity and high yield. Larger substrates can be used facilitating the fabrication or large-area integrated circuits. Improvements in the epitaxial layer structure were made in the base and collector. The base layer was graded in bandgap and in doping to improve the base transit time. A pulse-doped layer was added to the collector to delay the onset of Kirk effect. All these improvements have transformed a demonstration device technology into a advanced IC process and made possible high-performance integrated circuits. The choice of emitter-up or collectorup is still open. A emitter-up growth was used and the rationality of this choice is explained below.

A schematic cross-section of the transferred-substrate device, with the emitter or the collector as the upper electrode is shown in figure 2.7. We now explain the motivation for designing such a structure and for choosing structure (a) instead of structure (b). Polymer layers conduct heat poorly and the thermal via is essential. As seen in the figure, there is a parasitic capacitance through the insulator between the contact metal and the grounded thermal via. This capacitance is between emitter and ground (figure 2.7(a)) or between collector and ground (figure 2.7(b)) depending on whether the collector or the emitter is the top electrode. From a circuit viewpoint, the emitter is a low-impedance node and the collector is a high-impedance node. The parasitic capacitance will affect circuit performance more strongly if it is at a high-impedance node. Hence using the collector

Figure 2.7: Schematic cross-section of device structure reported in this thesis. While (a) the emitter or (b) the collector could be the top electrode in this figure, the text explains the motivation for using the collector as the upper electrode.

as the top electrode is beneficial.

One of the main features of the transferred-substrate HBT is the reduction in collector-base capacitance  $C_{cb}$  obtained by using narrow collector stripes. If the collector is the lower electrode, a parasitic collector-base capacitance in series with a base resistance would exist as shown in the figure. The parasitic capacitance would be significant compared to the intrinsic device capacitance and would therefore degrade  $f_{max}$  significantly. On the other hand, if the emitter is the lower electrode, parasitic emitter-base capacitance resulting from the device structure is present. The emitter-base capacitance of the HBT itself is  $\sim 100$ : 1 larger than the collector-base capacitance. Hence a small additional parasitic emitter-base capacitance introduced from the substrate-transfer process is only of minor concern. Again, using the collector as the top electrode is beneficial.

As an added advantage, a emitter-up growth also finally allows access to the extrinsic collector region, which can be recess etched to reduce the fringing collector-base capacitance. This is shown in figure 2.8. In figure 2.8(a), there is no recess etch, thus resulting in substantial fringing capacitance. In figure 2.8(b) only the collector sidewalls are removed leading to a  $\sim 30$  % reduction in  $C_{cb}$ . This etch profile results if a dry etch is used or if a anisotropic wet etch is used. If a isotropic wet etch is used, lateral undercutting during the etch results in the profile of figure 2.8(c), which leads to a significant further reduction in  $C_{cb}$ . This has been verified experimentally. Hence the collector is designed to be the upper electrode.

There is one significant disadvantage to the collector being the top electrode. The thermal via should preferably be closest to the region where most heat is generated in the device. For a HBT, this happens to be the base-collector junction area as the electrons are swept towards the collector contact under high field. Given that the collector is on top to avoid excess  $C_{cb}$ , the thermal via has to be on the emitter side even though the heat generation is primarily in the collector. Hence, there is a trade-off between microwave and thermal design of the transistor.

It is expected that with submicron scaling of transferred-substrate HBTs,  $f_{max}$  in excess of 700 GHz should be possible. With this high bandwidth, integrated circuits operating at very high speeds should be feasible. Circuit speed depends on device bandwidth as well as on other key factors outlined above. The transferred-substrate HBT IC process has been designed to incorporate the key IC requirements. To realize high-speed circuits and

Figure 2.8: Recess etching the collector to reduce fringing collector-base capacitance.

#### 24 CHAPTER 2. TRANSFERRED-SUBSTRATE HBTS: THEORY

devices, extensive process development was done. The fabrication process is presented in the next chapter.

# Chapter 3

## **Fabrication**

This chapter details the IC fabrication procedure. The process is complex with ten mask layers and tens of process steps. Starting with the work of Bhattacharya [31], process development involved extensive experimentation and multiple wafer runs, an effort which took two years of intense effort. The results from every process development experiment are not presented here in detail; only the final process is presented. The process is described in detail in the Appendix.

### 3.1 MBE layer structure

The AlInAs/GaInAs material system was chosen for the fabrication of transferred-substrate HBTs. This material system has several advantages over the AlGaAs/GaAs system including higher electron mobility, higher saturated electron velocity and lower surface recombination. Combined with the scalability of transferred-substrate HBT, the AlInAs/GaInAs system should yield very high-performance devices. The HBT epitaxial layer structure (figure 3.1(a)) is grown by molecular beam epitaxy (by D. Mensa) on a Fe-doped semi-insulating (100) InP substrate, starting with a 2500 Å AlInAs buffer layer. The GaInAs collector is 2700 Å thick, is Si-doped at  $1 \times 10^{16}/\text{cm}^3$  and contains a  $5 \times 10^{11}/\text{cm}^2$  Si pulse-doped layer 400 Å from the base. This pulse-doped layer delays the onset of base push-out [42] and depletes out-diffused Be in the collector. A thinner (2500 Å) collector was also used in some growths. Thin collectors increase the collector-base capacitance degrading  $f_{max}$ , but improve the collector transit time increasing

Figure 3.1: (a) MBE layer structure and (b) Band diagram under forward bias.

$f_{\tau}$ . Thinner collectors also improve the Kirk effect threshold thus enabling higher current density operation. Of course breakdown is worse in thin collectors because of the increased electric fields.

To reduce the base transit time, the 500 Å GaInAs base is graded in both doping and bandgap. The 100 Å of the Ga<sub>0.47</sub>In<sub>0.53</sub>As base immediately adjacent to the collector is Be-doped at  $3 \times 10^{19}/\text{cm}^3$ . The remaining 400 Å of the base is Be-doped at  $5 \times 10^{19}/\text{cm}^3$ . By increasing the Ga cell temperature progressively during growth of the 400 Å layer, the Ga:In ratio is gradually increased, introducing a  $\sim 0.03$  eV bandgap gradient across the 400 Å layer. In some of the results presented later, a thinner (400 Å) base was used. Thin bases improve the base transit time at the cost of increased base sheet resistance. Also, thin bases are difficult to grow in a controlled manner due to problems associated with outdiffusion of the Be dopant from the heavily doped base layer. The emitter-base etch involves a self-aligned etch down to the base epitaxial layer. Precise and uniform etching is desired to achieve low and uniform base resistance. With thin layers, more nonuniformity might result during this etch. An alternative to reducing the base thickness to improve transit time would be to increase the bandgap grading in the base. But, too much grading can cause excessive strain and growth defects in the semiconductor layers due to lattice mismatch. Also, GaInAs epitaxial layers with too much Ga behave more like GaAs which

27

has a higher surface recombination velocity and might degrade the current gain of the device.

The base is then graded in 300 Å to the AlInAs emitter. The first 66 Å of the grade is Be-doped at  $2 \times 10^{18}/\text{cm}^3$  and the remainder is Si-doped at  $8 \times 10^{17}/\text{cm}^3$ . The AlInAs emitter is about 1350 Å thick. The first 500 Å are Si-doped at  $8 \times 10^{17}/\text{cm}^3$  and the remainder is Si-doped at  $1 \times 10^{19}/\text{cm}^3$ . This is graded in 66 Å to the InGaAs emitter cap. The emitter cap is  $n^+$  doped with Si at  $1 \times 10^{19}/\text{cm}^3$ . The emitter layer design is similar to [43]. A InAs emitter cap was used in some growths to reduce the emitter resistance.

The band diagram corresponding to the layer structure of figure 3.1(a) under forward bias is shown in figure 3.1(b). The biasing conditions are as follows: base-emitter voltage  $V_{BE} = 0.7$  V, collector-emitter voltage  $V_{CE} = 1.0$  V, and a emitter current density of  $1 \times 10^5$  A/cm<sup>2</sup>. The collector current density is assumed to be the same as the emitter current density, as is the case of a narrow-collector HBT. The effect of the electrons in the collector space charge layer due to the collector current is included while calculating the electric field and the electrostatic potential in the collector space charge layer. An electron velocity of  $3 \times 10^5$  m/s is assumed in these calculations. The pulse-doped layer causes significantly band-bending in the collector, close to the base as shown in the band diagram. As a result of this, the current density corresponding to Kirk effect threshold in increased as a higher electron charge is now needed to flatten the conduction band in the collector at the base edge.

### 3.2 Fabrication

Figures 3.2 and 3.3 show sequentially, the steps involved in fabrication of transferred- substrate HBTs. The fabrication process starts with the evaporation of Ti/Pt/Au/Si ( $\sim 1~\mu m$  thick) emitter contacts. The Si layer is used as a mask for the following etches and is subsequently removed. A combination of a dry etch, a selective wet etch, and a non-selective wet etch is then used to etch down to the base epitaxial layer. The dry etch is done in a RIE system with CH<sub>4</sub>/H<sub>2</sub>/Ar and it removes most of the unmasked emitter epitaxial layers. A laser monitor is used to determine the etch stop point and the etch conditions are designed to give a anisotropic vertical sidewall etch. A selective wet etch (which etches AlInAs selectively over GaInAs) is used to remove the remainder of the AlInAs emitter layer and expose the

Figure 3.2: Fabrication process for transferred-substrate HBTs.

29

Figure 3.3: Fabrication process for transferred-substrate HBTs (contd.).

top GaInAs layer in the emitter-base grade. Lateral etching in this step reduces the emitter dimensions to below the lithographically defined area. The second wet etch is used to etch the 300 Å grade and expose the base GaInAs layer. This etch also reduces the lateral dimensions of the emitter. Figure 3.4 shows a SEM photomicrograph of the device cross-section after this step. The lateral undercuts can be seen in this cross-section.

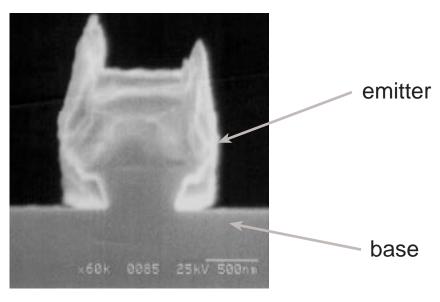

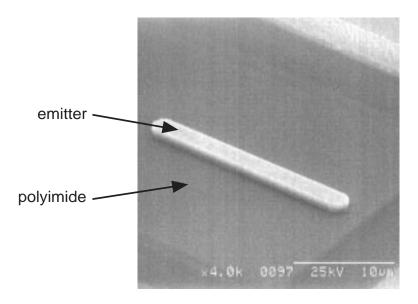

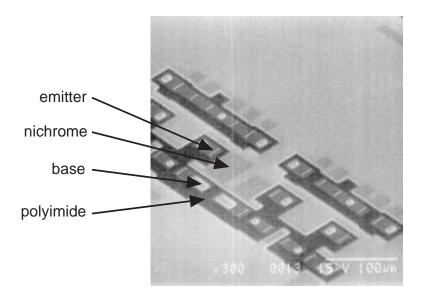

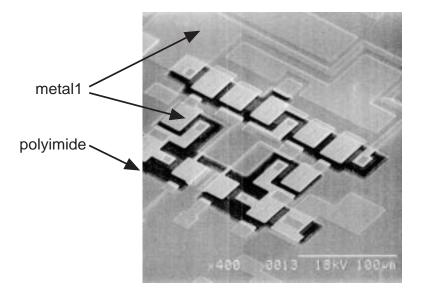

Figure 3.4: SEM cross-section of device after emitter-base etch.