#### UNIVERSITY OF CALIFORNIA

#### Santa Barbara

InP HBT Power Amplifier MMICs toward 0.4W at 220GHz

A Dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Thomas Benjamin Reed

Committee in charge:

Professor Mark Rodwell, Chair

Professor Emeritus Stephen Long

Professor Robert York

Doctor Zach Griffith

March 2013

The dissertation of Thomas Benjamin Reed is approved.

| Zach Griffith                 |  |

|-------------------------------|--|

|                               |  |

| Stephen Long                  |  |

|                               |  |

| Robert York                   |  |

|                               |  |

| Mark Rodwell, Committee Chair |  |

March 2013

In P HBT Power Amplifier MMICs toward 0.4W at 220GHz

Copyright © 2013

by

Thomas Benjamin Reed

#### **ACKNOWLEDGEMENTS**

This work relied on the countless contributions of those that came before.

Prof. Mark Rodwell is a driven visionary for the future of electronics. He has been a highly generous advisor.

Zach Griffith has a wealth of knowledge in high frequency device, circuit technology, and life. His advice has saved many headaches. Thank you for all your time and hard work to make this SSPA effort successful.

I acknowledge committee members Prof. Stephen Long and Prof. Robert York for their valuable experience and expertise.

UCSB Rodwell Group Members, including Vibhor Jain, Ashish Baraskar,

Evan Lobisser, Andy Carter, Saeid Daneshgar, Hyunchul Park, Johann Rode, Hanwei

Chiang, Prateek Choudhary are great colleagues.

Ken Ota, Serra Hoagland, and other non-engineers have helped me remain grounded. My family has been a source of strength throughout graduate school.

DARPA MTO has provided the funding resources through the HiFIVE program to pursue these power amplifier MMICs at 220GHz.

Finally, Sarah, my wife is a joy. She lightens the loads of life and has been there for me through the best and worst parts of this experience.

#### VITA OF THOMAS BENJAMIN REED

#### March 2013

| EDUCATION               |                                                                                           |                                         |

|-------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------|

| Dec. 2009 – Present     | University of California Santa Barbara<br>Ph.D. in Electrical Engineering (Estimated Marc | Santa Barbara, CA<br>h 2013 Graduation) |

| Sept. 2008 – Dec. 2009  | University of California Santa Barbara<br>M.S. in Electrical Engineering                  | Santa Barbara, CA                       |

| Sept. 2002 – April 2008 | Brigham Young University<br>BS in Electrical Engineering, Minor in Mathema                | Provo, UT                               |

| PROFESSIONAL EX         | PERIENCE                                                                                  |                                         |

| Aug. 2008 – Mar. 2013   | Graduate Student Researcher<br>Department of Electrical and Computer Engine               | Santa Barbara, CA ering, UCSB           |

| Jan. 2012 – Mar. 2012   | Laboratory Teaching Assistant Department of Electrical and Computer Engine                | Santa Barbara, CA ering, UCSB           |

| June 2011 – Aug. 2011   | Electrical Engineering Student Intern<br>Microsystems, Organization 1711, Sandia Nation   |                                         |

| Sept. 2007 – April 2008 | Teaching Assistant<br>Department of Electrical Engineering, Brigham                       | Provo, UT<br>Young University           |

| June 2007 – Aug. 2007   | Electrical Engineering Internship<br>ASIC Design Group, Cray, Inc.                        | Seattle, WA                             |

|                         |                                                                                           |                                         |

#### **PUBLICATIONS**

PRICATION

- Griffith, Z.; **Reed, T.**; Rodwell, M.; Field, M., "A 220GHz Solid-State Power Amplifier MMIC with 26.8dB S21 Gain, and 55.5mW P<sub>OUT</sub> at 17.0dB Compressed Gain," *Microwave Symposium Digest (MTT), 2013 IEEE MTT-S International*, pp. 1-4, 2-7 June 2013.

- Reed, T.B.; Rodwell, M.J.W.; Griffith, Z.; Rowell, P.; Urteaga, M.; Young, A.; Field, M., "A 220GHz InP HBT Solid-State Power Amplifier MMIC with 90mW P<sub>OUT</sub> at 8.2dB Compressed Gain," Compound Semiconductor Integrated Circuit Symposium (CSICS), 2012 IEEE, pp.1-4, 14-17 Oct. 2012

- H. Park, M. Lu, E. Bloch, T. Reed, Z. Griffith, L. Johansson, L. Coldren, and M. Rodwell, "40Gbit/s Coherent Optical Receiver Using a Costas Loop," European Conference and Exhibition on Optical Communication, OSA Technical Digest (Optical Society of America, 2012), paper Th.3.A.2.

- Reed, T.B.; Rodwell, M.J.W.; Griffith, Z.; Rowell, P.; Field, M.; Urteaga, M., "A 58.4 Solid-State Power Amplifier at 220 GHz using InP HBTs," *Microwave Symposium Digest (MTT), 2012 IEEE MTT-S International*, pp. 1444-1446, 17-22 June 2012.

Bloch, E.; Park, H.; Lu, M.; Reed, T.; Griffith, Z.; Johansson, L.; Coldren, L.; Ritter, D.; Rodwell, M. J., "A 1-20 GHz InP HBT Phase-Lock-Loop IC for Optical Wavelength Synthesis," Microwave Symposium Digest (MTT), 2012 IEEE MTT-S International, pp. 1492-1494, 17-22 June 2012.

Reed, T.B.; Rodwell, M.J.W.; Griffith, Z.; Rowell, P.; Urteaga, M.; Field, M.; Hacker, J., "48.8 mW Multi-Cell InP HBT Amplifier with On-Wafer Power Combining at 220 GHz," *Compound Semiconductor Integrated Circuit Symposium (CSICS)*, 2011 IEEE, pp. 196-199, 16-19 Oct. 2011.

Hacker, J.; Munkyo Seo; Young, A.; Griffith, Z.; Urteaga, M.; Reed, T.; Rodwell, M.; , "THz MMICs based on InP HBT Technology," *Microwave Symposium Digest (MTT), 2010 IEEE MTT-S International*, pp.1126-1129, 23-28 May 2010.

#### FIELD OF STUDY

Major Field: Studies in High Frequency Circuit Design with Professor Mark

Electronics/Photonics Rodwell and Zach Griffith, Ph.D.

#### ABSTRACT

InP HBT Power Amplifier MMICs toward 0.4W at 220GHz

by

#### Thomas Benjamin Reed

RF power amplification above 200GHz has become more critical as higher frequency bands are sought for radar and space applications. At 220GHz, a low-loss free-space propagation window is very alluring for potential systems, however, a single transistor cannot produce sufficient output power requisite for a wireless system. This work demonstrates solid-state power amplifier MMICs targeting up to 0.4W at 220GHz.

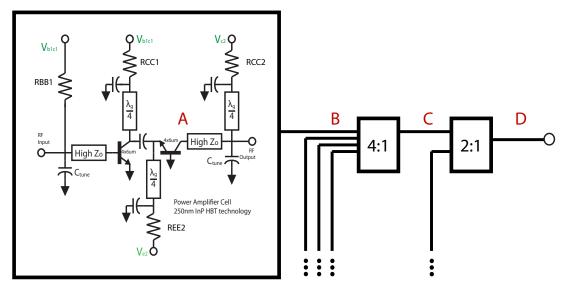

Power amplifier cells are designed using four  $6\mu m$ -long common emitter and common base InP HBTs to form a cascode. Single InP HBTs with 250nm-wide emitters and have shown a peak  $f_{MAX}$  of 700GHz and peak  $f_{T}$  of 400GHz. The cascode cell shows above 15dB of small signal available gain at 220GHz. Non-inverted microstrip IC interconnects shield the InP substrate and provide a low-loss environment for impedance tuning and power combining. Multiple levels of power combining are performed on wafer to reach a high overall saturated output power at 220GHz. Experiments were designed to find the limits of transistor density, the optimal Class A load line, the optimal number of power combining levels and gain stages, the maximum physical size, and the maximum possible DC power consumption at the IC level.

In the first attempt, a 4-Cell SSPA was reported to have 48.8mW of saturated output power at 220GHz with a compressed gain of 4.5dB. On a second maskset, a

2-stage, 8-Cell SSPA had 90mW of saturated 220GHz output power at 8.2dB of compressed gain. A third set of designs demonstrates a 4x increase in output HBT periphery over the 8-Cell SSPAs in Tapeouts 1 and 2. In full-thickness RF power measurements, 180mW of saturated power was observed at 214GHz when air cooled. When heat removal by wafer thinning and mounting is complete, power levels may be close to the 400mW shown in simulation.

### **Contents**

| ACKNOWLEDGEMENTS                                 | iv     |

|--------------------------------------------------|--------|

| VITA OF THOMAS BENJAMIN REED                     | V      |

| ABSTRACT                                         | vii    |

| LIST OF FIGURES                                  | xii    |

|                                                  |        |

|                                                  |        |

| 1                                                |        |

|                                                  |        |

| INTRODUCTION TO SSPA DESIGN                      |        |

| 1-A Introduction                                 | 1      |

| 1-B Design Challenges at 220 GHz                 | 2<br>5 |

| 1-C Noteworthy Results                           |        |

| 1-D Novel Methods In 220GHZ PA Design            | 6      |

| 1-E InP HBT Technology Description               | 8      |

|                                                  |        |

| <b>1</b>                                         |        |

| <b>2.1</b>                                       |        |

| <del></del>                                      |        |

| MICROWAVE POWER AMPLIFIER DESIGN                 |        |

| 2.1-A Linear Amplfiers                           | 15     |

| 2.1-B Transistor Amplifier Topologies            | 17     |

| 2.1-C Bandwidth Considerations and Parasitics    | 21     |

| 2.1-D RF Power Amplifiers                        | 22     |

| 2.1-E Class A Power Amplifiers                   | 25     |

| 2.1-F Other Power Amplifier Classes              | 26     |

| 2.1-G Power Amplifier Tuning                     | 28     |

| 2.1-H Transmission Lines                         | 30     |

| 2.1-I Impedance Matching                         | 34     |

| 2.1-J Impedance Transformation                   | 37     |

| 2.1-K Using Smith Charts                         | 37     |

| 2.1-L Smith Chart Impedance Matching Networks    | 41     |

| 2.1-M Transistor Impedance Matching              | 42     |

| 2.1-N Stability Factor and Stability Measure     | 44     |

|                                                  |        |

| 7 7                                              |        |

|                                                  |        |

| 220CHZ CCDA DECICN                               |        |

| 220GHZ SSPA DESIGN                               | 40     |

| 2.2-A Adjusting Microwave Methods for 220GHz     | 49     |

| 2.2-B 220GHz PA MMIC Specifications & Technology | 51     |

| 2.2-C 220GHz PA Cell Design                                    | 53       |

|----------------------------------------------------------------|----------|

| 2.2-D PA Cell DC Design                                        | 56       |

| 2.2-E Matching and Tuning Networks                             | 59       |

| 2.2-F Circuit, Layout, and EM Simulation                       | 66       |

| 2.2-G 2:1 Combiner Design                                      | 68       |

| 2.2-H 4:1 Combiner Design                                      | 70       |

| 2.2-I Off-Wafer Combiners For Larger Power                     | 72       |

| 2.2-J PA MMIC Synthesis                                        | 74       |

| 2.2-K Efficiency Accounting In an 8-Cell PA MMIC               | 78       |

| 2 2                                                            |          |

| 2.3                                                            |          |

| SSPA MEASUREMENT AND CALIBRATION                               | 0.4      |

| 2.3-A Description of S-parameters                              | 81       |

| 2.3-B VNA Setup & Calibration                                  | 82       |

| 2.3-C Calibration Tolerances                                   | 86       |

| 2.3-D VNA Calibration Methods                                  | 87       |

| 2.3-E Power Sweep Testing 2.3-F Power Sweep                    | 90<br>92 |

| 2.3-F Power Sweep  2.3-G Calibration of the Power Bench        | 93       |

| 3                                                              | 75       |

|                                                                |          |

| RESULTS OF HIFIVE PA MMICS                                     | 0.5      |

| 3.1-A Results of HiFIVE 1 PA MMICs                             | 95<br>95 |

| 3.1-B Load Line comparison & 2 Cell PA 3.1-C 4-Cell Amplifiers | 96       |

| 3.1-D 8-Cell Amplifiers                                        | 98       |

| 3.1-E Tapeout 1 Conclusions                                    | 99       |

| 3.2-A Results of HiFIVE 2 PA MMICs                             | 99       |

| 3.2-B 4-Cell Multi-Stage PAs                                   | 100      |

| 3.2-C 8-Cell Multi-Stage PAs                                   | 102      |

| 3.2-D Tapeout 2 Conclusions                                    | 105      |

| 3.3-A Results of HiFIVE 3 PA MMICs                             | 105      |

| 3.3-B 16-Cell PA                                               | 106      |

| 3.3-C 8-Cell PA using new 8x6μm HBT                            | 108      |

| 3.3-D 16-Cell PA using new 8x6µm HBT                           | 109      |

| 3.3-E Tapeout 3 Conclusions                                    | 111      |

# FUTURE WORK AND CONCLUSION 4-A Future Module Construction 112 4-B Future MMIC Work 112 4-c Conclusion 113 REFERENCES APPENDIX: OTHER CIRCUIT DESIGNS A1-A UCSB InP HBT PA MMIC 118 A1-B V-band Phase Shifter Pixel 122

## **List of Figures and Equations**

| INTRODUCTION TO SSPA DESIGN                                                                       |     |

|---------------------------------------------------------------------------------------------------|-----|

| Eq. 1. Friis Transmission Formula                                                                 | 3   |

| Eq. 2. Wireless System Power Budget                                                               | 4   |

| Eq. 3. $f_{MAX}$ and $f_{T}$ for an HBT small signal model                                        | ç   |

| Fig. 1. HBT Small Signal Model. Mark Rodwell                                                      | ç   |

| Fig. 2. Plot of $f_T$ and $f_{MAX}$ vs. bias point of the HBT                                     | 11  |

| Fig. 3. HiFIVE Interconnect Stack for PA Design.                                                  | 14  |

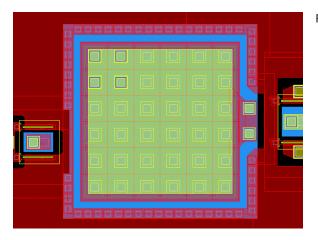

| Fig. 4. ADS 3-D Rendering of Tapeout 3 PA Cell with two 4x6μm HBTs                                | 14  |

| MICROWAVE POWER AMPLIFIER DESIGN                                                                  |     |

| Eq. 4. Linear Combinations                                                                        | 15  |

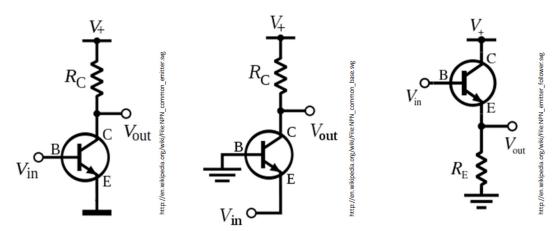

| Fig. 5. Single Transistor Amplifier Topologies: Common Emitter, Common Base, and Emitter Followe  | r18 |

| Fig. 6. Table of Voltage Gain, Input Resistance, and Output Resistance for Amplifier Topologies   | 19  |

| Fig. 7. Diagram of a Cascode Amplifier                                                            | 20  |

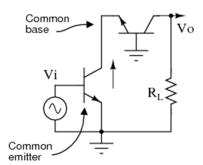

| Fig. 8. Plot of MAG/MSG for CE, CB, EF Amplifiers                                                 | 22  |

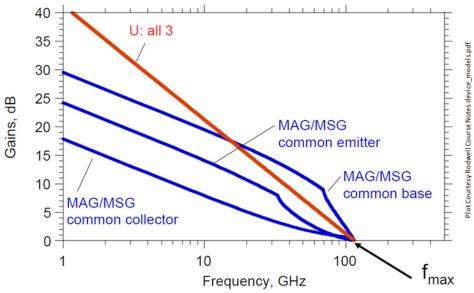

| Fig. 9. Transistor Safe Operating Area and Class A load line                                      | 24  |

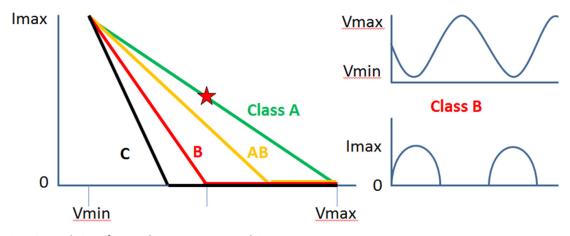

| Fig. 10. Load Lines for PA Classes A, AB, B, and C                                                | 27  |

| Fig. 11. DC power is consumed during time periods when both voltages and currents are non-zero.   | 27  |

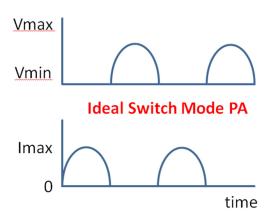

| Fig. 12. Desired Waveforms for an ideal switch-mode PA                                            | 28  |

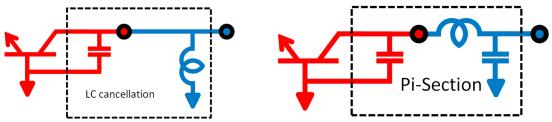

| Fig. 13. LC and Pi network cancellation of common-base output capacitance                         | 30  |

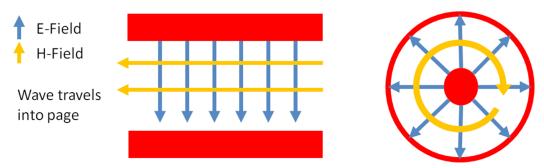

| Fig. 14. TEM Transmission Lines: Infinite Parallel Plate and Coaxial Lines                        | 31  |

| Fig. 15. Quasi-TEM Transmission Lines: Microstrip Lines                                           | 32  |

| Fig. 16. Model of a transmission line                                                             | 32  |

| Eq. 5. Characteristic Impedance for lossy and lossless transmission lines                         | 33  |

| Eq. 6. Input impedance of a loaded transmission line                                              | 34  |

| Eq. 7. Reflection and Transmission Coefficient                                                    | 36  |

| Eq. 8. Quarter-wave transformer input impedance                                                   | 37  |

| Fig. 17. Smith Charts: Real and Complex Impedances                                                | 38  |

| Fig. 18. Smith Charts: Admittances and Series/Shunt L/C                                           | 40  |

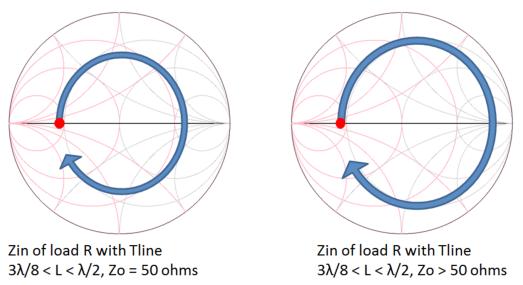

| Fig. 19. Smith Charts: Tracing Input Impedance with 50ohm and >50ohm TLines in a 50ohm system     | 41  |

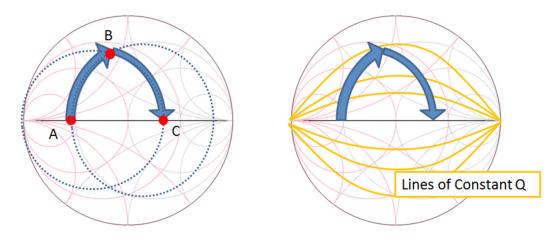

| Fig. 20. Smith Charts: Series L/Shunt C impedance matching and Lines of Constant Q                | 42  |

| Eq. 9. Rollette stability factor and stability measure                                            | 46  |

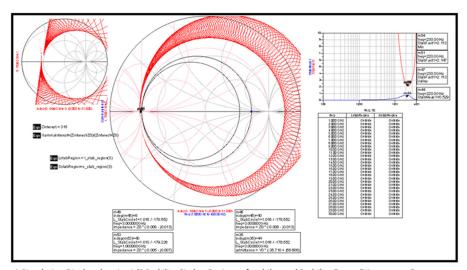

| Fig. 21. A Simulation of Source & Load Stability Circles, Stability Factor, and Stability Measure | 47  |

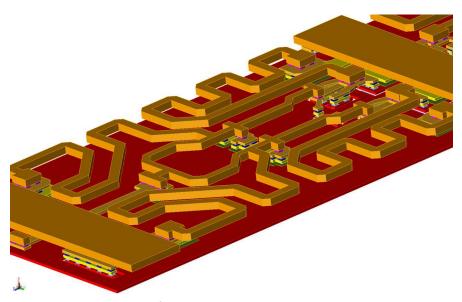

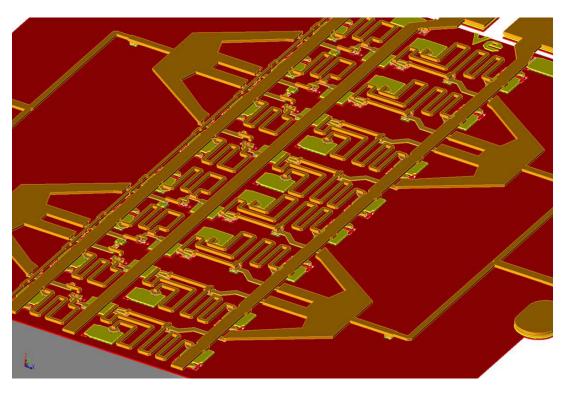

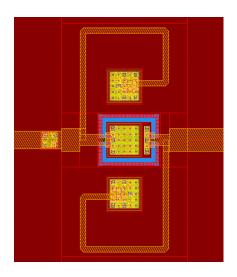

| Fig. 22. 3-D Rendering of an 8-cell SSPA                                                          | 48  |

| 220GHZ SSPA DESIGN                                                                                |     |

| Fig. 23. A DC Blocking Capacitor                                                                  | 55  |

| Fig. 24. A 220GHz tuned DC block                                                                  | 56  |

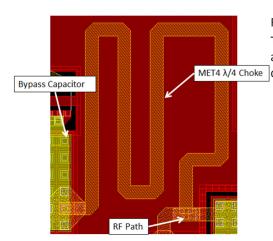

| Fig. 25. A Quarterwaye RF choke                                                                   | 58  |

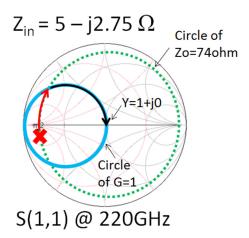

| Fig. 26. Smith Chart: PA Cell Input Tuning                                              | 60  |

|-----------------------------------------------------------------------------------------|-----|

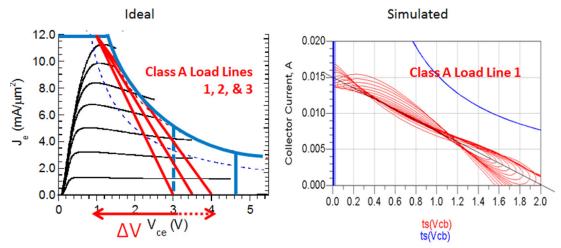

| Fig. 27. Ideal vs. Simulated Load Lines                                                 | 62  |

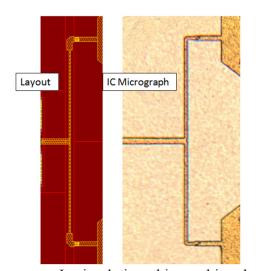

| Fig. 28. Layout and IC Micrograph View of 2:1 Combiner                                  | 69  |

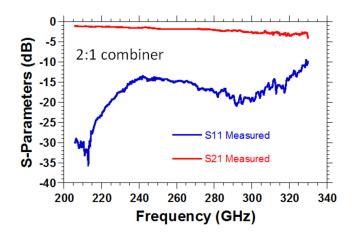

| Fig. 29. S11 and S21 of Back-to-back 2:1 Combiner                                       | 70  |

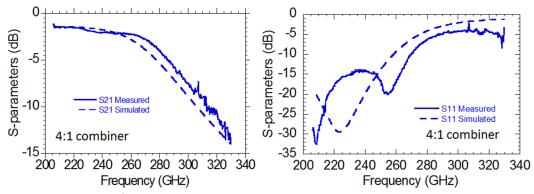

| Fig. 31. S-parameters for Back-to-back 4:1 power combiners. Measured vs. Simulated      | 71  |

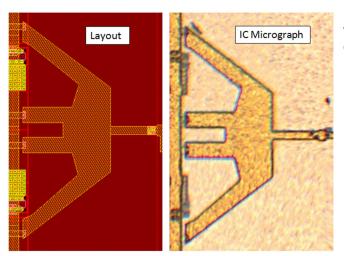

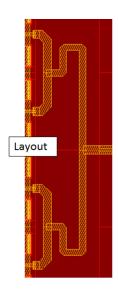

| Fig. 30. Layout and IC Micrograph View of 4:1 Dolph-Chebyshev Combiner                  | 71  |

| Fig. 32. Layout of New 4:1 Combiner used in Tapeout 3                                   | 72  |

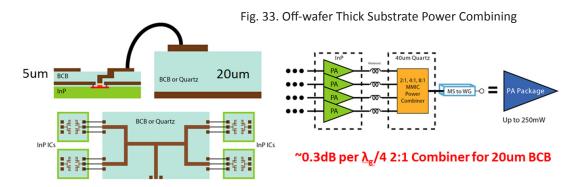

| Fig. 33. Off-wafer Thick Substrate Power Combining                                      | 73  |

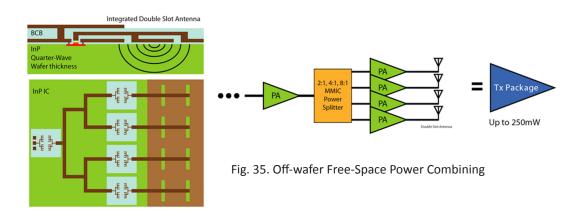

| Fig. 35. Off-wafer Free-Space Power Combining                                           | 74  |

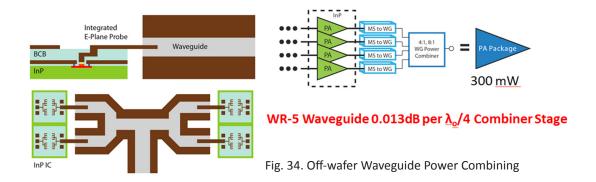

| Fig. 34. Off-wafer Waveguide Power Combining                                            | 74  |

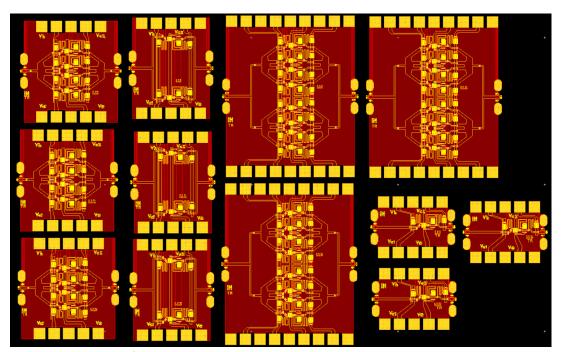

| Fig. 36. Layout Library for Tapeout 1                                                   | 76  |

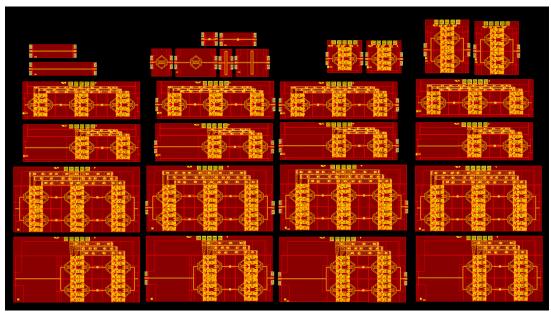

| Fig. 37. Layout Library for Tapeout 2                                                   | 77  |

| Fig. 38. Layout Library for Tapeout 3                                                   | 77  |

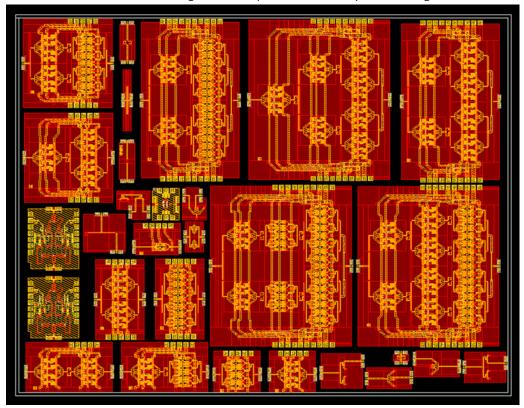

| Fig. 39. Schematic diagram of an 8-Cell SSPA with detail shown of a single PA Cell      | 80  |

| Fig. 40. Efficiency Table of DC power consumption and RF power losses in an 8-Cell SSPA | 80  |

| SSPA MEASUREMENT AND CALIBRATION                                                        |     |

| Fig. 41. Table of Waveguide Standards V-band and above                                  | 84  |

| Fig. 42. Image of 220-325GHz OML Frequency Extender Modules                             | 85  |

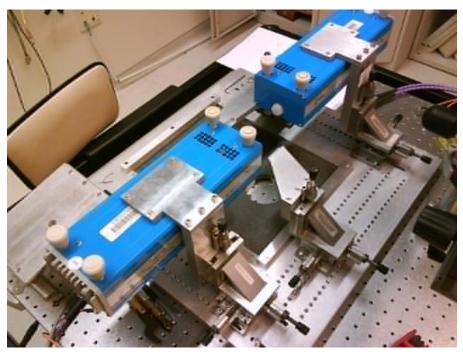

| Fig. 43. Image of VDI Multiplier Chain and Power Test Bench                             | 92  |

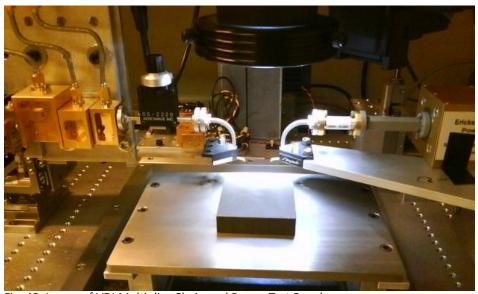

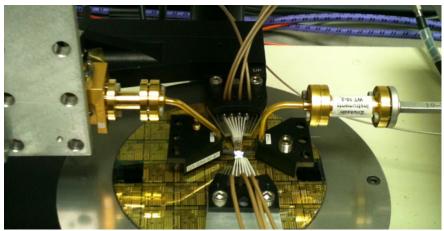

| Fig. 44. Image of wafer probes contacting the processed InP wafer                       | 93  |

| RESULTS OF HIFIVE PA MMICS                                                              |     |

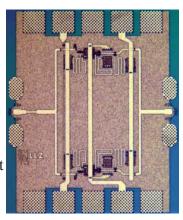

| Fig. 45. 2-Call PA Image                                                                | 95  |

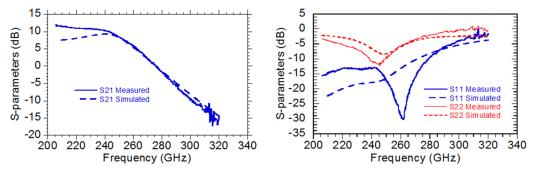

| Fig. 46. 2-Call PA S-parameters, measured vs. simulated                                 | 96  |

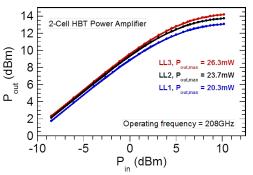

| Fig. 47. 2-Call PA power sweep comparison among three load lines                        | 96  |

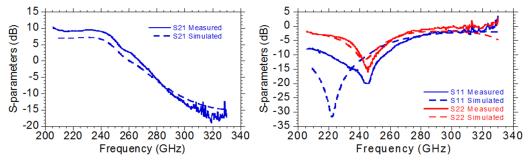

| Fig. 49. 4-Cell PA S-parameters                                                         | 97  |

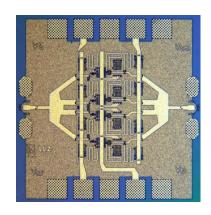

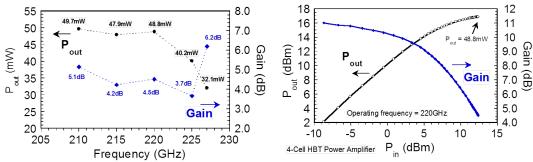

| Fig. 50. 4-Cell PA power and gain vs. frequency (left) and 220GHz power sweep (right)   | 97  |

| Fig. 48. 4-Call PA Image                                                                | 97  |

| Fig. 52. 8-Call PA S-parameters 206-325GHz                                              | 98  |

| Fig. 51. 8-Call PA Image                                                                | 98  |

| Fig. 53. 8-Cell PA power and gain vs. frequency (left) and 220GHz power sweep (right)   | 99  |

| Fig. 54. 4-Call, 3-Stage PA Image                                                       | 101 |

| Fig. 55. 4-Call, 3-Stage PA S-parameters 210-260GHz                                     | 101 |

| Fig. 56. 4-Call, 3-Stage PA Power Sweeps from 205-235GHz                                | 102 |

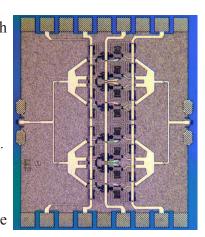

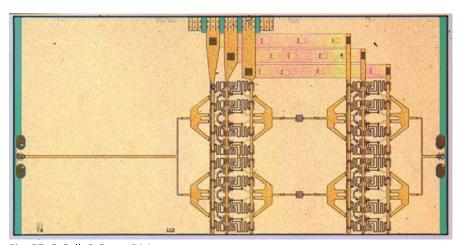

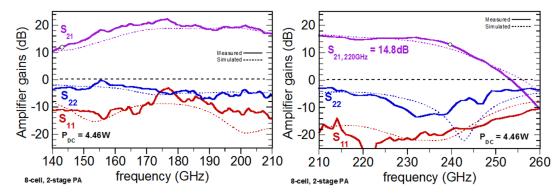

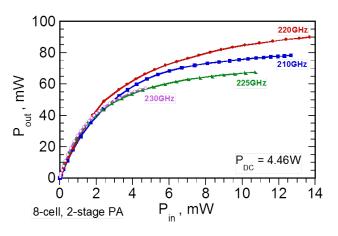

| Fig. 57. 8-Call, 2-Stage PA Image                                                       | 102 |

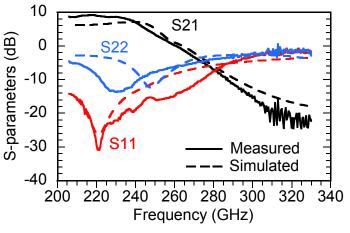

| Fig. 58. 8-Call, 2-Stage PA S-parameters in two bands covering 140-260GHz               | 103 |

| Fig. 59. 8-Call, 2-Stage PA power sweeps 210-230GHz                                     | 103 |

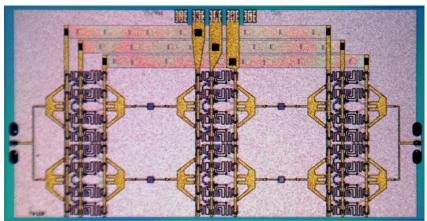

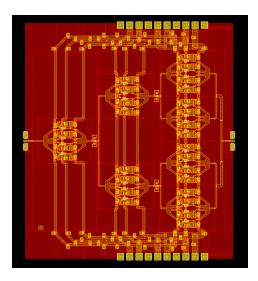

| Fig. 60. 8-Call, 3-Stage PA Image                                                       | 104 |

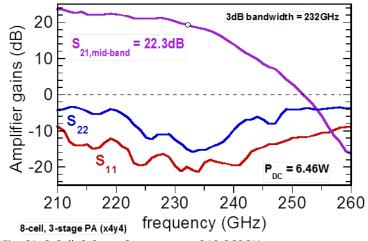

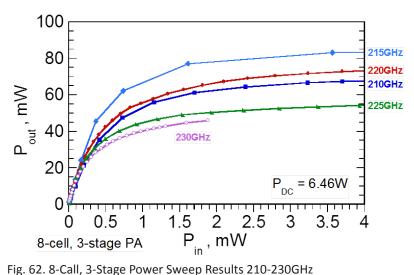

| Fig. 61. 8-Call, 3-Stage S-parameters 210-260GHz                                        | 104 |

| Fig. 62. 8-Call, 3-Stage Power Sweep Results 210-230GHz                                 | 105 |

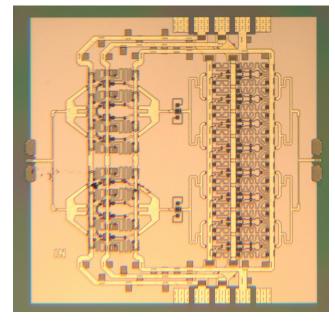

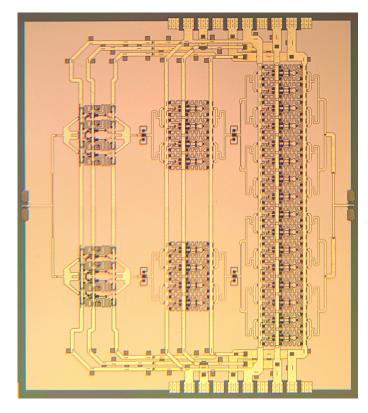

| rig. 63. 16-Cascode, 3-Stage PA image                                                 | 107 |

|---------------------------------------------------------------------------------------|-----|

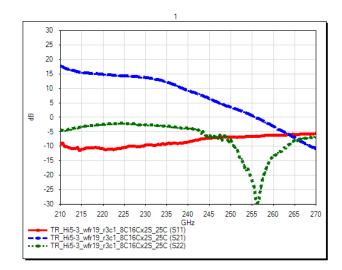

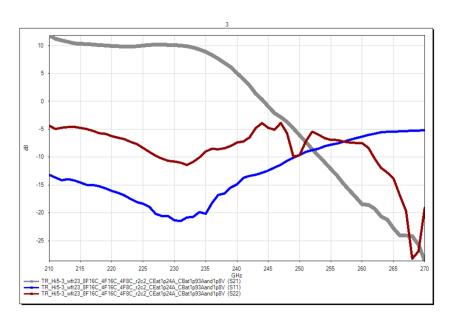

| Fig. 64. 16-Cascode, 3-Stage PA S-parameters 210-270GHz                               | 107 |

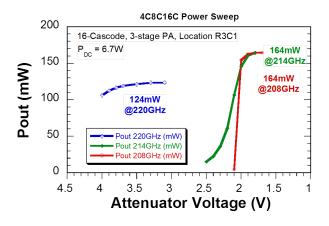

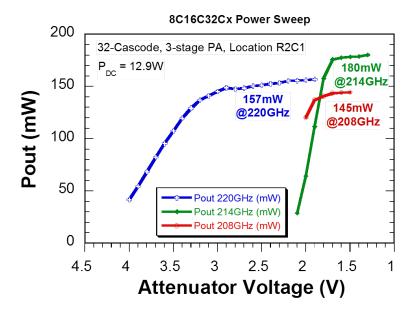

| Fig. 65. 16-Cascode, 3-Stage PA Power Sweeps 208-220GHz                               | 107 |

| Fig. 66. 16-Cascode, 2-Stage with new PA Cell Image                                   | 108 |

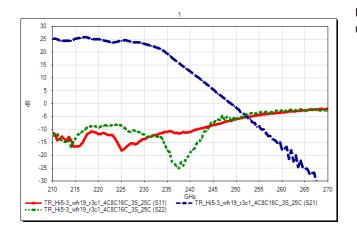

| Fig. 67. 16-Cascode, 2-Stage with new PA Cell S-parameters 210-270GHz                 | 109 |

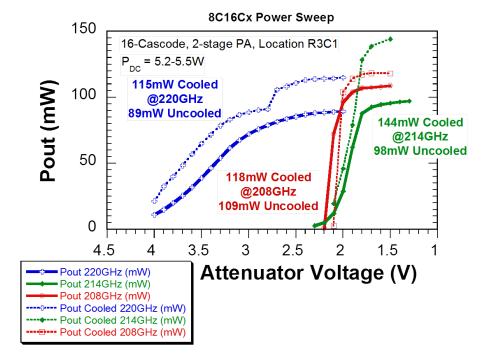

| Fig. 68. 16-Cascode, 2-Stage with new PA Cell power comparison of cooled measurements | 109 |

| Fig. 70. 32-Cascode, 3-Stage PA S-parameters                                          | 110 |

| Fig. 69. 32-Cascode, 3-Stage PA using new PA Cell Image                               | 110 |

| Fig. 71. 32-Cascode, 3-Stage PA cooled power sweep.                                   | 111 |

| FUTURE WORK AND CONCLUSION REFERENCES                                                 |     |

| APPENDIX: OTHER CIRCUIT DESIGNS                                                       |     |

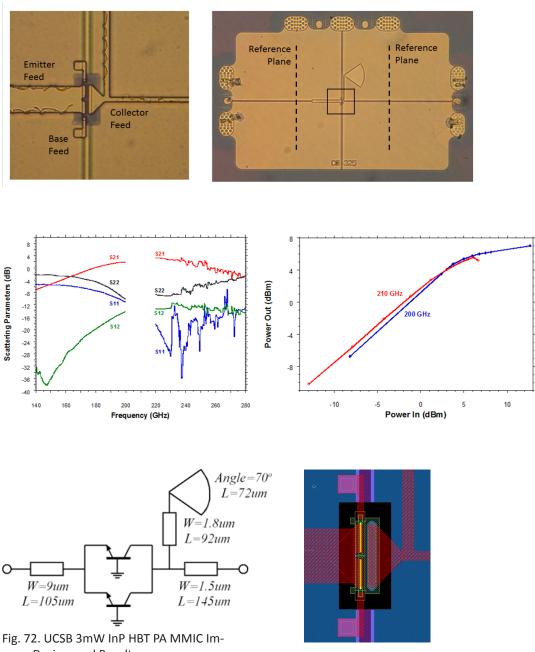

| Fig. 72. UCSB 3mW InP HBT PA MMIC Images, Design, and Results                         | 120 |

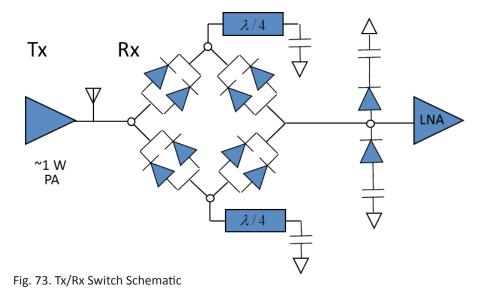

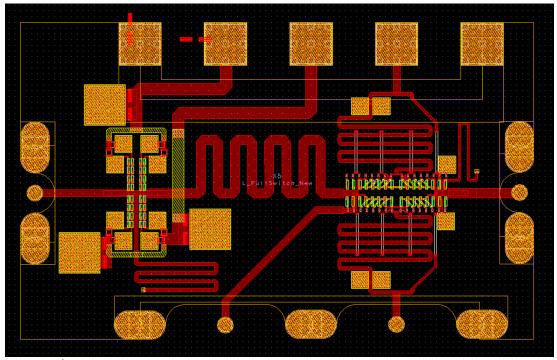

| Fig. 73. Tx/Rx Switch Schematic                                                       | 121 |

| Fig. 74. Tx/Rx Switch Layout                                                          | 122 |

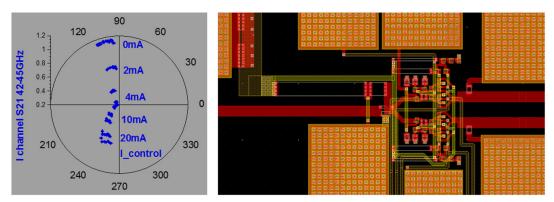

| Fig. 75. Phase Shifter Pixel Layout and Tuning Range Measurements                     | 123 |

## 1 Introduction to SSPA Design

#### 1-A INTRODUCTION

Extremely high frequency (30GHz to 300GHz) and far-infrared (300GHz to 3THz) electronics have been an area of high interest for many because of new transistor process technologies that can operate at those frequencies in the fundamental harmonic. Previous access to these frequencies was only possible through harmonic generation: A lower-frequency power amplifier produces a large output power and then a fraction of that power is converted into a high frequency signal through a frequency multiplier circuit. By using the frequency multiplier, however, the designer pays a significant toll in linearity, signal-to-noise ratio, and power-added efficiency.

With the maturing of higher frequency device processes, including the scaled InP DHBT, power amplification at high frequency has been made possible [1]. Fundamental tone circuits, including power amplifiers can now be designed and fabricated at these higher frequencies. As a result, systems requiring high power, linearity, SNR, and PAE can be considered. Even higher frequencies can then be accessed using harmonic frequency multipliation. The frontier of frequency can again be pushed higher

than before.

This pursuit is not solely for the breaking of records. Real systems are currently being researched that can demonstrate the usefulness of circuits above currently ubiquitous microwave/RF frequencies. Many of these circuits target low-loss free-space propagation windows located around 96GHz, 220GHz, 340GHz, and 670GHz, among others. These are local minima for free-space propagation losses due to absorption by common molecules in our atmosphere including H20 and O2 [2].

Future synthetic aperture radars and high resolution imaging systems will benefit greatly from continued development of solid state power amplifiers at these target frequencies. Efforts to increase the saturated power at 220GHz have been increasingly active. High power signals at 220GHz can be used to drive multiplier chains for THz applications or drive higher power vacuum tube amplifiers at the fundamental frequency [3]. Multiple power amplifier (PA) monolithic millimeter-wave integrated circuits (MMICs) can be mounted as pixels to form a high-powered array for radar systems. Many of these wireless applications will require additional output power at 220GHz to overcome attenuation due to weather events including heavy rain, humidity, dust storms, or fog.

#### 1-B DESIGN CHALLENGES AT 220 GHZ

Although 220GHz may be a local minimum for atmospheric absorption, this value is added onto already high signal attenuation caused by the spreading of electromagnetic energy in free space. The Friis formula shows that the magnitude of a received

signal after travelling through free space decreases as the square of range and also as the square of frequency [4].

This loss is a dominant factor in determining the minimum output power for a demonstration system. The amount of power necessary for a system at 220GHz can vary depending on system specifications—like range, antenna gain, bandwidth, and LNA noise factor. A simple communication system example can be illustrative of what the power requirements are at this frequency.

In a communications example, a 1Gbps wireless link is devised. With the right coding algorithm, a 3dB signal-to-noise ratio can be sufficient to extract data. A current status update on low-noise amplifiers (LNAs) showed that LNAs from 210-280GHz showed noise figures ranging from 7.5-11.5dB [5]. If a noise figure of 10dB is used in the example, the minimum received power at the receiver would be -70.8dBm.

$$\frac{P_{rec}}{P_{t}} = \alpha_{atm} G_{t} G_{r} \left(\frac{\lambda}{4\pi R}\right)^{2} = -1dB + 20dBi + 20dBi - 139dB = -100dB$$

Eq. 1. Friis Transmission Formula

Solving for the free-space signal attenuation can lead to a minimum transmitted power. For the example, a range of 300m at 220GHz, Tx/Rx antennas with 20dB antenna gain, and an atmospheric absorption of 3.3dB/km are selected. As a result, the absorption loss is 1dB and the free-space power spreading results in 139dB of signal loss. The result is a minimum transmitted power of 29.2dB or 0.83W.

$$P_{rec,min}=kTFBQ^2$$

$$P_{rec,min}=-173.8dBm/Hz+10dB(NF)+90dB(1Gbps)+3dB(Q^2)=-70.8dBm$$

Eq. 2. Wireless System Power Budget

This example illustrates that for systems at 220GHz, significant range can be used for this wireless system given that enough power can be generated. For a radar system, the usable range would at best be half that of the communication system example and lower for non-100% reflection of power. In either case, high minimum power requirements can only be met by increased development of power amplification at this frequency.

Apart from the high system power requirements at 220GHz, there are limitations to the potential gain and output power at the IC level. For a PA cell to have appreciable gain and output power at 220GHz, the transistor finger count and length will be limited by issues associated with device self-heating and interconnect parasitics of the multi-finger device [6]. At these frequencies, higher output power is achieved through on-wafer power combining. Careful design of the combiner is necessary to avoid excessive skin-effect loss; no significant increase in output power can come from combining if the insertion loss exceeds 1.5dB for a two-to-one power combiner.

Power amplifiers also struggle because the load tuning impedance for highest output power is almost never a "matched" impedance. Although high power generation may be occurring at the current source of the transistor, a percentage of that power may never be transferred to the load. This reduces the overall gain and output

power of the amplifier. Mismatched impedances increase the risk of standing waves, flow of power into other undesirable spurs, and waveform distortion.

#### 1-C NOTEWORTHY RESULTS

A noteable high-output power, solid-state, G-band (140-220 GHz) power amplifier is a sub-50nm InP HEMT amplifier having 75mW of saturated output power at 210 GHz in a waveguide-block package. The amplifier MMIC is designed with two side-by-side amplifiers with four common source stages. Each amplifier stage splits to and combines power from four HEMTs. Each of the eight total output HEMTs have a gate length of 120um. This design was done using a coplanar waveguide interconnect environment [7].

However, the work described in this dissertation uses InP HBTs. An early G-band medium power amplifier using InP HBTs produced greater than 8mW saturated output power at 190 GHz [8]. 300 GHz medium power amplifiers have been reported using 256-nm InP HBTs [9].

While 250nm InP DHBTs have much higher off-state breakdown compared to state-of-the-art InP HEMTs [10, 11], the usable voltage swing and current swing on the IV-plane (where MAG/MSG is appreciable) is similar. A closer examination of the MAG/MSG of a cascode cell formed with these technologies at high-mm-wave frequencies shows that the InP HBT cell yields more dB of gain compared to its InP HEMT counterpart.

For demonstration of a power amplifier at these same frequencies, low-loss

interconnects are essential. The use of a multi-layer, thin-film, substrate-shielded non-inverted microstrip environment using low-loss BCB ( $\epsilon r = 2.7$ ) available in the InP HBT processes allows very compact PA cells and combiner networks to be formed. These networks have much lower loss compared to similar networks formed in grounded coplanar waveguide (G-CPW) on thinned InP substrates, used in InP HEMT processes.

Power combining with multiple gate or emitter fingers is necessary for high saturated output power. On-wafer 4:1 and 2:1 power combiners have been demonstrated in a microstrip wiring environment at 95 GHz resulting in 427-mW of output power in a HEMT power amplifier [12]. 4-1 combiners at 220GHz were realized with similar Dolph-Chebyshev structures using coplanar waveguide in the 75mW amplifier reported above [6]. Additionally, a 206-294GHz mHEMT amplifier has been demonstrated using an identical non-inverted, shielded, thin-film microstrip environment with dense interconnect vias as the amplifiers reported here [13].

For a more complete coverage of all the power amplifier and low noise amplifier results, a recent Samoska paper may be consulted [5]. Amplifier power density (Watts per millimeter of transistor output periphery) are also reported in the Samoska paper.

#### 1-D NOVEL METHODS IN 220GHZ PA DESIGN

Taking the previous work and design challenges into consideration, this work shows that with correctly sized HBTs, care can be taken to model interconnect parasitics

within each power amplfier cell. Multiple modular cells can then be placed in parallel and power combined for a large overall power.

Rather than using a single-transistor amplifier in each PA Cell, an ac-coupled cascode was designed using a 4x6µm-long common emitter HBT and a 4x6µm-long common base HBT to provide high maximum available/stable gain (MAG/MSG) and high power handling at 220GHz. Interconnects, tuning networks, and DC chokes are modeled individually and collectively using a 2.5-D EM simulator to take into account openings in the ground plane, parasitic capacitances, and any inductive coupling behavior. Power combiners in low-loss thin-film microstrip have been demonstrated using a Dolph-Chebyshev structure for 4:1 combining/splitting and a quarter-wave structure for 2:1 combining. Power supply simulation revealed potential instabilities in the RF circuit and those design weaknesses were mitigated by RF stabilization of the power supply feeds.

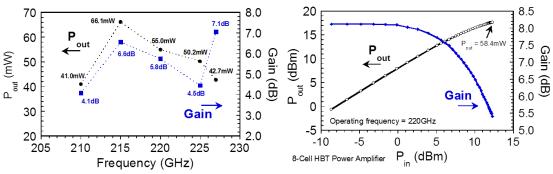

Using this approach, state-of-the-art ICs were demonstrated. A 4-Cell amplifier with 48.8mW of output power at 220GHz was measured with first pass design success. A 4.5dB compressed gain was measured at that power level. This MMIC had an S21 of 10.1dB at 220GHz and a 3dB bandwidth from 206 to 254GHz. Its DC power consumption was 1.1W [14]. An 8-Cell PA on the same maskset could not be driven fully into compression, but did show 58.4mW of output power. The S21 of this PA MMIC was 8.9dB at 220GHz and the DC consumption was 2.2W [15].

In a second tapeout, multi-cell PA MMICs were fabricated using similarly

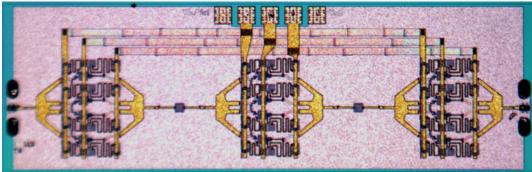

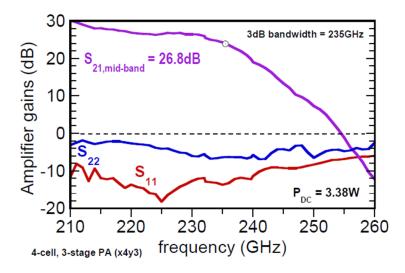

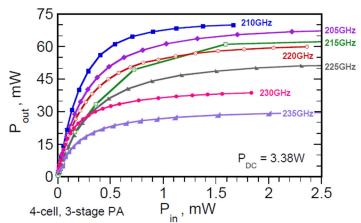

sized output amplifier stages. Additional gain stages were added to decrease the power requirements of the RF source used in power testing. An 8-cell, 2-stage amplifier showed 90mW of output power at 220GHz at 8.2dB compressed gain [16]. It had an S21 of 14.8dB at 220GHz and a DC power consumption of 4.46 W. In addition a 4-Cell, 3-Stage amplifier showed an S21 of 26.8dB at a DC power consumption of 3.38W. This design had an output power of 55.5mW at 220GHz with 17dB gain [17].

The third tapeout sought to increase power density in the PA Cells and increase the number of power combining levels. A PA Cell with 8x6µm HBTs was designed using a novel 3-port output power tuning network. One PA uses 16 of these new PA Cells in the output stage for an overall 4x increase in HBT output periphery. The 3-stage amplifier was designed to target 400mW output power at a gain of 17dB. In initial full-thickness substrate tests, the PA MMIC (2.2mm x 2.5mm) biases properly with a total DC power consumption of 11W and an S21 of 9.9dB in the first lot was below simulated estimates. The lower gain is due to insufficient heat dissipation of the full-thickness DUT. Full-thickness power measurements with forced air cooling showed a drastically higher gain and output power. The largest amplifier showed 180mW of saturated output power at 214GHz with cooling.

#### 1-E INP HBT TECHNOLOGY DESCRIPTION

Indium Phosphide (InP) is a III-V semiconductor material that has been of research interest because of its low effective mass and potential for very high velocity electron transport. Heterojunction Bipolar Transistor (HBT) technology has historically been a

transistor type used to maximize the transition frequency  $(f_T)$  and maximum frequency of oscillation  $(f_{MAX})$  and is common for RF PAs in other material systems including GaAs. Device high frequency operation is limited by the transit time for an electron to travel through the base and collector of the transistor. Capacitor charging time constants associated with access resistances and parasitic capacitances—caused by depletion, diffusion, and electric field across bulk semiconductor—also have a strong effect on  $f_T$  and  $f_{MAX}$  as shown in the formulas below [18].

$$f_{max} = \sqrt{\frac{f_T}{8\pi R_{bb}C_{cbi}}} \qquad f_T = \frac{g_m}{2\pi (C_{be} + C_{cbi})} \qquad \frac{f_{be}}{C_{be,diff}} = \frac{g_m}{g_m V_{be}} e^{-j\omega v_{cb}}$$

$$f_{max} = \sqrt{\frac{f_T}{8\pi R_{bb}C_{cbi}}} \qquad f_T = \frac{g_m}{2\pi (C_{be} + C_{cbi})} \qquad \frac{f_{be}}{C_{be,diff}} = \frac{g_m V_{be}}{g_m V_{be}} e^{-j\omega v_{cb}}$$

$$f_{a} = \sqrt{\frac{f_T}{8\pi R_{bb}C_{cbi}}} \qquad f_T = \frac{g_m}{2\pi (C_{be} + C_{cbi})} \qquad \frac{f_{be}}{C_{be,diff}} = \frac{g_m V_{be}}{g_m V_{be}} e^{-j\omega v_{cb}}$$

$$f_{a} = \sqrt{\frac{f_T}{8\pi R_{bb}C_{cbi}}} \qquad f_T = \frac{g_m}{2\pi (C_{be} + C_{cbi})} \qquad \frac{f_T}{C_{be}} = \frac{g_m V_{be}}{g_m V_{be}} e^{-j\omega v_{cb}}$$

$$f_{a} = \sqrt{\frac{f_T}{8\pi R_{bb}C_{cbi}}} \qquad f_T = \frac{g_m}{2\pi (C_{be} + C_{cbi})} \qquad \frac{f_T}{C_{be}} = \frac{g_m V_{be}}{g_m V_{be}} e^{-j\omega v_{cb}}$$

$$f_T = \sqrt{\frac{f_T}{8\pi R_{bb}C_{cbi}}} \qquad f_T = \sqrt{\frac{g_m}{2\pi (C_{be} + C_{cbi})}} \qquad \frac{f_T}{C_{be}} = \frac{g_m V_{be}}{g_m V_{be}} e^{-j\omega v_{cb}}$$

$$f_T = \sqrt{\frac{f_T}{8\pi R_{bb}C_{cbi}}} \qquad f_T = \sqrt{\frac{g_m V_{be}}{g_m V_{be}}} e^{-j\omega v_{cb}}$$

$$f_T = \sqrt{\frac{g_m V_{be}}{g_m$$

Eq. 3.  $f_{MAX}$  and  $f_{T}$  for an HBT small signal model Fig. 1. HBT Small Signal Model. Mark Rodwell

Many of the developments in the InP HBT at UCSB in Mark Rodwell's group have followed a desire to reduce the transit time within the HBT by scaling base and collector thicknesses and seeking to reduce the parasitic resistances and capacitances through major materials efforts and lateral device scaling [1]. The time constants associated with transit and capacitor charging are the factors that determine a transistor's maximum oscillation frequency. Miguel Urteaga and Zach Griffith demonstrated the 250nm InP HBT technology at UCSB with  $f_{MAX}$  over 400GHz [19, 20]. Later, Ashish Baraskar demonstrated the reductions in base contact resistance that would be necessary to reach above 1 THz  $f_{MAX}$  [21]. Vibhor Jain demonstrated a 220nm InP HBT technology generation with an  $f_T$  of 480GHz and  $f_{MAX}$  of 1.0 THz [22].

According to Mark Rodwell's transistor scaling roadmap [1], in order to get even faster transistors, further reduction of access and contact resistances must occur.

#### UCSB Technology Description

Work done within the University of California, Santa Barbara cleanroom in InP HBT research (Mark Rodwell Group) is done mostly with the purpose of achieving very high frequency transistors. The focus of masksets in the UCSB process is to create scaled transistors and little else—to facilitate faster processing, measurement, and improvement to subsequent transistors. Limited space is granted to circuit designers in these very experimental processes for circuit design (see Appendix 1). Even with space for circuits, only an ideal physics transistor model exists for circuit simulation of this experimental device process. This model is based solely on the ideal physical structures found in the HBT—e.g. collector thickness and corresponding InP electrical permittivity for C<sub>CB</sub>. This model's value is limited for an experimental process because, materials within the device, their physical size, shape, and relative position are highly variable in processing.

A full IC process for the UCSB designs include transistors, a thin Au film (0.2-0.3µm-thick) parallel to the InP substrate at the level of the collector (Coll MET) used as a ground plane, and a 0.8-1.0µm-thick layer of Au (MET 1) that can be placed to contact the emitter metal. A 0.8-1µm-thick layer of BCB (Er=2.7) is used as a dielectric layer between Coll MET and MET 1. In design work, it is convenient to use MET 1 as a signal interconnect for microstrip transmission lines. No resistors or capacitors are available in this process.

Given the challenges associated with using the UCSB process for circuit design, it has the potential to be an extremely high speed process. Most recent reported

data shows that  $f_{MAX}$  of these transistors has reached above 1 THz [22].

Teledyne Technology Description

Apart from UCSB's research laboratories, more mature InP HBT processes exist that make high-transistor-count InP circuits more feasible. The work described in this dissertation was brought about primarily using IC tapeouts at Teledyne Scientific Company, located in Thousand Oaks, CA. Many of the processes which Teledyne has perfected were born in the labs of UCSB, Rodwell, and his former Ph.D. students.

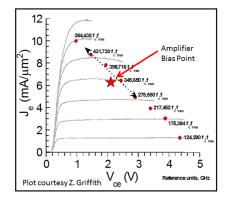

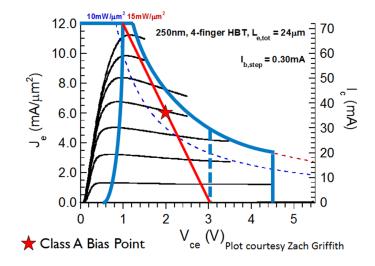

For the majority of design work done for this dissertation project, the Teledyne 250nm InP HBT process was used. The HBT has a breakdown voltage of 4.5V. The integrated circuit technology features single InP HBTs that have peak  $f_T$  of 400GHz and  $f_{MAX}$  of 700GHz. However, transistor gain,  $f_T$ , and  $f_{MAX}$  vary strongly with Quiescent bias point. Typically, current densities near the kirk current and base-collector voltages just above the knee voltage result in the highest transistor  $f_T/f_{MAX}$  for these transistors.

Fig. 2. Plot of  $f_T$  and  $f_{MAX}$  vs. bias point of the HBT Data taken from a UCSB 250nm InP HBT [Z. Griffith, et al., "Z. Griffith, E. Lind, M. Rodwell, Xiao-Ming Fang, D. Loubychev, Ying Wu, J. Fastenau, A. Liu, "Sub-300 nm InGaAs/InP Type-I DHBTs with a 150 nm collector, 30 nm base demonstrating 755 GHz  $f_{MAX}$  and 416 GHz  $f_T$ ," Indium Phosphide & Related Materials, IEEE 19th Annual Conference on, pp.403,406, 14-18 May 2007].

New transistor device layouts were also developed at Teledyne for use in PA design for this project. Using longer HBTs or multi-finger HBTs, a much higher total

current and higher maximum RF power can be realized versus a single short device optimized for high frequency performance. For HBTs longer than 6um, parasitic base feed inductance and resistance causes significant degradation in maximum available gain for a single transistor. As a result, multi-finger HBTs were developed for larger RF power handling. The trade-off in device layout centers in the compactness of the multi-finger layout versus transistor self-heating. A more compact cell has reduced parasitic inductance, resistance, and phase difference associated with the routing signal to all the bases, emitters, and collectors of the multi-finger device [6].

With a compact HBT layout, there is more dc power consumption per unit area. Self-heating effects can drastically reduce the transistor gain. In work done by Z. Griffith at Teledyne, various types of multi finger devices were laid out and tested. As a result of his work, a 4-finger HBT was created with 4 single-sided HBTs each with 6 $\mu$ m emitters. This device was selected for PA MMICs because it maintained a level of high frequency performance at 220 GHz that was comparable to the performance of a single finger HBT. A single common-emitter HBT (CE) shows a  $f_r$ =350GHz and  $f_{MAX}$ =590GHz at the amplifier's quiescent bias point of Je=5.5mA/  $\mu$ m² and a Vce=1.8V. In comparison, The 4-finger HBT as described had  $f_r$ =333GHz and  $f_{MAX}$ =530GHz under the same bias conditions. This shows that the parasitics associated with using the multi-finger HBT does little to decrease the available gain at 220GHz in PA designs. For PA design, both a common emitter and common base 4-finger HBT were developed. The physical size of the CE device was 18x7.5 $\mu$ m². The physical size of the CB device was 6x9 $\mu$ m² [6].

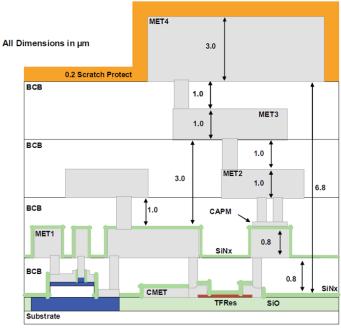

Development of this process technology has resulted in a designer's guide containing design rules to increase device and circuit yield. As the technology has evolved, the process has featured a 3- or 4-layer Au interconnect stack depending on the desires of the customer and the end use of the circuits being designed. Metal layers in the interconnect stack can flexibly be used for transmission lines, grounding, or power supply. For a 1µm thick metal interconnect, the maximum supported current density is 5mA/um. For the PA interconnects, the MMIC process had 4 metal layers not including the thin collector metal layer (CMET). During the first iteration of designs, all four metal layers were 1µm thick with 1µm of BCB (Er=2.7) between each layer. The result was a maximum microstrip transmission line dielectric height of 5um. In subsequent runs of the PA designs, Teledyne provided a thicker 3µm MET 4 layer to allow for greater current flow to the design under test for the same width of power supply line.

NiCr resistors are available on the collector metal layer at 50ohm/square. The thickness of the resulting NiCr layer is quite small (.02um). The resistors are limited to 1mA/μm of width, but have been shown to handle higher current densities. Capacitors are available in the process between the MET 1 and MET 2 layers in the process. A thin layer (0.2um) of Silicon Nitride is deposited with another layer of Au above it. A via connects the top CAPM layer to MET 2. The result is a capacitor that can be designed with 0.3 fF/μm². A very convenient capacitor to ground with few parasitic effects beyond 220GHz can be generated When MET1 is selected as a ground plane and MET2 is used to access the top capacitor metal layer.

Fig. 3. HiFIVE Interconnect Stack for PA Design.

[Z. Griffith, M. Urteaga, R. Pierson, P. Rowell, M. Rodwell, B. Brar, "A 204.8GHz Static Divide-by-8 Frequency Divider in 250nm InP HBT," *Compound Semiconductor Integrated Circuit Symposium (CSICS), 2010 IEEE*, pp.1-4, 3-6 Oct. 2010.]

Fig. 4. ADS 3-D Rendering of Tapeout 3 PA Cell with two  $4x6\mu m$  HBTs

# **2.1**Microwave Power Amplifier Design

#### 2.1-A LINEAR AMPLFIERS

When speaking with colleagues in other disciplines about amplifiers, I simply describe an amplifier as a system where upon putting in a signal, you get the same signal out, just larger. Audio amplifiers connected to microphones and speakers are a much more palpable example (versus high frequency amplifiers) for non-engineers. Someone speaks at one level and a much louder sound comes out.

Like most things, amplifiers also have limitations. The most significant limit for an amplifier is the range of power levels within which it can operate as a linear amplifier [23]. Suppose you have two signals. When put through a system, each input results in a unique output. A linear system is one in which the system performs operation such that if any linear combination of those two signals is input into the system, then the output is the linear combination of the two individual outputs. This is shown below:

$$f(Ax + By) = Af(x) + Bf(y)$$

Eq. 4. Linear Combinations

Linear amplification allows designers to enlarge a signal without distorting it.

An amplifier's linear range is bounded at low and high power. The linear limit of an amplifier at low input powers is the minimum detectable signal above the amplifier's input noise floor.

The upper limit on amplifier linearity has to do with the maximum amount of voltages and currents that can be generated by the amplifier. If driven with larger RF input power, no gain in RF ouptut power will be shown. This roll-off in output power is called gain compression because the gain is reduced to zero as more power is applied to the input. There are two ways to quantify this gain compression effect. The maximum power observed as a plateau in  $P_{\text{OUT}}$  vs.  $P_{\text{IN}}$  is called the saturated output power. When signals are fully compressed, other non-linear effects can cause significant distortion to communication signals. Many engineers value a different statistic called the 1dB-compression point. This is the output power level where the gain has dropped by 1dB from the small signal level.

Besides gain compression, there are other large-signal distortion effects that can be important in amplifier design for communication systems. When two or more nearby tones are sent through any system with nonlinearities (including amplifiers, mixers, etc.), the system generates harmonics of the individual fundamental tones and sum and differences of the two frequencies. The third order difference frequencies lay close enough to the signals of interest that they can't be filtered out in typical systems and can cause signal distortion.

The third-order term in the output signal is usually not significant relative to

the rest of the signal under small signal conditions because it has a small Taylor series coefficient. Being a cubic  $(x^3)$  term, the power level (in dB) increases three times faster than the linear or fundamental output term  $(x^1)$ . This means that at a given power level, the third order term and the first order term will be equivalent in power level. The input power level at which these two terms have equal power levels is considered the Third Order Intermodulation Intercept Point (IIP3).

In practice, the amplifier is in heavy gain compression much before the third-order signal gets anywhere near the power level of the fundamental signal. To get a value of IIP3, the  $P_{\text{OUT}}1$  and  $P_{\text{OUT}}3$  versus  $P_{\text{IN}}$  can be observed in the amplifier's linear range. The trends for  $P_{\text{OUT}}1$  and  $P_{\text{OUT}}3$  can be extrapolated so that an intercept point can be found.

For the amplifiers reported in the academic literature, the way power amplifier statistics are reported varies. For circuits up to 67GHz, it is common to see noise figure, IIP3, P1dB, and saturated output power. For higher frequencies including 220GHz, noise figure and IIP3 are often omitted because of the complexity of creating a proper test bench for such measurements. Currently available measurement systems above 67GHz are expensive, rare, and often lack sufficient dynamic range to give reliable data. However, it seems likely that new generations of spectrum analyzers and signal generators reaching up to 220GHz may come soon.

#### 2.1-B TRANSISTOR AMPLIFIER TOPOLOGIES

From what are high frequency amplifiers constructed?

Designing amplifiers with highly scaled transistors is an effective way to achieve RF amplification at high frequency. The technology used for the amplifiers reported here is described in depth in the InP HBT technology section of this dissertation. A standard transistor is a three port device. In a common transistor amplifier configuration, one of the ports is used as an AC ground reference, another is used as an RF output current source, while the third port is an RF input that controls that current source [24]. Device operation for amplifiers usually has the base-emitter junction forward biased to control current flow while the base-collector junction reverse biased to act as a current source. Three common single transistor amplifiers are shown below:

Fig. 5. Single Transistor Amplifier Topologies: Common Emitter, Common Base, and Emitter Follower

When biased and supplied with an RF input signal, the common emitter amplifier acts as a trans-conductance amplifier meaning an RF Input voltage results in an

RF current swing. The common base is a voltage gain amplifier, meaning the RF current flowing from input to output is constant while voltage swing increases from input and output. The common collector (also known as an emitter follower) is a current gain amplifier.

|                     | Voltage<br>Gain                 | Input<br>Resistance       | Output<br>Resistance |

|---------------------|---------------------------------|---------------------------|----------------------|

| Common<br>Emitter   | -g <sub>m</sub> *R <sub>c</sub> | $R_{\pi} = \beta / g_{m}$ | $R_c$                |

| Common<br>Base      | g <sub>m</sub> *R <sub>c</sub>  | 1/g <sub>m</sub>          | $R_c     r_{out}$    |

| Emitter<br>Follower | 1                               | β*R <sub>E</sub>          | 1/g <sub>m</sub>     |

Fig. 6. Table of Voltage Gain, Input Resistance, and Output Resistance for Amplifier Topologies

In linear amplifiers, transistors act as an energy conversion device. DC power is converted into RF power proportional to the RF input signal. The drain efficiency is a ratio of RF output power to DC power consumption in the circuit. Similarly, the power added efficiency (PAE), is the RF output power minus RF input power all divided by the DC power consumption.

Apart from single transistor amplifier configurations, other multi-transistor amplifiers are possible. One very common topology for high gain and bandwidth is a cascode amplifier.

Fig. 7. Diagram of a Cascode Amplifier

A cascode amplifier as a two or more transistor amplifier topology has the benefit of two gain stages in row including a transconductance stage and a voltage gain stage that can result in a higher overall output impedance than a common emitter alone. Cascodes also have great input-output isolation which makes RF matching network design a more straight-forward effort at high frequency. However, the large available gain at high frequency could also result in potential instabilities over large RF bandwidths. The gain of a cascode amplifier is shown below:

Other amplifier topologies exist (e.g. a Cherry-Hooper amplifier) but such amplifiers require a large number of transistors that are to be connected in close proximity. This makes routing signals to each transistor with low parasistics tricky. Also, introducing many transistors in a small area can incur a penalty with grounding the circuit at high frequency. Selection of a low-metal layer ground plane will result in many holes in that plane and impede the flow of ground return currents. A high-metal layer ground plane selection will incur added resistance and inductance for grounding through vias.

#### 2.1-C BANDWIDTH CONSIDERATIONS AND PARASITICS

Amplifier design can take different forms depending on what frequency of operation is desired relative to the maximum frequency of oscillation of the transistor. Near the flat band of gain for a transistor, closed loop transfer function theory, compensation, and feedback can be used to extend the bandwidth of the amplifier and achieve gains near the beta or gm of the transistor.

At frequencies near  $f_{MAX}$ , device capacitances become increasingly more significant. At these frequencies, gain slopes that drop 20dB per decade have had more than a decade drop from its 3dB bandwidth for InP HBTs. An unmatched transistor will likely have an S21 gain less than 0dB as frequency approaches  $f_{MAX}$ , meaning that if no tuning techniques are applied to the transistor's ports, it will not act as an amplifier at all.

At high frequency, "microwave" techniques can be used to achieve the maximum available or stable gain of the transistor amplifier. For frequencies below  $f_{MAX}$ , the MAG/MSG is greater than zero for common emitter and common base transistors. MAG is the term for the maximum gain possible at a given frequency given that the amplifier is unconditionally stable. MSG is the term for the maximum gain possible for a potentially unstable amplifier after it has been stabilized or made unconditionally stable.

Fig. 8. Plot of MAG/MSG for CE, CB, EF Amplifiers

One noteable characteristic of all these amplifiers is that since the transistor current gain, capacitances, and transit time are what dominate the maximum frequency of oscillation, the  $f_{MAX}$  of the transistor remains the same no matter which configuration (e.g. CE, CB, EF topologies). However, the relative position of parasitic capacitances and resistances at each port have a significant impact on the available gain and input/output impedance of the transistor amplifier. In order to get amplifiers to provide gain at high frequency, careful consideration of transistor impedances must be taken. It will be shown that "Microwave"-style (millimeter-wave) matching and tuning networks will provide a way to access gain at frequencies like 220GHz.

#### 2.1-D RF POWER AMPLIFIERS

Power amplifiers are designed to push transistors to their highest possible RF power densities. At lower frequencies, PAs with watts, kilowatts, or megawatts can be de-

signed depending on the size of transistor used. In all cases, high power is achieved by swinging RF voltages and currents to a transistor's physical limits.

A transistor's operation is limited by maximum and minimum voltages and currents. This portion of the IV-plane can be described as a transistor's high performance operating area. The linear or saturation region of operation is a desirable place for amplifier gain. This is limited at low voltage bias by the saturation (or knee) voltage. This is the bias above which the collector-base junction in the transistor is reverse-biased and acts as a current source. In other words, this is the minimum voltage to turn the amplifier on. A hard limit to maximum operating voltages is the breakdown voltage of the transistor. At this voltage, large electric fields lead to avalanche breakdown, a current multiplication effect, and irreversible damage. A softer limit on the maximum voltage in a transistor exists as well. As the transistor swings into the higher voltage area of operation, the  $f_{\rm T}/f_{\rm MAX}$  are reduced because of increased base-collector capacitance. The result is a reduction of maximum available gain at the design frequency.

Current limits also exist. At low currents (near zero) the transistor has little or no gain. At high currents the transistor reaches the kirk current limit—meaning the current density is so high that base transit time increase significantly due to base push out, thus reducing the available gain of the transistor at the design frequency. In addition, high power densities (product of instantaneous current and voltage) can lead to reduced performance over time and device destruction. Since power density is based on the time averaged power density of the transistor, a y = 1/x curve can be drawn to

show the safe long-term power density limit of the transistor.

The resulting high performance operating area of the Teledyne 250nm InP HBT is shown below:

Fig. 9. Transistor Safe Operating Area and Class A load line

The Class A amplifier is biased at the midpoint of its load line.

This is marked with a star. Blue lines denote operating area limits due to Kirk effect, destructive power density, breakdown, and gain reduction.

In this InP HBT process, voltages are limited by the breakdown voltage,  $V_{CE}$  =4.5V, and the knee voltage,  $V_{CE}$ ~=0.8V. Maximum available gain at 220GHz drops significantly above 3V. The maximum current density in the transistor is ~12mA/ $\mu$ m² or for a single 6 $\mu$ m-long transistor 17.5mA. The destructive power density limit is at 20mW/ $\mu$ m² with a safe long-term operating power density of 15mA/ $\mu$ m². Within the region on the IV curve defined by these limits, an amplifier can operate with gain and avoid degraded performance or destruction.

As a designer, it is possible to control how voltages and currents swing in the IV plane. The way in which currents and voltages swing in an amplifier is called the Load Line. One thing to note is that if the amplifier has any energy storage parasitics (capacitance or inductance), the load line won't look like a line at all. Instead a curve

will show how instantaneous currents and voltages change throughout the sinusoidal cycle. There is an advantage to turning an oval or circular load line into a linear relationship. As higher power levels are introduced, circular load lines take up more of the IV plane and could potentially begin sweeping instantaneous power densities outside the transistor's power density limit

#### 2.1-E CLASS A POWER AMPLIFIERS

A classic loadline is used in a Class A amplifier. In this power amplifier, a large output power is generated by sweeping the loadline from one corner of the safe operating area to the other. At one end, there is the maximum instantaneous current and the minimal knee voltage. At the other end of the load line, there is near-zero current and voltages near breakdown. For a Class A power amplifier, the transistor will be biased at the center of the load line— $V_{CE}=(V_{BR}+V_{KNEE})/2$  and  $Ic=I_{MAX}/2$ . The resulting output power will be  $(V_{BR}-V_{KNEE})*(I_{MAX})/8$ . With knowledge of the DC bias point and the maximum RF output power, a collector efficiency can be calculated. For a  $V_{KNEE}=0V$ , a class A power amplifier consumes an average of  $(V_{BR}/2)*I_{MAX}/2=V_{BR}*I_{MAX}/4$ , while the RF output power is  $V_{BR}*I_{MAX}/8$ . The resulting maximum theoretical collector efficiency is 50% [23].

The actual efficiency of the transistor will always be less than 50%. The knee voltage cannot be zero, not only does the collector base junction need to be reverse biased by a small voltage to stay on, but the emitter base junction must be significantly forward biased. In the InP HBTs used in this project that knee voltage was up to 1.0V

at the maximum current value. In addition, any IR drops in bias control resistance and power feeds adds to the total DC power consumed. The RF power will pass through transmission lines, power combiners, pads, waveguide transitions, and waveguides that all have a finite associated loss. These losses can reduce the RF output power significantly. Smaller RF output and larger DC consumption reduces efficiency directly.

Efficiency may seem relatively arbitrary in a laboratory setting. But for system design, power consumption can be heavily restrictive. In a real-world, millimeter-wave system, an array of power amplifiers may be flown or mobilized. On a flight, there is a finite amount of power that can be directed from flight systems and digital processing to amplification.

With large arrays or power requirements, there will always be a portion of the DC power that is not converted into RF power. All other power is turned into heat that increases the temperature of the transistors, substrate, and surrounding environment. With large arrays, temperature gradients can reduce the relative performance across the array or potentially cause damage to some of the pixels. At the IC level, increased temperatures can also decrease performance of single transistors and potentially cause failure of an entire MMIC. If a DC power budget exists, then a higher efficiency PA will produce more RF output power at a set DC power level and leave less total power to heat the system.

## 2.1-F OTHER POWER AMPLIFIER CLASSES

Much effort has gone into exploring other amplifier classes with a goal of extracting

the highest possible efficiency. The trade-off for higher efficiency is lower linearity or maximum output power.

Class AB, Class B, and Class C power amplifiers are variations of the Class A amplifer [23]. In order to reduce the DC power consumption in each transistor, the current is biased below  $I_{MAX}/2$ . For Classes B and C, the bias current is set at 0. For class C, the voltage is also biased below the Class A quiescent voltage. The resulting waveform for a class B amplifier is a half-wave amplifier. Transient waveforms for Classes AB and C also look similar to Class B's half-wave shape with a different fraction of time where the transistor is completely off. Where Class A amplifiers are a pure sinusoid and having a single tone spectrum, these amplifier classes with sharp off-on waveforms begin to develop strong coupling of energy into the third-order harmonics and higher. DC power is only consumed when both voltage and current are non-zero. The theoretical efficiency of each of these PA classes are greater than the class A amplifier.

Fig. 10. Load Lines for PA Classes A, AB, B, and C

Fig. 11. DC power is consumed during time periods when both voltages and currents are non-zero.

Class D, E, and F are "switch-mode" power amplifier classes. These amplifiers also trade off linearity for theoretical drain efficiencies near 100%. In order to achieve such efficiency, transistors must be operated well below the maximum frequency of oscillation so that output waveforms can utilize higher order harmonic terms for waveform shaping. These amplifier classes further reduce the time when both voltage and current are non-zero. Some switch-mode transient waveforms are shown:

Fig. 12. Desired Waveforms for an ideal switchmode PA

Theoretical maximum PAE is 100% for these amplifiers since there is no instantaneous power consumption.

## 2.1-G POWER AMPLIFIER TUNING

After deciding on a particular amplifier class and load line, the next step is to design a load impedance such that the voltages and currents actually swing to form that load line. The load line represents how the transistor's electron current source swings voltage and current. Electron current does not include displacement currents that "flow" in capacitors.

For example, the frame of reference for a load line in a common emitter HBT would be inside the parasitic capacitance on the collector. In this case, the intrinsic

device capacitance is not seen as part of the device, but rather a local tuning element. With a linear load line, the desired impedance seen at the current source is purely real. Given a load line's change in voltage ( $dV = V_{MAX} - V_{KNEE}$ ) and change in current ( $dI = I_{MAX} - 0$ ), the real load line resistance is just dV/dI.

For low frequency circuits, one can get the correct load line by applying a resistor with a value equal to the load line, since resistors are linear elements and have a fixed ratio of current to voltage. At high frequency, where interconnects within the circuit are not small electrically, microwave techniques and transmission line theory must be considered.

At high frequency the idea of a resistor, capacitor, inductor, and wire are fictional. Even small structures have picohenries and femptofarads of parasitic inductance and capacitance that can lead to dominant reactances at 220GHz. This makes modeling of every interconnect, transmission line, capacitor, and resistor a critical part of design.

The point of this discussion is that given all the imperfections in your tuning networks, two things must be accomplished by a tuning network connected to the transistor. First, at a minimum there must be reactive cancellation. To first order, this means cancellation the collector-base capacitance internal to the transistor for a common base HBT. In a tuning network, this could be done with a shunt inductance or with a pi section.

Fig. 13. LC and Pi network cancellation of common-base output capacitance

Second, the tuning network must provide the correct load line impedance to the electron current source of the transistor. This ensures that the trajectory (and linear relationship between voltage and current) travels in the correct area of the IV-plane. No matter the load line resistance required, the resulting amplifier will undoubtedly be connected to a larger system for test or system assembly. 50ohms is a typical system impedance, and a tuning network must transform that 50ohm system impedance to the real load line impedance desired at the electron current source.

The resistance of the load line that is required is affected by the number and size of transistors and other technology specifications. For example a transistor sized to handle a maximum current of 125mA and with  $V_{\text{KNEE}}$ =1V and  $V_{\text{BR}}$ =6V, will have a class A load line resistance of 40ohms. A transistor size twice as large should operate at the same current density and have a load line of 20ohms. This becomes important when considering the relative difficulty of doing impedance transformation from a 50ohm system impedance to 20 ohms compared to transforming to 40ohms.

## 2.1-H TRANSMISSION LINES

For Integrated Circuit (IC) design, several types of signal transmission lines are possi-

ble. The most common are non-inverted microstrip, inverted microstrip, and coplanar waveguide transmission lines. In addition to transmission line structures, integrated waveguides are often used in optics and metallic rectangular waveguides are used in packaging, long-distance transmission, and module-to-module interconnects.

Transmission line theory is an important factor when the distance that a signal must travel is a significant fraction of a wavelength (or larger) at that frequency.

Conversely, over short electrical distances, transients and reflected waves caused by transmission lines may be negligible.

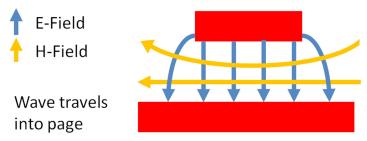

Transmission lines have a signal path and ground path with different potential energies [25]. The fundamental mode of propagation of a voltage-current wave (electro-magnetic wave) in a coaxial and parallel plate transmission line is a TEM (Transverse Electro Magnetic) mode with electric fields as shown below. The fundamental TEM mode is one of many possible solutions to the wave equation. With a TEM mode, a wave can propagate along the length of the transmission line with electric and magnetic fields being excited in the two orthogonal directions.

Fig. 14. TEM Transmission Lines: Infinite Parallel Plate and Coaxial Lines

In a microstrip transmission line, the ground may be considered an infinite

plate, but the signal line is of finite width. The fields of the fundamental microstrip mode are not uniform in one direction. But, in the central region of the line, field lines look similar to a TEM transmission line. Microstrip is considered a "quasi-TEM" transmission line.

Fig. 15. Quasi-TEM Transmission Lines: Microstrip Lines

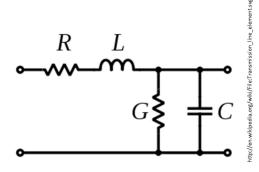

In any transmission line, the signal line provides a forward path for current flow and the ground provides a reference for voltages on the signal line and a return path for current flow. A standard model for a transmission line is a series inductance and a shunt capacitance for a lossless transmission line. A lossy transmission line model has the inductor and capacitor with an added series resistance and shunt conductance.

Fig. 16. Model of a transmission line

When a voltage wave is propagated in the transmission line, a corresponding

current wave is also excited. The ratio of voltage to current for each wave is constant and is called the characteristic impedance of the transmission line. In a lossless transmission line, the value of the characteristic impedance is only dependent on its energy storage components—inductance and capacitance per unit length. The equations for characteristic impedance are shown. A complex impedance means that there is loss per unit length in the transmission line.

$$Z_{o,Lossy} = \sqrt{\frac{R + j\omega L'}{G + j\omega C'}}$$

$Z_{o,Lossless} = \sqrt{\frac{L'}{C'}}$

Eq. 5. Characteristic Impedance for lossy and lossless transmission lines

The linear capacitance density (C') of the transmission line is computed like a parallel plate capacitor. The electrical permittivity of the dielectric is multiplied by the effective width of the capacitor and divided by the dielectric thickness. The effective width of the transmission line corresponds to the width where the electric fields originate and terminate on signal and ground, respectively. A wider microstrip line with a shorter distance to ground will have greater capacitance.

The linear inductance density (L') is a little more complicated to compute. A loop of current is formed as forward currents travel down a transmission line and return along the ground plane. The current loop generates a magnetic field through the center of the loop. Inductance is increased with a narrower signal line. Inductance is increased logarithmically for greater distance from the ground plane. Relative magnetic permeability of a typical dielectric is 1. Comparing two transmission lines in the

same material system, a narrower signal line with greater distance from the ground has greater inductance.

With this understanding, it makes sense that as a transmission line is narrowed, the inductance increases and the capacitance decreases, leading to greater characteristic impedance and a transmission line that behaves similarly to a series inductor. Conversely, a wider microstrip transmission line will lead to a smaller characteristic impedance and behavior similar to a shunt capacitor.

When a transmission line is terminated with a load impedance, the input impedance varies with the value of the load impedance, the transmission line electrical length, and the characteristic impedance of the transmission line. An equation for input impedance for a transmission line is shown below.

$$Z_{in}(l) = Z_0 \frac{Z_L + jZ_0 \tan(\beta l)}{Z_0 + jZ_L \tan(\beta l)}$$

Eq. 6. Input impedance of a loaded transmission line

#### 2.1-I IMPEDANCE MATCHING

Now is an important time to consider impedance matching. Impedance matching is relevant for two reasons. Impedance matching leads to the best possible outcome for transferring power from a generator to a load. Impedance matching with transmission lines can also reduce reflections and transients that can distort signals.

To begin thinking about the power transfer taking place in a simple circuit, consider a 100V AC voltage generator with a finite impedance of 50ohms. Now, con-

sider a load with a variable impedance that can be swept from being a short circuit, thru a 50ohm, to an open circuit. When the generator is attached to the short circuit load, the current is simply the generator voltage divided by the generator resistance or 2A. However, there is no voltage drop at the load, so no power is consumed or transferred to the load. When connected to an open circuit, there is 100V across the load, however no current flows and therefore no power.

As the impedance of the load is adjusted to the generator impedance, the total power transferred to the load reaches a maximum. When a 50ohm load is selected, 100ohms is seen at the voltage source and 1A of current flows through the circuit. 50V is dropped across the load for a total of 50W transferred to the load. While considering only these impedances is far short of a proof, it is useful in understanding how power is transferred from a generator with a finite impedance.

A similar idea holds for complex impedances. When impedances are complex conjugates, it is said that the impedances are matched. The maximum power is transferred from the generator to the load. This occurs for the same reasons described above. The real impedances are matched and allow maximum power transfer, while the conjugate values for reactance cancel at the interface where power transfer is being considered.

At the interface between two impedances, conservation of energy is in effect.

When a wave with RF power hits an interface, a reflected wave of power returns to the source. The incident wave is called a forward travelling wave and the reflected wave is a reverse wave. For a matched load, all the RF power is transferred to the

load and there is zero reflected energy. A transmitted wave with RF power equal to the forward wave continues through the interface. In the case where impedances are not matched, a reflected wave and a transmitted wave are generated. A greater difference in impedance at the interface corresponds to a larger amount of reflected power and less power transmission. Still the sum of reflected and transmitted power must be equal to the incident RF power at the interface. A reflection coefficient can be created to demonstrate the value of the reverse voltage waves relative to the forward voltage wave.

$$\Gamma = \frac{Z_L - Z_0}{Z_L + Z_0} \qquad T = 1 - \Gamma$$

Eq. 7. Reflection and Transmission Coefficient

When transmission lines and other more complex passive structures are introduced into a circuit design, the importance of impedance matching increases. Consider a generator, a transmission line, and a load. Mismatched impedances at the two interfaces can create a series of reflected voltage waves on the transmission line as shown below. Such reflections can add standing waves, delay, or otherwise distort the signal received at the load.

In cases where the source and generator impedances are the same, selection of the right transmission line characteristic impedance can be straight forward. Select RG=RL=Zo. When the impedances on generator and load are not the same, there are various techniques to transform the impedance so that one or both sides have a result-

ing impedance match and the power can be losslessly transferred from the generator to the load.

## 2.1-J IMPEDANCE TRANSFORMATION

There are several ways to transform impedances [25]. Generally, impedance transformation is a band-limited operation.

A quarter-wave transformer is one classic way to transform impedances. This uses the equation shown above (for transmission line input impedance) to match the generator impedance to an arbitrary real load impedance. When the transmission line is a quarter wavelength long at the desired frequency, the input impedance is reduced to sqrt(Zo\*ZL). If Zo is chosen such that this expression equals the impedance of the generator, then impedances will be matched. Full power transfer will occur between two different impedances through the chosen transmission line.

$$Z_{in}\left(\frac{\lambda}{4}\right) = \frac{{Z_o}^2}{Z_L}$$

Eq. 8. Quarter-wave transformer input impedance

Other matching networks can be chosen to transform impedances. Many are more easily visualized on a Smith Chart.

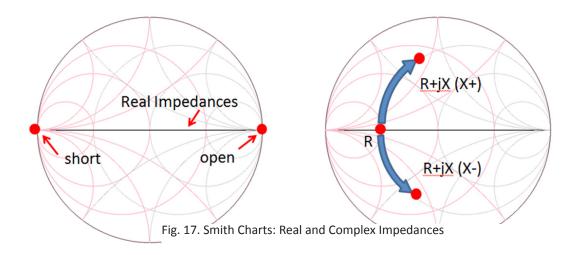

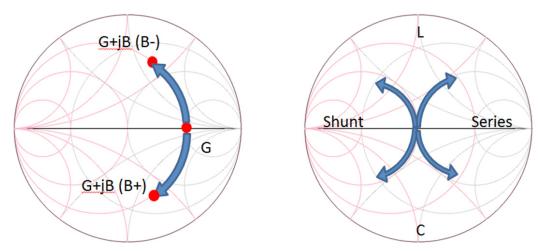

## 2.1-K USING SMITH CHARTS

Smith Charts are a useful way to visualize the complex impedance plane on the unit circle [25]. The x-axis represents the real component of an impedance normalized

to a system impedance. Commonly a 50ohm system is selected, so the center point of the unit circle that sits at a normalized impedance of 1, also represents the system impedance. At the coordinate (-1,0) a short circuit or 0 impedance is represented. At (1,0), the impedance is infinite or an open circuit.