## University of Ulm

# INVESTIGATIONS INTO MATRIX-ADDRESSABLE VCSEL ARRAYS

**Master Thesis**

by

Shamsul Arafin

**Faculty of Engineering Science Institute of Optoelectronics**

INSTITUTE OF

ulm university universität **UUIM**

# INVESTIGATIONS INTO MATRIX-ADDRESSABLE VCSEL ARRAYS

Master Thesis

Submitted by

Shamsul Arafin Matriculation No. 611852 Communication Technology <u>March, 2008</u>

Presented to

**Institute of Optoelectronics**

Examiner: Prof. Dr. -Ing. K.J. Ebeling Supervisor: M.Sc. Abdel-Satter Gadallah

I hereby declare that I have completed this work independently and using only the aids included. Any passages that have been extracted or cited from other sources have been referenced appropriately.

Ulm, March 31, 2008.

(Shamsul Arafin)

This work is dedicated tomy loving parents and my youngest sister. Their love and selfless support made this work possible.

## Acknowledgements

First, all praise to God, the most Gracious and most Merciful, whose help and guidance is ever dominating throughout my life.

I would like to express my sincere gratitude to Abdel Satter Gadallah, M.Sc., for being my advisor. Throughout this work I got the invaluable support, perfect guidance, useful suggestions, magnificent cooperation, continuous support, effective advice, proper supervision and consistent encouragement from him. I am really grateful to him for his great assistance during the thesis period.

I was fortunate to be supervised by Dr. -Ing Rainer Michalzik with his gentle guidance, strong encouragement and great motivation.

I am deeply indebted to Prof. Dr. -Ing. K.J. Ebeling granting me the opportunity to do my M.Sc. thesis in his department.

I specially thank her whose contribution in this work was unforgettable and whose helping attitude was admirable, whose guidance was very spontaneous. She is none but Dipl. - Ing. Andrea Kroner.

I would like to convey my heartfelt thanks to Dipl.-Ing. Hendrik Roscher, Dipl.-Ing. Ihab Kardosh, Dipl.-Ing. Wolfgang Schwarz, Sussane Menzel and all other members of the Optoelectronics Department for their continuous support during the thesis period.

I am also grateful to Dr. Katrin Reimer and Prof.Dr.-Ing.Hermann Schumacher for organizing the necessary financial support during these six months.

I would also like to remember his name whose presence made me active and jubilant during the thesis period. He is my colleague and friend, Ahmed-Al Samaneh.

Finally, I appreciate my family's support and love in the two years' M.Sc. program.

## Contents

| 1 | Introduction 1     |                                          |  |  |  |  |  |

|---|--------------------|------------------------------------------|--|--|--|--|--|

|   | 1.1                | Motivation                               |  |  |  |  |  |

|   | 1.2                | Thesis Outline   2                       |  |  |  |  |  |

| 2 | VCS                | SEL Modeling 3                           |  |  |  |  |  |

|   | 2.1                | Introduction                             |  |  |  |  |  |

|   | 2.2                | Device Structure                         |  |  |  |  |  |

|   | 2.3                | Band Diagram                             |  |  |  |  |  |

|   | 2.4                | Refractive Index                         |  |  |  |  |  |

|   | 2.5                | Standing-Wave Pattern                    |  |  |  |  |  |

|   | 2.6                | Reflectivity Spectrum                    |  |  |  |  |  |

|   | 2.7                | Summary                                  |  |  |  |  |  |

| 3 | 2-D VCSEL Arrays 9 |                                          |  |  |  |  |  |

|   | 3.1                | Introduction 9                           |  |  |  |  |  |

|   | 3.2                | Independent Addressing                   |  |  |  |  |  |

|   |                    | 3.2.1 Advantages                         |  |  |  |  |  |

|   |                    | 3.2.2 Disadvantages                      |  |  |  |  |  |

|   | 3.3                | Matrix Addressing                        |  |  |  |  |  |

|   |                    | 3.3.1 Advantages                         |  |  |  |  |  |

|   |                    | 3.3.2 Disadvantages                      |  |  |  |  |  |

|   | 3.4                | Strategy of MA Array Fabrication         |  |  |  |  |  |

|   | 3.5                | Summary                                  |  |  |  |  |  |

| 4 | Mag                | k Design for Matrix Addressable Array 18 |  |  |  |  |  |

| - | 4.1                | Introduction                             |  |  |  |  |  |

|   | 4.1                | Mask for Mesa Etching                    |  |  |  |  |  |

|   | 4.2<br>4.3         | Mask for N-Contact Bondpad               |  |  |  |  |  |

|   | 4.3<br>4.4         | Mask for Column Isolation                |  |  |  |  |  |

|   | 4.4<br>4.5         | Mask for P-Contact Ring                  |  |  |  |  |  |

|   | 4.5<br>4.6         | Mask for Polyimide-1                     |  |  |  |  |  |

|   | <b>H</b> .U        | wask 101 1 01ymuue-1                     |  |  |  |  |  |

|   | 4.7                                     | Mask for Polyimide-2                                    | 26 |  |  |  |

|---|-----------------------------------------|---------------------------------------------------------|----|--|--|--|

|   | 4.8                                     | Mask for Polyimide-Safety                               | 27 |  |  |  |

|   | 4.9                                     | Mask for P-Contact Bondpad                              | 28 |  |  |  |

|   | 4.10                                    | Summary                                                 | 30 |  |  |  |

| 5 | Matrix Addressable Array Fabrication 31 |                                                         |    |  |  |  |

|   | 5.1                                     | Introduction                                            | 31 |  |  |  |

|   | 5.2                                     | Mesa Formation                                          | 31 |  |  |  |

|   | 5.3                                     | Selective Lateral Oxidation                             |    |  |  |  |

|   |                                         | 5.3.1 Oxidation Rate Dependencies                       | 35 |  |  |  |

|   |                                         | 5.3.2 Electrical and Optical Confinement                | 35 |  |  |  |

|   | 5.4                                     | Column Isolation                                        | 36 |  |  |  |

|   |                                         | 5.4.1 Electrochemical Reaction                          | 38 |  |  |  |

|   | 5.5                                     | N-Contact                                               | 39 |  |  |  |

|   | 5.6                                     | P-Contact Ring                                          | 41 |  |  |  |

|   | 5.7                                     | Polyimide Step                                          | 42 |  |  |  |

|   | 5.8                                     | P-Row Contact                                           | 48 |  |  |  |

|   | 5.9                                     | Summary                                                 | 49 |  |  |  |

| 6 | Matı                                    | rix Addressable Array Characterization                  | 50 |  |  |  |

|   | 6.1                                     | Introduction                                            | 50 |  |  |  |

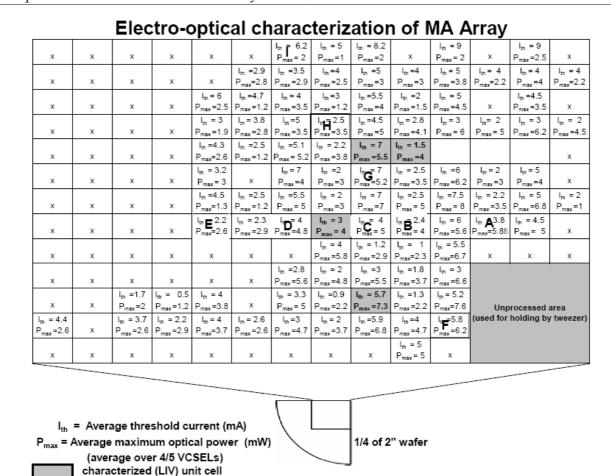

|   | 6.2                                     | Electro-optical Characterization                        | 50 |  |  |  |

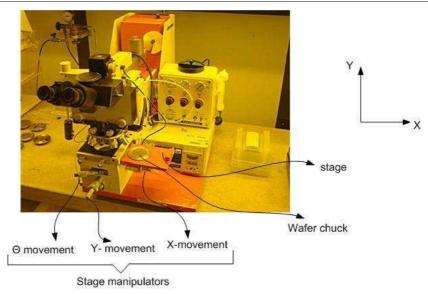

|   |                                         | 6.2.1 Experimental Setup                                | 51 |  |  |  |

|   |                                         | 6.2.2 Classification of Unit Cell                       | 51 |  |  |  |

|   | 6.3                                     | Important Results Depending on the LIV Characterization | 53 |  |  |  |

|   |                                         | 6.3.1 Oxide Aperture Shape                              | 60 |  |  |  |

|   |                                         | 6.3.2 Calculation of $D_a$                              | 60 |  |  |  |

|   | 6.4                                     | Calculation of Sheet Resistance                         | 60 |  |  |  |

|   | 6.5                                     | Processed Wafer Characterization                        | 61 |  |  |  |

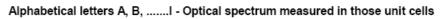

|   | 6.6                                     | Optical Spectra                                         | 62 |  |  |  |

|   | 6.7                                     | Summary                                                 | 64 |  |  |  |

| Α | Sim                                     | ulation Script                                          | 65 |  |  |  |

| В | Star                                    | iding Wave Pattern of E-Field Amplitude Calculation     | 68 |  |  |  |

| С | Refl                                    | ectivity Spectrum Calculation                           | 69 |  |  |  |

| D | Mas                                     | k Layout Using AutoCAD                                  | 71 |  |  |  |

| Е | Instructions for Cleanroom              |                                                         |    |  |  |  |

| F | Process Overview                        |                                                         |    |  |  |  |

| G Epitaxial Structures | 109 |

|------------------------|-----|

| Bibliography           | 111 |

# Chapter

## Introduction

#### 1.1 Motivation

Vertical-cavity surface-emitting laser (VCSEL) is one type of special promising laser which can be superior by its excellent performance among all existing semiconductor lasers at the present time. For the last few years, this has become the most attractive device for the fabrication of large two-dimensional (2-D) arrays of compact coherent optical sources due to number of performance and manufacturing advantages, e.g. low threshold current of 8.7  $\mu$ A [1], low threshold voltage of 1.33 V [2], high packing density [3], higher power conversion efficiency at 50% [4], on-wafer testing, single mode operation and so on. These 2-D arrays are of great potential importance for various optical interconnection schemes [5], 2-D optical scanners [6] and display technology. All applications mentioned here require convenient optical or electronic addressing technique to communicate each VCSEL on-chip.

There are different methods available for addressing the VCSELs in the 2-D array. Among them, matrix addressing is one method of interest by which each VCSEL in an array can be electronically addressed and at the same time much larger array can be fabricated without having any problem since it requires less number of metal connections at the edges of the chip, unlike its individual addressing counterpart which requires large number of metal connections. The main drawback of 2-D matrix addressable array is that the devices fabricated in the array share contact-lines for which some control is lost over which devices can be turned on at a given time but that can be overcome by well known multiplexing techniques.

Recently this matrix addressable array has got great importance due to plenty of attractive applications like confocal microscopy [7], non-mechanical particle movement by optical tweezers [8, 9], and video imaging where large number of parallel optical sources with desired beam profile are needed. Matrix addressable VCSEL array can be the strong candidate to be implemented in these demanding applications since matrix addressing technique is capable of producing larger and denser 2-D array easily than independent

#### Chapter: 1 Introduction

addressing. Here comes the supremacy of matrix addressing over independent addressing technique. However, by this time there have been some works done on this matrix addressing by the research community. Von Lehman *et al.* [10] showed the way to fabricate matrix addressing 32 x 32 array for the first time in 1991 and then Morgan *et al.* [11] fabricated 10 x 10 array in 1994 and then finally Choquette *et al.* [12] in 2002 also successfully fabricated this matrix addressable 64 x 64 array where they monolithically integrated the photodetectors.

The present thesis is devoted to the investigation into matrix addressable VCSEL array fabrication and the characterization afterwards. The entire work is carried out on the sample designed for the standard wavelength regime around 850 nm, grown by solid source molecular beam epitaxy (MBE) on undoped GaAs substrate. In this thesis work, at first one prototype mask is designed for matrix addressable 4 x 4 arrays which is smaller but denser because the pitch size is 125  $\mu$ m. Then using this mask, eight lithographic steps associated with other necessary works e.g. oxidation of AlAs layer, wet chemical etching, metallization, lift-off etc. are performed for fabricating the arrays, followed by the characterization of the devices which includes measurement of light-current-voltage curves, uniformity of the arrays and so on.

#### 1.2 Thesis Outline

In chapter 2, one typical VCSEL fabricated in the matrix addressable 4 x 4 array is numerically modeled depending on the sample recipe file where the description of device epitaxial layers was written. In chapter 3, some fundamental principles of matrix addressable arrays making the comparison with other addressing techniques have been summarized. At the same time the design approach of this work has been depicted by some schematic diagrams along with useful explanations. In chapter 4, the full description of the mask layout has been provided from where the design approach in this work gets revealed. In chapter 5, the experimental results and important relevant comments based on the device fabrication procedures have been described. The characterization and the measurements of the devices fabricated in the array are illustrated then in chapter 6. The thesis is then concluded by chapter 7 where the summary of this work and recommendations for future work contain.

Appendix A includes the source code used in SimWindows-V.1.5.0 to obtain the band diagram of the unbiased and biased VCSEL structure and the refractive index profile as well. Appendix B and C provide the mathematical equations necessary for calculating the standing-wave pattern of the electric field and the reflectivity spectrum of the full VCSEL structure respectively. Appendix D contains some handy tips and rules-regulations for drawing the mask layout in AutoCAD. All the necessary instructions need to be known in advance for working with the sophisticated devices in the cleanroom is attached in Appendix E. Appendix F provides all the process sequences maintained while fabricating the arrays. Finally Appendix G summarizes the epitaxial layer structures of the sample.

# Chapter 2

# **VCSEL** Modeling

#### 2.1 Introduction

VCSEL modeling refers to the numerical analysis of device structure. In other words, the analysis of important characteristics of VCSEL depending on the materials grown by MBE machine is termed as VCSEL modeling. In particular, this modeling includes the band diagram, band diagram with biasing, refractive index profile, standing-wave of electric field intensity pattern and reflectivity spectrum of the full VCSEL structure. Though these are not only the modeling parameters, but these parameters are enough to get a general idea of the internal structure of the device.

In this chapter, the characterization parameters extracted from the information of MBEgrown sample (so-called recipe file which contains the specifications of all epitaxial layers) will be reviewed which are simulated in different software (e.g. MATLAB, SimWindows, REFLEX) and the results are discussed here as well.

#### 2.2 Device Structure

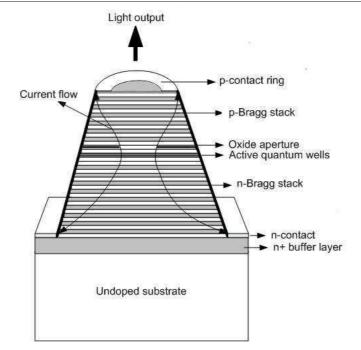

A schematic drawing illustrating the cross-section of a VCSEL fabricated in the array is provided in Fig. 2.1. All the epitaxial layers were grown on a 500 µm semi-insulating GaAs substrate. The VCSEL contains three quantum wells made by GaAs material (having a low bandgap) each of which is 8 nm in thickness separated by barrier layers made by AlGaAs material (having a high bandgap) each of which is 10 nm in thickness to form the heterostructure. It is obvious that the VCSEL designed in this configuration will be for top emitting since the substrate material (GaAs) is absorptive. This also leads to grow higher number of n-DBR (Distributed Bragg Reflector) mirror pairs than p-DBR mirror pairs in order to get a much higher combined reflection from the bottom n-mirror side so that light can emit from the top side. A Bragg mirror pair consists of two layers with high and low refractive indices where each layer has one quarter of wavelength thickness. By

Figure 2.1: Schematic cross-section of VCSEL structure.

repeating these two layers in an alternating manner, constructive interference is achieved which ultimately increases the total reflectivity of the structure. In particular, these two layers are grown in this design with a graded interface just by varying the Al content; as a result, electrical resistance gets reduced. In this design the active region, i.e. three quantum wells along with barrier layers, is sandwiched by top 23 pairs of C-doped (p-type) mirror stacks and bottom 38 pairs of Si-doped (n-type) mirror stacks. Close to the active region, AlAs layer (i.e. high Al content) of 32 nm is grown to form the native oxide for current and carrier confinement. It is noteworthy that there is also a 2  $\mu$ m highly doped n<sup>+</sup> buffer layer just at the top of the substrate is grown on which the n-contact will be photolithographically defined. Furthermore, a highly doped of some ten nm thick p<sup>+</sup> layer was also grown as topmost layer to facilitate the electrical conduction where the p-contact will be formed. In addition, the epitaxial layer structures of the sample used in this work is summarized in Appendix G.

#### 2.3 Band Diagram

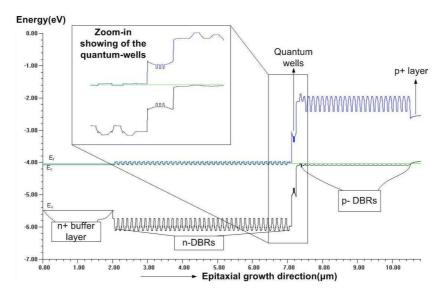

Fig. 2.2 shows the band diagram of the full VCSEL structure without any biasing, i.e. the Fermi level of n-region will remain completely aligned with p-region. The zoom-in showing of the microcavity active region is also provided in Fig. 2.2 where three QWs are located. But Fermi level misalignment will take place as soon as biasing is applied in the device which is shown in Fig. 2.3. This non-equilibrium condition resulting from the forward biasing can be depicted by so-called quasi-Fermi levels. Now the electrons will

2.4 Refractive Index

be allowed to go into the QW from the n-region and holes from the p-region ultimately lead to stimulated action. These band diagrams with and without biasing are obtained by using the semiconductor simulation program SimWindows-V.1.5.0 (cf. appendix A).

Figure 2.2: Band diagram of the full unbiased VCSEL structure.

Figure 2.3: Band diagram of the full VCSEL structure with 1 V forward bias.

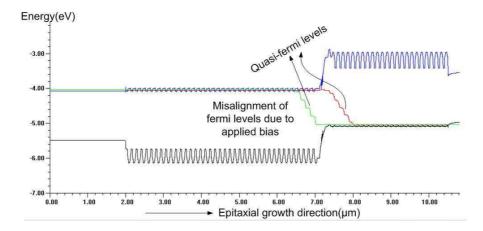

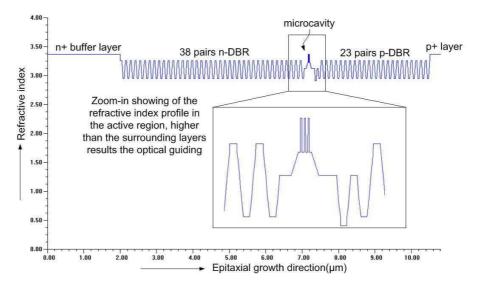

## 2.4 Refractive Index

The refractive index profile of the full VCSEL structure is shown in Fig. 2.4 where the active region with higher refractive index is surrounded by the region with low refractive index results the optical guiding. It is seen that in the Bragg reflectors there is no sharp interface, i.e. jumping from high refractive index to low refractive index directly; continuous grading

Chapter: 2 VCSEL Modeling

has been introduced instead, in order to reduce the potential barrier and thus the electrical resistance. This refractive index profile of the device can be calculated by using the same program SimWindows (cf. appendix A).

Figure 2.4: Refractive index profile of the full VCSEL structure.

## 2.5 Standing-Wave Pattern

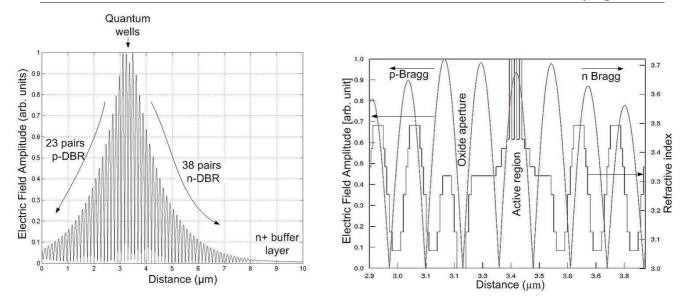

Fig. 2.5(a) shows the standing-wave pattern of the electric field intensity of the full VCSEL structure that contains three active GaAs QWs in the center, 38 pairs bottom Bragg reflector, 23 pairs top Bragg reflector including n<sup>+</sup> buffer layer. It is obvious that there is pronounced resonating action produced in the device since the field amplitude is much higher at the active region due to higher reflectivities at the mirrors. On the other hand, the field amplitude gradually decays at both mirror side. Fig. 2.5(b) shows a close-up view of the same standing-wave pattern at the active region including the refractive index profile where we can see that the active region has been placed in such a position of the device where electric field intensity peak appears which necessitates the  $\lambda$ -length cavity. These two figures are obtained by using the one-dimensional simulation program REFLEX where the material recipe file (.INR file) was given as input. The necessary equations used to simulate this program are attached in Appendix B.

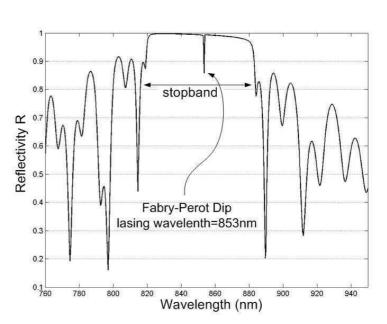

## 2.6 Reflectivity Spectrum

The reflectivity spectrum calculated from full VCSEL structure gives very important information about the lasing wavelength of the device. Fig. 2.6 shows the spectrum where we see the spectral width of the high-reflectivity stop-band which can be controlled by the materials employed. At the center of the stop-band we also see a dip, having a lower

(a) Standing-wave pattern of the electric field of a full VCSEL (b) Standing-wave pattern close-up of the active region includstructure. ing the refractive index profile.

Figure 2.5: Standing-wave pattern of VCSEL.

reflectivity, indicates the resonance wavelength just like а Fabry-Perot res-Though the emisonator. sion wavelength designed for this sample was 850 nm which is standard for high speed data communication but due to many reasons, it is difficult to achieve this exact wave-This reflectivity length. spectrum was numerically calculated by transfer matrix method using MAT-LAB. The necessary equations implemented in the source code are given in Appendix C.

Figure 2.6: Reflectivity spectrum of the full VCSEL structure designed for emission wavelength 850 nm. The reflectivity dip at the centre signifies the resonance wavelength.

#### Just after the epitaxial

growth, the measurement of reflectivity spectrum is extremely helpful because it tells about the emission wavelength to be obtained from the sample. In most practical cases, the emission wavelength at the center of the sample is not same with the periphery of the Chapter: 2 VCSEL Modeling

sample; some deviation was noticed for this sample.

### 2.7 Summary

In this chapter, the important modeling parameters of VCSEL have been presented based on the epitaxial layers. The importance and the significance of these parameters are also briefly discussed in this chapter. In addition, the simulated outputs for these parameters obtained by using the different software are inserted here.

# Chapter 3

## 2-D VCSEL Arrays

### 3.1 Introduction

Producing the VCSELs as an array in single chip containing thousands of VCSELs is not difficult at all. The technology of 1-D and 2-D VCSEL array fabrication in the last decade have advanced rapidly just because of the ease of producing 2-D VCSEL array. Why 2-D VCSEL array is important? 2-D VCSEL array has plenty of major applications; optical interconnection is one of the most important applications, beside the parallel data processing over optical fiber for short distance communication, optical data storage and so on. In fact, for short distance data transmission where the number of coupled elements will be needed, VCSEL has become the first choice as a device there nowadays. But the problem arises when the time comes to communicate them, i.e. each of the VCSEL in 2-D VCSEL array need to be addressed. So far work has been carried out on four different addressing schemes. Those are as follows:

- Independent addressing

- Matrix addressing

- Direct addressing

- Optical addressing

Out of these different addressing schemes the first two methods have been demonstrated by many people many times on many applications.

In this chapter, the principles of different addressing techniques for 2-D VCSEL array along with their merits and demerits have been summarized. In addition to that, the strategies of fabricating the matrix addressable arrays in this thesis work is discussed including some schematic diagrams from which one can easily get some feelings of the whole work.

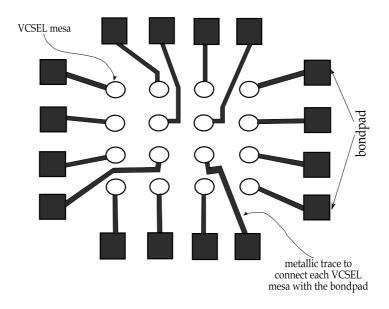

## 3.2 Independent Addressing

This is the most straightforward way of addressing the VCSEL in an array which is schematically illustrated in Fig. 3.1. In fact, this type of addressing needs a p-contact at the top of the devices. That's why the metallic traces have to be defined for each VCSEL which will connect the anode of the device to the bondpad located at the edge of the chip. On the other hand, the bottom doped substrate (ground contact as common) can be used for n-contact of all devices. Array of this kind has been demonstrated by Von Lehman *et al.* [13] in 1991 and Giaretta *et al.* [14] in 1997 and Hendrik Roscher [15] in 2002 and so on.

Figure 3.1: Schematic diagram of metallization pattern for 4 x 4 individually addressed array.

#### 3.2.1 Advantages

- 1. Each of the VCSEL can be operated independently, i.e. any single device, any combination of the device and all of the devices can be turned on at the same time without any additional circuitry.

- 2. 2-D array fabrication is comparatively easier.

#### 3.2.2 Disadvantages

The array size will be limited due to the complicacy created by many bondpads and metal traces. Because for each VCSEL there will be one dedicated metallic trace and bondpad should be defined. In a generalizing way, for M x N array, we will need M x N metal lines and the same amount of bondpads, obviously a big number which require a lot of space in the chip.

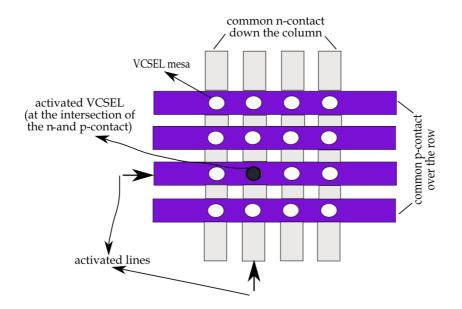

#### 3.3 Matrix Addressing

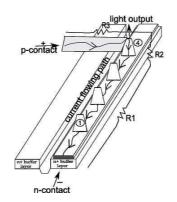

This is another promising method for addressing the VCSEL in the 2-D array. This type of addressing is little bit complicated because each device will not have its own independent metal line and bondpad connection to be turned on, but common cathode and common anode connection will be defined in column and row for addressing the device, instead. Fig. 3.2 demonstrates the schematic diagram of the typical metallization pattern of 4 x 4 matrix addressing. In fact, a VCSEL located at the intersection of the n-metallization line and p-metallization line will be turned on in this method. In most practical cases, the p-contacts of the devices over a row and the n-contacts of devices down a column are connected together. Then by applying a positive voltage to the desired row and an equal negative voltage to the column, the VCSEL at the intersection would be turned on. Array of this kind has been demonstrated by Von Lehman *et al.* [10] in 1991, Morgan *et al.* [11] in 1994 and Choquette *et al.* [12] in 2002 and so on.

Figure 3.2: Schematic diagram of metallization pattern for 4 x 4 matrix addressed array.

#### 3.3.1 Advantages

1. It is already understood that the main problematic issue in the 2-D VCSEL array is that the number of metal traces and bondpads to communicate the single or multiple VCSELs. The larger the array, i.e. the higher number of VCSELs, the higher the complicacy because more metal lines and bondpads would be needed then which can be realized by the independent addressing. Matrix addressing in this case shows a magnificent performance by reducing the number of metallic traces and bondpads. In a generalizing way, for M x N array, we will need M + N metal

#### Chapter: 3 2-D VCSEL Arrays

lines and the same amount of bondpads, obviously much less than the independent addressing which saves a lot of space in the chip lead us to fabricate a large array (e.g. 32 x 32 array). To fabricate 32 x 32 array, only 32 + 32=64 metal lines are required in matrix-addressable array whereas  $32 \times 32=1024$  metal lines are required in individually addressable array, i.e. 960 would be needed additionally - really a lot. This is the supremacy of Matrix-Addressing method over Independent-Addressing.

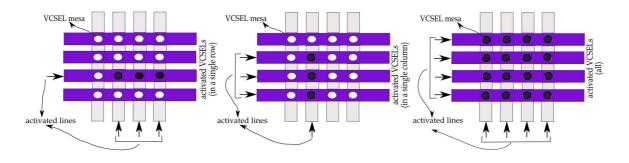

Figure 3.3: Different schemes of Matrix Addressing technique to address the devices. Any number of devices in a single row (the leftmost), in a single column (at the middle) and all the devices at a time (the rightmost) can be turned on.

Figure 3.4: Limitation of matrix addressing technique where we can see that random multi-element addressing over the array is not possible.

2. Chip size can be minimized since less number of bondpads will be required.

#### 3.3.2 Disadvantages

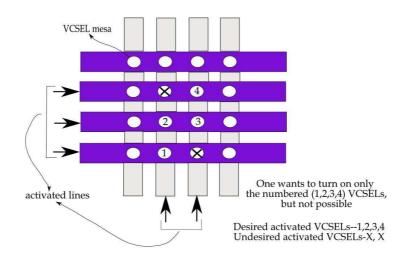

1. The main disadvantage in this type of addressing method is that the lack of controlling the VCSELs in the array. Matrix addressing allows only the following schemes in the array:

- Single VCSEL (Fig. 3.2)

- Any number of VCSELs in a single row or in a single column (Fig. 3.3)

- All of the VCSELs at a time.(Fig. 3.3)

So, it is clear that random multi-element addressing is not possible here as shown in Fig. 3.4. But some additional circuitry (e.g. multiplexer) can help to operate the VCSEL array randomly which involves cost and effort and may be complicacy will get increased. For example, any character is formed by multiplexing the display

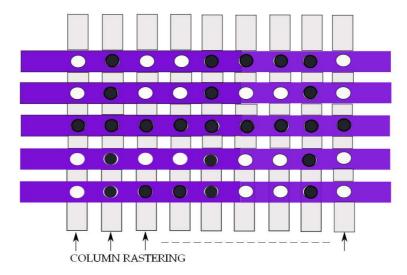

Figure 3.5: *Photograph of the symbol '\$'(rotated by -90<sup>0</sup>) produced by column-row rastering the laser array.*

columns with the scanning logic. Each of the nine columns (shown in Fig. 3.5) are selected individually while placing the data in the character generator for that column on the rows. This process is repeated until all columns of the matrix have been activated [11]. In this way, matrix addressing overcomes the limitation mentioned earlier.

- 2. 2-D array fabrication is not so easy.

- 3. The p-contacts of devices along a row and the n-contacts of devices down a column are connected together. Then by applying a positive voltage to the desired row and an equal negative voltage to the column, the VCSEL at the intersection would be turned on. Other devices along the row and down the column would see only the half voltage of this device. It is necessary to make sure that the threshold voltage of all devices fabricated in the array has to be less than half of the desired operating voltage [16].

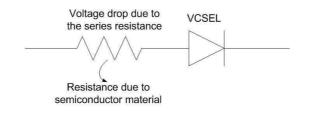

4. One of the most challenging issues in MA<sup>1</sup> VCSEL arrays is the larger effective series resistance [12].

### 3.4 Strategy of MA Array Fabrication

How the sample will be processed and what strategy (the process sequences) will be followed for fabricating the MA VCSEL array in an optimized way, the rough blueprint of that was determined in advance especially before drawing the mask. Of course, it will help us to understand and to develop some feelings about the present work. The following discussion provides the information of the planning regarding the processing steps, starting from the mesa formation just after getting the sample till the last step of the metal contact.

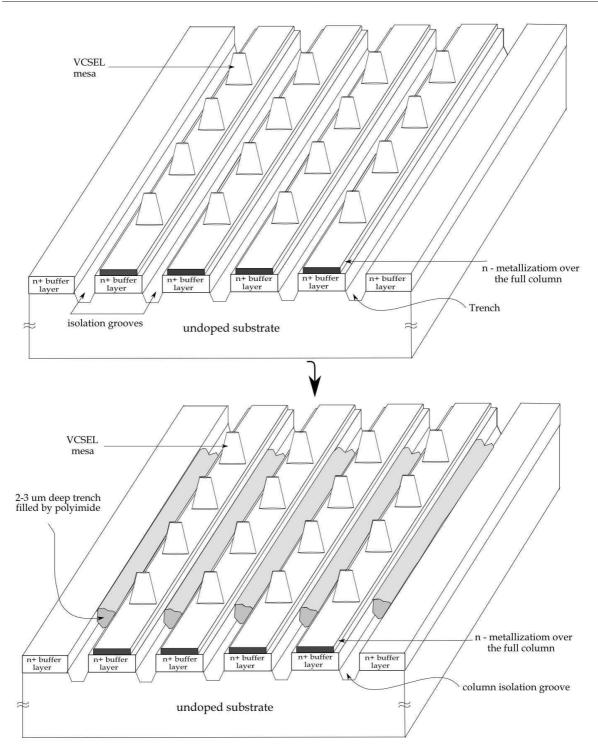

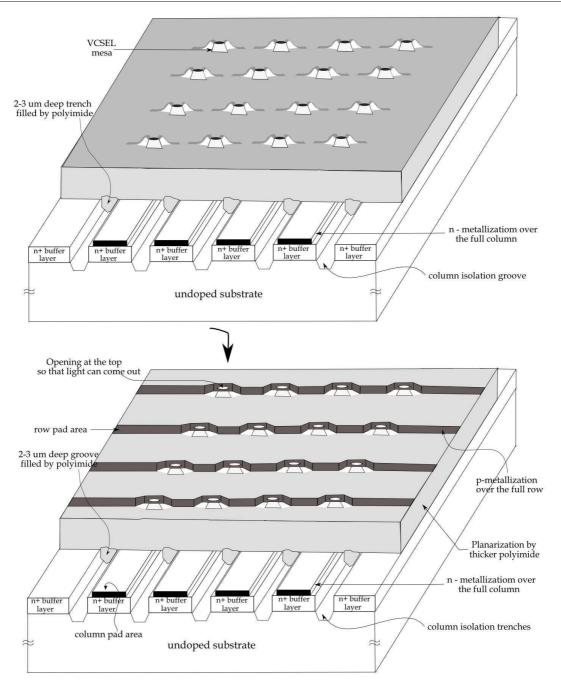

According to the proposed method, at first, the sample will be etched down till n<sup>+</sup> buffer layer (8-9 µm deep) resulting the mesa of the devices as indicated in Fig. 3.6. Then those devices can be selectively oxidized for current and optical confinement. Later, the sample should be metallized selectively which will serve as common n-contact so-called column pad area. In fact, the n-contact metallization should be done down the full column (except the circular device region) on top of the  $n^+$  buffer layer. This process will be followed by the etching for the column isolation grooves by removing the n<sup>+</sup> buffer layer which will electrically isolate the columns as displayed in the upper part of Fig. 3.6. Now the passivation between n- and p-contacts and planarization of the sample surface should be made by the polyimide. In carrying out the planaraization of the sample, the trenches so-called column isolation grooves defined by etching (mentioned earlier) should be filledup at first as shown in the lower part of Fig. 3.6. Then the rest of the region should be planarized by the thicker polyimide which resulted from the deep 8-9 µm mesa etching as indicated in the upper part of Fig. 3.7. Lastly comes the metallization for p-contact. For that, row pad areas have to be formed which will act as common p-contacts of the devices located in one row as illustrated in the lower part of Fig. 3.7. Note that, the p-contact metallization should be done over the full row except the small circular region where the devices are located so that light can escape from the top of the device since the design is based on top emission.

<sup>&</sup>lt;sup>1</sup>MA = Matrix Addressable

Figure 3.6: Illustration showing the fabrication procedure of  $4 \times 4$  VCSEL arrays where the formation of the mesa, column pad area for common n-contact of the devices, isolation trenches in the above figure and then the way of filling-up the trenches by the polyimide in the lower figure.

#### Chapter: 3 2-D VCSEL Arrays

Figure 3.7: Illustration showing the fabrication procedure of  $4 \times 4 \text{ VCSEL}$  arrays where the selective planarization of the sample surface having 8-9µm deep etched region by the thicker polyimide in the above figure and the formation of row pad area for common p-contact of the devices in the lower figure.

## 3.5 Summary

In this chapter, the important discussion concerning the matrix addressable array and its supremacy over other addressing techniques have been presented with some illustrations. Besides, this chapter will be followed by the 'Mask Design' where the design approaches will be discussed directly assuming that one has already the understanding about the basic theories and the design approach of this thesis work. Moreover, this chapter will be very helpful to follow the ideas, views and comments introduced in the next chapter. Finally, a very brief summary of the basic steps for processing of the MA array including some schematic diagrams are outlined here.

# Chapter 4

# Mask Design for Matrix Addressable Array

## 4.1 Introduction

In designing the matrix addressable VCSEL arrays, the first and the most important task is the mask design which needs high accuracy especially in dimension of the structures. The mask contains the high resolution transparent-opaque images on one side of the surface which is required to get a certain pattern on the sample. In particular, the important factors (e.g. lateral undercut of wet chemical etching), special parameters of different photolithographic steps (e.g. alignment in mask aligner) need to be considered in the mask design in order to get a good yield of the devices. So, the mask design plays an important role in fabricating the devices successfully.

Traditionally, for the layout of the mask the computer aided design tool, AutoCAD<sup>2</sup> was used. AutoCAD produces the data format .DWG file which is converted into GDSII file by the manufacturer company to write the structure on Quartz glass<sup>3</sup> by E-beam lithography.

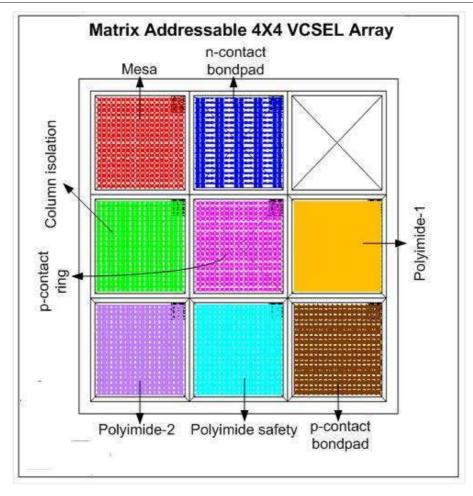

Fig. 4.1 shows the entire layout of the mask drawn in the AutoCAD. There are eight blocks in the layout which implies that eight or may be more than eight photolithographic steps are necessary to fabricate the matrix addressable VCSEL arrays. The dimension of each block is 1.55 cm by 1.55 cm which is sufficient to cover the half of the quarter of 2" wafer. Or in other words, half of the quarter of 2" wafer can be processed by each block of the mask. In addition, the name of each block in the layout will tell the purpose of corresponding block which has to be carried out in the fabrication. Moreover, the blocks of the layout were designed to be usable with both type of photoresist, positive and negative, depending on the requirements. The details of the design can be viewed by zooming in

<sup>&</sup>lt;sup>2</sup>Some handy tips of drawing the mask layout efficiently in AutoCAD are given in Appendix D which might be helpful for the beginners.

<sup>&</sup>lt;sup>3</sup>Quartz is the second most common mineral in the Earth's continental crust. It is made up of a lattice of silica SiO<sub>2</sub> tetrahedra. Source:-http://en.wikipedia.org/wiki/Quartz

Figure 4.1: Entire layout of the mask drawn in AutoCAD, there are eight different blocks defined for eight different photlolithographic steps for processing the Matrix Addressable 4 x 4 VCSEL Array.

on the typical three-inch mask as displayed in Fig. 4.1.

In this chapter, the description of the mask design along with the necessary explanations, the relevant issues taken into account, the dimensions of the structures drawn in the layout are outlined including the figures. It should finally be noted that this was a prototype photomask that was designed to conduct the processing which can be the harbinger of next work.

#### 4.2 Mask for Mesa Etching

The name of this block itself is telling that the mesa of VCSEL arrays will be formed by etching (e.g. wet chemical etching) to expose the AlAs layer for oxidation which is  $3/4 \,\mu m$  in depth - quite conventional, but in this step we etched down till n<sup>+</sup> buffer layer instead of

#### Chapter: 4 Mask Design for Matrix Addressable Array

just AlAs layer to avoid the difficulty. Difficulty in this sense that the different etch depths will create some problem in getting the surface planarized afterwards. For example, if we would make the etching up to AlAs layer in this step and then anyway we have to etch till  $n^+$  buffer layer and then again etching is necessary to isolate the columns resulting three different etch depths.

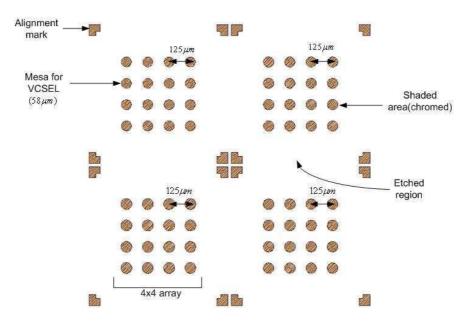

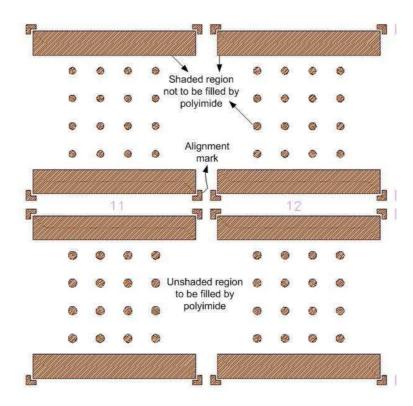

The four VCSEL arrays of each having  $4 \times 4$  structures with different mesa diameters are shown in Fig. 4.2. Each  $4 \times 4$  array will be called as one unit cell from now. However, the advantage of etching down till n<sup>+</sup> buffer layer is that the sample becomes completely ready for oxidation and at the same time for the latter step, n-contact metallization without any further processing, e.g. wet chemical etching. Besides, there are four alignment marks at the corner of each array as well, which will help to align the structures with the structures defined already in the sample by the earlier photolithographic step. The shaded part as displayed in Fig. 4.2 indicates that the region covered with chrome which will block the UV light during UV exposure. So, the shaded region will be protected by the resist after development if positive resist is used.

Figure 4.2: Close-up showing of the block, MESA, in the mask layout.

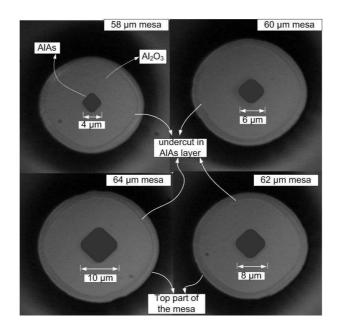

In this mask the four different circles distinguished by the dimensions, i.e.  $58 \mu m$ ,  $60 \mu m$ ,  $62 \mu m$  and  $64 \mu m$  in four different regions separated by alignment markers are drawn. The circles of these different dimensions will give the active diameters  $4 \mu m$ ,  $6 \mu m$ ,  $8 \mu m$  and  $10 \mu m$  respectively after oxidation which are necessary for the following reasons:

- 1. Standard for data communication used in short distance fiber-optical links.

- 2. Single mode<sup>4</sup>

<sup>&</sup>lt;sup>4</sup>Yang et al. reports that the 10 µm square laser with the special type of epi-layer structure operates in a

#### 4.3 Mask for N-Contact Bondpad

Figure 4.3: Explanation of the dimension used in calculating the mesa circle diameter.

- 3. Gaussian beam allows simpler optics.

- 4. Less heating problem since less threshold current is necessary.

- 5. Excellent device reliability.

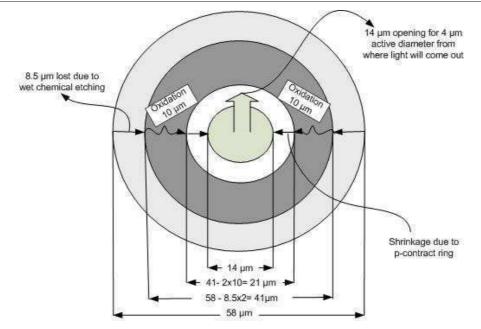

Why the circle, having the diameter  $58 \,\mu\text{m}$ , is drawn in the mask to get the active diameter  $4 \,\mu\text{m}$ ? There are some factors which were considered to calculate this dimension mentioned below:

- Lateral undercut for wet chemical etching

- Oxidation

- p-contact ring

- Safety factor

These are illustrated in Fig. 4.3.

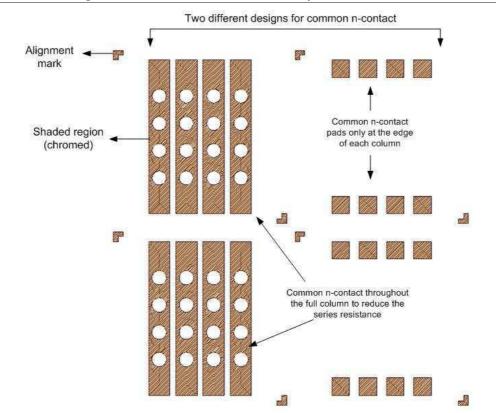

#### 4.3 Mask for N-Contact Bondpad

The n-contact metallization for matrix addressable arrays is also quite different from the conventional one because this metallization will not be done in the whole backside of the wafer, one full column except the region of the device or only the rectangular areas at the

single mode with 20 dB of transverse mode suppression [1].

#### Chapter: 4 Mask Design for Matrix Addressable Array

Figure 4.4: Close-up showing of the block, n-contact bondpad, in the mask layout where there are two different designs.

edge like bondpad will be metallized, instead. Actually, the overlying  $n^+$  layer on top of the semi-insulating substrate will be patterned by this mask.

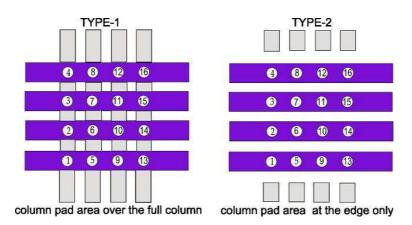

One of the most challenging issues in Matrix Addressable VCSEL arrays is the larger effective series resistance [12]. Taking this into account, two different types of n-contact metallization were designed. One of them is the metallization over the full column except the VCSEL circular region (left part of Fig. 4.4) which is very good from the viewpoint of series resistance. Another is just at the edge of every array like bondpad (right part of Fig. 4.4) where the needle will be placed on for electrical conduction. In addition, to reduce the series resistance, the bondpads were provided in both sides, i.e. top and bottom side of the arrays results increasing the total number of cathode bondpads to 8 instead of 4 for  $4 \times 4$  array.

There are two alignment markers at the opposite corner of each array instead of having four because these two alignment markers (shown in Fig. 4.4) will help us in aligning the profiles with the profiles of the subsequent steps which may not be correct since the alignment markers produced at the mesa formation step is the most correct one, like a reference. These will be visible in the next steps as well even if we do not make any met-

allization which can be helpful for alignment purpose. In other words, the two alignment markers in n-contact metallization step will be metallized and the other two alignment markers (not drawn in Fig. 4.4) already produced in the mesa formation step will be visible which will be quite helpful during the alignment from the third photolithographic step.

Since this is a metallization step, we need to design the mask in such a way so that we can get the negative tone, i.e. shaded area will not be protected by resist, consequently only the shaded area will be metallized. The negative tone is very necessary to get a negative slope of the resist which ultimately makes the lift-off process easier.

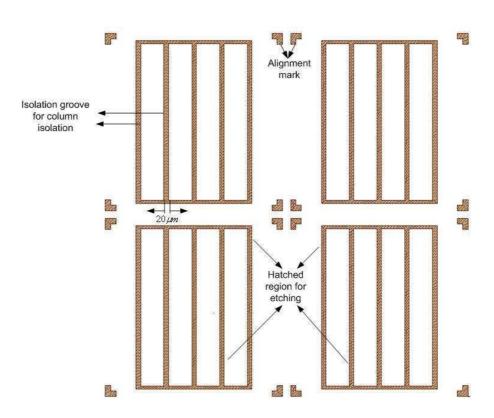

## 4.4 Mask for Column Isolation

Figure 4.5: Close-up showing of the block, Column Isolation, in the mask layout.

This mask is also for etching but not so much deep like mesa etching, only 2-3  $\mu$ m will be etched here. This etching will help us to reach into the undoped (intrinsic / insulating / not conducting) substrate by removing the n<sup>+</sup> buffer layer in order to isolate the four columns of 4 x 4 arrays. In this way, the four columns will become separated electrically by defining the trenches of width 20  $\mu$ m. It should be stressed that not only the five vertical lines are drawn but also the horizontal lines at the top and bottom are necessary for perfect isolation between adjacent columns as demonstrated in Fig. 4.5.

#### Chapter: 4 Mask Design for Matrix Addressable Array

This mask was designed for using the negative photoresist. Accordingly, the shaded area, i.e. chromed region will be ready for etching down till insulating substrate which implies that all the region except the chromed ones are protected by resist after development. As an alternative, the opposite design could be done, that is most of the region except the columns will be covered by chrome which forces to use the positive photoresist in order to get the desired pattern. If it were the case, then we would have faced a great problem in aligning by the mask aligner. Because large region covered by chrome in the mask means that the structures in the sample (already defined in the 2nd lithographic step) will not be clearly visible under the mask during the alignment. Because the chromed region will block to see through over the sample.

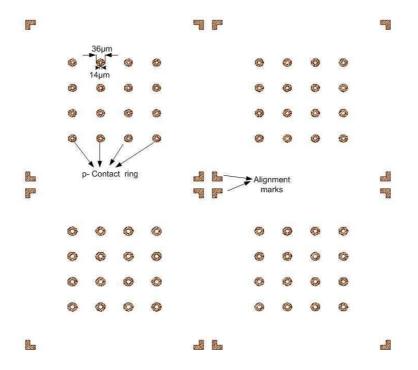

### 4.5 Mask for P-Contact Ring

Figure 4.6: Close-up showing of the block, Contact ring, in the mask layout.

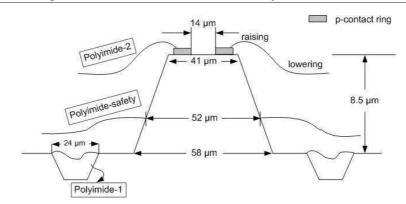

This mask is just for the metallization of the p-contact ring of each individual device. The aperture window in the contact ring must be included to allow the beam to escape. There are four different types of ring sizes as shown in Fig. 4.6 depending on the size of the mesa diameters.

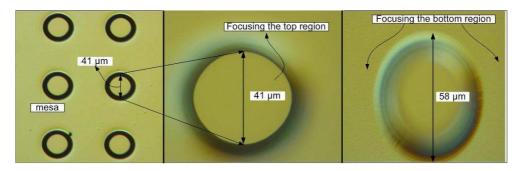

It is clear that the shaded area will be metallized here as usual. The design for the contact ring with an outer diameter of  $36 \,\mu\text{m}$  and inner diameter of  $14 \,\mu\text{m}$  for the mesa diameter of  $58 \,\mu\text{m}$  (the smallest one), whereas the mesa diameter size after etching till n<sup>+</sup> buffer layer will be like  $41 \,\mu\text{m}$  for the first approximation since the lateral undercut is almost equal to

4.6 Mask for Polyimide-1

the etching depth. We are getting  $2.5 \,\mu$ m in both sides as tolerances which will ultimately help us for good alignment in the mask aligner. The dimensions of the four alignment marks at the corners of each array have to be modified which should be different from the previous photolithographic step due to the lateral undercut in wet chemical etching there.

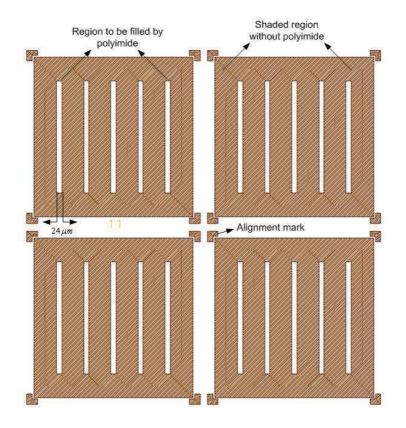

## 4.6 Mask for Polyimide-1

Figure 4.7: Close-up showing of the block, Polyimide-1, in the mask layout.

Now it is the time to planarize the surface by polyimide before the formation of the row pad area providing common p-contact. In addition to the surface planarization, polyimide plays also an very important role in facilitating the top contact metallization leads to prevent the short circuit by isolating from n-contact.

There are two different etch depths, one results from the mesa etching and another is from the trenches for column isolation. Basically this mask is designed for the latter one by which the trenches can be filled by the polyimide which is part of the first planarization. Logically, the name of the mask has been kept as polyimide-1 which will fill-up the only column-isolation grooves, i.e.  $2-3 \,\mu$ m in depth.

#### Chapter: 4 Mask Design for Matrix Addressable Array

From Fig. 4.7, we see that there are two different regions, shaded (should be covered by chrome) and unshaded, where the unshaded region will be filled by polyimide since the polyimide shows the behaviour like negative resist, i.e. the exposed area will be insoluble to the developer. Thus, the partial planarization by polyimide will be done in this step. Note that, the width of each column, i.e. unshaded area, is  $24 \,\mu$ m which will be filled by polyimide to the usage of the negative photoresist in the step, "column isolation" discussed in sect. 4.4.

Large region covered by chrome in the mask creates a problem during the alignment, mentioned earlier. But the opposite design is not possible in this case since the polyimide behaviour can not be made as positive tone.

## 4.7 Mask for Polyimide-2

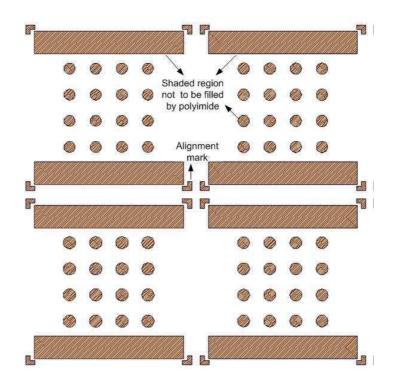

Figure 4.8: Close-up showing of the block, Polyimide-2, in the mask layout.

In the next polyimide mask the rest of the region which is  $7/8 \mu m$  down from the top of the mesa has to be planarized by spinning the thick or thin polyimide (if thin polyimide, using multiple times) and then removing the polyimide from that region photolithographically defined by this mask. Fig. 4.8 shows that, this polyimide mask contains circles with four different dimensions in four different arrays which indicates that the VCSELs top part from where the light will come out and two rectangles at the two opposite sides where

the underlying n-contact pads are located will not be covered by polyimide.

However, the overlap between the p-contact ring (the outer circle diameter is  $36 \,\mu$ m) and the polyimide mask-2 (the circle diameter is  $31 \,\mu$ m) is  $2.5 \,\mu$ m in both sides. It is known that here, also the unshaded area (shown in Fig. 4.8) like the polyimide-1 step are filled-up by the polyimide.

## 4.8 Mask for Polyimide-Safety

Figure 4.9: Close-up showing of the block, Polyimide-safety, in the mask layout.

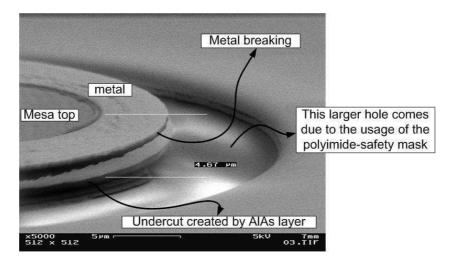

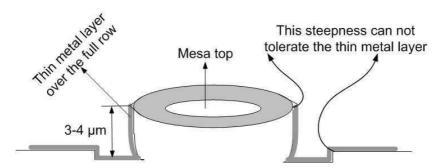

This mask is designed just for safety. Because while designing the mask it was not certain that how many masks will be needed for planarization. Or in other words, how many steps should be carried out in planarizing the surface that was unsure. It is true that, the lesser the number of steps , the lesser the time and effort will be needed and the higher the yield of the devices on the sample. Because more lithographic steps or more processing obviously degrade the quality of the sample and some devices might get damaged in each processing. So it is recommended that the number of steps should be as less as possible. On the other hand, plnaraizing the surface in a single step staying from 8-9  $\mu$ m down is not so easy task. Because filling-up so much depth by the polyimide will result some undesired effects like metal breaking (discontinuity of metals after p-metallization) due to extra raise in the mesa overlap region or due to lowering of the polyimide beside the mesa

Chapter: 4 Mask Design for Matrix Addressable Array

Figure 4.10: Schematic diagram of the design of different polyimide masks including the dimensions.

top. In order to reduce the uncertainty one extra mask, polyimide safety mask (shown in Fig. 4.9) is designed. The shape of this mask is exactly the same like polyimide-2 but differs from the dimension of the circle diameters. Basically this mask is designed by planning the planarization steps of polyimide in three steps. So the circle diameter has a greater dimension which indicates that half of total etch depth (8-9  $\mu$ m) will be filled-up by the polyimide in this step. Then the rest will be done by polyimide-2.

Moreover, how the planarization by the polyimide will be done in three steps and where the "polyimide-safety" will play a role that have been demonstrated in Fig. 4.10.

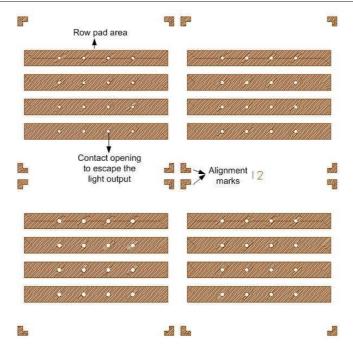

### 4.9 Mask for P-Contact Bondpad

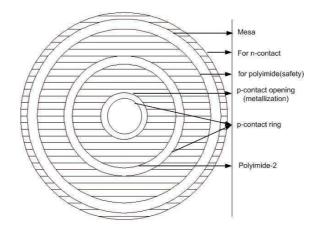

This mask is for the p-contact metallization over the full row and at the same time maintaining some isolation between the devices of two adjacent rows. The shaded areas, i.e. the row pads areas except the small circles inside will be metallized as displayed in Fig. 4.11. In fact, the circles inside the row pad areas will be just the opening of each VCSEL which is 18  $\mu$ m (mesa diameter 58  $\mu$ m) in diameter whereas 14  $\mu$ m is the inner diameter of pcontact ring. This 2  $\mu$ m in both sides is just for tolerance from alignment point of view. So ultimately 6.5  $\mu$ m is the overlap between the p-contact ring and p-contact bondpad which is sufficient for electrical current conduction. Of course, the higher the overlap, the better the performance in conducting current through the devices. But the pitch size of the devices which are 125  $\mu$ m - the limiting factor in this case.

In a tabular format, the diameters of the circles for different photolithographic steps drawn in the mask layout (starting from the mesa till p-contact circles inside the p-contact bondpad) are summarized in Table 4.1.

In addition, the same information has been illustrated in Fig. 4.12 schematically.

#### 4.9 Mask for P-Contact Bondpad

Figure 4.11: Close-up showing of the block, p-contact bondpad, in the mask layout.

| Mesa(µm) | n-<br>contact<br>(µm) | p-contact ring<br>(inner-outer)<br>(µm) | Polyimide-<br>2(µm) | Polyimide-<br>safety<br>(µm) | p-contact<br>(bondpad)<br>(µm) | Output<br>(active)<br>(µm) |

|----------|-----------------------|-----------------------------------------|---------------------|------------------------------|--------------------------------|----------------------------|

| 58       | 62                    | 14-36                                   | 31                  | 52                           | 18                             | 4                          |

| 60       | 64                    | 16-38                                   | 33                  | 54                           | 20                             | 6                          |

| 62       | 66                    | 18-40                                   | 35                  | 56                           | 22                             | 8                          |

| 64       | 68                    | 20-42                                   | 37                  | 58                           | 24                             | 10                         |

Table 4.1: Dimensions of different circles drawn in the mask layout in a tabular format.

Figure 4.12: Schematic diagarm of the dimensions of different circles drawn in the mask layout.

## 4.10 Summary

In summary, the mask design approach for fabricating the Matrix Addressable  $4 \times 4$  VCSEL array has been presented in this chapter. This prototype mask design, discussed in this chapter, inevitably will help to fabricate these arrays very successfully in the next future. Because all important issues need to be considered while designing the mask, all the problems which might come in fabricating this array are also outlined in this chapter.

# Chapter 5

## Matrix Addressable Array Fabrication

## 5.1 Introduction

Now VCSEL array needs to be fabricated depending on the designed mask. In fact, this is the most important and critical step where real problems have to be handled with great intelligence because the design what we implemented in the mask that can not be changed any more. Thus, keeping the mask structures completely unchanged and facing plenty of practical problems, the processing should be continued in order to get the arrays with a large number of good devices. In addition, one can get the chance to compare his existing ideas and views of fabricating this array used in designing the mask with the reality which will help in making some further improvements afterwards.

In this chapter, all the processing steps done in the cleanroom for fabricating the VCSEL array are outlined with the practical figures and schematics. This will be quite helpful for the readers to understand all the practical steps starting from the formation of the mesa till the metallization of p-contact over the full row. Besides, the problems and the difficulties in fabricating the devices and the solutions of those are also highly illustrated in this chapter.

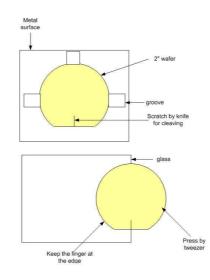

## 5.2 Mesa Formation

In fabricating the 2-D MA VCSEL array, the first task is to form the mesa for the devices which can be defined by wet chemical etching or dry etching. But both of these etching methods have some advantages and disadvantages. For example, wet chemical etching is cheap, easy to do and almost no damage due to purely chemical nature but this process has very poor anisotropy and poor control in etching. On the other hand, dry etching (e.g. RIE) has very high anisotropy but it creates some damage on the sample and it is expensive as well. Considering these merits and demerits, wet chemical etching was used to define the mesa.

Standard wet chemical etching of III-V semiconductors occurs by oxidizing the semiconductor surface and etching the oxide. Typically this is achieved by submerging the semiconductors in a liquid mixture consisting of an oxidizing agent and a complexing (oxide etching) agent [17]. Obviously the basic process consists of using hydrogen peroxide  $H_2O_2$  as the oxidizing agent to form GaAs-oxide compounds at the GaAs surface (oxidation step), that are then removed using an acid ( $H_2SO_4$ ).

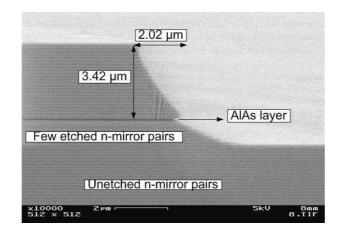

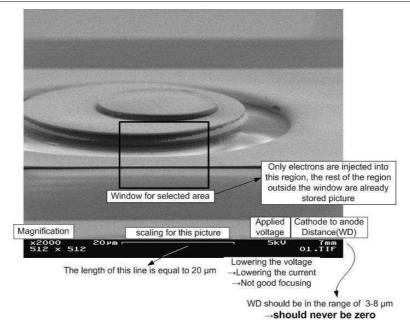

Figure 5.1: SEM photograph (10,000x) of the cross sectional profile of mesa which shows that the etching was performed just till AlAs layer for oxidation, though few n-mirror pairs underneath AlAs layer were also etched.

Fig. 5.1 shows the typical cross sectional profile of mesa where the perpendicular etch depth is  $3.42 \,\mu\text{m}$  (from the top p<sup>+</sup> layer to AlAs layer) and the lateral undercut due to isotropic nature is  $2.02 \,\mu\text{m}$  which one was assumed earlier. The etching was done in acidic solution (H<sub>2</sub>SO<sub>4</sub> : H<sub>2</sub>O<sub>2</sub> : H<sub>2</sub>O) for 3 minutes to reach little bit down to AlAs layer which is sufficient for oxidation taking the etching rate 1.2  $\mu$ m/minute into account.

But as mentioned earlier, the etching should be continued till  $n^+$  buffer layer in this work which is located under n-mirror pairs. It means that all the p-mirror pairs, AlAs layer, active region, all n-mirror pairs should be etched to reach in n-doped buffer layer. A question comes, then how the cross-sectional profile looks like. Will it be just like the typical case, illustrated in Fig. 5.1 but just extending more down or different?

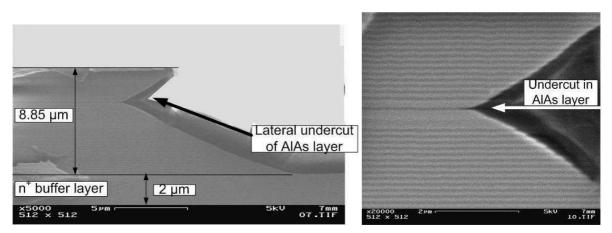

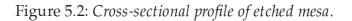

To get the answer the same acidic solution was used for etching but the duration of etching was too long, 7 minutes instead of 3 minutes. Again the cross-sectional profile of the mesas was examined in SEM machine but this time the profile was little bit interesting and obscure.

From Fig. 5.2 we see that there is a huge lateral undercut in AlAs layer which completely changes the shape of the cross-sectional profile of mesa structure. Then it becomes clear

#### 5.2 Mesa Formation

(a) SEM photograph (5000x) of the cross sectional profile of mesa (b) SEM photograph (20,000x) of the cross which shows that the etching was performed till last n-mirror sectional profile of mesa close to the AlAs layer pairs for oxidation.

that this is the typical mesa profile in the acidic etchant which was done at the room temperature and for long time, 7 minutes. The reason of this event is that the lateral etching rate of AlAs layer is much faster than the other layers which causes the lateral undercutting of the layers close to AlAs layer [18]. For a short time etching (until the AlAs layer is approached by the etchant) the etchant used at the room temperature behaves like a diffusion one, and a diffusion profile is created which is shown in Fig. 5.1.

Figure 5.3: Optical microscope image (20x) of the top view of the mesa having smallest diameter after wet chemical etching (the leftmost). Image (100x) where mesa top has been focused(the middle one). Image (100x) where mesa bottom has been focused (the rightmost).

It should be stressed that during mesa formation by wet chemical etching, in order to expose AlAs layer, there is a symptom can be found by looking at the sample well which is extremely helpful for knowing the location of the epitaxial layers. The symptoms gets well-pronounced after about 2 minutes 40 seconds (3.16  $\mu$ m down from the top) when the sample will be completely becoming black for a long time from the bright condition then

it can be realized that AlAs layer is reached. After a while the sample will start to be full of bright-dark regions again since the etching is still ongoing and then after almost 6 minutes 45 seconds there is one very interesting symptom was found which can be used as a indicating factor for stopping the etching. In particular, that bright-dark regions like the stripes of Zebra in the sample is indicating that the n-mirror pairs are being etched and that stripes will disappear after about 6 minutes 45 seconds from which it was realized that  $2 \mu m$  thick n-doped buffer layer starts from here where the etching should be stopped.

## 5.3 Selective Lateral Oxidation

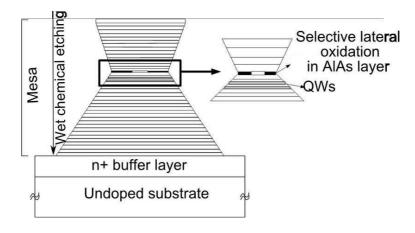

Figure 5.4: Schematic cross-section view of a selectively oxidized VCSEL after deep mesa etching.

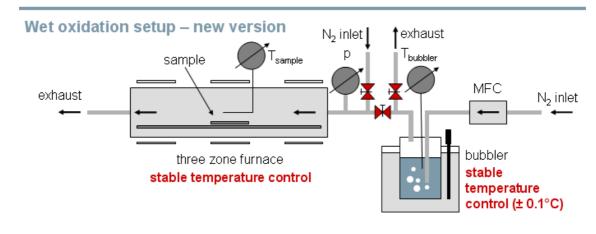

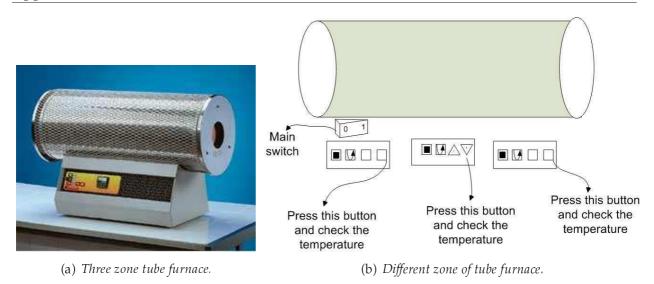

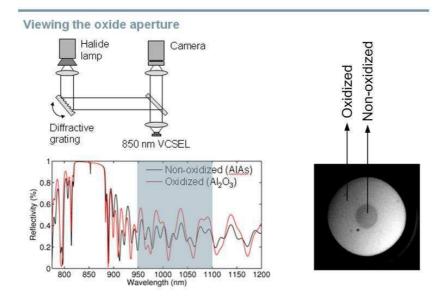

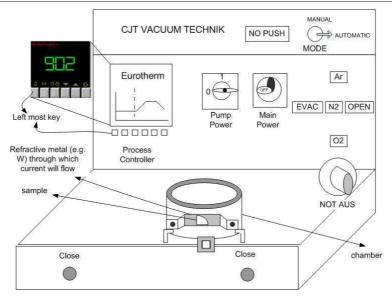

Then comes to the oxidation. But there are two meaningful words before the oxidation, selective and lateral. What do these mean? Selective means the sample should be oxidized selectively. In details, while oxidizing, the sample should be inserted into the hot three zone furnace where all the epitaxial layers are exposed to the hot furnace to be oxidized. But only that layer,  $Al_xGa_{1-x}As$ , where,  $x \ge 0.95$  will be oxidized and converted into  $Al_2O_3$ . At the same time, the rest of the epi-layers will remain unchanged and unaffected. In the sample used here, x is equal to 1, i.e. AlAs whose thickness is about 30 nm. Here selectivity comes from this point of view. And the word, 'lateral' becomes very clear from Fig. 5.4 where the AlAs layer gets oxidized laterally - has been shown.

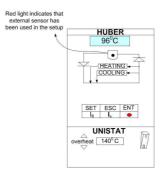

The oxidation procedure is very simple. Exposed AlAs layer will react with water vapor transported by inert and carrier  $N_2$  gas into the hot furnace where the temperature will be around  $380^{\circ}$  C and that AlAs layer will get converted into  $Al_2O_3$ . Note that, the water vapor mentioned earlier is supplied to the hot furnace by bubbling  $N_2$  through deionized water. Moreover, while going to the hot furnace, the water vapor passes through a heated tube to avoid condensation. Note that the resist should be well-stripped from the sample before the oxidation, otherwise that resist will be very hard and sticky to the sample surface which is very difficult to remove will act as insulating layer.

#### 5.3.1 Oxidation Rate Dependencies

The following factors control the oxidation rate [19] :

- Inert carrier gas, N<sub>2</sub> flow

- Al composition

- The layer thickness

- Bubbler temperature

- Furnace tube temperature

#### 5.3.2 Electrical and Optical Confinement

The oxidized region exhibits excellent current-blocking properties and confines the current to the non-oxidized region. Additionally, the native oxide exhibits a much lower index of refraction than the original upper confining layer (n=3.3). Thus, the index step (3.3 to 1.5), through the the thickness of the AlAs layer, forms an optical waveguide in the lateral direction [19].

Figure 5.5: Illustration of the top view of the lateral oxidation in AlAs layer of four different mesas which can be viewed by infrared camera (40x). Here, the dark and bright region indicate the non-oxidized and oxidized area respectively. The undercut in AlAs layer due to the wet chemical etching can be observed as well.

The parameters used in the oxidation process are as follows: Temperature of the furnace in three-zones,  $T_{furnace} = 382^{0}C \parallel 382^{0}C \parallel 382^{0}C$

Chapter: 5 Matrix Addressable Array Fabrication

Bubbler water temperature,  $T_{bubbler} = 96^{\circ}C$ Amount of N<sub>2</sub> flow = 0.5 litre/min Sample temperature,  $T_{sample} = 380^{\circ}C$ Pressure of water vapor, P = 1012 mbar

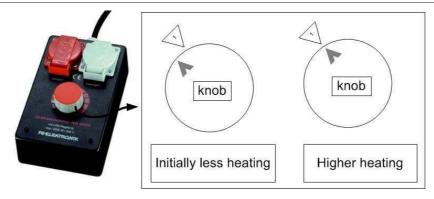

After using the above process parameters and checking the oxidation rate by a dummy sample, the oxidation is done. Fig. 5.5 shows the top view of four different sized mesas where we can see the rhombus shaped oxide apertures after oxidation process. Thus approximately the desired active diameters of the devices are found. The operating procedures of the oxidation machine along with the necessary explanations are discussed in details in appendix E.

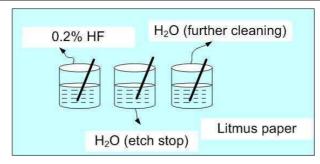

## 5.4 Column Isolation

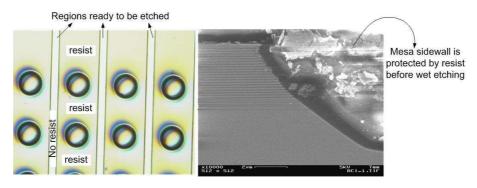

Figure 5.6: Optical microscope image (10x) of the top view of resist patterning after development prior to etching for column isolation (the left). SEM photograph (10,000x) of the mesa sidewall which is protected by resist so that etching solution does not affect the sidewall at all during the etching (the right).

After the lateral oxidation process, photoresist was patterned in the wafer for wet chemical etching. Basically in this step, the columns of width 20  $\mu$ m should be etched 2-3  $\mu$ m down till undoped substrate by removing the n-doped buffer layer in order to electrically isolate the columns from each other. In addition, the top and bottom regions of few micrometers in width should be etched as well for perfect column isolation. Otherwise, the current flow through the devices can not be controlled properly. Considering this, one can say that this is the most crucial step in matrix addressing array processing.

TI35ES or TI35E photoresist can be used as etch mask which is protective against the harsh condition like wet etching. But due to the problem mentioned in Sect. 5.5, these resists should be avoided. Finally the resist, AZnLOF 2070 resist is used in this etching which is also stable against wet etching. This time, one should make sure that the whole wafer, e.g. the mesa, the mesa sidewall and all the regions except the region of width 20  $\mu$ m which need to be etched, should be protected by resist so that etching solution can not

affect at these structures as indicated in Fig. 5.6.

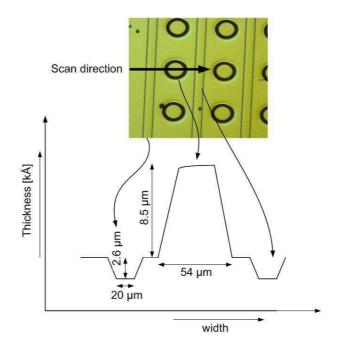

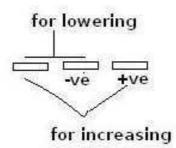

Figure 5.7: Etch depth measurement by the Alpha-Step surface profilometer after two etching processes.

Then the same acidic solution like mesa etching is used in etching for column isolation. But the etching rate is much slower at this time compared with mesa etching due to absence of Al-content in the layer, i.e. pure GaAs. Usually the sample is soaked in acidic solution for 3 minutes 30 seconds and the etch depth is found around 2.6-3.0  $\mu$ m by measuring in alpha step and optical microscope. On the basis of the processing result, it can be said that the etch rate of GaAs is 0.78  $\mu$ m/min which is accurate and reproducible. Noteworthy that all the etching experiments were performed in this work at room temperature.

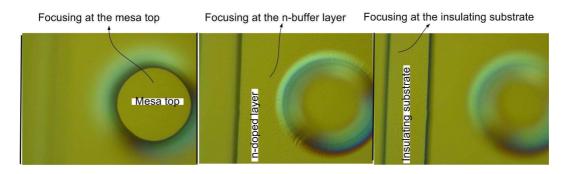

Fig. 5.7 shows the measurement result which is obtained by scanning through the sample structure in the profilometer, alpha-step. As an alternative, the etch depth can be measured very easily just by changing the focusing knob of the optical microscope as indicated in Fig. 5.8. It is often convenient that the etching depth should be greater than  $2 \,\mu m$  which ensures the arrival in insulating substrate which is very much necessary for matrix addressing operation.

It should finally be noted that before starting the wet etching process, the resist (AZnLOF 2070) patterning after development should be checked very well to make sure there is no residual resist in the etched region which creates a severe problem. May be in this case,  $O_2$  plasma is a solution which can remove this residual resist. Otherwise, after etching it may be found that there are some regions where there is desired 2-3µm etching and there

are some regions without any etching at all. In fact, AZnLOF 2070 resist becomes very stable on the wafer after heat treatment processes. So, well-development and  $O_2$  plasma both are always recommended before the etching process.

Figure 5.8: Etch depth measurement by the optical microscope after two etching processes.

#### 5.4.1 Electrochemical Reaction

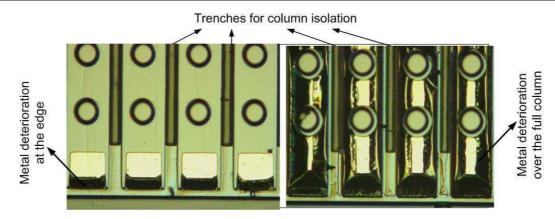

GaAs etching rate and shape in a given etching solution can be altered by the presence of a metal substance on the GaAs surface due to the so-called electrochemical effect which is the result of the electric circuit formed between the semiconductor, acting as an anode, and the metal as a cathode [20]. This type of reaction takes place when exposed metals appear in the vicinity of the GaAs area to be etched by the etchant [21]. Due to the different surface potentials, semiconductor and exposed metal behave like anode and cathode in the etchant, respectively, thus forming an electrochemical circuit, thus effecting the etching rate of GaAs by increasing the rate of surface oxidation [22]. It has a pronounced impact on the electrical performance of the device, so one should change the processing steps order so that wet processes are performed before metallization is applied [20].

In this work, it is true that the metal surface can be completely covered by photoresist before the etching process in order to avoid this problem. But it is very possible to finish the two etching processes successively ahead of metallization. Besides, there is also a possibility of exposing the metal surface at the edge of the structures which can cause these problems and at the edge of the wafer, of course, this will take place due to less control in processing over there. Considering all these facts, the n-contact metallization steps should be done later, i.e. after column isolation etching step which will not create any problem in the subsequent processing at all.

In addition to the above-mentioned obvious and serious effect, the metal deterioration problem was also found in the processing if the column isolation etching is carried out after n-contact metallization step which is indicated in Fig. 5.9. But the proper reason of this event can not be figured out due to the lack of time.

Figure 5.9: Illustration showing the metal deterioration probably caused by the etchant, the metallization is done earlier than the etching for column isolation here.

## 5.5 N-Contact

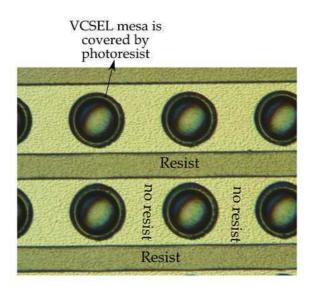

After column isolation step, the sample has to be ready for n-contact metal evaporation. Since it is selective metallization, one photolithographic step is necessary before loading the sample into the metal evaporation chamber. Fig. 5.10 shows the perfect conditions necessary for selective n-contact metallization. Here we see the resist patterning after n-contact photolithographic step, in specifically, after development, otherwise the desired metallization can never be possible.

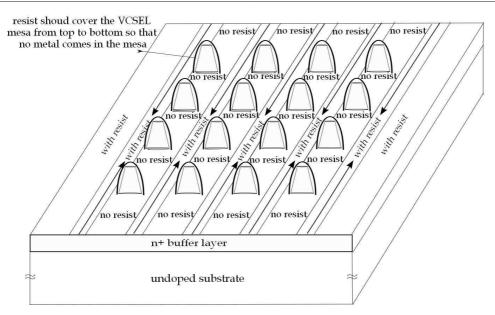

At first, TI35ES, image reversal photoresist, very thin or low viscous but has the ability of giving very good resolution, was tested for this purpose. Can TI35ES resist fulfill this condition? After metal evaporation and then lift-off process, the sample is checked in optical microscope to make sure about the desired metallization. Unfortunately the lift-off process does not work well in this way. The main problem is observed at the top of the mesa from where the metal can not be lifted-off. In fact, there should not be any metal since it is supposed to be covered by resist. After investigating the reason it is found that TI35ES photoresist is so thin (low viscosity) that it does not have the ability to cover the deep mesa after development even if very low spinning speed is used in the spin coating machine. Or in other words, after spin coating and then development if the resist patterning is checked very carefully in the microscope then it will be clear that there is no resist at the top of the mesa or some resist at the middle of the mesa but no resist is at the edge of the top mesa which is sufficient for unsuccessful lift-off process. It is very known that resist should be exposed to MP (1-Methyl-2- Pyrrolidon) for lift-off process. If metal covers the top mesa fully then MP can not attack the resist which prevents to lift-off the metal.

In order to solve the problem the thicker negative resist which has the ability of covering the deep mesa after development was used. AZnLOF 2070 is such type of resist which

Figure 5.10: Schematic view of 4x4MAarrays after n-contact photolithographic step, in particular, after development. Two different regions, named 'with resist' and 'no resist' indicate 'no metal' and 'with metal' respectively after lift-off process. In addition, mesas of height 8.5-9 µm are completely protected by the resist so that no metal can remain here.

has a high viscosity and can give the thickness of 10-12  $\mu$ m after development depending on the spin speed, but at the expense of the resolution.

Thus by using this resist, metal is evaporated and then lift-off is performed without any problem, or in other words, the desired regions gets metallized. Note that, AZnLOF 2070 has also the ability of withstanding higher temperature in metal evaporation chamber. In most practical cases, before loading the wafer into the evaporation chamber, the sample is soaked in HCl solution (HCl :  $H_2O = 1:1$ ) for 30 seconds in order to remove the native oxides formed on the sample.

Concerning the n-contact metal evaporation, the materials used Ge(17nm)Au(50nm)-Ni(10nm)-Au(50nm) which are very important for good ohmic contact on the surface of GaAs surface. This contact is also known as alloyed contact which implies that heat treatment process so-called annealing is needed to ensure a good ohmic contact. Actually, GeAu-Ni-Au to n-type GaAs is very complicated ohmic contact process which gets alloyed into the GaAs at temperatures in excess of 400<sup>o</sup>C to provide the necessary low contact resistance.

However, the selection of a metallization system that creates a surface region with a high carrier concentration promoting a tunneling mechanism. It is known that by providing a

Figure 5.11: Optical microscope imgae (20x) of the top view of the resist patterning after development in n-contact metallization photolithographic step.

barrier layer and making it very narrow width by high doping concentration it is possible to achieve an ohmic type contact based on the tunneling mechanism. In such metallization system, Ge, the first material, acts as a dopant element, Au acts as a base metal, Ni acts as a diffusion barrier [23]. Since Ge is a donor, this forms a heavily doped n-type region that promotes tunneling mechanism which leads to an ohmic behavior.

## 5.6 P-Contact Ring

This is an optional step in matrix addressable array processing. Undoubtedly, p-contact ring enhances the device performance, especially good contact point of view, this step is very important. But skipping this step, one can also test the arrays which saves a lot of time and increases the yield of the chip. Since each photolithographic step reduces the probability of getting the number of good devices. Once all the mandatory processing steps are optimized and the array works well with reproducibility then this optional step can be applied for more improvement.

For a good ohmic p-contact on the surface of GaAs surface, Ti(20nm)-Pt(50nm)-Au(150nm) these three metal layers are used. In fact, this is non-alloyed contact for which annealing is not needed. Evidently these metal layers just sit on the GaAs surface and make the ohmic contact.

A question will arise, why do we need to use these three metals to get an ohmic contact instead of using a good conductive metal (e.g. Au)? Well, among these three metals, Au of course, the base metals for good electrical conduction since it has much higher

conductance and its place in the table of conductance is the third. But the other metals are also needed for good ohmic contact. At first a thin Ti layer was used because it has good adhesion properties with the GaAs surface. Then the interesting metal layer, Pt was deposited as a barrier layer in order to prevent the diffusion from Au into GaAs semiconductor. What would happen if there would be no Pt at all? The answer is obvious, the resulting contact would be converted into Schottky contact since metal carriers and semiconductors carriers will be allowed to diffuse each other then which ultimately lead a rectifying contact - undesired. It is worthy to mention that Au has a high diffusion factor into GaAs and the rate of Au diffusion into the GaAs is a function of the temperature and the material concentration gradient [24]. So, Pt is very necessary. At the end, thick Au layer, base metal, was deposited on top of Pt layer.

It is found experimentally that the arrays work well without any ring contact at the top of the devices. However, the step of the p-contact ring should come after planarization by polyimide. Because keeping the surface unplanarized if the ring contact process is started then there is high probability of unsuccessful lift-off process as mentioned in Sect. 5.5. It is also true that the thick resist (e.g. AZnLOF 2070) can be a solution of this problem but the problem comes when one thinks about the resolution as the ring contact dimensions are not so big.

## 5.7 Polyimide Step

Polyimide has mainly two purposes in device processing, one is planarization and the other one is electrical isolation between two parts so-called passivation. Thanks to polyimide, both purposes are fulfilled by the polyimide step at the same time. Experimentally, this is the most difficult step in the processing because one has to make sure the planarization of the surface of 8-9  $\mu$ m and keeping the desired profile at the top of the device in order to facilitate the p-metallization simultaneously. Moreover, without successful polyimide step one can not think of the good devices because this step highly influences the subsequent steps.

There are three types of polyimide which can be used in the device processing, Durimide 7505, durimide 7510 and durimide 7520 are the three options to be used which are orderly arranged according to the thickness. These polyimides have the ability of planarizing in the range 2-40  $\mu$ m. Apparently it seems that there should be no problem to planarize the surface of 8-9  $\mu$ m. Where does the problem come from then? The following discussion will help the readers to know the answer.

To optimize the polyimide step for matrix addressable array, different approaches are adopted from the beginning. In fact, four different approaches (three of them are unsuccessful) were used in the processing which will be discussed now.

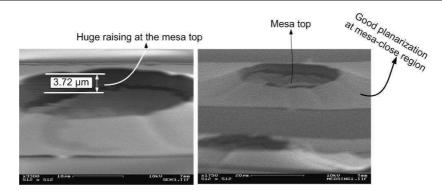

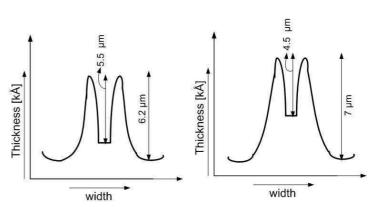

#### 1) Three steps of polyimide and usage of "POLYIMIDE SAFETY" mask:

At first, the traget is made like this, the planarization will be done in three steps. The 'polyimide-1' which is designed just for filling the trenches will be used initially and then the 'polyimide safety' mask which has a bigger dimension to make very rough planarization and then the rest planarization will be done as the conventional 'polyimide-2' which has the overlap with the top of the devices as discussed in chapter 4. The processing steps are maintained keeping this target at the front. But the processing are not successful due to various reasons. Fig. 5.12 highlights these reasons. The polyimide planarization will

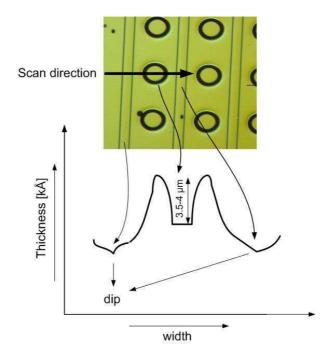

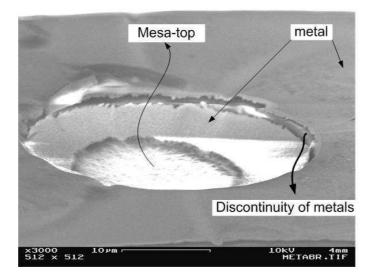

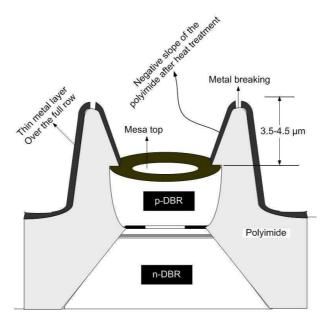

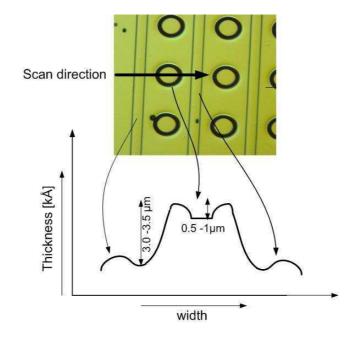

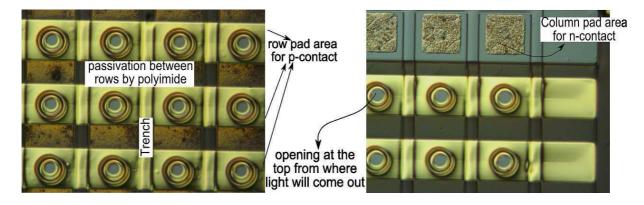

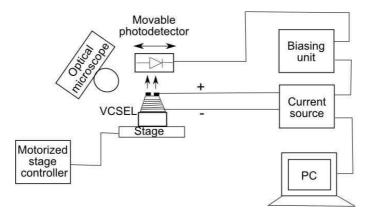

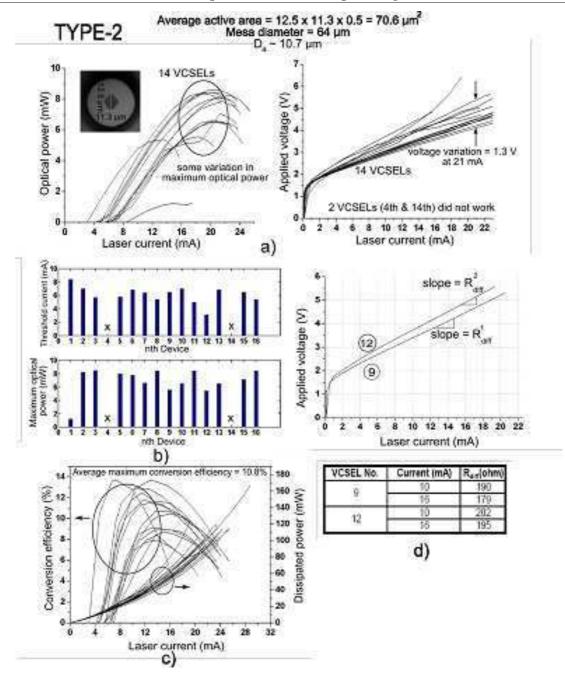

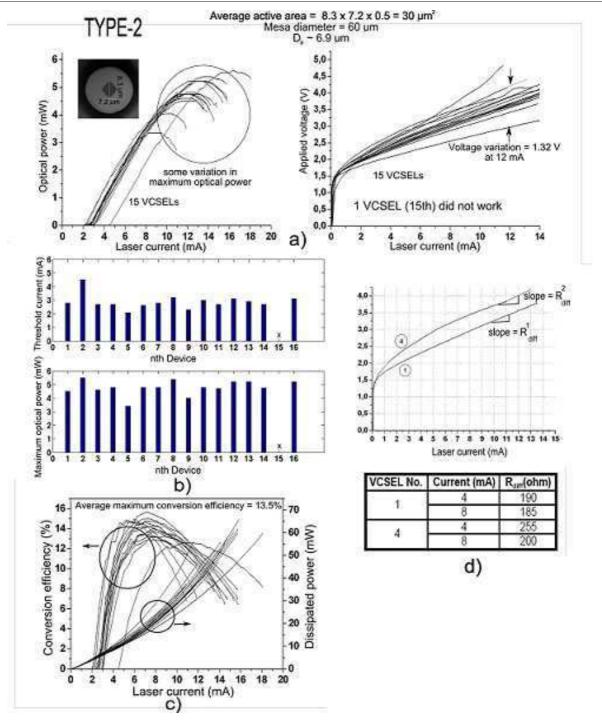

Figure 5.12: SEM photograph (5000x) of the lateral view of the mesa top and mesa-close regions where after three steps planarization by the polyimide, p-metallization is done over the full row.