| Name:   | <br> |  |

|---------|------|--|

|         |      |  |

|         |      |  |

|         |      |  |

| Porm No |      |  |

## UNIVERSITY OF CALIFORNIA, SANTA BARBARA

Department of Electrical and Computer Engineering

## **MIDTERM EXAMINATION-ECE124A**

Room: ESB-Cooper Lab, November 8, 3:30-5:00 PM

## **READ CAREFULLY:**

- > This is a CLOSED BOOK Exam. Any form of notes is not allowed. Calculators OK.

- > READ the questions carefully before answering. Include all your answers in locations specified on these pages. Show ALL WORKING used to arrive at answers. Use space provided for all working. Use the back sides if necessary. There are 8 pages including the cover page. Be sure to write Your NAME/Perm No. on EVERY PAGE.

| Question | Scores |

|----------|--------|

| #1       | / 35   |

| #2       | / 30   |

| #3       | / 35   |

| TOTAL    | / 100  |

Good Luck!

## **ECE 124A-Fall 2011** Prof. K. Banerjee

- Part I: (17 pts) (2 pts each for a-d) (suggested time: 10 minutes) 1.

- Consider a long-channel NMOS transistor. Which of the following gate-to-source voltage conditions can be used to obtain a constant-current source?

- (A) Vgs<Vds+Vt & Vgs>Vt

- (B) Vgs < Vt

- (C) Vgs>Vds+Vt & Vgs>Vt

- (D) Vgs < 0.5Vds & Vgs > Vt

- Which of the following operating regions in a MOSFET results in largest gate capacitance? **b**)

- (A) saturation (B) linear

- (C) cut-off

- (D) A and C (E) B and C (F) A and B

- Which of the following parameters scale identically according to both constant-Vdd and c) constant-Electric field scaling theories?

- (A) active power

- (B) intrinsic gate delay

- (C) energy-delay product

- (D) gate capacitance/unit area

- (E) A and B

- (F) B and D

- (G) C and D

- Applying a forward body bias to the PMOS transistor of a CMOS inverter may result in:

- (A) higher gate delay (B) reduced sub-threshold leakage (C) lower gate delay

- (D) lower NM (E) only B and C (F) only A and B (G) B, C and D (H) B and D

- Consider an inverter with fanout of three. Ignore interconnect and diffusion capacitances for now. If a gate dielectric with higher k value (but same thickness) is used, then the inverter delay (ignoring any change in threshold voltage): (3 pts)

- (A) decreases, since the drive current increases

- (B) increases, since the gate capacitance increases

- (C) does not change, since the drive current and delay both increase

- (D) decreases, since increase in drive current is more than that of capacitance

- (E) increases, since increase in capacitance is more than that of drive current

- For the inverter in part (e), assume that the total capacitance is the sum of gate, interconnect and diffusion capacitance. If the gate oxide is thinned, then which of the following statement is most accurate? (3 pts)

- (A) since the drive current increases, delay reduces

- (B) since the total capacitance increases, delay increases

- (C) since the drive current and total capacitance both increase, delay does not change

- (D) increase in drive current is > the increase in total capacitance, hence delay reduces

- (E) increase in total capacitance is > that of drive current, hence the delay increases

- Typically a ratio of 2 for PMOS to NMOS transistor widths is used for an inverter, which gives a trip (switching) point of Vdd/2. If the NMOS channel length reduces due to process variations, which of the following statement is most accurate? (3 pts)

- (A) trip point increases, and one of the noise margins increases

- (B) trip point decreases, and one of the NMs increases while other decreases

- (C) trip point decreases, and one of the NMs increases while other decreases

- (D) trip point doesn't change, and one of the NMs increases while other decreases

- (E) trip point does not change, and noise margins do not change

Perm No.

**1. Part II:** (8 pts) (suggested time: 8 minutes) As we know, the propagation delay of a CMOS inverter is:

$$t_p = t_{pintrinsic} + t_{pload} = t_{po}(1 + \frac{f}{\gamma})$$

where f is effective fanout and  $\gamma$  is intrinsic output capacitance over input (gate) capacitance of the inverter.

If the delay of a chain of two minimum sized inverter,  $t_{p1} = 5 \text{ ns}$ ,

and the delay of a chain of two inverters where the first is minimum sized and the second one is 3 times minimum, equals  $t_{p2} = 7 \text{ ns}$ .

Calculate  $t_{p0}$  and  $\gamma$ .

Perm No. \_\_\_\_\_

1. Part III: (10 pts) (suggested time: 8 minutes) All transistors in the NMOS pull-down network below have a (W/L) ratio of  $\alpha$ . Determine the best-case  $\tau_{pHL}$ , if the worst-case  $\tau_{pHL}$  is 9 ns.

Perm No.

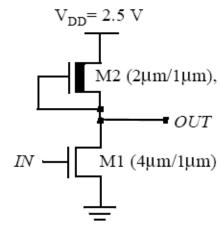

2. (30 pts) (suggested time: 20 minutes) Consider the circuit shown below. Device M1 is a standard NMOS device. Device M2 has all the properties identical to M1, except that its device threshold voltage is negative and has a value of -0.5V. Assume that all the current equations and inequality equations (to determine the mode of operation) for the depletion device M2 are the same as a regular NMOS. Also, assume that the input IN has a 0V to 2.5V swing.

Note:

$$I_{ds} = k_n \frac{W}{L} \left[ (V_{GS} - V_T) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

, where  $k_n = \mu_n C_{ox=115\mu A/V}^2$

i) Device M2 has its gate terminal connected to its source terminal. If  $V_{IN} = 0V$ , what is the output voltage? In steady state, what is the mode of operation of device M2 for this input?

ii) Compute the output voltage for  $V_{IN} = 2.5V$ . You may assume that  $V_{OUT}$  is small to simplify your calculation and  $V_{dsat} = 0.265$  V. In steady state, what is the mode of operation of device M2 for this input?

iii) Assuming the probability that (IN = 0) = 0.4, what is the static power dissipation of this circuit?

**3. (30 pts)** (*suggested time: 25 minutes*) (a) Minimize the following switching function and implement in static CMOS style. You may assume that inverted inputs are available without skew.

$$F(v, w, x, y, z) = \sum (1, 2, 6, 7, 9, 13, 14, 15, 17, 22, 23, 25, 29, 30, 31)$$

| Name:                                      | ECE 124A–Fall 2011<br>Prof. K. Banerjee                   |

|--------------------------------------------|-----------------------------------------------------------|

| Perm No.                                   |                                                           |

| (b) Size the pull-up and pull-down transit | stors so that each stage is equivalent to a 2:1 inverter. |

|                                            |                                                           |

|                                            |                                                           |

|                                            |                                                           |

|                                            |                                                           |

|                                            |                                                           |

|                                            |                                                           |

|                                            |                                                           |

(c) Calculate the logical effort of the gate (for each input).

| Name:    | ECE 124A-Fall 2011 |

|----------|--------------------|

|          | Prof. K. Banerjee  |

| Perm No. |                    |

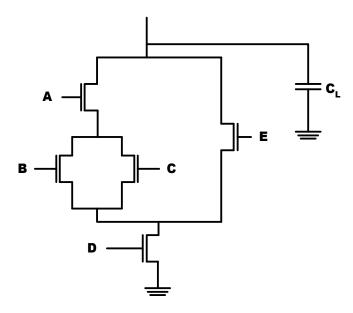

(d) Derive an expression for the worst-case pull-down delay of the gate in terms of the resistance of the minimum size NMOS (= $R_0$ ) and corresponding internal node capacitance ( $C_0$ ) when driving an external load  $C_L$ .