## ECE 122A VLSI Principles Lecture 4

Prof. Kaustav Banerjee Electrical and Computer Engineering University of California, Santa Barbara *E-mail: kaustav@ece.ucsb.edu*

Lecture 4, ECE 122A, VLSI Principles

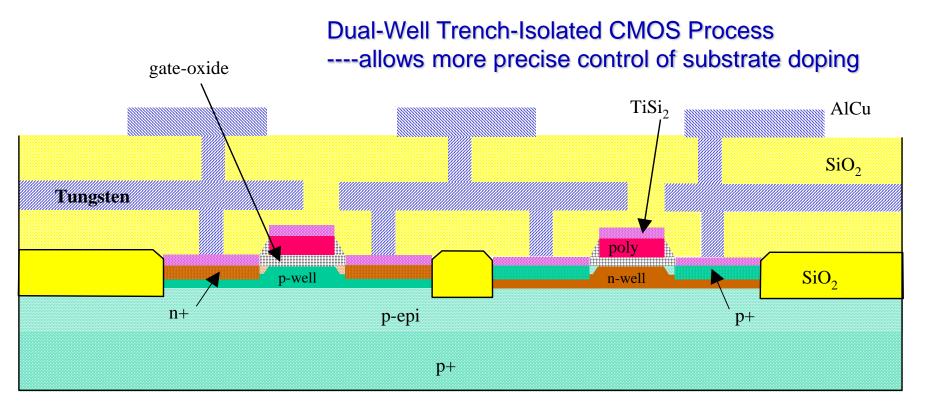

#### A Modern CMOS Process

- > p+ substrate is typical for pure digital circuits....

- For state-of-the-art bulk CMOS processes (say 32 nm)...substrate need not be heavily doped since "Latchup" is not as severe at low Vdd (~1V)

- For RF or high-frequency circuits, substrate is usually lightly doped .....to prevent large eddy current losses in inductors

Lecture 4, ECE 122A, VLSI Principles

#### **Basic Steps-I**

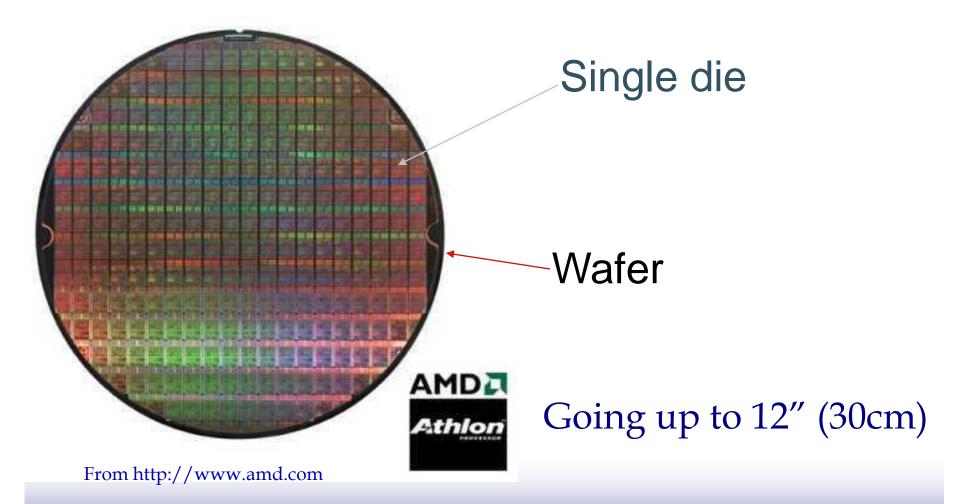

#### Si Wafer:

- Single-crystalline, lightly-doped wafer (6-12 inch diameter)

- Thickness of at most 1mm

- Obtained by cutting a single crystal ingot into thin slices

- An epitaxial layer is grown over the surface of the wafers before device processing

- A starting p- wafer has a typical resistivity of 25-50 Ohm-cm, which corresponds to a doing level of the order of 10<sup>15</sup> cm<sup>-3</sup>

- Defect density must be very low

- Well dopings are of the order of 10<sup>16</sup> to 10<sup>17</sup> cm<sup>-3</sup> (this explains the lower doping of the p substrate

- Crystal orientation: all ICs are manufactured using (100) surface orientation. Why? (fewer imperfections on a (100) surface....gives significantly better Si/SiO<sub>2</sub> interface)

#### **Basic Steps-II**

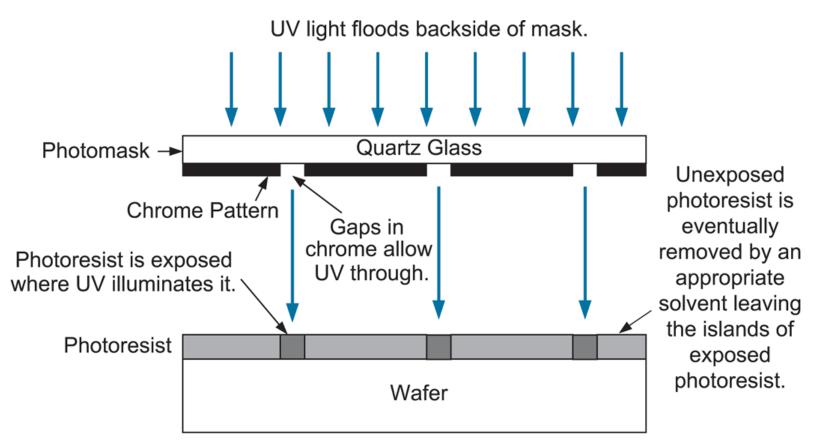

#### Photolithography:

- Applied throughout the manufacturing process

- In each processing step, a certain area of the chip needs to be masked out---using an appropriate optical mask

- Desired processing step can be selectively applied to the remaining regions

- Needed for a number of processing steps:

- oxidation, etching, metal and polysilicon deposition, ion implantation

- Different operations involved in a typical photolithographic process

- Oxidation layering, photoresist (PR) coating, stepper exposure, PR development and bake, acid etching, spin-rinse-dry

Negative PR: a light sensitive polymer that is originally soluble in an organic solvent, but has the property that the polymers cross-link when exposed to light, making the affected areas insoluble.

Positive PR: originally insoluble but soluble after exposure

#### **Photolithography:**

#### Photomasking with negative photoresist

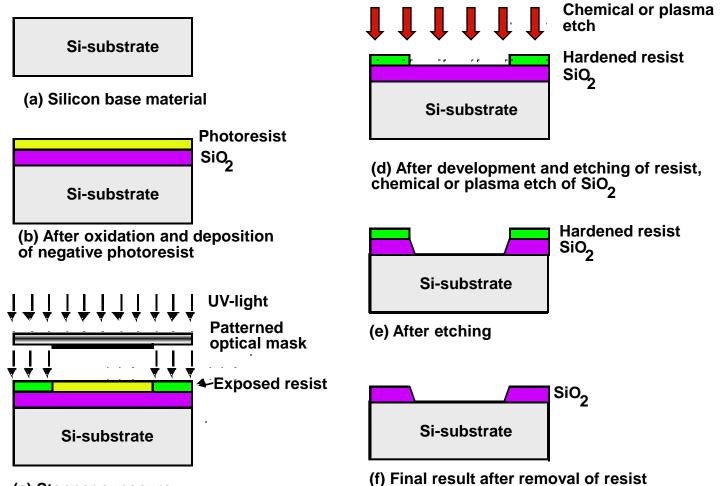

## **Patterning of SiO2**

(c) Stepper exposure

Lecture 4, ECE 122A, VLSI Principles

#### **Recurring Process Steps-I**

#### Diffusion

- Wafers placed in quartz tube embedded in a heated furnace (900-1100 C)

- Dopants introduced through a gas

- Dopants diffuse into the exposed surface

- Final dopant concentration greatest at the surface and decreases in a gaussian profile deeper into the material

#### □ Ion Implantation:

- Dopants are introduced as ions in the material

- Implantation system directs and sweeps a beam of purified ions over the Si surface

- Wafer needs annealing (wafer is heated to 1000 C for 15-30 minutes) to repair lattice damage and to activate the dopants

#### **Recurring Process Steps-II**

#### Deposition

- Many of the materials (gate oxide, silicon nitride, poly etc) are directly deposited

- Using a chemical deposition process (CVD etc)

- □ Etching:

- Wet etching: uses acid or basic solutions

- Dry etching: uses plasma (like sandblasting...)

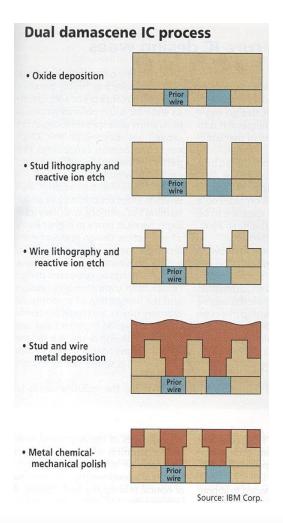

- Planarization

- Surfaces must be flat

- Chemical Mechanical Polishing (CMP) before deposition

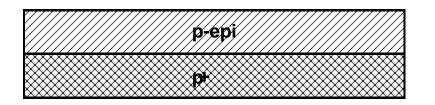

(a) Base material: p+ substrate with p-epi layer

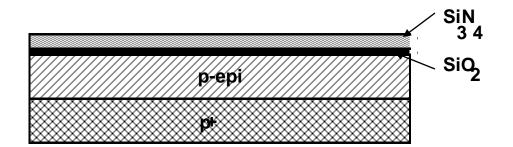

(b) After deposition of gate-oxide and sacrificial nitride (acts as a buffer layer)

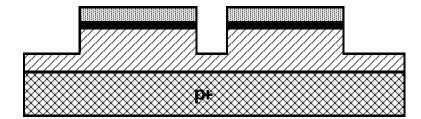

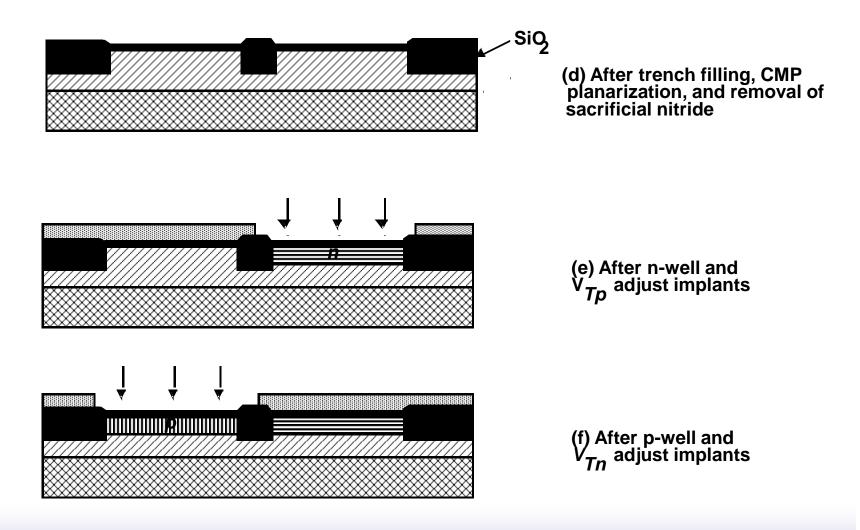

(c) After plasma etch of insulating trenches using the inverse of the active area mask

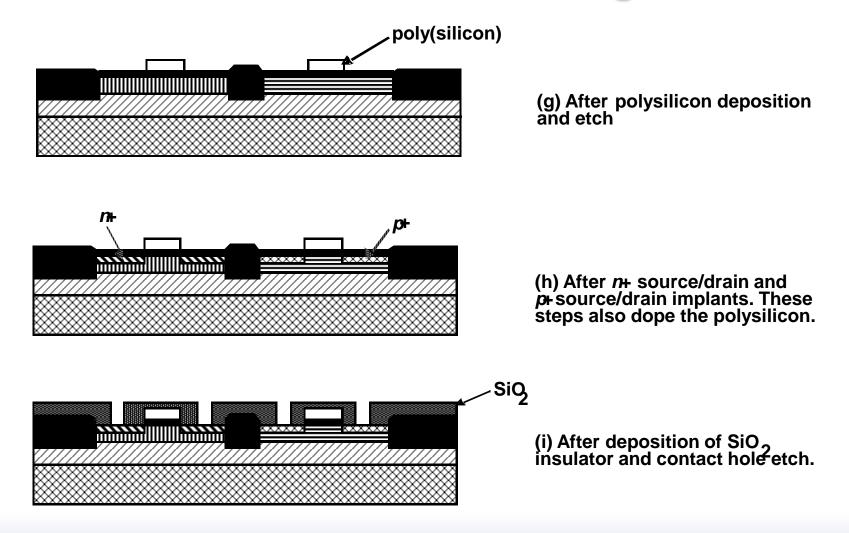

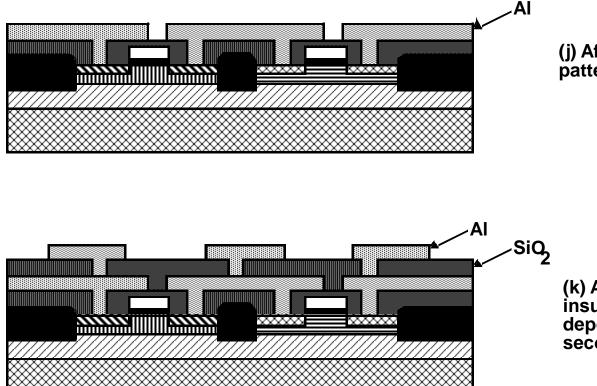

(j) After deposition and patterning of first Al layer.

(k) After deposition of SiO insulator, etching of via's, <sup>2</sup> deposition and patterning of second layer of Al.

#### **Advanced Metallization: Cu based**

#### Lecture 4, ECE 122A, VLSI Principles

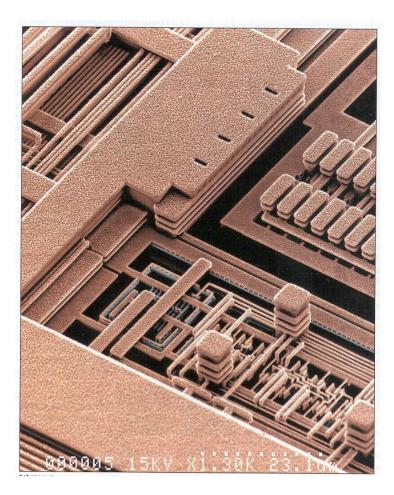

#### **Fully Processed Wafer**

Lecture 4, ECE 122A, VLSI Principles

## **Packaging Requirements**

Electrical: Low parasitics

Mechanical: Reliable and robust

Thermal: Efficient heat removal

Economical: Cheap

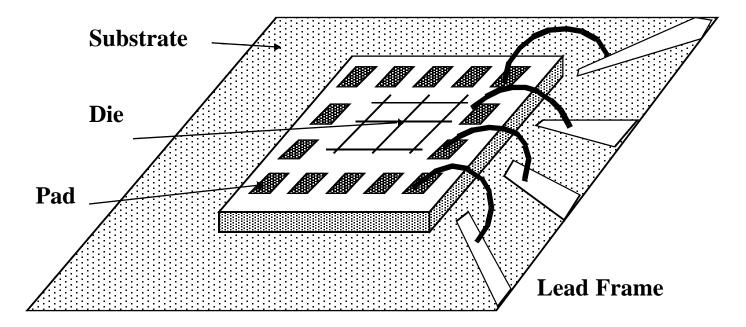

#### **Bonding Techniques** Wire Bonding

Less reliable.... More parasitics....difficult to predict

Lecture 4, ECE 122A, VLSI Principles

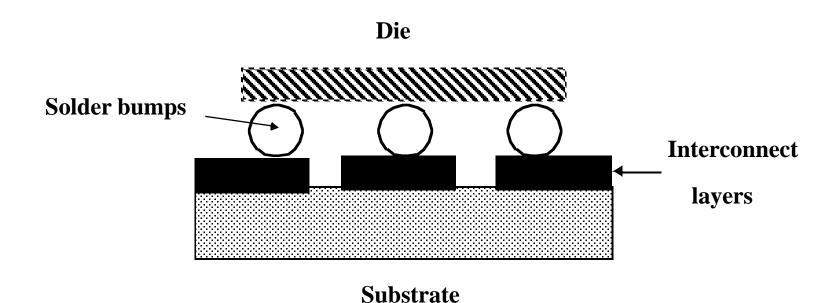

## **Flip-Chip Bonding**

Less parasitics.....more reliable

Lecture 4, ECE 122A, VLSI Principles

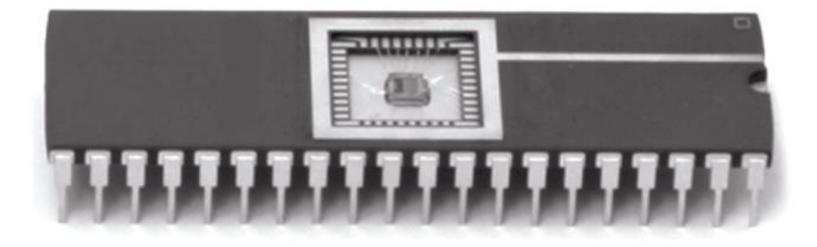

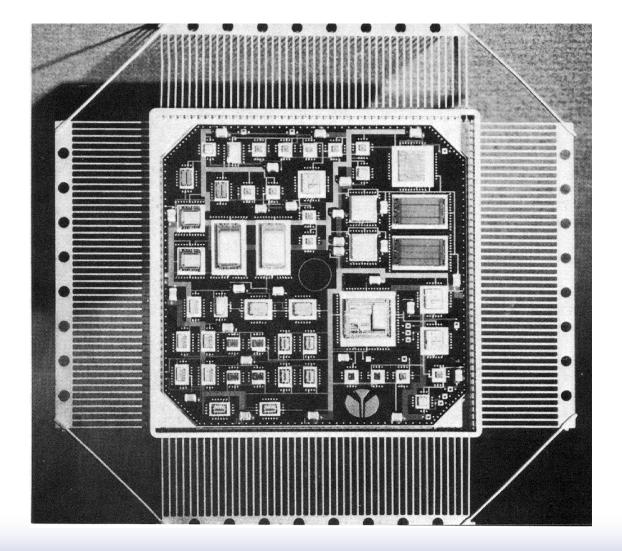

#### Packaged Chip...

#### FIG 1.71 Chip in a 40-pin dual-inline package

Lecture 4, ECE 122A, VLSI Principles

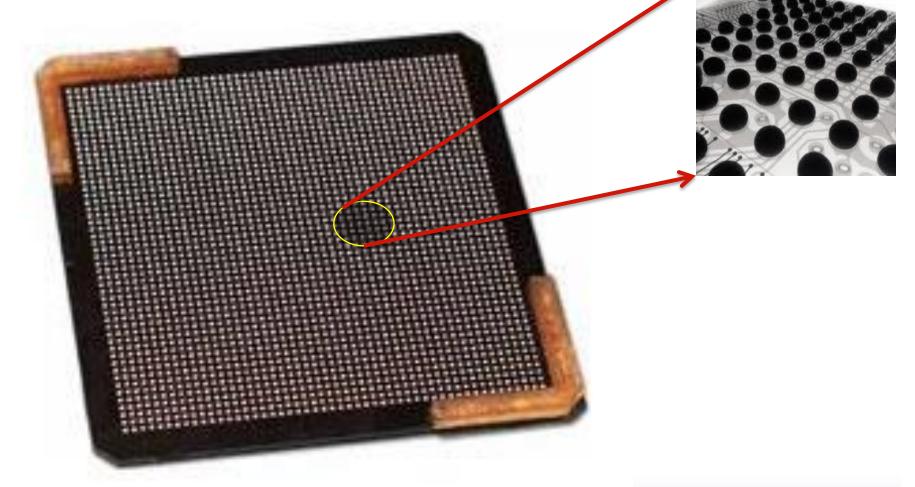

## Ball-Grid Array (BGA)....

Lecture 4, ECE 122A, VLSI Principles

#### **Package Parameters**

| Package Type           | Capacitance<br>(pF) | Inductance<br>(nH) |

|------------------------|---------------------|--------------------|

| 68 Pin Plastic DIP     | 4                   | 35                 |

| 68 Pin Ceramic DIP     | 7                   | 20                 |

| 256 Pin Pin Grid Array | 5                   | 15                 |

| Wire Bond              | 1                   | 1                  |

| Solder Bump            | 0.5                 | 0.1                |

Typical Capacitances and Inductances of Various Package and Bonding Styles (from [Sze83])

## **Multi-Chip Modules**

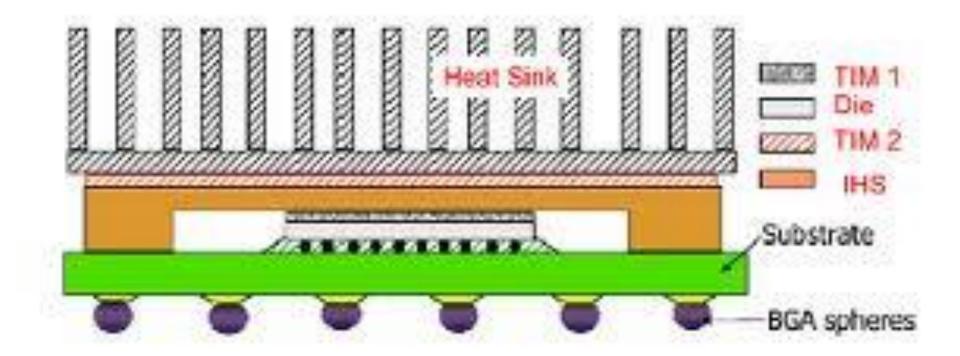

# Cross-Section of a Packaged Chip with Heat-Sink

Note: heat sink is attached to the back-side of the chip ....

Lecture 4, ECE 122A, VLSI Principles

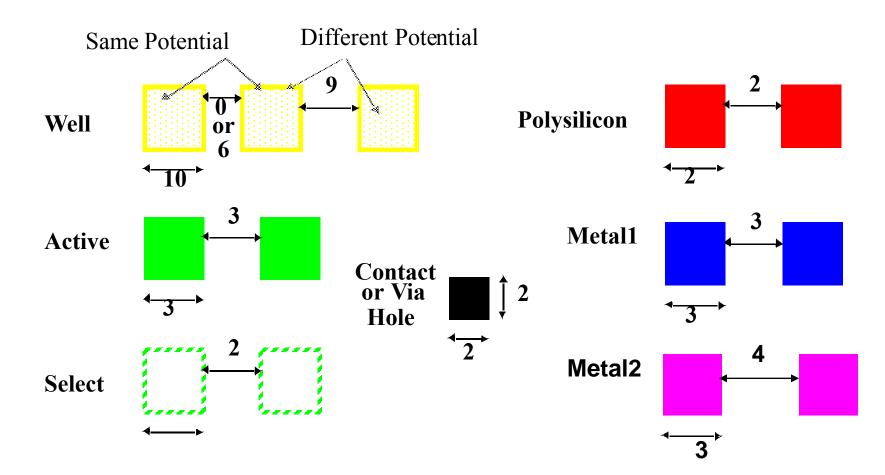

#### **Design Rules....how small? How close?**

- □ Interface between designer and process engineer

- Design rules are also determined based on reliability and manufacturability issues

- Guidelines for constructing process masks

- Unit dimension: Minimum poly-Si or metal-gate line width (L)

- absolute dimensions (micron rules)

- Used in industry, difficult to migrate from process to process

- scalable design rules: lambda ( $\lambda$ ) parameter

- Used mostly in academic research,  $\lambda = L/2$ , more conservative....round up dimensions to an integer multiple of  $\lambda$ , but makes process migration easier...by simply changing value of  $\lambda$

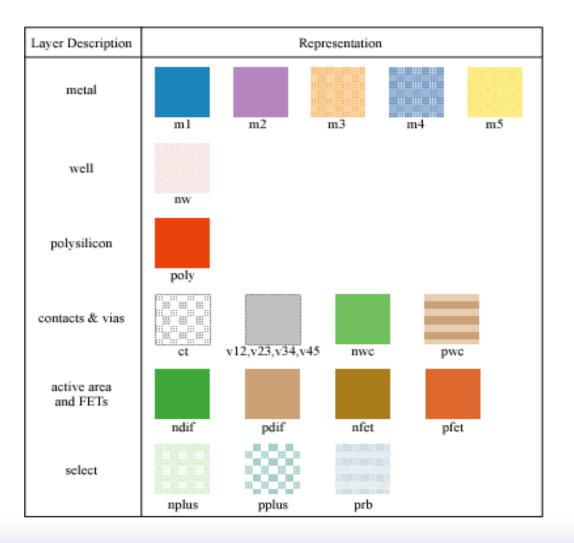

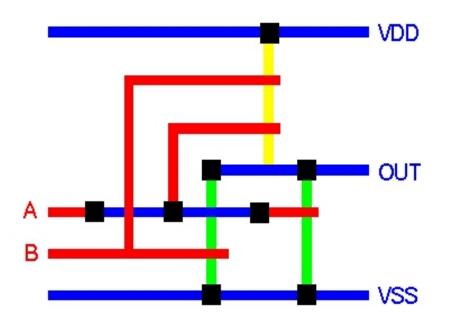

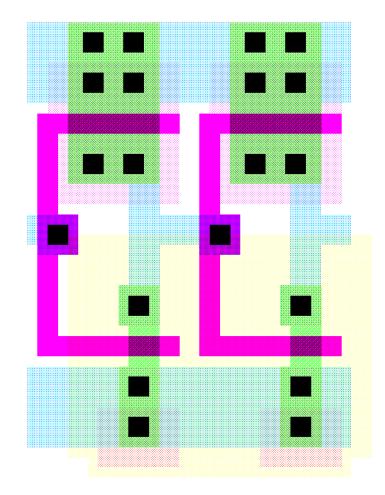

## **CMOS Process Layers**

| Layer                | Color   | Representation |

|----------------------|---------|----------------|

| Well (p,n)           | Yellow  |                |

| Active Area (n+,p+)  | Green   |                |

| Select (p+,n+)       | Green   | <u>(</u> )     |

| Polysilicon          | Red     |                |

| Metal1               | Blue    |                |

| Metal2               | Magenta |                |

| Contact To Poly      | Black   |                |

| Contact To Diffusion | Black   |                |

| Via                  | Black   |                |

## Layers in 0.25 µm CMOS process

Lecture 4, ECE 122A, VLSI Principles

#### **Intra-Layer Design Rules**

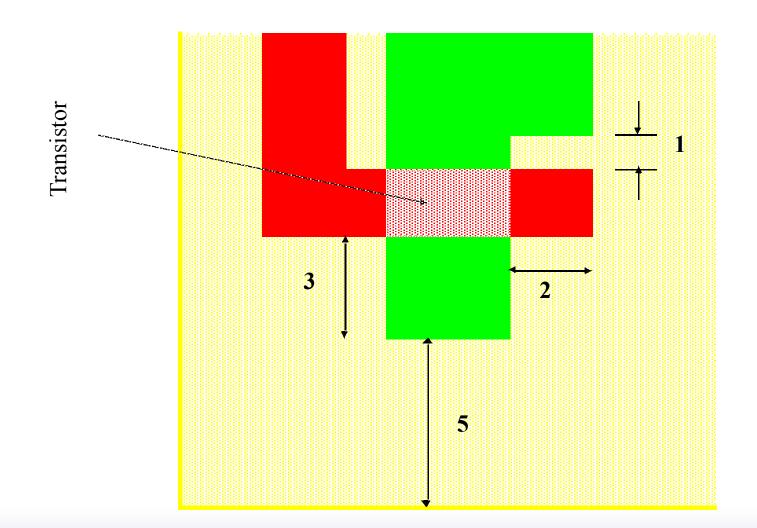

#### **Transistor Layout**

Lecture 4, ECE 122A, VLSI Principles

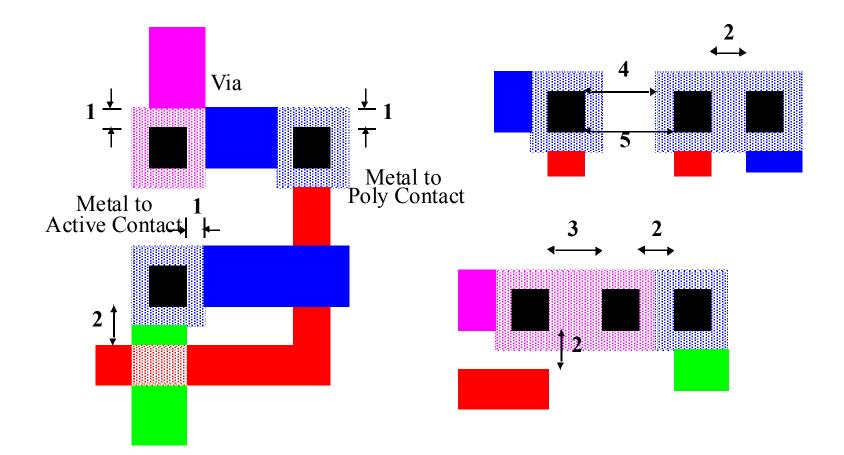

#### Vias and Contacts

## Select Layer...an interface for generating the mask

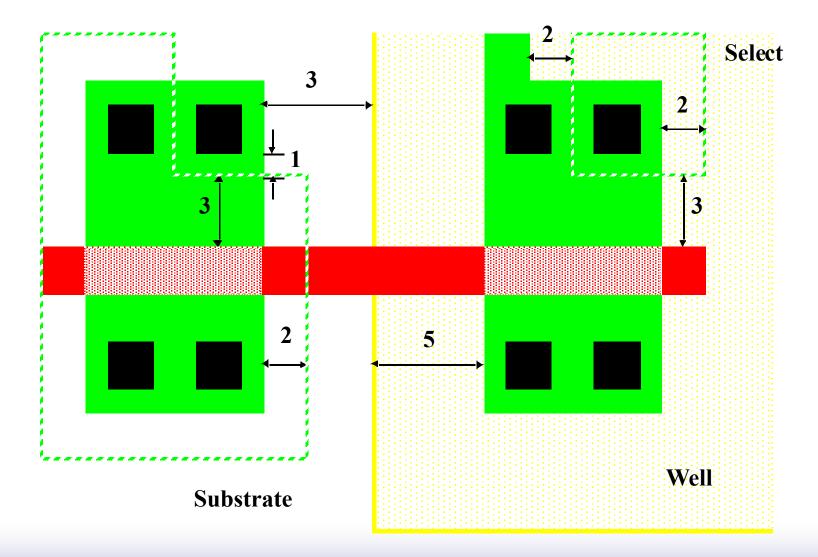

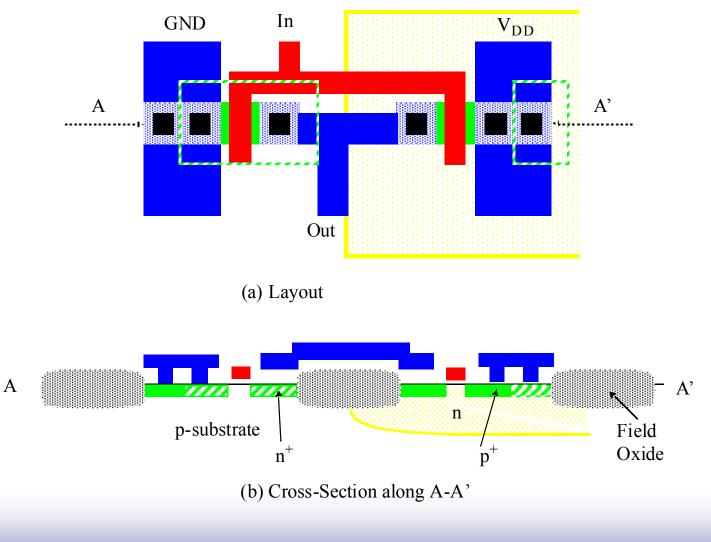

#### **CMOS Inverter Layout**

Lecture 4, ECE 122A, VLSI Principles

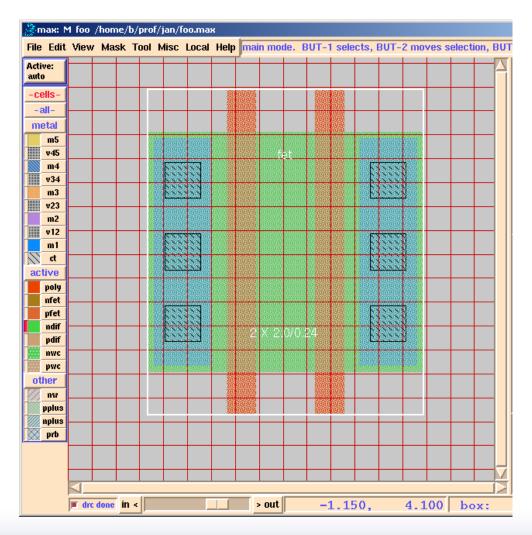

## Layout Editor....MAX

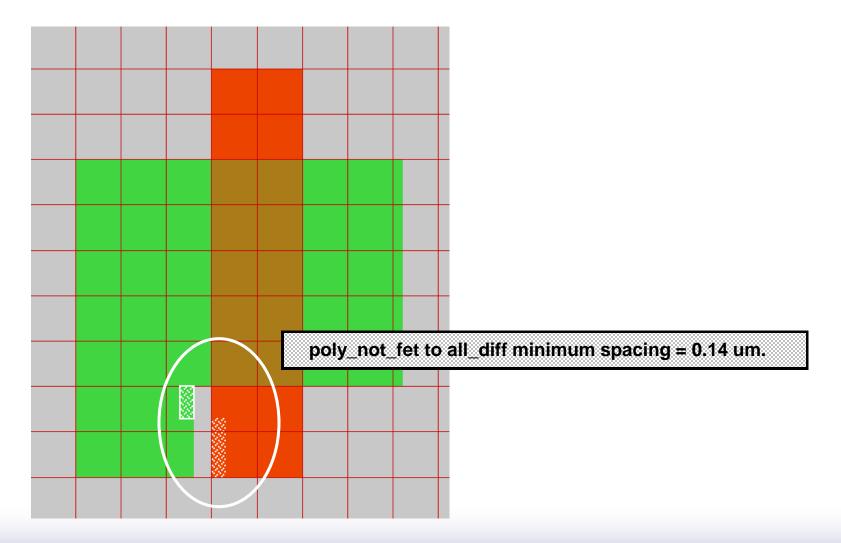

#### **Design Rule Checker**

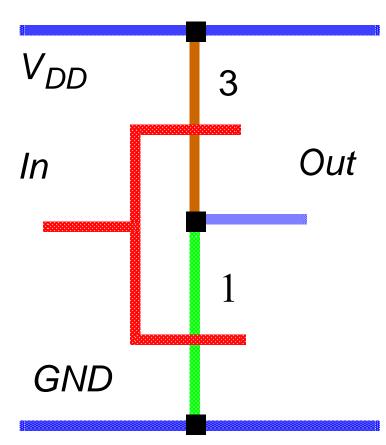

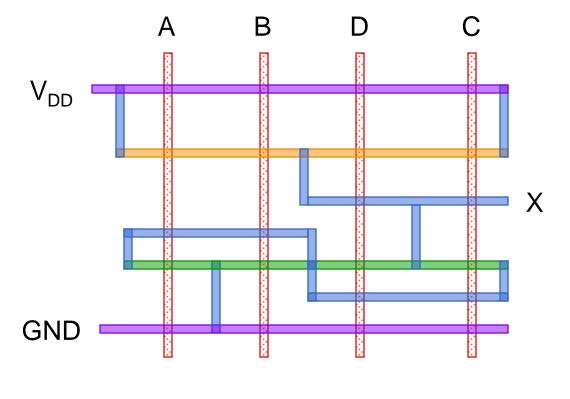

#### Stick Diagram.... Cartoon of a layout

## Allows quick layout planning & area estimation without detailed layout

- Dimensionless layout entities

- Only topology is important

- Determine height and width of cell by counting number of wire tracks and multiplying by wire pitch (width+spacing)

#### Stick diagram of CMOS inverter

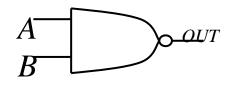

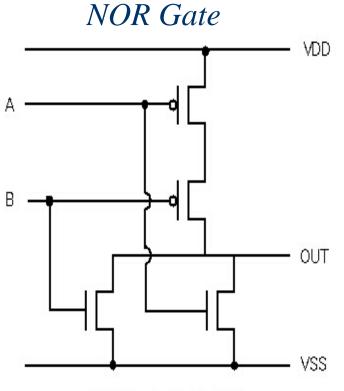

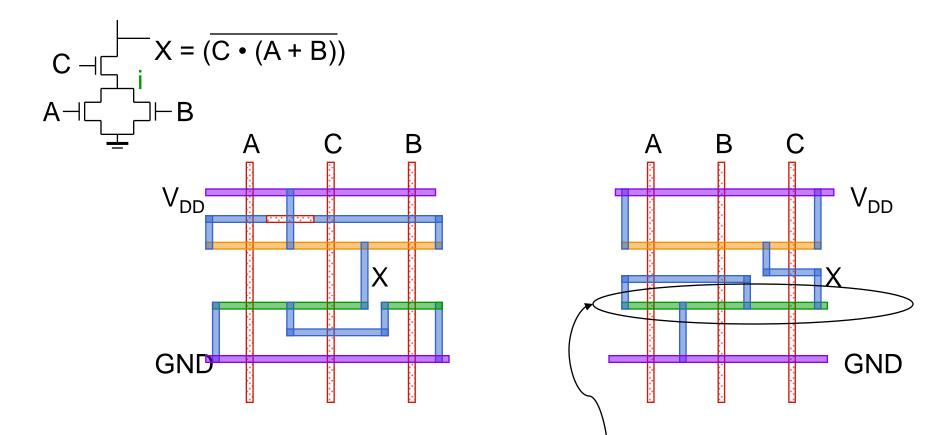

## Stick Diagram....2-input NOR

Stick diagram of 2-input CMOS NOR

NOR gate in CMOS

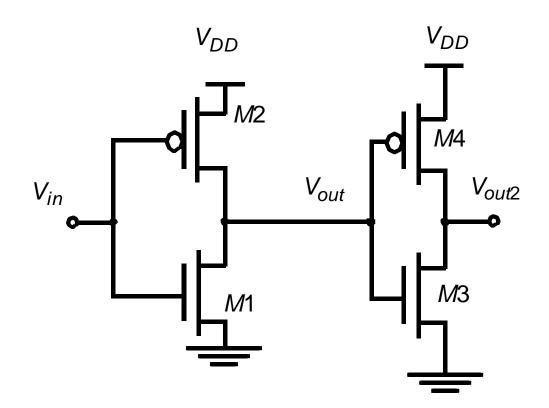

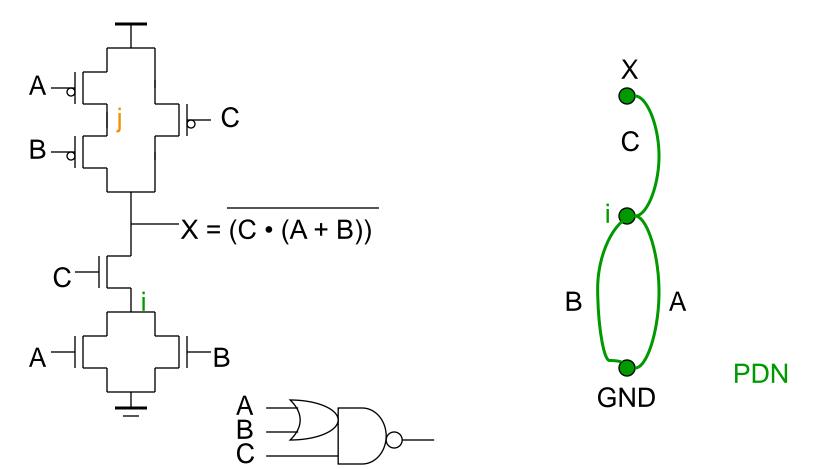

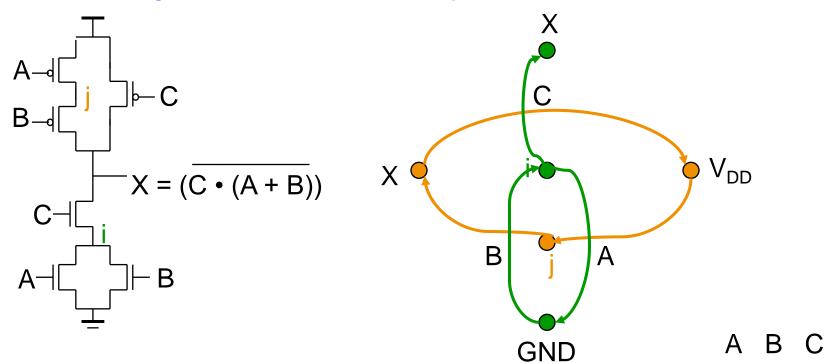

#### **Circuit Under Design**

Lecture 4, ECE 122A, VLSI Principles

#### **Its Layout View**

Lecture 4, ECE 122A, VLSI Principles

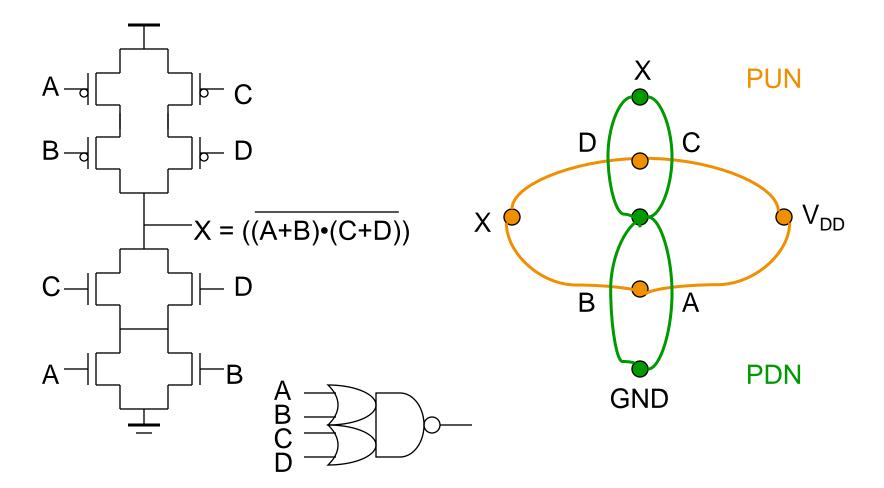

#### **Euler Paths...**

A graph is said to be containing an Euler path if it can be traced in 1 sweep without lifting the pencil from the paper and without tracing the same edge more than once.

Vertices may be passed through more than once. The starting and ending points need not be the same.

An Euler circuit is similar to an Euler path, except that the starting and ending points must be the same.

## Two Stick Layouts of (C • (A + B))

uninterrupted diffusion strip

#### Logic Graph

#### **Consistent Euler Path**

- An uninterrupted diffusion strip is possible only if there exists a Euler path in the logic graph

- Euler path: a path through all nodes in the graph such that each edge is visited once and only once.

For a single poly strip for every input signal, the Euler paths in the PUN and PDN must be consistent (the same)

Lecture 4, ECE 122A, VLSI Principles

Logic Graph

$$X = ((A+B)\bullet(C+D))$$

Lecture 4, ECE 122A, VLSI Principles