# ECE 122A VLSI Principles Lecture 9

Prof. Kaustav Banerjee Electrical and Computer Engineering University of California, Santa Barbara *E-mail: kaustav@ece.ucsb.edu*

Lecture 9, ECE 122A, VLSI Principles

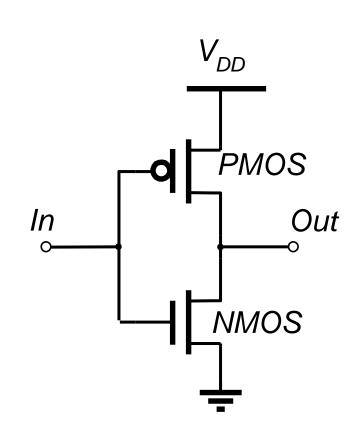

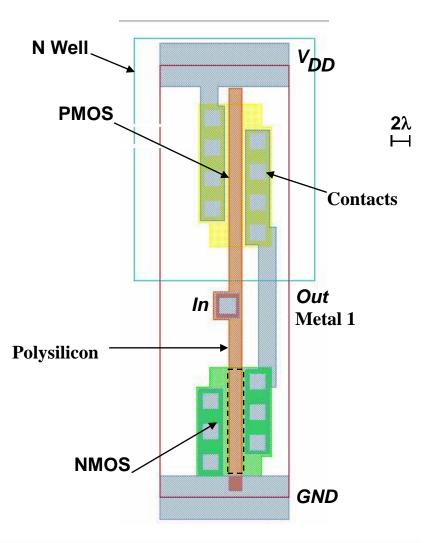

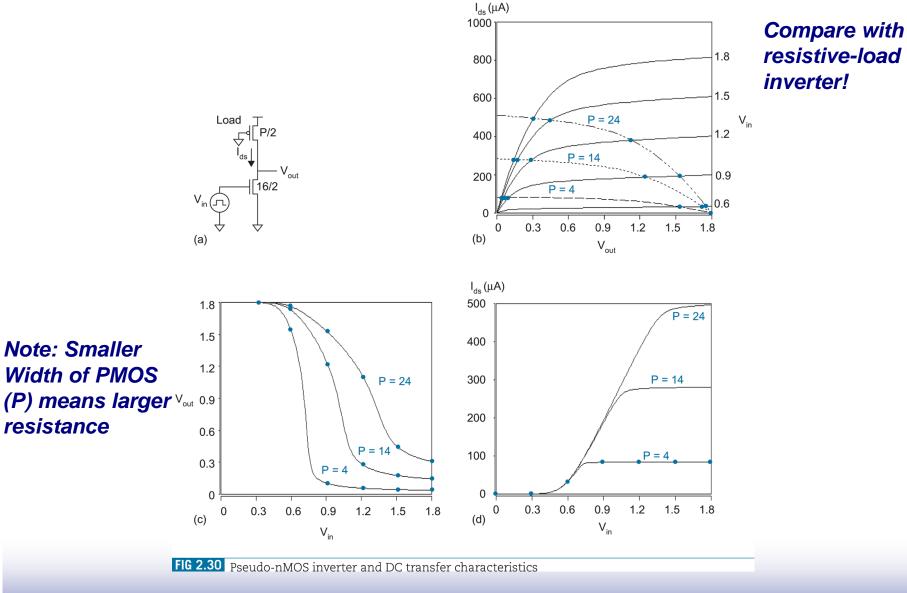

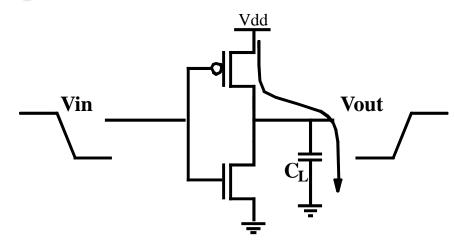

# **CMOS Inverter**

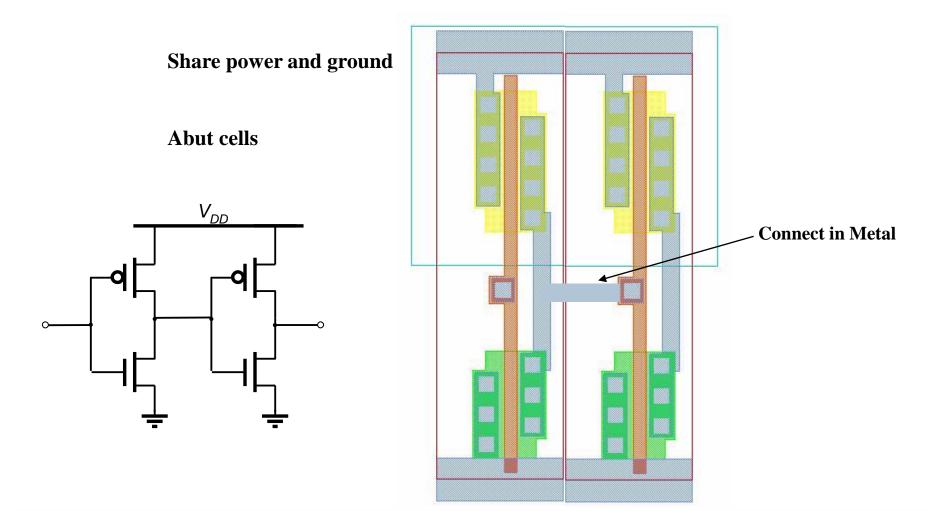

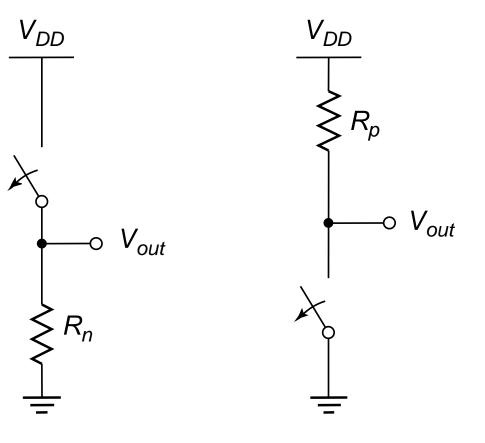

### **Two Inverters**

#### **CMOS Inverter First-Order DC Analysis**

$V_{OL} = 0$  $V_{OH} = V_{DD}$  $V_M = f(R_n, R_p)$

$V_{in} = V_{DD}$

Lecture 9, ECE 122A, VLSI Principles

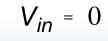

#### **CMOS Inverter: Transient Response**

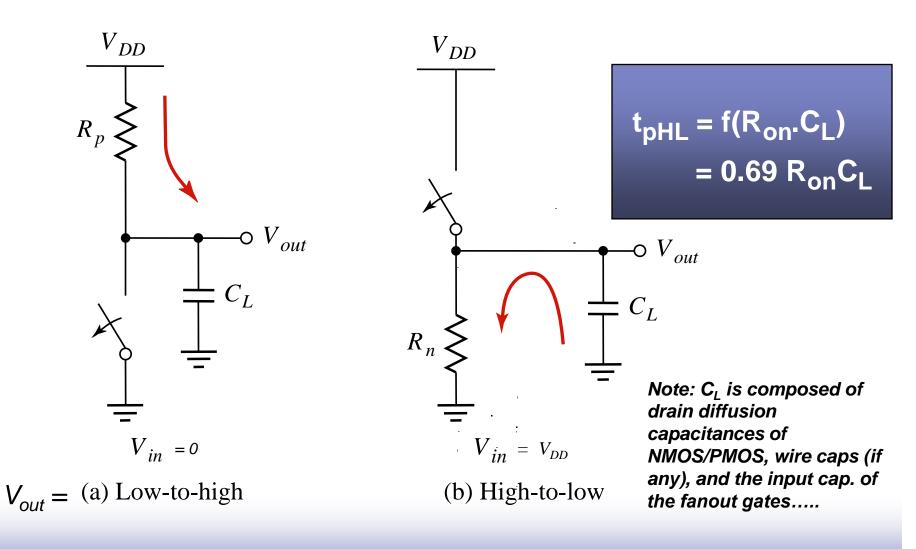

#### The Transistor as a Switch

Lecture 9, ECE 122A, VLSI Principles

#### The Transistor as a Switch

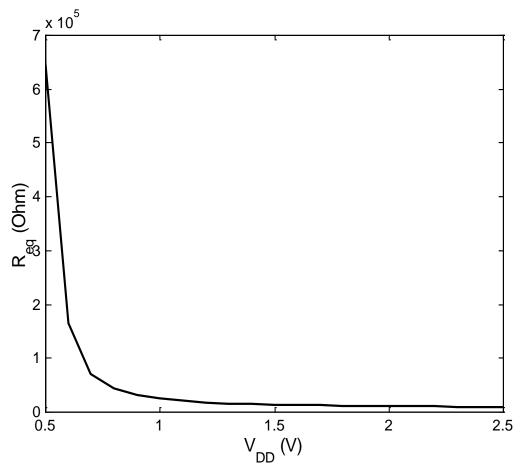

As  $V_{DD}$  increases, drain current increases....for both NMOS and PMOS

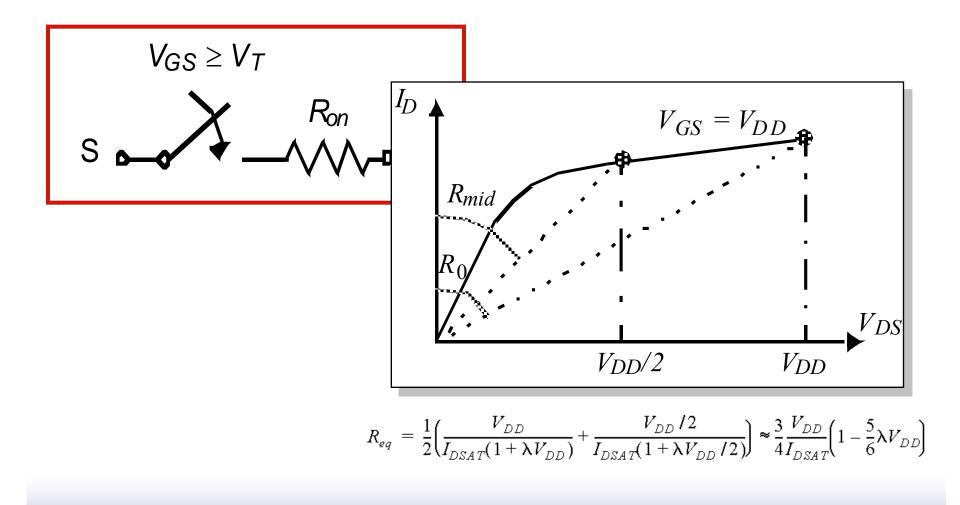

# The Transistor as a Switch

**Table 3.3** Equivalent resistance  $R_{eq}$  (*W*/*L*= 1) of NMOS and PMOS transistors in 0.25 µm CMOS process (with  $L = L_{min}$ ). For larger devices, divide  $R_{eq}$  by *W*/*L*.

| $V_{DD}$ (V) | 1   | 1.5 | 2  | 2.5 |

|--------------|-----|-----|----|-----|

| NMOS (kΩ)    | 35  | 19  | 15 | 13  |

| PMOS (kΩ)    | 115 | 55  | 38 | 31  |

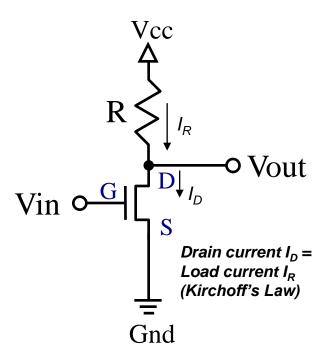

# **Resistive-load Inverter**

- Requires only NMOS transistor and resistor

- **u** When Vin = 0:

- NMOS is OFF ( $V_{GS} = 0$ )

- No current through NMOS or resistor

- Vout ≈ Vcc

- $\Box$  When Vin = Vcc:

- NMOS is ON (V<sub>GS</sub> = Vcc)

- NMOS ON resistance << R</li>

- Vout ≈ 0

Not suitable for VLSI: large area of R, DC power dissipation.

Remember: if body terminal not shown, it is connected to gnd for NMOS, Vcc for PMOS

Kaustav Banerjee

Lecture 9, ECE 122A, VLSI Principles

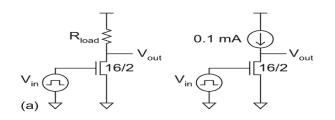

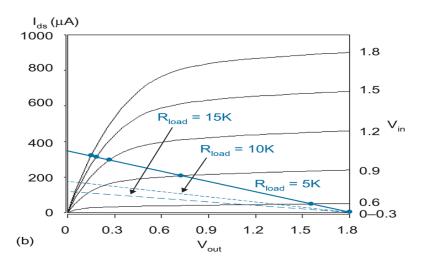

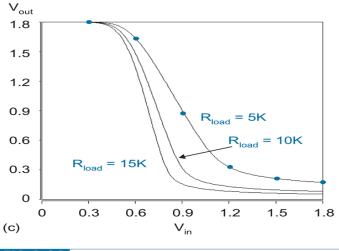

# **Resistive-load Inverter**

$$I_{ds} = V_{cc} / R_{load}$$

Lecture 9, ECE 122A, VLSI Principles

Larger R<sub>load</sub> = smaller PU transistor...LO skewed...

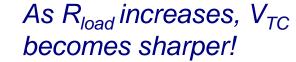

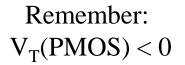

# **Pseudo-NMOS Inverter**

- Replace resistor with "alwayson" PMOS transistor

- Easier to implement in standard process than large resistance value

- PMOS load transistor:

- ON when  $V_{GS} < V_T \rightarrow V_{GS} = -V_{CC}$ : transistor always on

- Linear when  $V_{DS} > V_{GS} V_T \rightarrow V_{out} V_{cc} > -V_{cc} V_T \rightarrow V_{out} > -V_T$

- Saturated when  $V_{DS} < V_{GS} V_T \rightarrow$

$$V_{out}$$

- $V_{cc}$  < - $V_{cc}$ - $V_{T}$   $\rightarrow$   $V_{out}$  < - $V_{T}$

Lecture 9, ECE 122A, VLSI Principle

#### **Pseudo-NMOS Inverter**

Lecture 9, ECE 122A, VLSI Principles

# **Propagation Delay**

Lecture 9, ECE 122A, VLSI Principles

# Two CMOS Inverters...

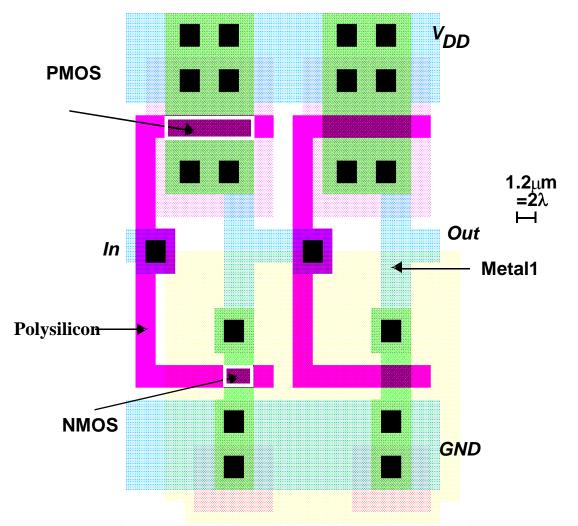

# **CMOS inverter capacitances**

Lecture 9, ECE 122A, VLSI Principles

#### **CMOS inverter capacitances**

$$C_{load} = \underbrace{C_{db,n} + C_{db,p}}_{C_{db,n}} + \underbrace{C_{gd,n} + C_{gd,p}}_{gd,n} + C_{int} + \underbrace{C_{gate}}_{C_{gate}} + \underbrace{C_{gd,n}, C_{gd,p}}_{C_{gd,n}, C_{gd,p}} = \underbrace{C_{gate}}_{WL_{drawn}C_{ox}} + \underbrace{C_{gate}}_{Miller Effect} + \underbrace{C_{gate}}_{For each gate} + \underbrace{C_{gate}}_{For each$$

Lecture 9, ECE 122A, VLSI Principles

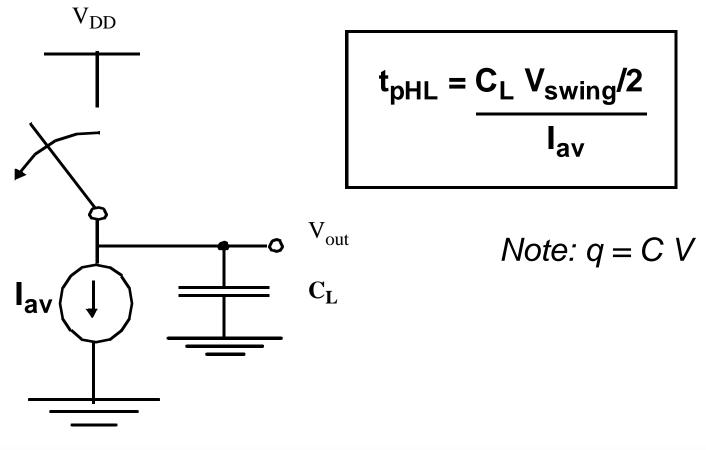

#### **CMOS Inverter Propagation Delay Approach 1**

$V_{in} = V_{DD}$

#### Lecture 9, ECE 122A, VLSI Principles

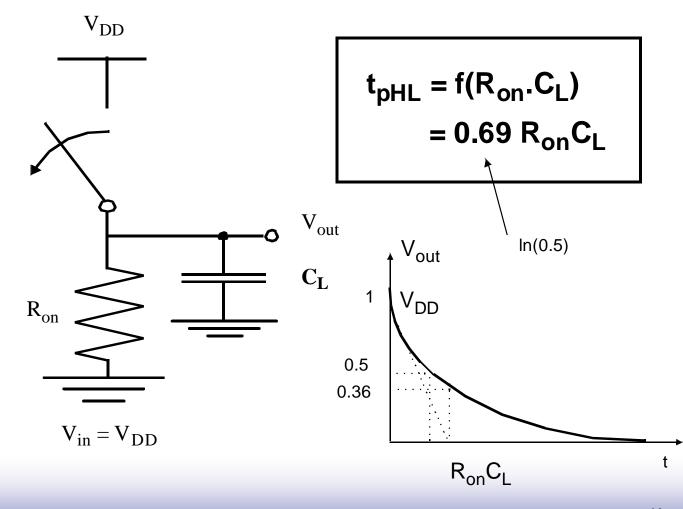

#### **CMOS Inverter Propagation Delay Approach 2**

Lecture 9, ECE 122A, VLSI Principles

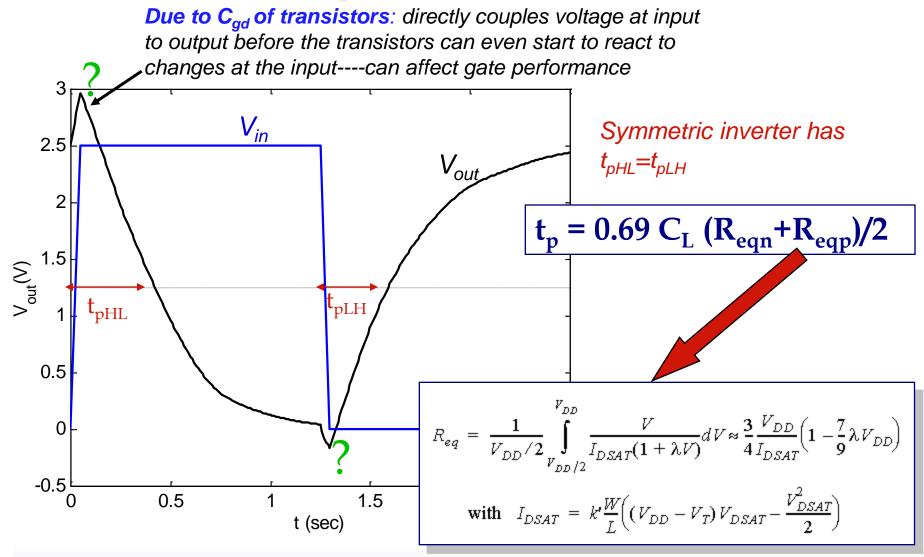

#### **Transient Response**

Lecture 9, ECE 122A, VLSI Principles

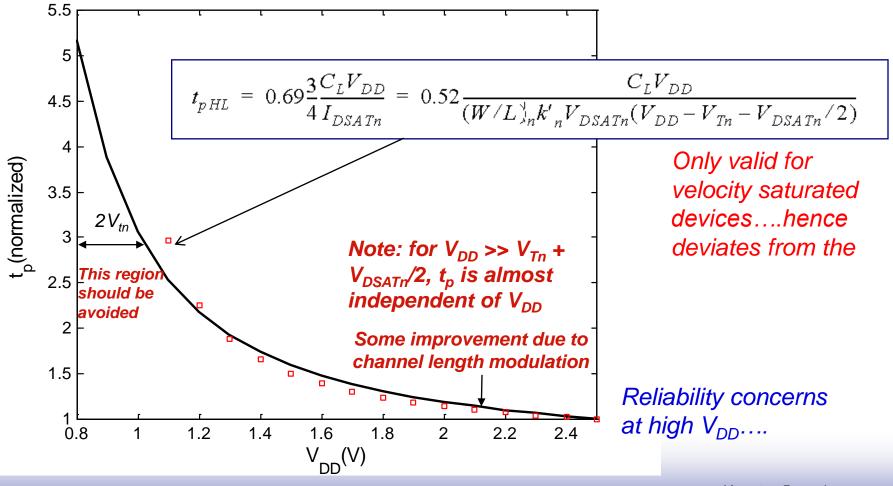

#### **CMOS Inverter Delay as a function of V<sub>DD</sub>**

Same as the ON resistance of a transistor....

Trade off energy dissipation vs performance.....

Lecture 9, ECE 122A, VLSI Principles

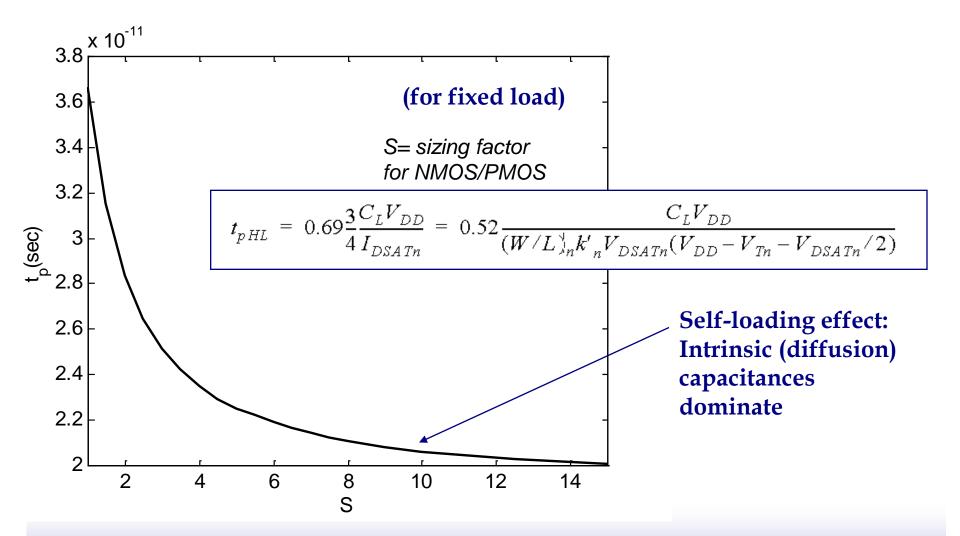

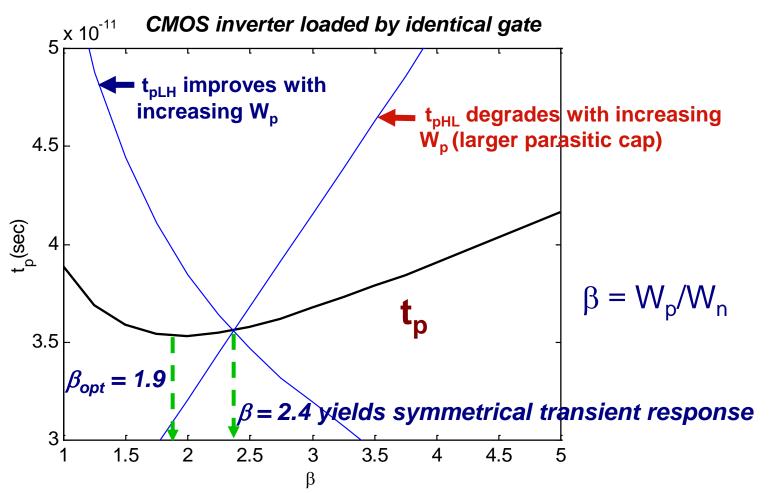

# **Effect of Device Sizing**

#### NMOS/PMOS ratio

If symmetry and noise margins are not of prime concern, inverter delay can be reduced by reducing the width of PMOS....

Lecture 9, ECE 122A, VLSI Principles

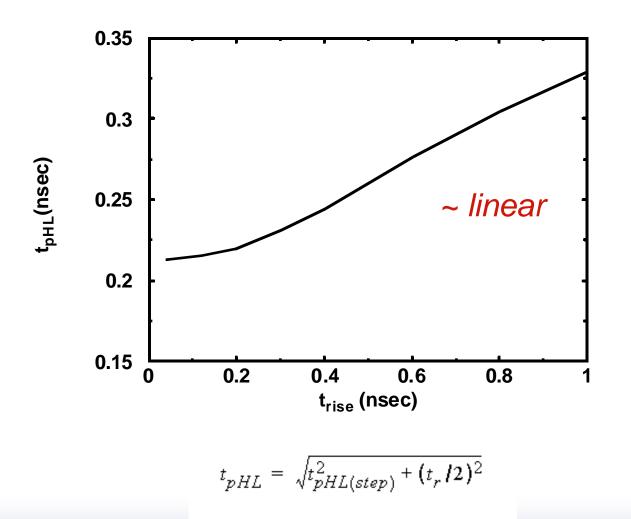

# Impact of Rise Time on Delay

As the input signal changes gradually, both PMOS and NMOS conduct simultaneously....

Lecture 9, ECE 122A, VLSI Principles

# **Design for Performance**

□ Keep load capacitances (C<sub>L</sub>) small

- Recall that three major components contribute to the load cap.

- internal diffusion + overlap caps

- interconnect cap.

- -fan-out (gate cap)

- Increase transistor sizes

- watch out for self-loading!

- □ Increase V<sub>DD</sub> (??)

- watch out for reliability issues!

#### **Power Dissipation**

Lecture 9, ECE 122A, VLSI Principles

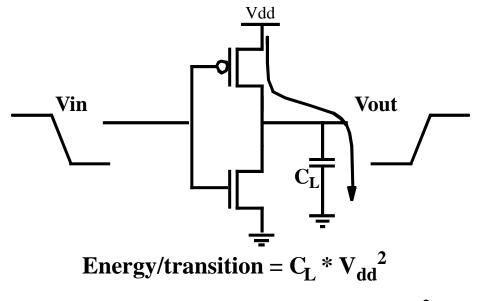

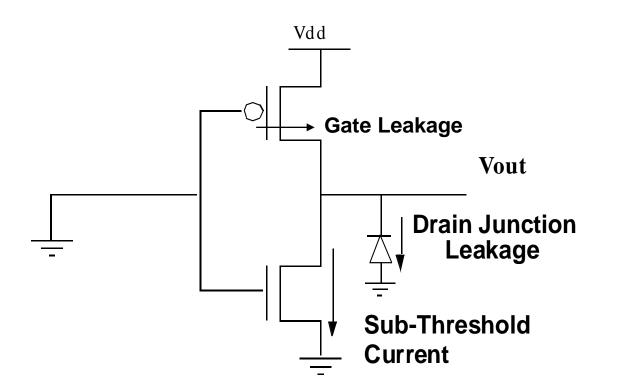

# Where Does Power Go in CMOS?

#### Dynamic Power

Due to charging/discharging of capacitors....

#### Leakage Power

- Subthreshold

- Gate

- Junction

#### Short-Circuit Power

When NMOS and PMOS are both turned ON....

Lecture 9, ECE 122A, VLSI Principles

# **Dynamic Power Dissipation**

Note: Here C<sub>L</sub> is an external capacitor....

Power = Energy/transition  $*f = C_L * V_{dd}^2 * f$

- Energy/transition is not a function of transistor sizes!

- Need to reduce C<sub>L</sub>, V<sub>dd</sub>, and *f* to reduce power.

Energy taken from supply during transition:

$$E_{V_{DD}} = \int_{0}^{\infty} i_{V_{DD}}(t) V_{DD} dt = V_{DD} \int_{0}^{\infty} C_{L} \frac{dv_{out}}{dt} dt = C_{L} V_{DD} \int_{0}^{V_{DD}} dv_{out} = C_{L} V_{DD}^{2}$$

Lecture 9, ECE 122A, VLSI Principles

# **Dynamic Power Dissipation**

Note: during the discharge phase, charge is removed from C<sub>1</sub> and its energy is dissipated in the NMOS

Energy taken from supply during transition:

$$E_{V_{DD}} = \int_{0}^{\infty} i_{V_{DD}}(t) V_{DD} dt = V_{DD} \int_{0}^{\infty} C_{L} \frac{dv_{out}}{dt} dt = C_{L} V_{DD} \int_{0}^{V_{DD}} dv_{out} = C_{L} V_{DD}^{2}$$

Energy stored in the capacitor:

$$E_{C} = \int_{0}^{\infty} i_{V_{DD}}(t) v_{out} dt = \int_{0}^{\infty} C_{L} \frac{dv_{out}}{dt} v_{out} dt = C_{L} \int_{0}^{V_{DD}} v_{out} dv_{out} = \frac{C_{L} V_{DD}^{2}}{2}$$

Where is the other half of the energy? ....Dissipated by the PMOS

Lecture 9, ECE 122A, VLSI Principles

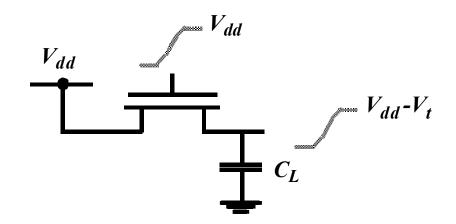

#### Modification for Circuits with Reduced Swing

$$\mathbf{E}_{0 \to 1} = \mathbf{C}_{L} \bullet \mathbf{V}_{dd} \bullet (\mathbf{V}_{dd} - \mathbf{V}_{t})$$

• Can exploit reduced swing to lower power (e.g., reduced bit-line swing in memory)

Lecture 9, ECE 122A, VLSI Principles

# **Primary Leakage Mechanisms**

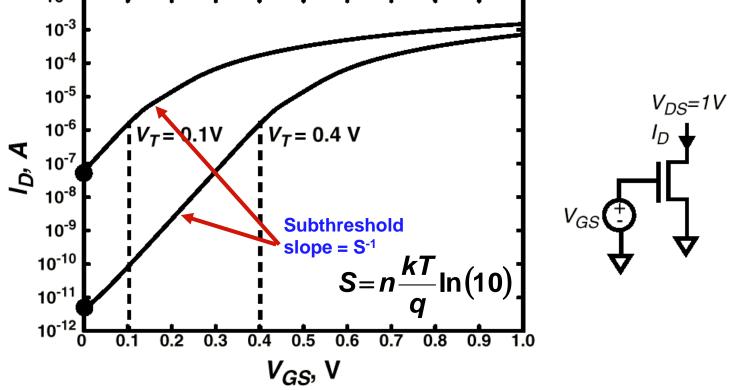

Sub-threshold current one of most compelling issues in low-energy circuit design!

#### Subthreshold Leakage Component

Subthreshold Slope = S = 60 mv/decade (for ideal transistor with n=1) 10<sup>-2</sup>

Leakage control is critical for low-voltage operation

Lecture 9, ECE 122A, VLSI Principles

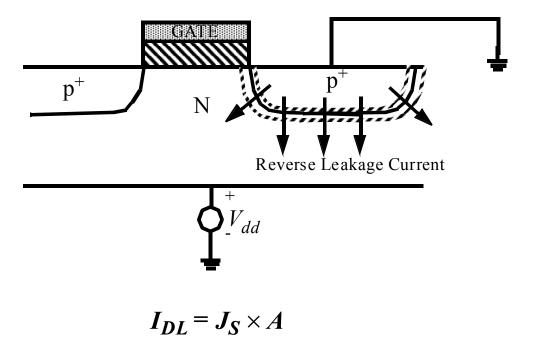

#### **Reverse-Biased Diode Leakage**

$JS = 10-100 \text{ pA}/\mu\text{m2}$  at 25 deg C for  $0.25\mu\text{m}$  CMOS JS doubles for every 9 deg C!

Lecture 9, ECE 122A, VLSI Principles

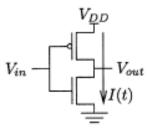

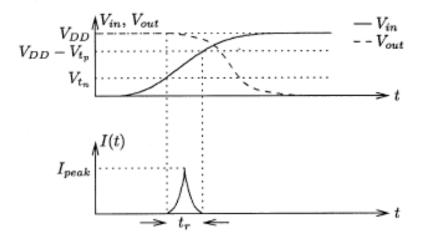

# **Short Circuit Currents**

(a) CMOS

inverter.

(b) Voltage and current waveforms.

K. Banerjee and A. Mehrotra, IEEE Transactions on Electron Devices, Vol. 49, No. 11, 2002.

Fig. 5. Voltage and current waveforms of a CMOS inverter.

Lecture 9, ECE 122A, VLSI Principles

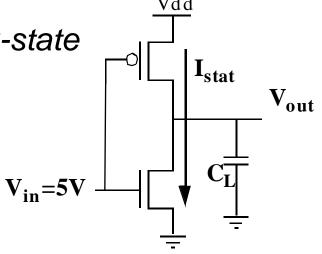

# **Static Power Consumption**

In the absence of switching....steady-state operation

Sources:

Due to all previously mentioned leakage currents.....

$P_{stat} = P_{(In=1)} V_{dd} I_{stat}$

Wasted energy ... Should be avoided in almost all cases, but could help reducing energy in others (e.g. sense amps)

Lecture 9, ECE 122A, VLSI Principles

# Leakage

#### □ Effect of leakage current

- "Wasted" power: power consumed even when circuit is inactive

- Leakage power raises temperature of chip

- Can cause functionality problem in some circuits: memory, dynamic logic, etc.

- Reducing transistor leakage

- Long-channel devices

- Small drain voltage

- Large threshold voltage V<sub>T</sub>

# **Principles for Power Reduction**

□ Prime choice: Reduce voltage!

- Recent years have seen an acceleration in supply voltage reduction

- Design at very low voltages still open question (0.6 ... 0.9 V by 2010!)

- Reduce switching activity

- Reduce physical capacitance

- Device Sizing

# Leakage Power Reduction

#### Process scaling

- V<sub>T</sub> reduces with each new process (historically)

- Leakage increases ~10X!

- □ Leakage vs. performance tradeoff:

- For high-speed, need small  $V_T$  and L

- For low leakage, need high  $V_T$  and large L

- $\Box$  One solution: dual-V<sub>T</sub> process

- Low-V<sub>T</sub> transistors: use in critical paths for high speed

- High-V<sub>T</sub> transistors: use to reduce power

| Parameters                                                                                                   |                                                         | Constant Vdd<br>scaling                        | Constant E<br>scaling               |  |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------|-------------------------------------|--|

|                                                                                                              | Width = w                                               | 0                                              | 0.7                                 |  |

| Dimentions                                                                                                   | Length = L                                              | 0                                              | 0.7                                 |  |

|                                                                                                              | Oxide thickness t <sub>ox</sub>                         | 0                                              | 0.7                                 |  |

|                                                                                                              | Junction depth X <sub>j</sub>                           | 0                                              | 0.7                                 |  |

| Die Area                                                                                                     |                                                         | (0.                                            | $(0.7)^2$                           |  |

| Gate capacitance per unit area ( $C_{gox} = \frac{\varepsilon_{ox}}{t_{ox}}$ )                               |                                                         | $\frac{1}{0}$                                  | $\frac{1}{0.7}$                     |  |

| Gate capacitance ( $C_g = wLC_{gox}$ )                                                                       |                                                         | 0                                              | 0.7                                 |  |

| Total Capacitance ( <i>C</i> )                                                                               |                                                         | 0                                              | 0.7                                 |  |

| Supply Voltage ( $V_{DD}$ )                                                                                  |                                                         | 1                                              | 0.7                                 |  |

| Current per device ( $I_{DS} \propto \frac{W}{L} \frac{\mathcal{E}_{ox}}{t_{ox}} (V_{gs} - V_{th}) V_{DD}$ ) |                                                         | 1                                              | 0.7                                 |  |

| Intrinsic Gate Delay ( $\tau = \frac{C_g \Delta V}{I_{AV}}$ )                                                |                                                         | 0.7                                            | 0.7                                 |  |

| Frequency $(f \propto \frac{1}{\tau})$                                                                       |                                                         | $\frac{1}{0}$                                  | $\frac{1}{0.7}$                     |  |

| Active Power                                                                                                 | Active Power Dissipation ( $P_{active} = CV_{DD}^2 f$ ) |                                                | $(0.7)^2$                           |  |

| Energy-Delay                                                                                                 | Energy-Delay Product ( $CV_{DD}^2 \tau$ )               |                                                | $(0.7)^4 = 0.2401$                  |  |

| Power Dissipation density ( $\frac{P_{active}}{Area}$ )                                                      |                                                         | $(0.7)^2 = 0.49$ $\frac{1}{(0.7)^2} \approx 2$ | $\frac{(0.7)^2}{(0.7)^2} \approx 1$ |  |