# ECE 122A VLSI Principles Lecture 3

Prof. Kaustav Banerjee Electrical and Computer Engineering University of California, Santa Barbara *E-mail: kaustav@ece.ucsb.edu*

Lecture 3, ECE 122A, VLSI Principles

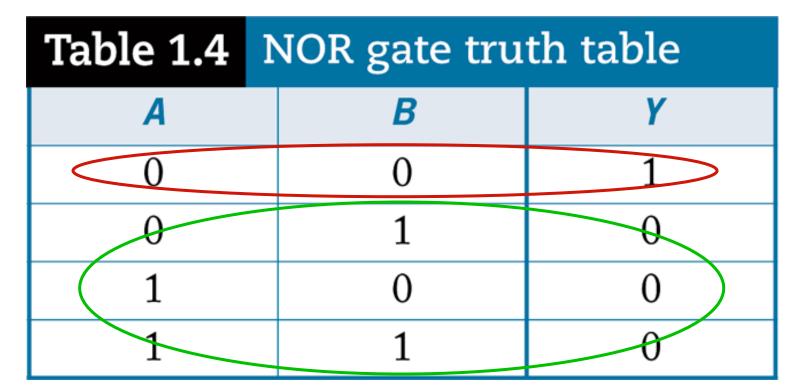

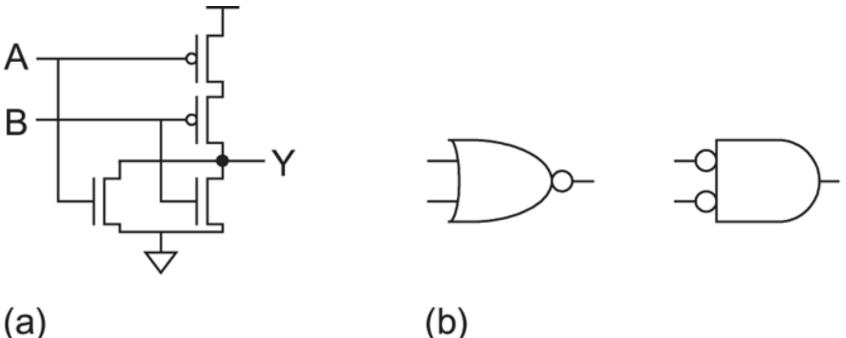

#### 2-input NOR Gate

2-input NOR:  $Y = \overline{A} + \overline{B} = \overline{A} \cdot \overline{B}$

# 2 PMOS must be in series.....2 NMOS must be in parallel....

Lecture 3, ECE 122A, VLSI Principles

Kaustav Banerjee

#### **CMOS NOR Implementation**

(a)

#### FIG 1.15 2-input NOR gate schematic (a) and symbol (b) $Y = \overline{A + B}$

Lecture 3, ECE 122A, VLSI Principles

Kaustav Banerjee

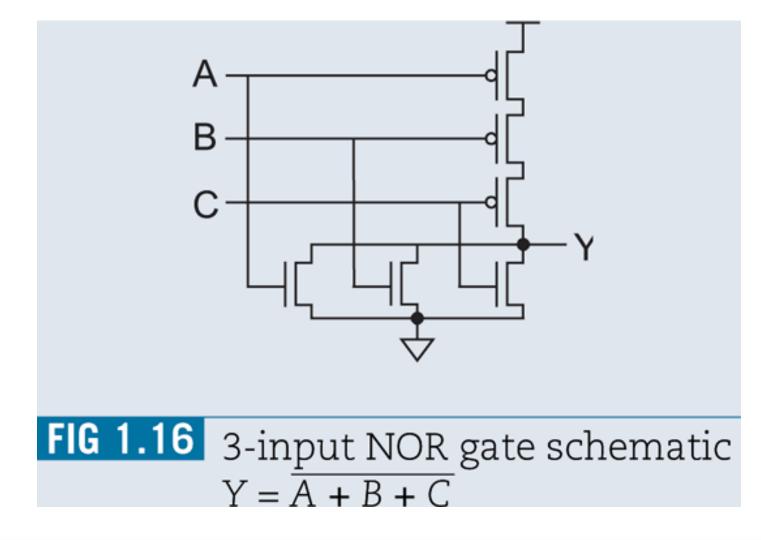

#### **CMOS 3-input NOR Implementation**

Lecture 3, ECE 122A, VLSI Principles

Kaustav Banerjee

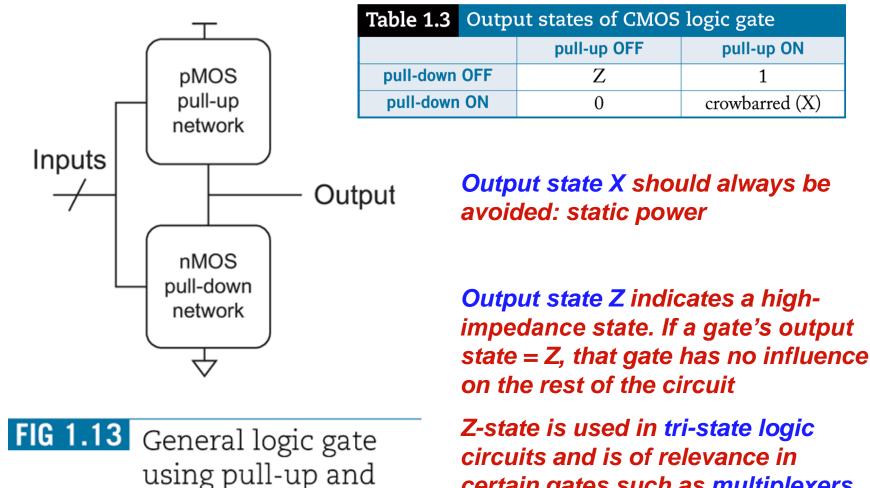

### **Combinational Logic**

pull-down networks

certain gates such as multiplexers

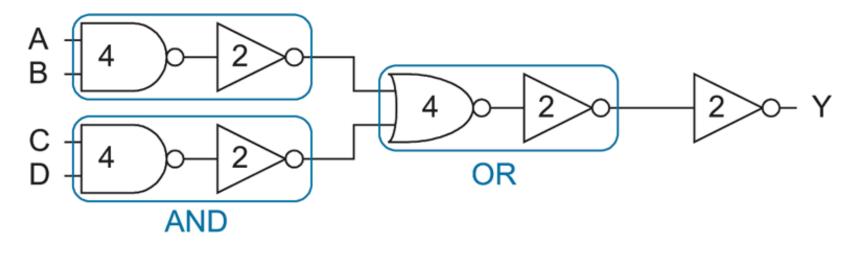

**FIG 1.23** Inefficient discrete gate implementation of AOI22 indicating transistor counts

Lecture 3, ECE 122A, VLSI Principles

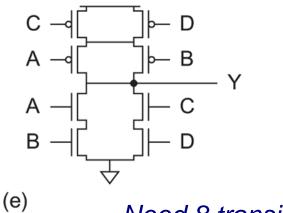

#### **Compound Gates** Y= A.B + C.D

Need 8 transistors

Lecture 3, ECE 122A, VLSI Principles

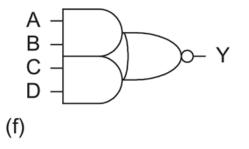

#### **Compound Gates**

Lecture 3, ECE 122A, VLSI Principles

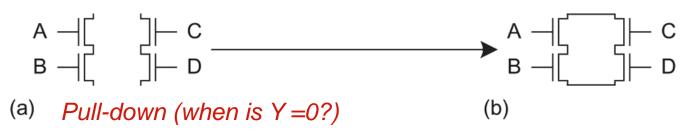

#### **Pass Transistors**

| nMOS | g<br>⊥d         | g = 0<br>s ⊸∽ <b>v</b> ⊸ d | Input $g = 1$ Output $0 \rightarrow strong 0$     |

|------|-----------------|----------------------------|---------------------------------------------------|

|      |                 | g = 1<br>s∞d               | g = 1<br>1 <i>-</i> ⊶⊷-degraded 1                 |

|      | (a)             | (b)                        | (c)                                               |

| pMOS | g<br>↓<br>s ⊥ d | g = 0<br>s _₀_→o_ d        | Input $g = 0$ Output $0 \rightarrow - degraded 0$ |

|      | (d)             | g = 1<br>s∽∕▼₀_ d<br>(e)   | $g = 0$ $1 \rightarrow strong 1$ (f)              |

FIG 1.19 Pass transistor strong and degraded outputs

Lecture 3, ECE 122A, VLSI Principles

Kaustav Banerjee

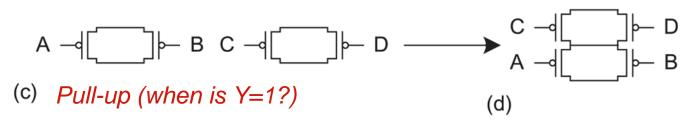

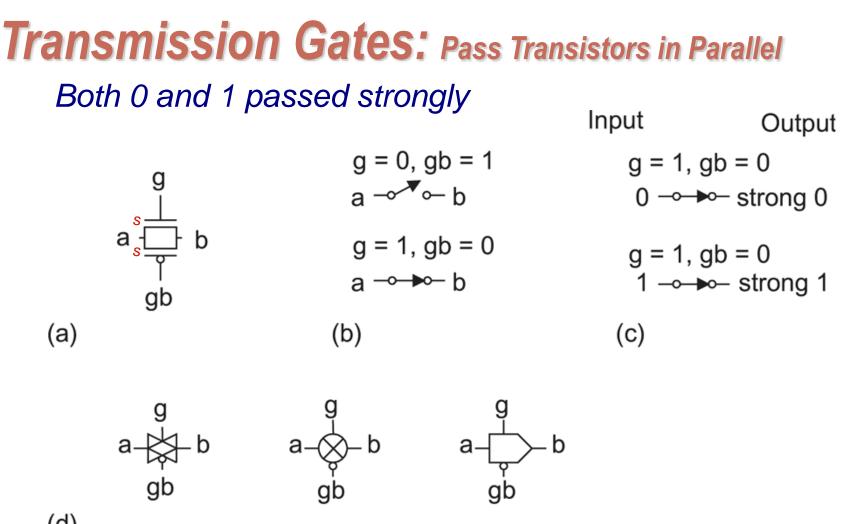

(d)

Double Rail Logic: both the control input and its complement is required

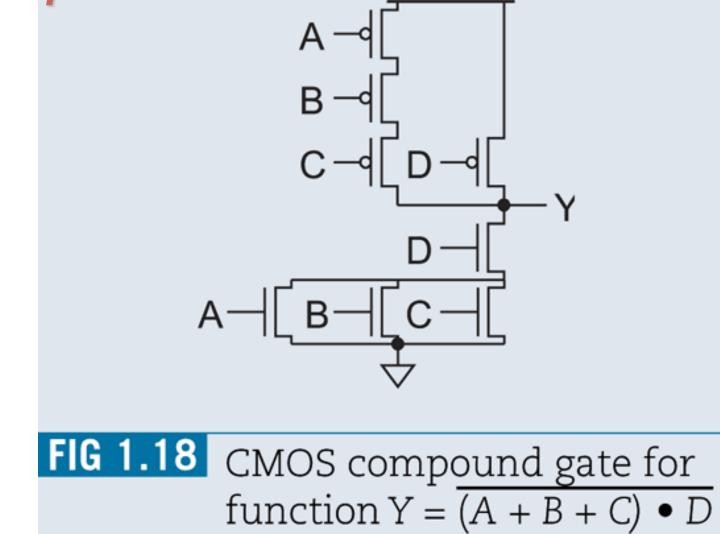

FIG 1.20 Transmission gate

Lecture 3, ECE 122A, VLSI Principles

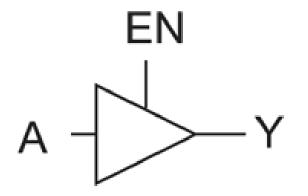

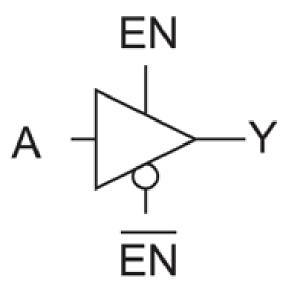

#### **Tristate Buffer**

# FIG 1.24 Tristate buffer symbol

Lecture 3, ECE 122A, VLSI Principles

#### **Tristate Buffer**

| Table 1.5 | Truth table for tristate |   |  |  |

|-----------|--------------------------|---|--|--|

| EN / EN   | A                        | Y |  |  |

| 0/1       | 0                        | Z |  |  |

| 0/1       | 1                        | Z |  |  |

| 1/0       | 0                        | 0 |  |  |

| 1/0       | 1                        | 1 |  |  |

Note: Z indicates a 'high-impedance' third state....

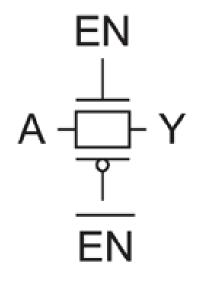

#### **Transmission Gate as Tristate Buffer**

Non-restoring: input-signal will slowly degrade over a number of stages.... since Y is not connected to either Vdd or Gnd

#### **Tristate Buffer as Inverter**

А А Α EN ΕN EN = 1 EN = 0 $Y = \overline{A}$ Y = 'Z'(a) (b) (c) (d)

FIG 1.26 Tristate inverter

Lecture 3, ECE 122A, VLSI Principles

14 Kaustav Banerjee

**Restoring:** O/P (**Y**) is directly connected to **Vdd** or **GND**

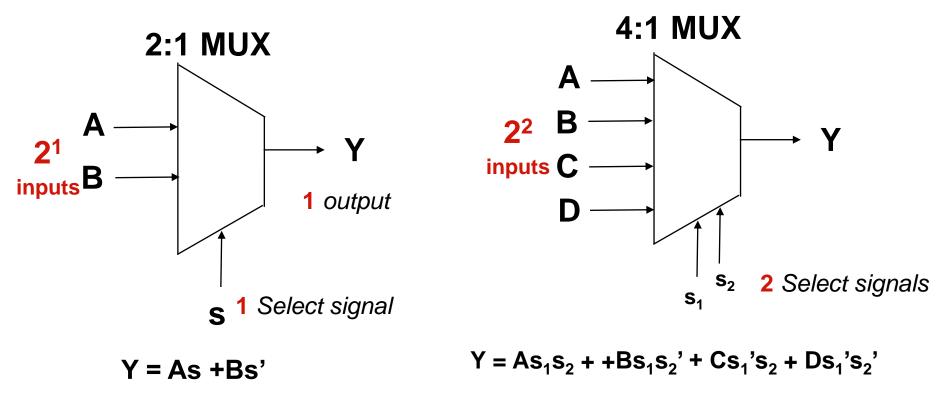

### Multiplexer (MUX)

Connects one of n inputs to the output....

Used as data selectors...encoders

In general, 2<sup>n</sup> inputs will have n select signals  $Y = \sum_{k=0}^{2^n - 1} m_k I_k$

$m_k$  is a minterm of the n control variables and  $I_k$  is the corresponding data input 15

Lecture 3, ECE 122A, VLSI Principles

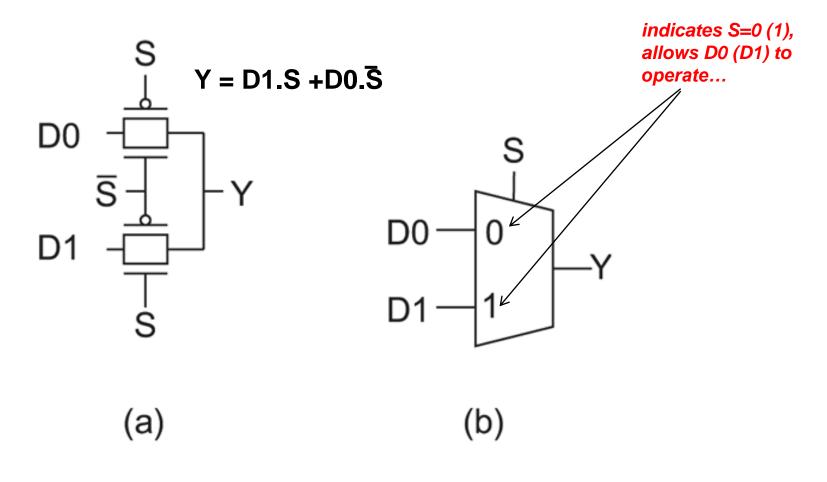

### 2:1 Multiplexer (MUX)

| Table 1.6 | Multiplexer truth table |    |   |  |

|-----------|-------------------------|----|---|--|

| s/s       | D1                      | DO | Y |  |

| 0/1       | X                       | 0  | 0 |  |

| 0/1       | X                       | 1  | 1 |  |

| 1/0       | 0                       | Х  | 0 |  |

| 1/0       | 1                       | Х  | 1 |  |

Y = D1.S +D0. $\overline{S}$  (when s = 0, D1=X, when  $\overline{s}$ =0, D0=X)

Note: X indicates a don't care condition

#### **Non-restoring MUX**

FIG 1.27 Transmission gate multiplexer

Lecture 3, ECE 122A, VLSI Principles

Kaustav Banerjee

#### **Inverting and Restoring MUX** $S/\overline{S} = 0/1$ D0 = 0: Y = 1=D0 $\overline{Y}$ = D1.S +D0.S D0 = 1: Y = 0 = D0ร D0 D0 D $\overline{S}$ D1 S S Υ Y D0 0 $\overline{S}$ ริ S S (a) (b) (c)

#### FIG 1.28 Inverting multiplexer

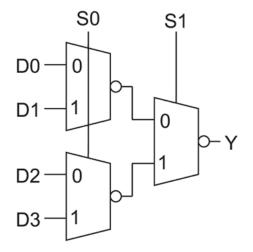

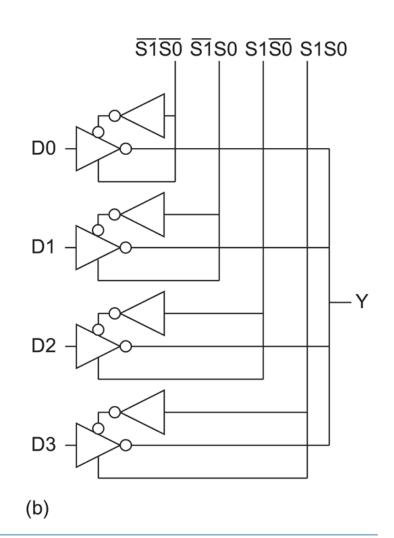

#### A 4:1 MUX

(a) Using three 2:1 MUXs

FIG 1.29 4:1 multiplexer

## **Static CMOS Summary**

- In static circuits at every point in time (except when switching) the output is connected to either GND or V<sub>DD</sub> via a low resistance path.

- fan-in of n (or n-inputs) requires 2n (n N-type + n P-type) devices

- Non-ratioed logic: gates operate independent of PMOS or NMOS sizes (since no conflict between pull-up and pull-down networks)

- □ No path ever exists between Vdd and GND: low static power

- Fully-restored logic: (NMOS passes "0" only and PMOS passes "1" only

- □ Gates must be INVERTING:  $Y = \overline{X}$ , so that X=1 (NMOS pulldown network is "ON") for Y=0 (node is fully discharged)

Lecture 3, ECE 122A, VLSI Principles

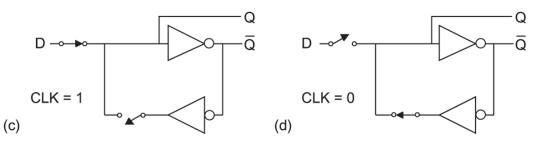

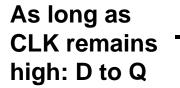

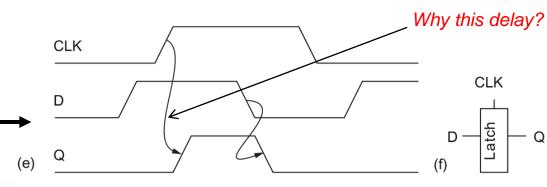

### Latches (level sensitive device)

CLK=1: D to Q CLK=0:Holds state of Q

FIG 1.30 CMOS positive-level-sensitive D latch

Lecture 3, ECE 122A, VLSI Principles

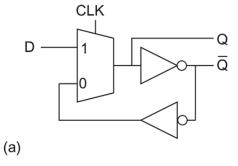

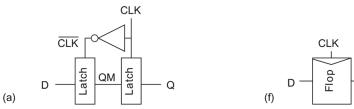

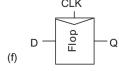

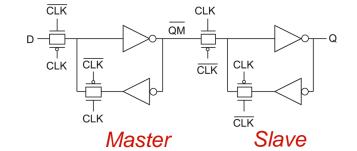

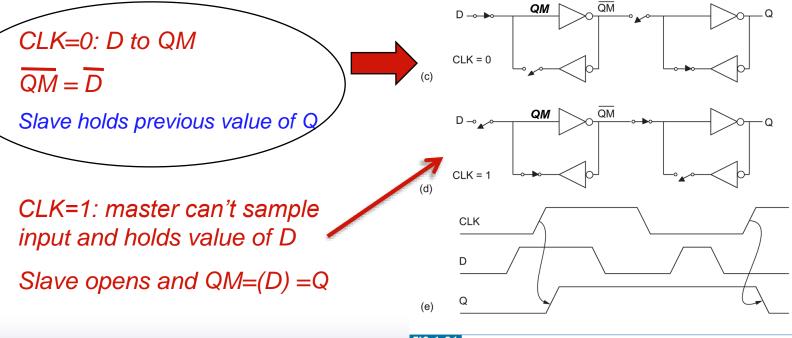

#### Flip-Flops (edge-triggered device)

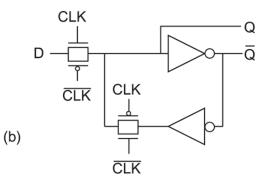

#### Combines two latches:

One +ve sensitive (slave) and one –ve sensitive latch (master)

Edge Triggered FF or Master-Slave FF

(b)

FIG 1.31 CMOS positive-edge-triggered D flip-flop

Lecture 3, ECE 122A, VLSI Principles

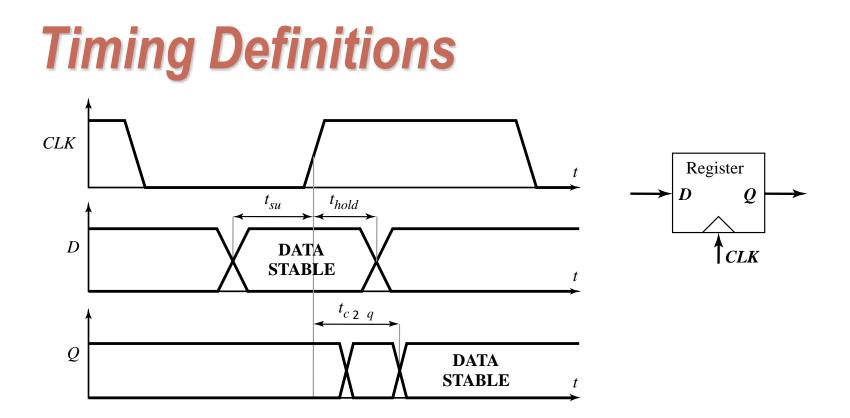

$t_{su}$  = setup time =time for which the data inputs (D) must be valid before the CLK edge  $t_{hold}$  = hold time =time for which data input must remain valid after the CLK edge  $t_{c2g}$  = worst case propagation time through the Register (w.r.t the CLK edge)

Lecture 3, ECE 122A, VLSI Principles