# ECE 122A VLSI Principles Lecture 7

Prof. Kaustav Banerjee Electrical and Computer Engineering University of California, Santa Barbara *E-mail: kaustav@ece.ucsb.edu*

Lecture 7, ECE 122A, VLSI Principles

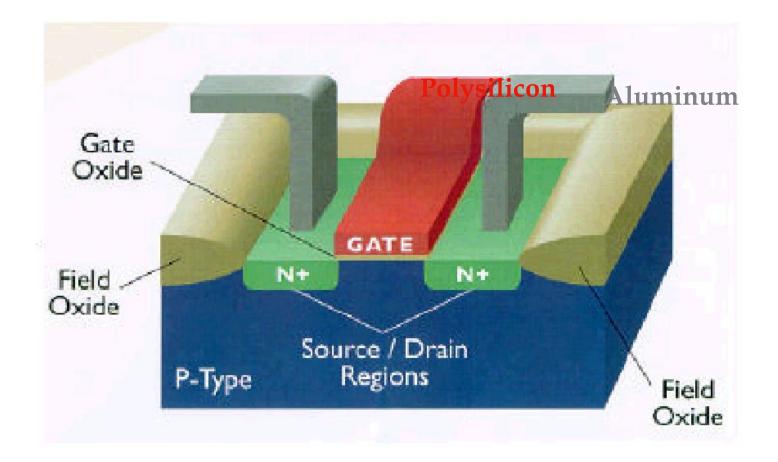

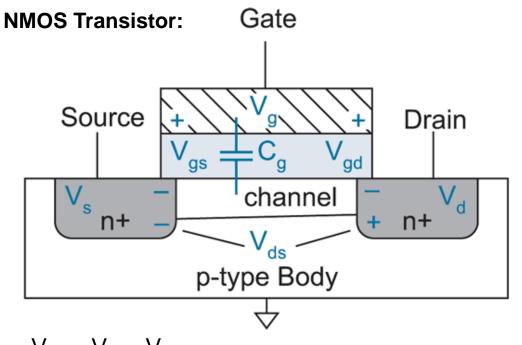

### The MOS Transistor

Lecture 7, ECE 122A, VLSI Principles

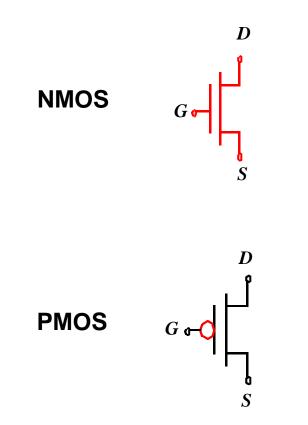

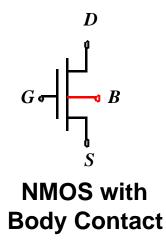

### MOS Transistors -Types and Symbols

For NMOS: Body tied to Gnd For PMOS: Body tied to Vdd Why?

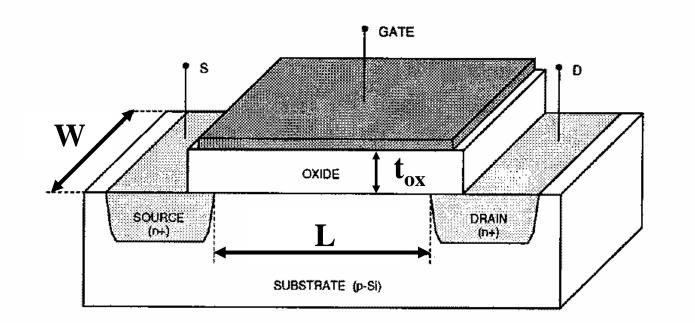

## **MOS Transistor**

Important transistor physical characteristics

- Channel length L

- Channel width W

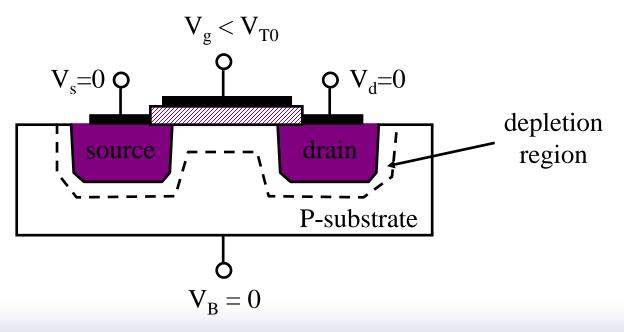

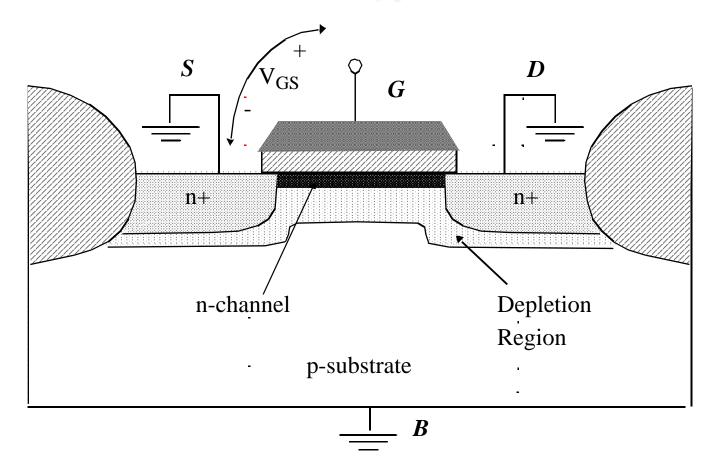

### **MOS Transistor Operation**

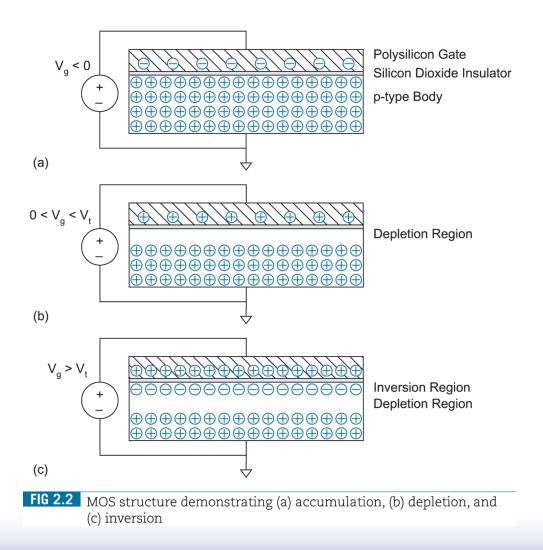

□ Simple case:  $V_D = V_S = V_B = 0$

- Operates as MOS capacitor

- □ When  $V_{GS}$  <  $V_{T0}$  (but positive), depletion region forms

- No carriers in channel to connect S and D

- $\Box$  V<sub>T0</sub> is known as the *threshold voltage*

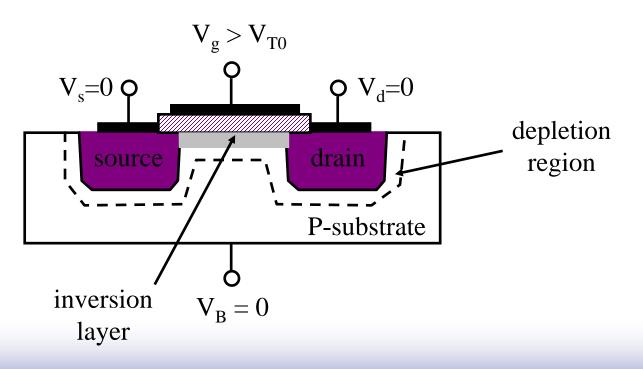

## **MOS Transistor Operation**

When V<sub>GS</sub> > V<sub>T0</sub>, inversion layer forms

Source and drain connected by conducting n-type layer (for NMOS)

# **Threshold Voltage (V<sub>T0</sub>): Concept**

Note: gate is insulated from the substrate...hence no dc current flows through the oxide...channel is capacitively coupled to the gate through the electric-field in the oxide....that's how it gets the name MOS-FET (field effect transistor)

Lecture 7, ECE 122A, VLSI Principles

# **Physical Parameters that Affect V** $_{T0}$

- □ Threshold voltage (V<sub>T0</sub>): voltage between gate and source required for inversion

- NMOS Transistor is "off" when  $V_{GS} < V_{T0}$

- □ Components:

- Work function difference between gate and channel (Flat-band voltage)

- Gate voltage to change surface potential

- Gate voltage to offset depletion region charge

- Gate voltage to offset fixed charges in gate oxide and in silicon-oxide interface

# **Threshold voltage (1)**

- $\succ$  Work function difference  $q\Phi_{GC}$  between gate and channel

- Represents built-in potential of MOS system

- For metal gate:  $\Phi_{GC} = \Phi_{M}(\text{metal-gate}) \Phi_{F}(\text{substrate}) = \Phi_{ms}$

- For poly gate:  $\Phi_{GC} = \phi_F(\text{poly-Si-gate}) \phi_F(\text{substrate})$

$$V_{T0} = \Phi_{GC} + \cdots$$

# Threshold voltage (2)

- First component accounts for built-in voltage drop

- Now apply additional gate voltage to achieve inversion: change surface potential by -2\u03c6<sub>F</sub> (note that \u03c6<sub>F</sub> is negative for p-type substrate)

$$V_{T0} = \Phi_{GC} - 2\phi_F + \cdots$$

# **Threshold voltage (3)**

- Offset depletion region charge, due to fixed acceptor ions

- > Calculate charge at inversion ( $\phi_{S} = -\phi_{F}$ )

> From before:

$$Q = -\sqrt{2qN_A\varepsilon_{Si}}|\phi_S - \phi_F|$$

> So:

$$Q_{B0} = -\sqrt{2qN_A\varepsilon_{Si}} - 2\phi_F$$

Depletion charge is negative....why? (acceptor ions after accepting electrons are –ve)

For non-zero substrate bias ( $V_{SB} \neq 0$ ):

$$Q_B = -\sqrt{2qN_A\varepsilon_{Si}} \Big| - 2\phi_F + V_{SB} \Big|$$

➤Due to larger depletion region

Lecture 7, ECE 122A, VLSI Principles

## Threshold voltage (3, cont.)

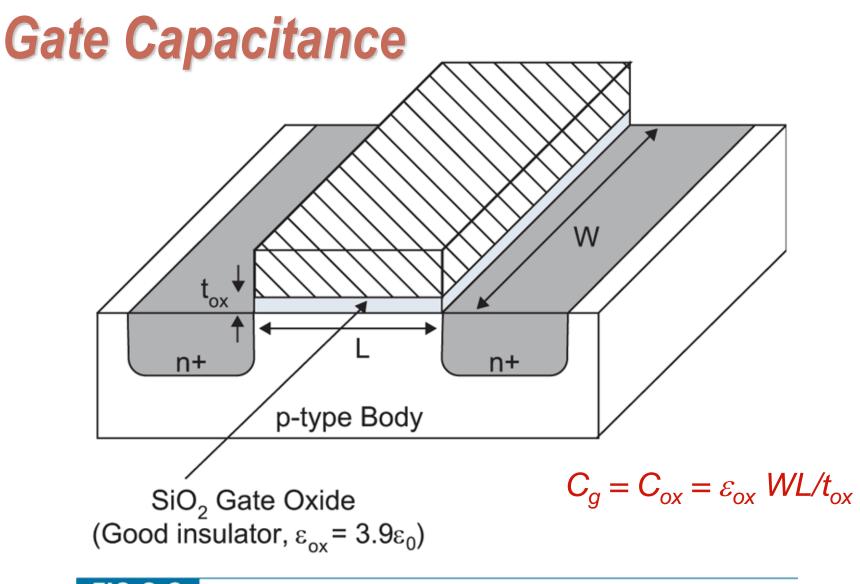

- > To offset this charge, need voltage  $-Q_B/C_{ox}$

- Cox = gate capacitance per unit area

- C<sub>ox</sub>=ε<sub>ox</sub>/t<sub>ox</sub>

t<sub>ox</sub> = thickness of gate oxide (normally in Å)

$$V_{T0} = \Phi_{GC} - 2\phi_F - \frac{Q_B}{C_{ox}} + \cdots$$

# **Threshold voltage (4)**

- Finally, correct for non-ideal fixed charges

- > Fixed positive charged ions at boundary between oxide and substrate. Density =  $N_{OX}$

- > Due to impurities, lattice imperfections at interface

- > Positive charge density  $Q_{ox} = qN_{ox}$

- > Correct with gate voltage =  $-Q_{ox}/C_{ox}$

- Final threshold voltage formula (for NMOS):

$$V_{T0} = \Phi_{GC} - 2\phi_F - \frac{Q_{B0}}{C_{ox}} - \frac{Q_{ox}}{C_{ox}}$$

### Threshold voltage, summary

> If  $V_{SB} = 0$  (no substrate bias):

$$V_{T0} = \Phi_{GC} - 2\phi_F - \frac{Q_{B0}}{C_{ox}} - \frac{Q_{ox}}{C_{ox}}$$

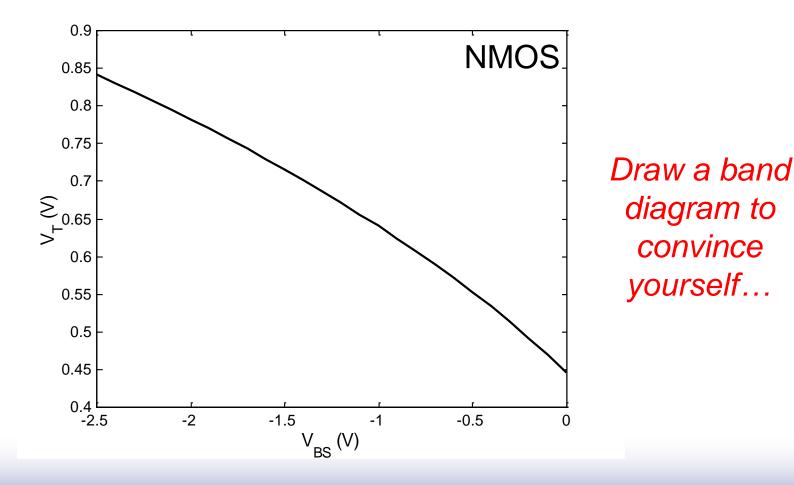

> If  $V_{SB} \neq 0$  (non-zero substrate bias)

$$V_{T} = V_{T0} + \gamma \left( \sqrt{\left| -2\phi_{F} + V_{SB} \right|} - \sqrt{\left| 2\phi_{F} \right|} \right) \qquad \begin{array}{l} \text{For uniform} \\ \text{body doping...} \end{array}$$

#### Body effect (substrate-bias) coefficient:

$$\gamma = \frac{\sqrt{2qN_A}\varepsilon_{Si}}{C_{ox}} + \text{for NMOS} - \text{for PMOS}$$

For modern FETs with retrograde doping,  $V_T$ varies ~linearly with  $V_{SB}$

Threshold voltage increases as V<sub>SB</sub> increases! (easy to explain with a band diagram...) Lecture 7, ECE 122A, VLSI Principles

Kaustav Banerjee

### **The Body Effect**

# Threshold Voltage (NMOS vs. PMOS)

|                                            | NMOS                | PMOS                |

|--------------------------------------------|---------------------|---------------------|

| Substrate Fermi potential                  | $\phi_{F} < 0$      | $\phi_{F} > 0$      |

| Depletion charge density                   | Q <sub>B</sub> < 0  | Q <sub>B</sub> > 0  |

| Substrate bias coefficient                 | γ > <b>0</b>        | γ < 0               |

| Substrate bias voltage                     | $V_{SB} > 0$        | $V_{SB} < 0$        |

| Threshold voltage<br>(enhancement devices) | V <sub>T0</sub> > 0 | V <sub>T0</sub> < 0 |

**Remember:** You need not memorize this table but rather should be able to fill it in based on the band diagrams...

Lecture 7, ECE 122A, VLSI Principles

# **Threshold Voltage Adjustment**

- Threshold voltage can be changed by doping the channel region with donor or acceptor ions

- □ For NMOS:

- V<sub>T</sub> increased by adding acceptor ions (p-type)

- V<sub>T</sub> decreased by adding donor ions (n-type)

- Opposite for PMOS

- $\Box$  Approximate change in V<sub>T0</sub>:

- Density of implanted ions = N<sub>1</sub> [cm<sup>-2</sup>]

- Assume all implanted impurities are ionized

$$\Delta V_{T0} = \frac{qN_I}{C_{ox}}$$

# Example: V<sub>T0</sub> Adjustment

#### Consider an NMOS device:

- P-type substrate:  $N_A = 2 \times 10^{16} \text{ cm}^{-3}$

- Polysilicon gate:  $\Phi_{GC} = -0.92V$

- $t_{ox} = 600 \text{ Å} (1\text{ Å} = 1 \text{ x } 10^{-8} \text{ cm})$

- $N_{ox} = 2 \times 10^{10} \text{ cm}{-2}$

- $\epsilon_{Si} = 11.7 \epsilon_{0,} \epsilon_{ox} = 3.97 \epsilon_{0}$

### □ (a) Find $V_{T0}$

# □ (b) Find amount and type of channel implant to get $V_{T0} = 0.4 \text{ V}$

# **MOS Capacitor (Review)**

Lecture 7, ECE 122A, VLSI Principles

# **MOSFET Operation (NMOS)**

Easy to understand with a band diagram across S-Ch-D.....

regions of operation

Lecture 7, ECE 122A, VLSI Principles

Remember, both drift and diffusion currents play a role...

**Pinch-off:** conduction still takes place from Source to Drain due to drift of electrons under the influence of the +ve drain voltage

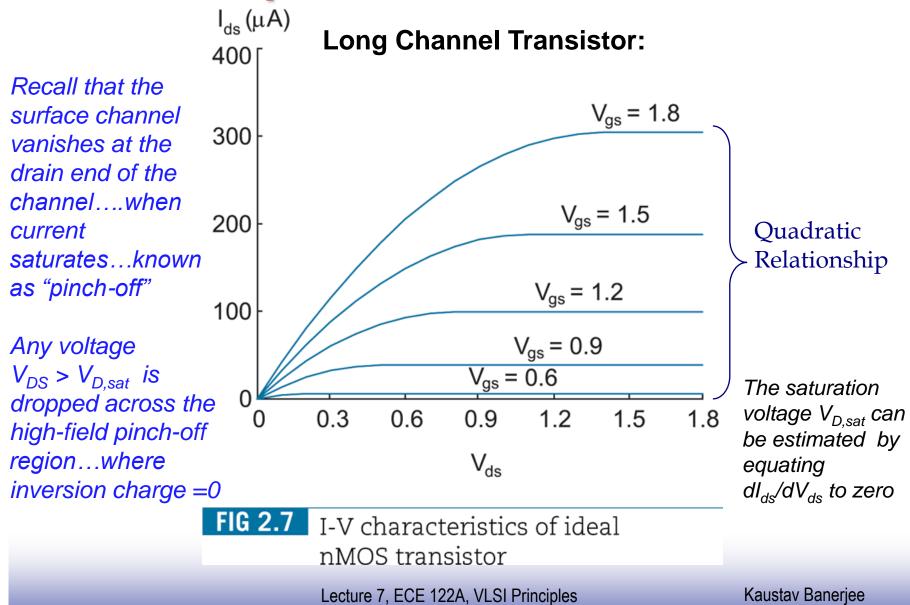

### NMOS Output Characteristics

### **Channel Mobile Charge**

Note: i) The inversion layer thickness is assumed to be zero: all charges are assumed to be located at the Si surface....like a sheet of charge.... ii) Hence, there is no potential drop or band bending across the inversion layer....

$Q_{channel} = C_g \left( V_{gc} - V_t \right)$

$$V_{ds} = V_{gs} - V_{gd}$$

Average gate to channel potential:

$$V_{gc} = (V_{gs} + V_{gd})/2 = V_{gs} - V_{ds}/2$$

FIG 2.5 Average gate to channel voltage

Lecture 7, ECE 122A, VLSI Principles

FIG 2.6 Transistor dimensions

Lecture 7, ECE 122A, VLSI Principles

## **Transistor Currents (NMOS)**

Cutoff Region:

$$I_{ds} = 0$$

,  $V_{gs} < V_t$

Linear Region:  $V_{gs} > V_t$ ,  $V_{ds} < V_{gs} - V_t$

$I_{ds} = W Q_{channel}$  .carrier velocity(v)

$I_{ds} = \mu C_{ox} W/L (V_{gs} - V_t - V_{ds}/2)V_{ds}$

Since Vds is small, Vds/2 can be neglected...and Ids is linearly proportional to Vds....like a resistor

Saturation Region:

$$V_{gs} > V_t$$

,  $V_{ds} > V_{gs} - V_t$

Note: as Vds increases, average Q<sub>channel</sub> decreases...

$$dI_{ds}/dV_{ds} = 0 at V_{ds} = V_{dsat} = V_{gs} - V_t$$

Substituting  $V_{ds}$  with  $V_{dsat}$  above:  $I_{ds} = \beta/2 (V_{gs} - V_t)^2$

Note: for PMOS  $V_{tp} = V_{tn}$   $\mu_p < \mu_n$ , hence  $(W/L)_{PMOS} \sim 2 (W/L)_{NMOS}$

$$Q_{channel} = C_g (V_{gc} - V_t)$$

$$V_{gc} = V_{gs} - V_{ds}/2$$

$$v = \mu E$$

$$E_{lateral} = V_{ds}/L$$

$$\beta = \mu C_{ox} W/L$$

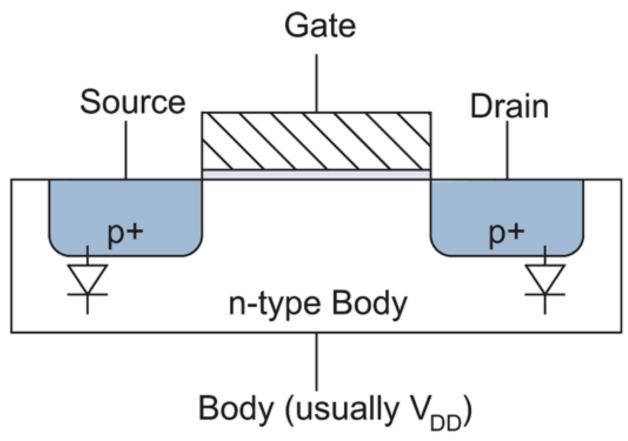

### **PMOS Transistor**

### FIG 2.4 pMOS transistor

Lecture 7, ECE 122A, VLSI Principles

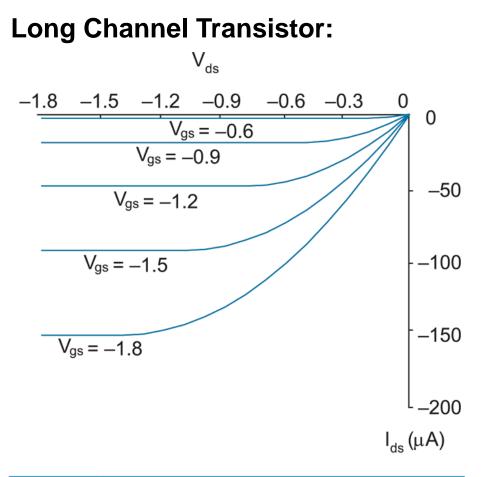

### **PMOS Output Characteristics**

**FIG 2.8** I-V characteristics of ideal pMOS transistor

Lecture 7, ECE 122A, VLSI Principles

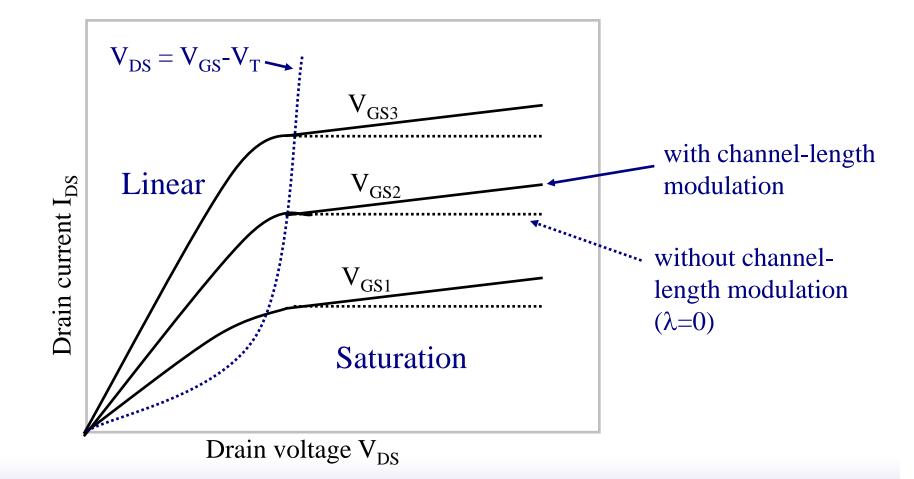

# **Channel Length Modulation**

□ In saturation, pinch-off point moves

- As V<sub>DS</sub> is increased, pinch-off point moves closer to source

- Effective channel length becomes shorter

- Current increases due to shorter channel

$$\dot{L} = L - \Delta L$$

$$I_{D} = \frac{1}{2} \mu_{n} C_{ox} \frac{W}{L} (V_{GS} - V_{TN})^{2} (1 + \lambda V_{DS})$$

$\lambda$  = channel length modulation coefficient

Lecture 7, ECE 122A, VLSI Principles

### Summary: MOS Output I/V I/V curve for NMOS device:

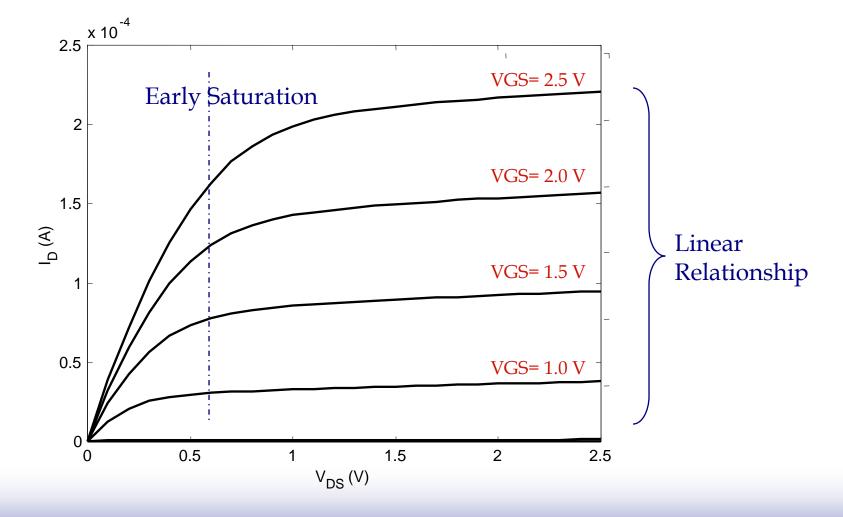

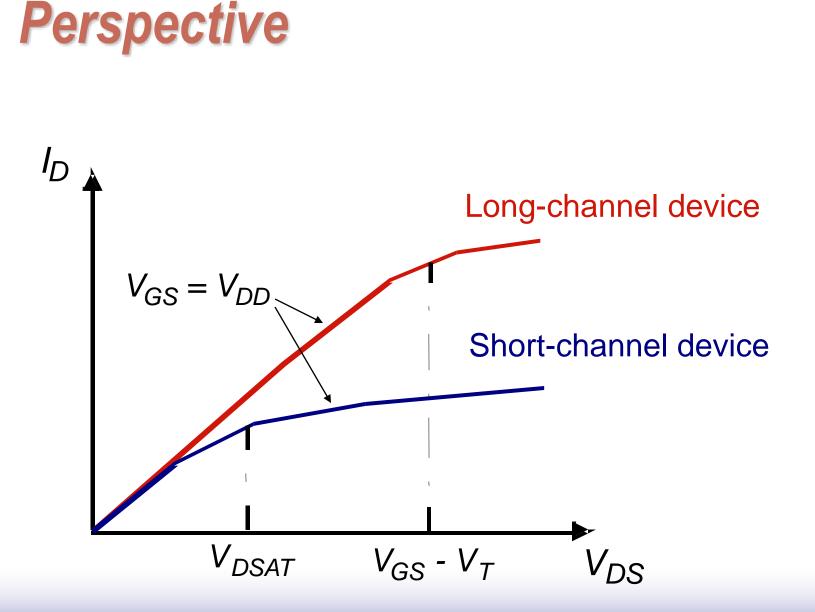

# **Current-Voltage Relations Short-Channel Transistors**

Lecture 7, ECE 122A, VLSI Principles

Lecture 7, ECE 122A, VLSI Principles

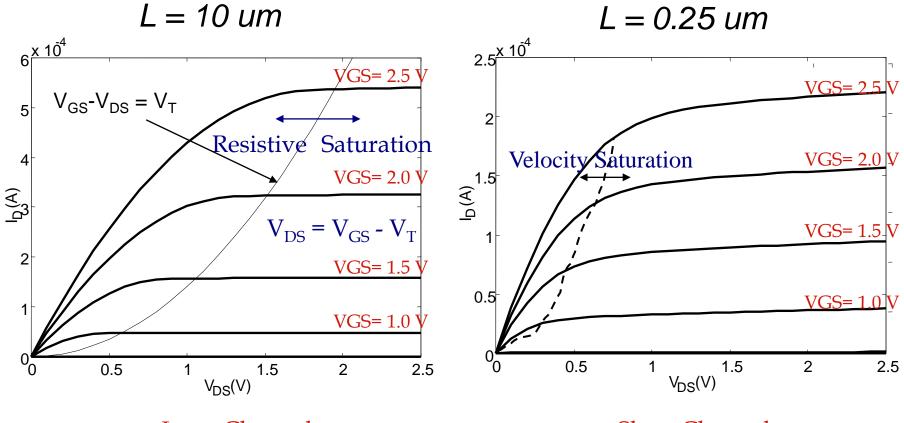

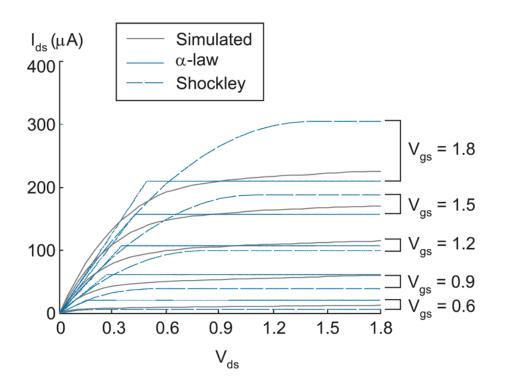

# **Output Characteristics:** I<sub>D</sub> versus V<sub>DS</sub>

W/L = 1.5 for both cases....

Long Channel

Short Channel

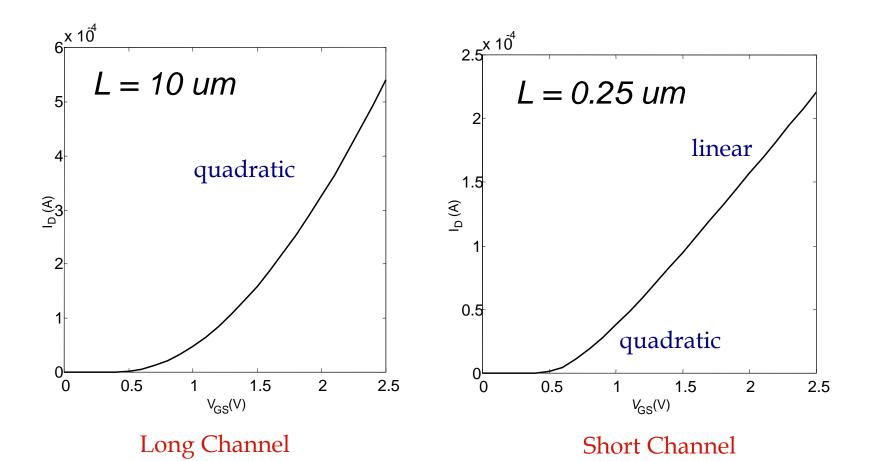

# Input Characteristics: I<sub>D</sub> versus V<sub>GS</sub>

Note: These are Linear-Linear Plots!!

Lecture 7, ECE 122A, VLSI Principles

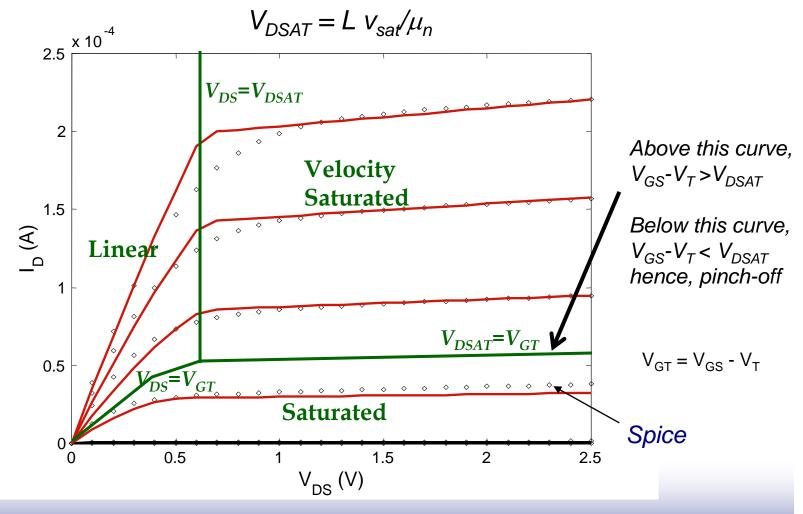

# Simple Model (solid lines) versus SPICE

Lecture 7, ECE 122A, VLSI Principles

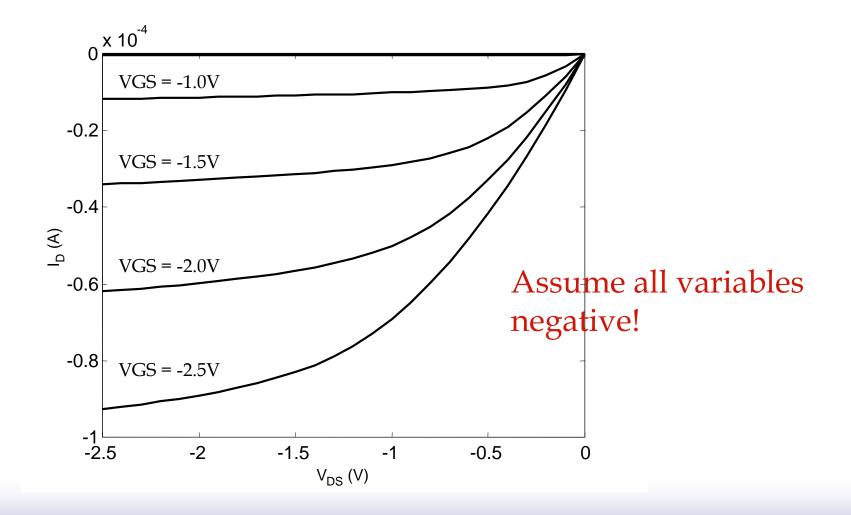

## **A PMOS Transistor (short-channel)**

Lecture 7, ECE 122A, VLSI Principles

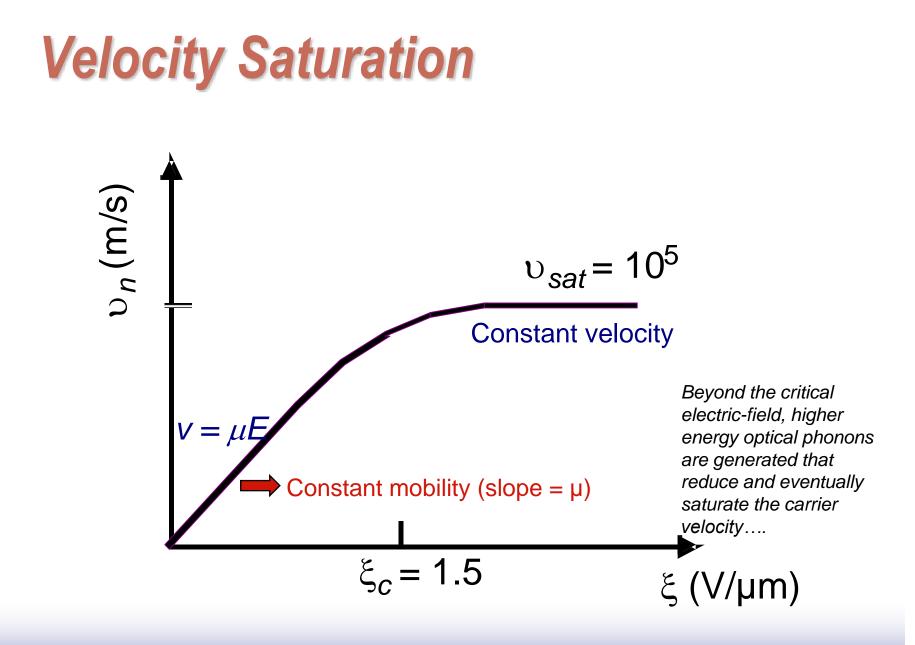

# **Alpha-Power MOSFET Model**

FIG 2.17 I-V characteristics for nMOS transistor with velocity saturation

Sakurai Model:  $I_{ds} \propto (V_{gs} - V_t)^{\alpha}$

At low lateral E-fields, V<sub>ds</sub>/L, current increases linearly with E-field

At high fields, E= E<sub>sat</sub>

Carrier velocity saturates due to carrier scattering =  $v_{sat}$  (=  $\mu E_{sat}$ )

$I_{ds} = \mu C_{ox} W/L (V_{gs} - V_t)^2$ ---no velocity saturation

$I_{ds} = C_{ox} W (V_{gs} - V_t) v_{sat}$

---complete velocity saturation

Practical situation: carrier velocity doesn't increase linearly with field but is not completely velocity saturated....

$1 < \alpha < 2$ , is the velocity saturation index, determined by curve fitting.....also accounts for mobility degradation due to high vertical field ( $V_{qs}/t_{ox}$ )

Lecture 7, ECE 122A, VLSI Principles

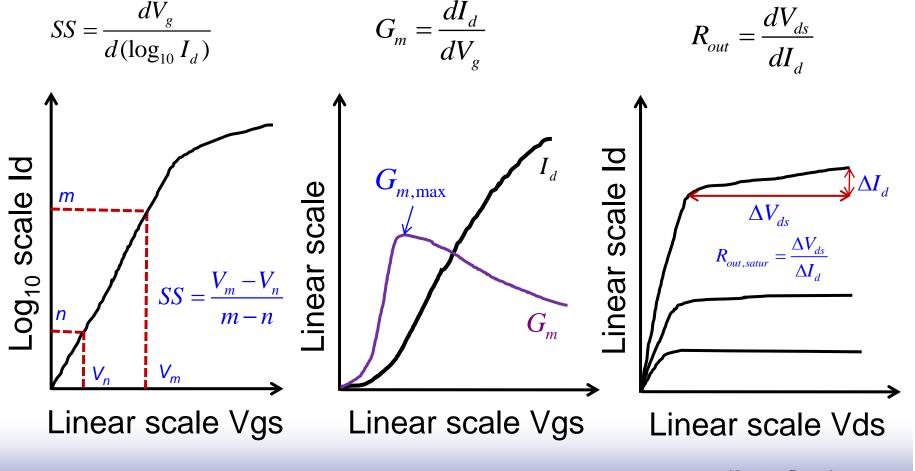

# How to Extract SS, G<sub>m</sub>, and R<sub>out</sub>

SS: Sub-threshold voltage swing

*G<sub>m</sub>: Transconductance*

R<sub>out</sub>: output resistance

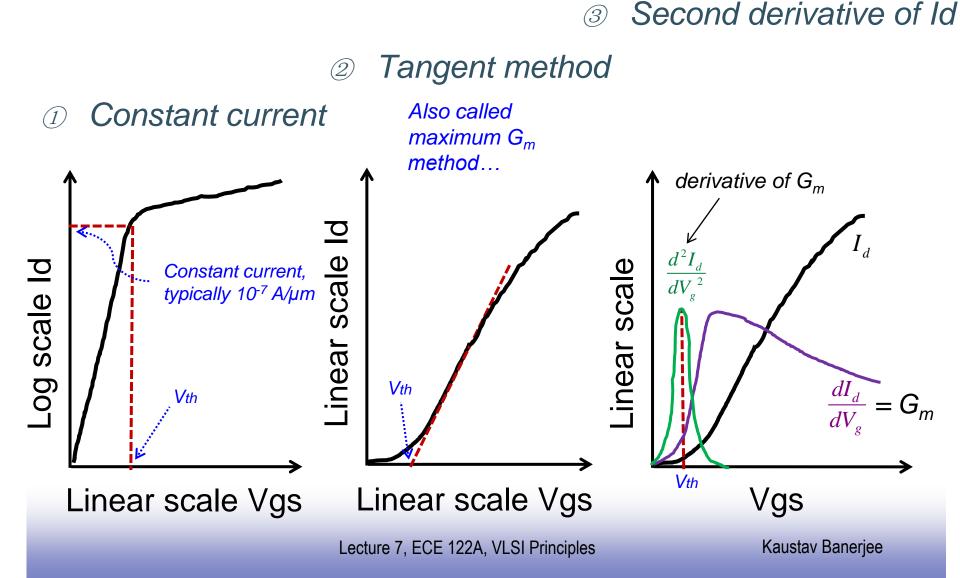

### **Methods to Extract Vth**