# ECE 122A VLSI Principles

#### Lecture 8

Prof. Kaustav Banerjee

Electrical and Computer Engineering

University of California, Santa Barbara

E-mail: kaustav@ece.ucsb.edu

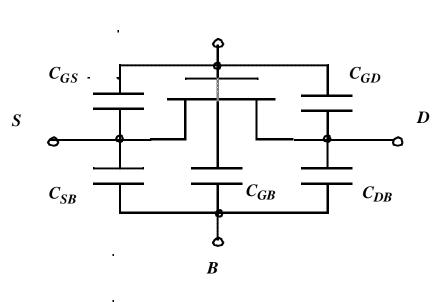

## Dynamic Behavior of MOS Transistor

#### Oxide Capacitance

- Gate to Source overlap

- Gate to Drain overlap

- Gate to Channel/Bulk

- □ Junction Capacitance

- Source to Bulk junction

- Drain to Bulk junction

$\boldsymbol{G}$

capacitances limit the operation frequency and switching speed

## Oxide capacitances

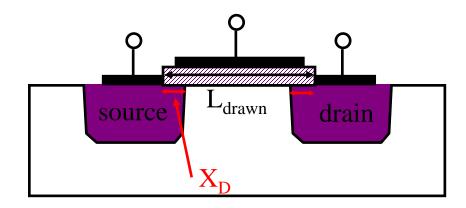

Overlap

#### Overlap capacitances

- gate electrode overlaps source and drain regions

- X<sub>D</sub> is overlap length on each side of channel

- $L_{eff} = L_d 2X_D$

- Total overlap capacitance:

$$C_{overlap} = C_{GSO} + C_{GDO} = 2C_{ox}WX_D$$

## Oxide capacitances

#### **Channel**

#### Channel capacitances

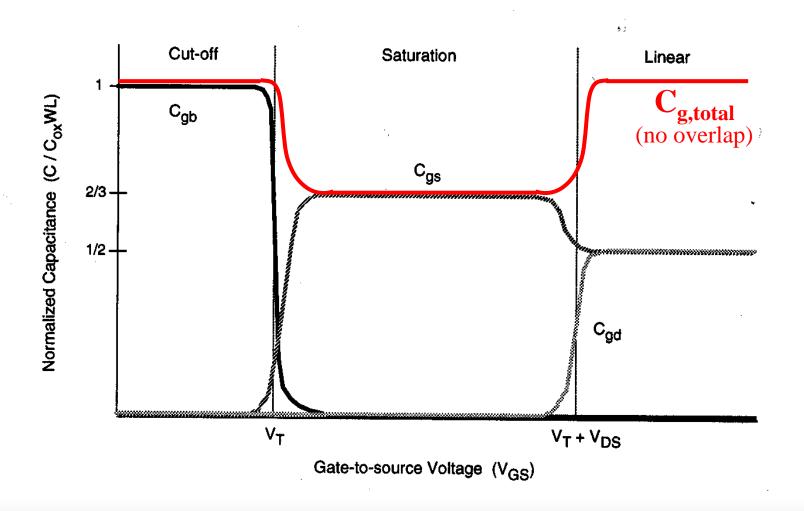

Gate-to-source: C<sub>gs</sub>

■ Gate-to-drain: C<sub>gd</sub>

Gate-to-bulk: C<sub>gb</sub>

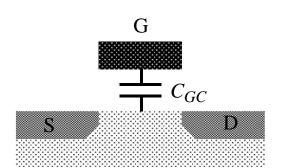

#### Cutoff:

- No channel connecting source and drain (to form "other" side of the capacitor)

- $C_{gs} = C_{gd} = 0$

- $C_{qb} = C_{ox}WL_{eff}$

- Total channel capacitance C<sub>GC</sub> = C<sub>ox</sub>WL<sub>eff</sub>

# Oxide capacitances

#### Channel

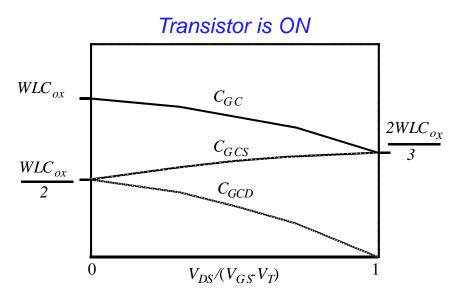

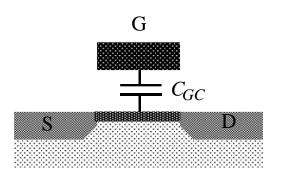

#### □ Linear mode

- Channel spans from source to drain

- Capacitance split equally between S and D

$$C_{GS} = \frac{1}{2}C_{ox}WL_{eff} \qquad C_{GD} = \frac{1}{2}C_{ox}WL_{eff} \qquad C_{GB} = 0$$

$$C_{GB} = 0$$

completely shielded by channel chain channel chan

Electric field completely channel charges

- Total channel capacitance  $C_{GC} = C_{ox}WL_{eff}$

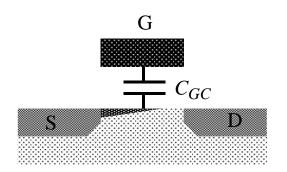

#### ■ Saturation mode

– Channel is pinched off:

Drain voltage no longer affects channel charge

$$C_{GD} = 0 C_{GS} = \frac{2}{3}C_{ox}WL_{eff} C_{GB} = 0$$

- Total channel capacitance  $C_{GC} = 2/3 C_{ox}WL_{eff}$

# Oxide capacitances Channel

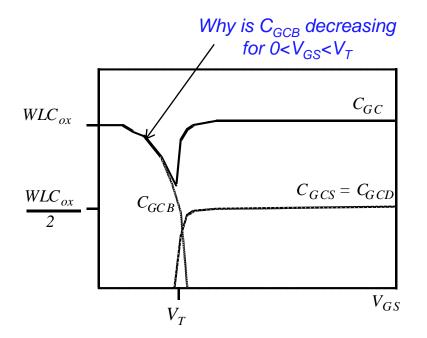

## Gate-to-Channel Capacitance

Note:  $C_{GC} = C_{GCB} + C_{GCS} + C_{GCD}$

Capacitance as a function of  $V_{GS}$  (with  $V_{DS} = 0$ )

Capacitance as a function of the degree of saturation

Bottom Line: Cap. components are non-linear

# Gate-to-Channel Capacitance (summary)

$$C_{GC} = C_{gb} + C_{gs} + C_{gd}$$

| Operation Region | $C_{gb}$         | $C_{gs}$              | $C_{gd}$           |

|------------------|------------------|-----------------------|--------------------|

| Cutoff           | $C_{ox}WL_{eff}$ | 0                     | 0                  |

| Resistive        | 0                | $C_{ox}WL_{eff}/2$    | $C_{ox}WL_{eff}/2$ |

| Saturation       | 0                | $(2/3)C_{ox}WL_{eff}$ | 0                  |

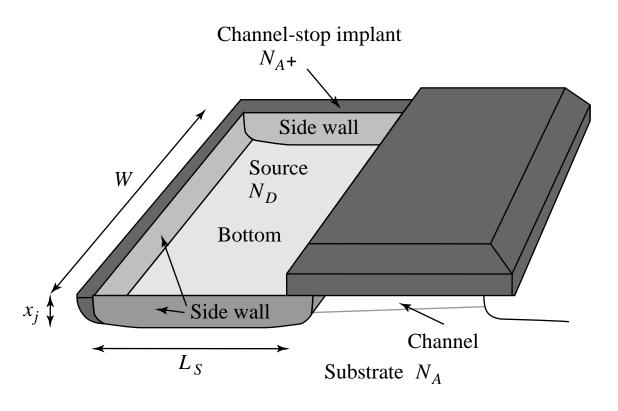

## **Diffusion Capacitance**

$$\begin{split} C_{diff} &= C_{bottom} + C_{sw} = C_{j} \times AREA + C_{jsw} \times PERIMETER \\ &= C_{j}L_{S}W + C_{jsw}(2L_{S} + W) \end{split}$$

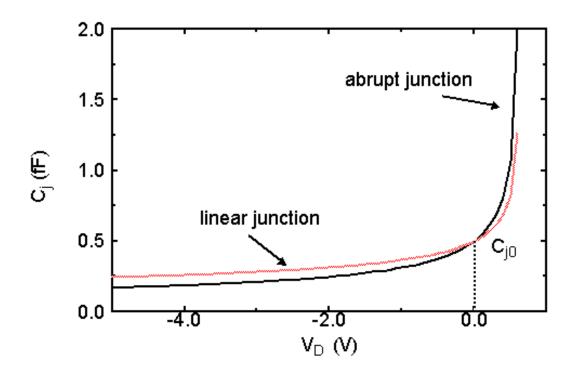

## **Junction Capacitance**

$$C_j = \frac{C_{j0}}{(1 - V_D I \phi_0)^m}$$

m = 0.5: abrupt junction m = 0.33: linear junction

## Linearizing the Junction Capacitance

Replace non-linear capacitance by large-signal equivalent linear capacitance which displaces equal charge over voltage swing of interest

$$C_{eq} = \frac{\Delta Q_{j}}{\Delta V_{D}} = \frac{Q_{j}(V_{high}) - Q_{j}(V_{low})}{V_{high} - V_{low}} = K_{eq}C_{j0}$$

$$K_{eq} = \frac{-\phi_0^m}{(V_{high} - V_{low})(1-m)} [(\phi_0 - V_{high})^{1-m} - (\phi_0 - V_{low})^{1-m}]$$

# Capacitances in 0.25 $\mu$ m CMOS Process

|      | $C_{\rm ox}$ (fF/ $\mu$ m <sup>2</sup> ) | $C_{\mathcal{O}}$ (fF/ $\mu$ m) | $\frac{C_j}{(	ext{fF}/	ext{	ext{m}}^2)}$ | $m_{j}$ | $\phi_b \ (V)$ | C <sub>jsw</sub><br>(fF/μm) | $m_{jsw}$ | $egin{array}{c} oldsymbol{\phi}_{bsw} \ (V) \end{array}$ |

|------|------------------------------------------|---------------------------------|------------------------------------------|---------|----------------|-----------------------------|-----------|----------------------------------------------------------|

| NMOS | 6                                        | 0.31                            | 2                                        | 0.5     | 0.9            | 0.28                        | 0.44      | 0.9                                                      |

| PMOS | 6                                        | 0.27                            | 1.9                                      | 0.48    | 0.9            | 0.22                        | 0.32      | 0.9                                                      |

## MOS Cap. Summary

In general, these capacitances are nonlinear and voltage dependent....

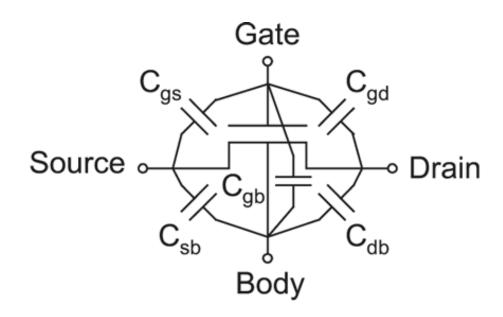

Note: The diffusion capacitances,  $C_{sb}$  and  $C_{db}$  are parasitic capacitances....but they do impact circuit performance

FIG 2.14 Capacitances of an MOS transistor

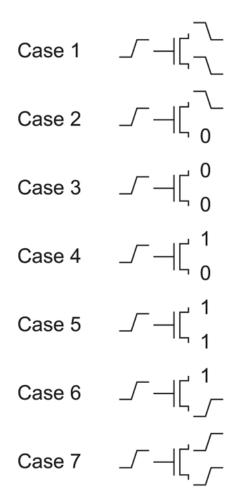

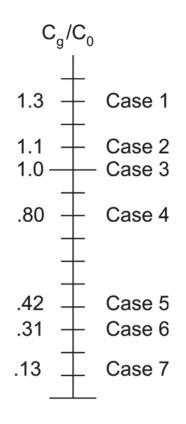

## Data Dependency

Effective gate capacitance (C<sub>g</sub>) varies with the switching activity of the source and drain....

Think about a parallel plate capacitor...with the each electrode tied to the same voltage or different voltages...

FIG 2.12 Data-dependent gate capacitance

## Subthreshold Leakage

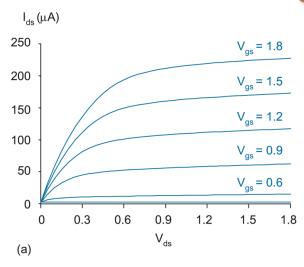

Saturation

- Dominant leakage mechanism

- Function of both V<sub>GS</sub> and V<sub>DS</sub>

- Increases exponentially as temperature increases or Vt decreases.....

$V_{ds} = 1.8$ 1 mA Region 100 μΑ Subthreshold How much 10 μΑ Region do we need  $1 \mu A$ to reduce 100 nA  $V_{GS}$  for lds to 10 nA Subthreshold drop by a 1 nA Slope 100 pA factor of 10 pA 10..... 0 0.3 0.6 0.9 1.2 1.5

(b)

#### Subthreshold swing (S) = (subthreshold slope)-1

$$S = n (kT/q) ln (10)$$

For ideal transistor with sharpest possible roll-off, n=1 and S=60 mV/decade

...a fundamental limit for MOSFETs!!!

1.8

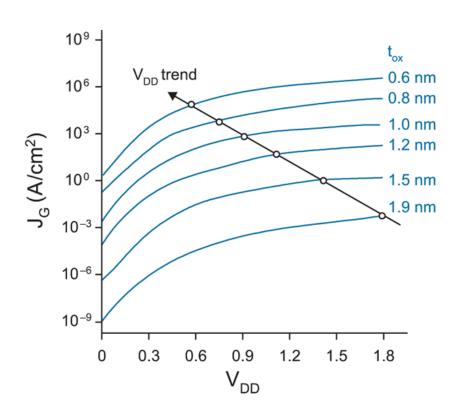

## Gate Leakage (Direct Tunneling)

FIG 2.20 Gate leakage current from [Song01]

- Increases with gate oxide (SiO2) scaling

- High-k gate oxides can be used to lower gate leakage

- Independent of temperature

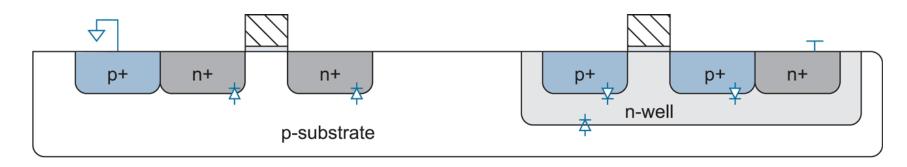

## Junction Leakage

FIG 2.19 Reverse-biased diodes in CMOS circuits

- Less significant than gate and subthreshold leakage

- Increases with temperature

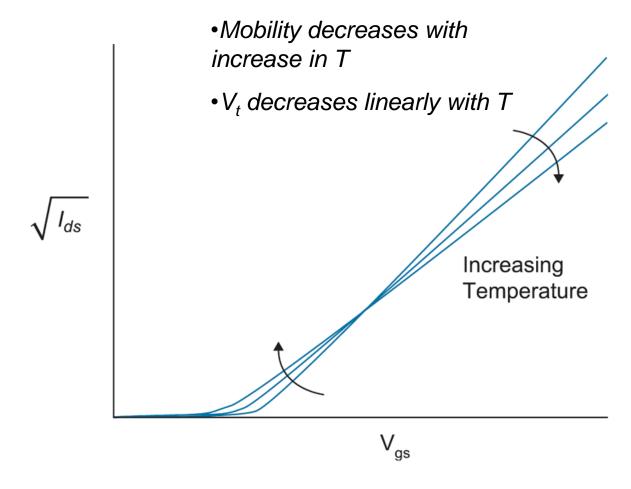

## Temperature Effects

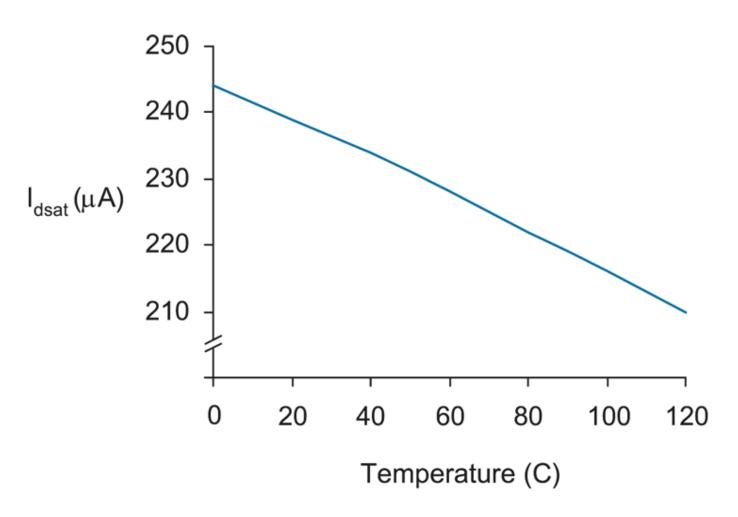

FIG 2.21 I–V characteristics of nMOS transistor in saturation at various temperatures

## Temperature Effects

FIG 2.22  $I_{dsat}$  vs. temperature

## Temperature Effects

#### Chip Cooling can:

- 1. Improve Circuit performance

- speed up transistors since mobility improves

- decrease the delay of interconnects since metal resistance decreases with temperature

- Lowers junction capacitance (increases depletion width)

- 2. Decrease leakage (mainly subthreshold)

- 3. Improve reliability of the chip

For more detailed info. read the paper posted on the class web site: "Cool Chips: Opportunities and Implications for Power and Thermal Management", by S-C. Lin and K. Banerjee, IEEE Transactions on Electron Devices, vol. 55, No. 1, 2008, 245-255

## **Inverter Operation**

□ Inverter is the simplest digital logic gate

- Many different circuit styles possible

- CMOS

- Resistive-load

- Pseudo-NMOS

- Dynamic

- □ Important characteristics

- Performance (operating speed or delay through the gate)

- Power/Energy consumption

- Robustness (tolerance to noise)

- Cost (complexity and area)

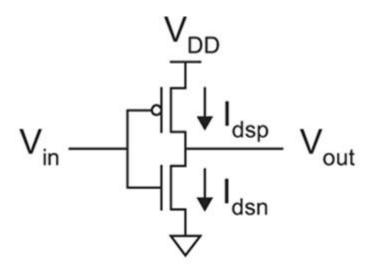

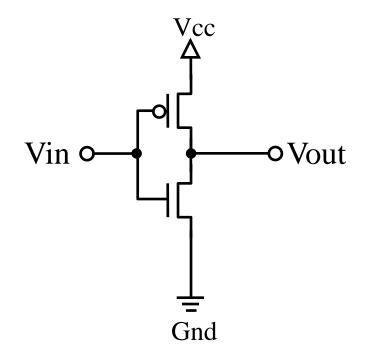

## **CMOS** Inverter

The most widely used gate....

A CMOS inverter

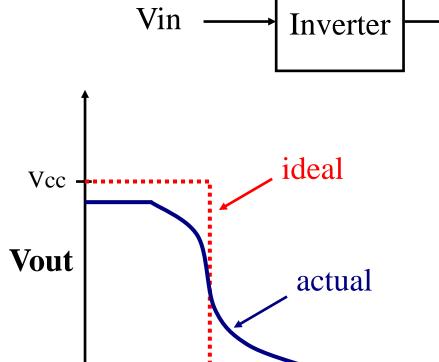

### Inverter model: VTC

Voltage transfer curve (VTC): plot of output voltage Vout vs. input voltage Vin

Vin

#### Ideal digital inverter:

When Vin=0, Vout=Vcc

Vout

- When Vin=Vcc, Vout=0

- Sharp transition region

Vcc

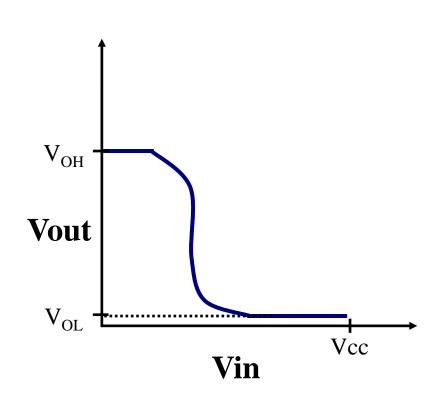

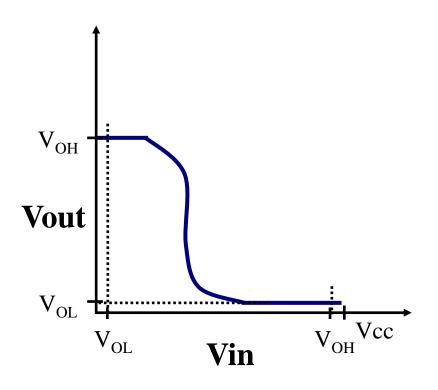

# Actual inverter: V<sub>OH</sub> and V<sub>OL</sub>

- □ V<sub>OH</sub> and V<sub>OL</sub> represent the "high" and "low" output voltages of the inverter

- $\Box$  V<sub>OH</sub> = output voltage when Vin = '0'

- $\Box$  V<sub>OL</sub> = output voltage when Vin = '1'

- □ Ideally,

- V<sub>OH</sub> = Vcc

- $V_{OL} = 0$

# V<sub>OL</sub> and V<sub>OH</sub>

#### In transfer function terms:

- $V_{OL} = f(V_{OH})$

- $V_{OH} = f(V_{OL})$

- f = inverter transfer function

- □ Difference (V<sub>OH</sub>-V<sub>OL</sub>) is the *voltage swing* of the gate

- Full-swing logic swings from ground to Vcc

### **Inverter Threshold**

# Inverter switching threshold:

- Point where voltage transfer curve intersects line Vout=Vin

- Represents the point at which the inverter switches state

- Normally, V<sub>M</sub> ≈ Vcc/2- Why?

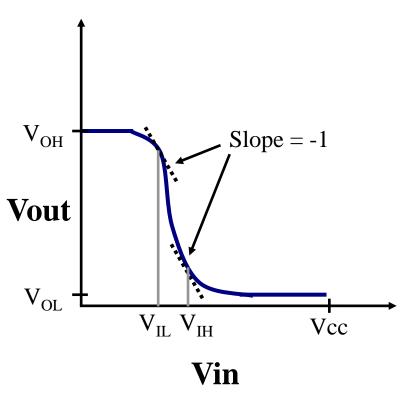

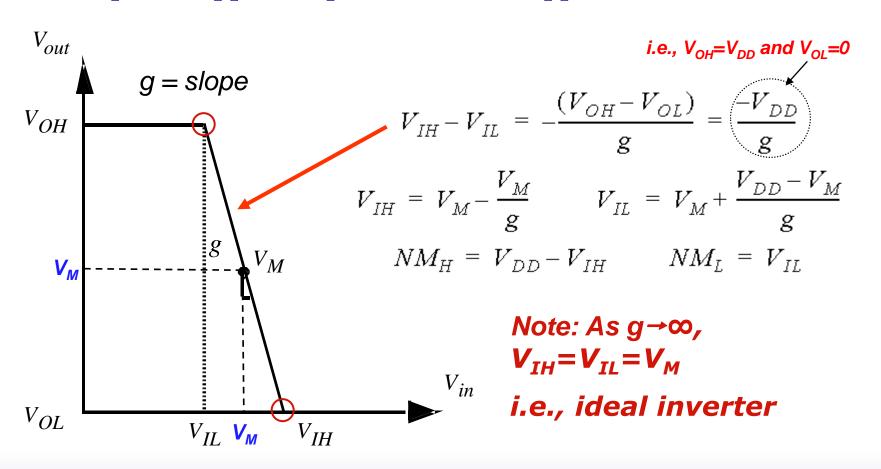

## Noise Margins....

- V<sub>IL</sub> and V<sub>IH</sub> measure

effect of input voltage

on inverter output

- □ V<sub>IL</sub> = largest input voltage recognized as logic '0'

- □ V<sub>IH</sub> = smallest input voltage recognized as logic '1'

- □ Defined as point onVTC where slope = -1

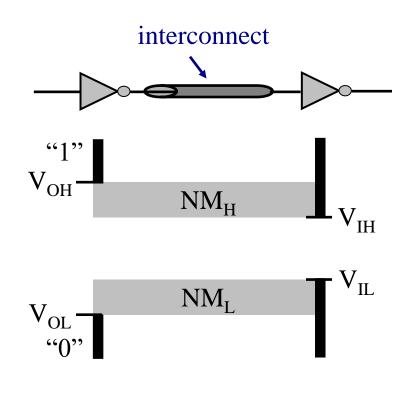

## Inverter Noise Margin

Ideally, noise margin should be as large as possible

- Noise margin is a measure of the *robustness* of an inverter

- $N_{ML} = V_{IL} V_{OL}$

- $N_{MH} = V_{OH} V_{IH}$

- Models a chain of inverters. Example:

- First inverter output is V<sub>OH</sub>

- Second inverter recognizes input > V<sub>IH</sub> as logic '1'

- Difference V<sub>OH</sub>-V<sub>IH</sub> is "safety zone" for noise

# Noise Margin (cont)

- □ Why are V<sub>II</sub>, V<sub>IH</sub> defined as unity-gain point on VTC curve?

- Assume there is noise on input voltage V<sub>in</sub>

$$V_{out} = f(V_{in} + V_{noise})$$

First-order approximation (Taylor Series):

$$V_{out} = f(V_{in}) + \frac{dV_{out}}{dV_{in}} V_{noise}$$

$V_{out} = f(V_{in}) + \frac{dV_{out}}{dV_{in}} V_{noise} \quad \begin{array}{l} \textit{Note:} \ \text{dV}_{\text{out}}/\text{dV}_{\text{in}} = 0 \ \text{occurs only} \\ \text{at the beginning and at the end} \\ \text{of the VTC curve, elsewhere it} \end{array}$ is negative

- If gain  $(dV_{out}/dV_{in}) > 1$ , noise will be amplified.

- If gain < 1, noise is filtered. Therefore  $V_{IL}$ ,  $V_{IH}$ ensure that gain < 1

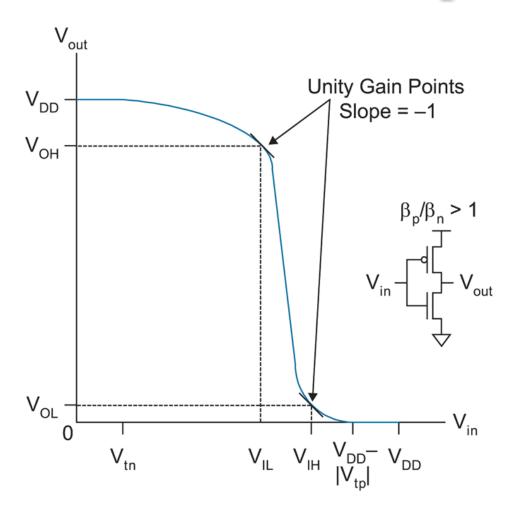

# **CMOS Inverter Noise Margins**

FIG 2.28 CMOS inverter noise margins

# Determining V<sub>IH</sub> and V<sub>IL</sub>

A simplified approach: piecewise linear approximation of the VTC

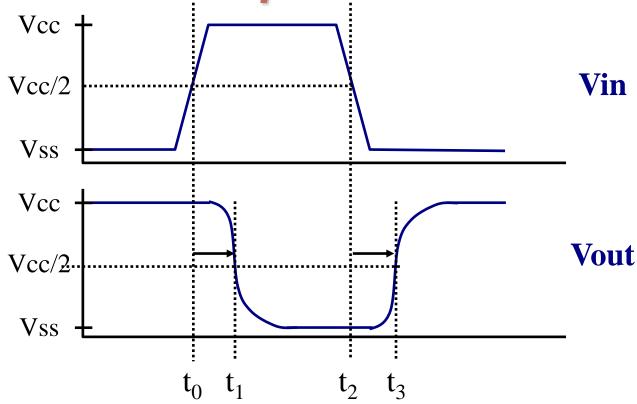

Inverter Time Response

□ Propagation delay measured from 50% point of Vin to 50% point of Vout

$$\Box t_{phl} = t_1 - t_0, t_{plh} = t_3 - t_2, t_p = \frac{1}{2}(t_{phl} + t_{plh})$$

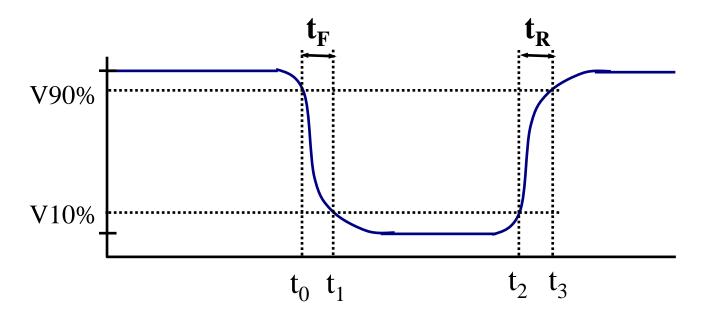

### Rise and Fall Time

- □ Fall time: measured from 90% point to 10% point

- $t_F = t_1 t_0$

- □ Rise time: measured from 10% point to 90% point

- $t_R = t_3 t_2$

- □ Alternately, can define 20%-80% rise/fall time

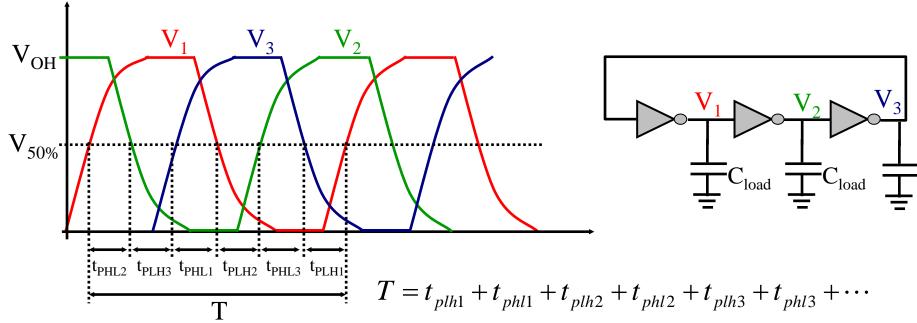

## Ring Oscillator

- Ring oscillator circuit: standard method of comparing delay from one process to another

- Odd-number n of inverters connected in chain: oscillates with period T (usually n >> 5)

For

$$n$$

stages:  $T = 2nt_p$ ,

For n stages:

$$T = 2nt_p$$

,  $f = \frac{1}{T} = \frac{1}{2nt_p}$ ,  $t_p = \frac{1}{2}$

## **CMOS** Inverter

- Complementary NMOS and PMOS devices

- In steady-state, only one device is on (no static power consumption)

- □ Vin=1: NMOS on, PMOS off

- Vout =  $V_{OI} = 0$

- □ Vin=0: PMOS on, NMOS off

- Vout =  $V_{OH}$  = Vcc

- □ Ideal V<sub>OL</sub> and V<sub>OH</sub>!

- High input resistance (insulated gate) and low output impedance (finite resistance path between output and Vcc or Gnd)

- □ Ratioless logic

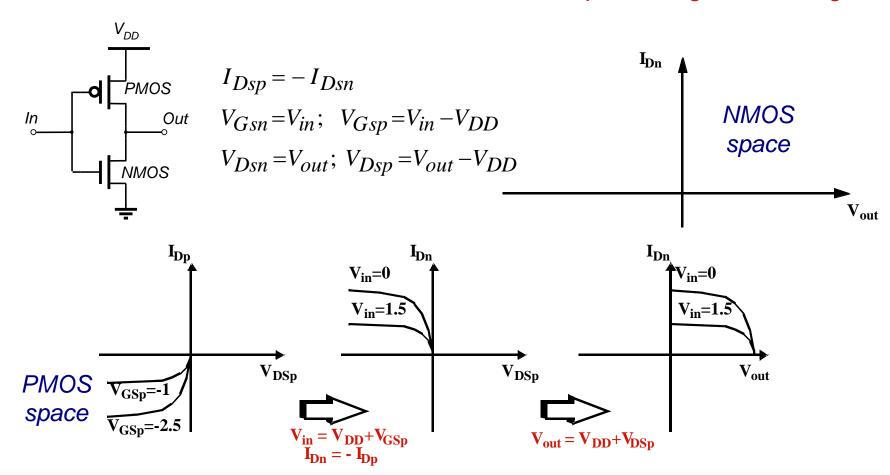

### Generating the Inverter VTC

A. Translate PMOS I-V Relations into NMOS Variable Space using the following:

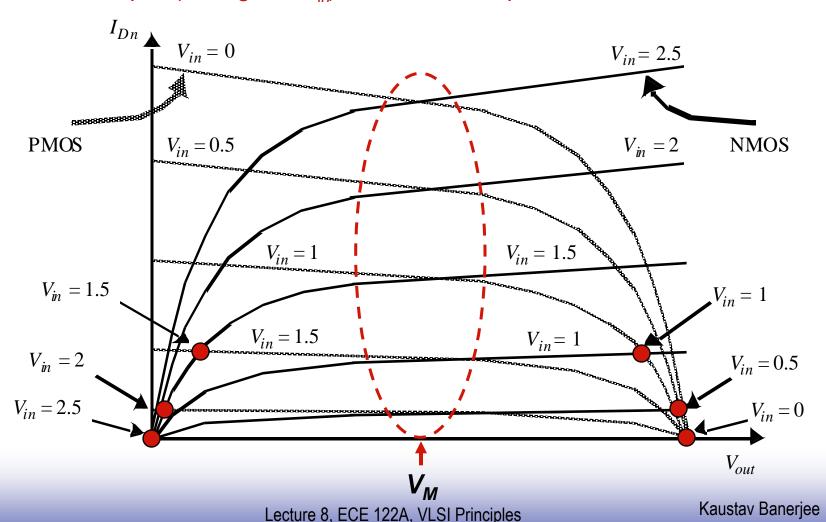

#### **CMOS Inverter Load Characteristics**

B. For a DC operating point to be valid, currents through NMOS and PMOS must be equal (for a given  $V_{in}$ ), hence find the points of intersection.

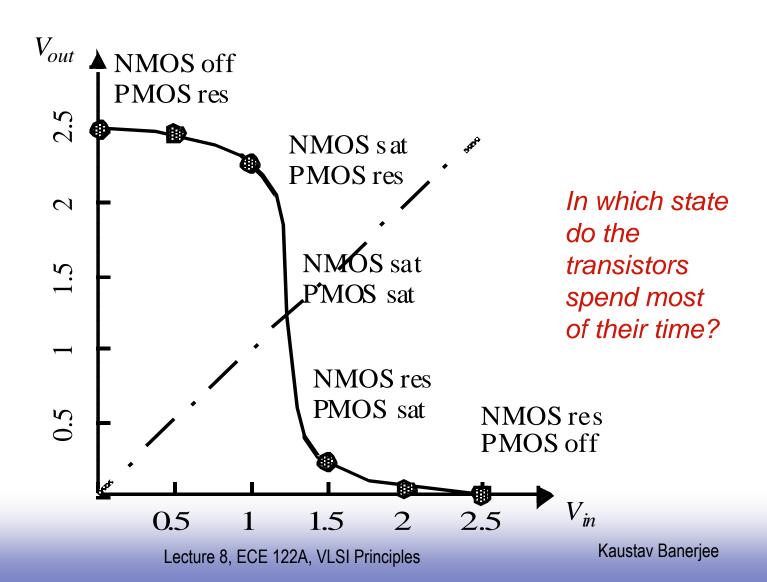

#### **CMOS Inverter VTC**

# **CMOS Inverter Operation (summary)**

| Table 2.2 | Relationships between voltages for the three regions of operation of a CMOS inverter |                                       |                                       |  |  |

|-----------|--------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|--|--|

|           | Cutoff                                                                               | Linear                                | Saturated                             |  |  |

| nMOS      | $V_{gsn} < V_{tn}$                                                                   | $V_{gsn} > V_{tn}$                    | $V_{gsn} > V_{tn}$                    |  |  |

|           | $V_{\rm in} < V_{tn}$                                                                | $V_{\rm in} > V_{tn}$                 | $V_{\rm in} > V_{tn}$                 |  |  |

|           |                                                                                      | $V_{dsn} < V_{gsn} - V_{tn}$          | $V_{dsn} > V_{gsn} - V_{tn}$          |  |  |

|           |                                                                                      | $V_{ m out}$ < $V_{ m in}$ - $V_{tn}$ | $V_{\rm out} > V_{\rm in} - V_{tn}$   |  |  |

| pMOS      | $V_{gsp} > V_{tp}$                                                                   | $V_{gsp} < V_{tp}$                    | $V_{gsp} < V_{tp}$                    |  |  |

|           | $V_{\rm in}$ > $V_{tp}$ + $V_{DD}$                                                   | $V_{\rm in}$ < $V_{tp}$ + $V_{DD}$    | $V_{\rm in}$ < $V_{tp}$ + $V_{DD}$    |  |  |

|           |                                                                                      | $V_{dsp} > V_{gsp} - V_{tp}$          | $V_{dsp} < V_{gsp} - V_{tp}$          |  |  |

|           |                                                                                      | $V_{\rm out} > V_{\rm in} - V_{tp}$   | $V_{ m out}$ < $V_{ m in}$ - $V_{tp}$ |  |  |

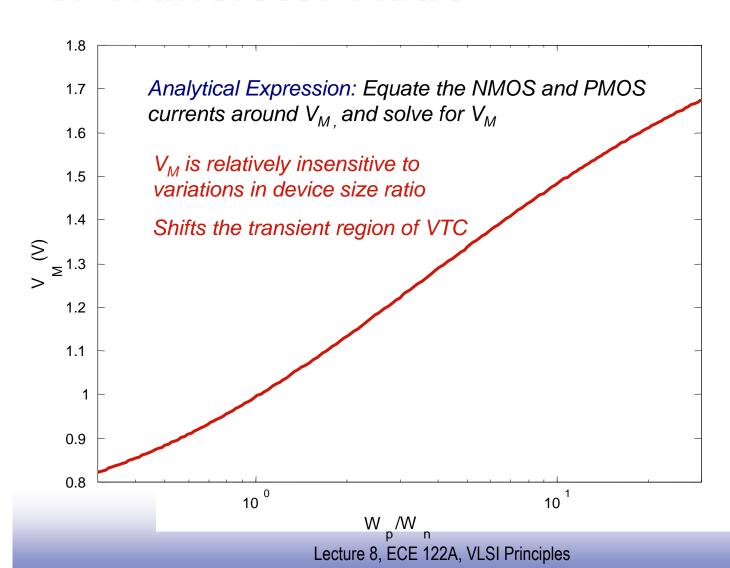

# Switching Threshold as a function of Transistor Ratio

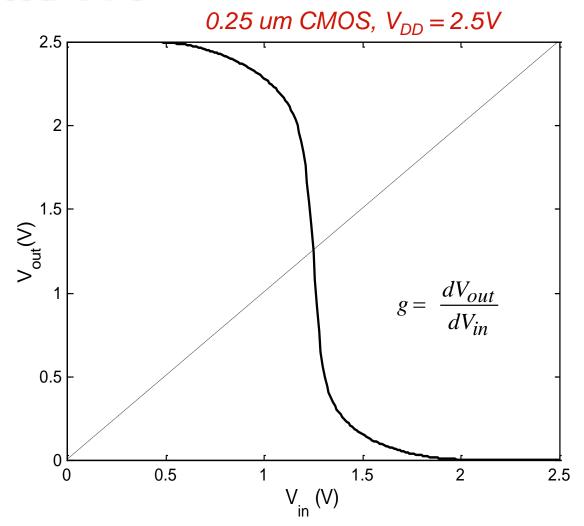

#### Simulated VTC

Note: piecewise linear approximation of the VTC would lead to higher gain

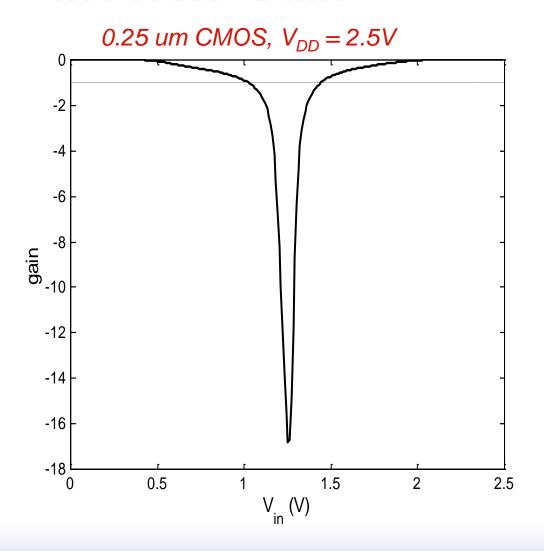

## **Inverter Gain**

Gain is mostly determined by technology parameters, especially channel length modulation, but also by V<sub>DD</sub>

Note: approximately  $V_M \propto V_{DD}$

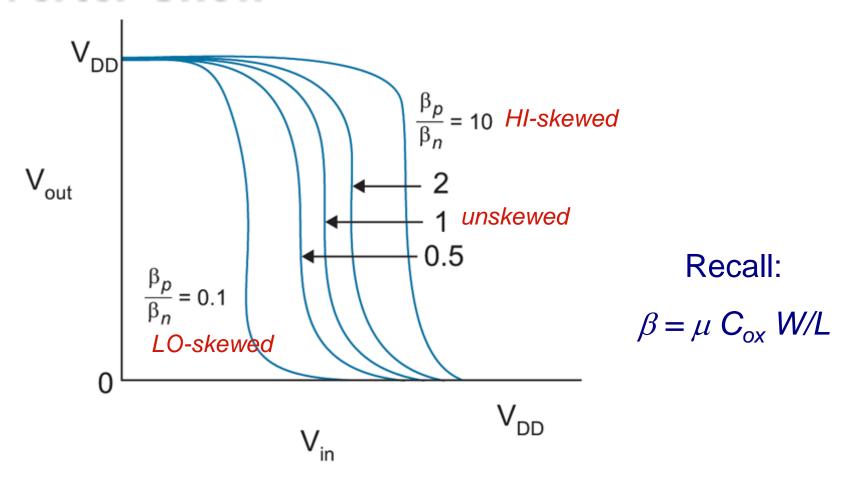

## **Inverter Skew**

FIG 2.26 Transfer characteristics of skewed inverters