# University of California, Santa Barbara Department of Electrical and Computer Engineering

## ECE 189A - Senior Computer Engineering Capstone Project

### Homework: PCB Design Introduction

This assignment introduces the PCB design software Eagle which is free to use for 3 years under an educational license from Autodesk. It can be installed on your personal computer as it is available for Windows, Mac OS, and Linux. This homework will be based on the <u>Eagle 9.5.1</u> Windows version.

In this assignment, we will be providing you with a central library that contains all the parts that you'll need pre-defined. This will simplify the process of designing the PCB to only the main portions of designing a PCB: schematic drawing and board layout. Additional complexities such as symbol, cell, and part creation as well as part library manipulation are skipped both in avoidance of any unnecessary confusion as well as the availability of downloadable parts from websites such as <u>snapeda.com</u>. This homework is just an introduction to the PCB designing process. If you would like to learn more about any of these other topics, there are an abundance of resources and tutorials for Eagle online. I recommend following these two tutorials for this homework:

Eagle Schematic Tutorial Eagle Board Layout Tutorial

They are slightly out of date, but they are mostly correct and will be a good guide in Eagle PCB flow.

#### Schematic:

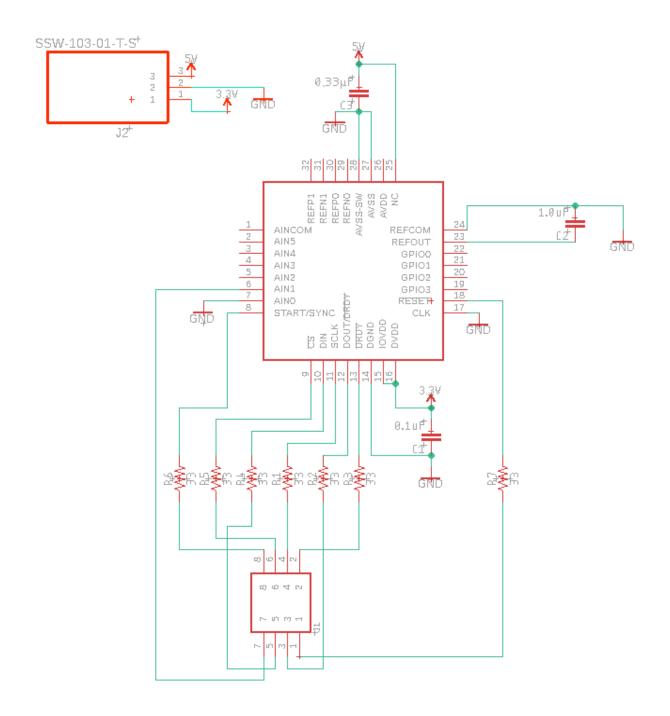

Use the provided library and create a schematic similar to the one below. To use this library, in the CE Capstone lab, copy Homework1.lbr file into your directory C:\Users\{CELabUsername} \Documents\EAGLE\libraries and restart Eagle.

Note: There will be multiple sizes for capacitors and resistors. For this homework, use the 0603 size when available and the 0805 size otherwise.

The figure in the next page depicts a schematic of an ADC with an analog input pin, SPI and data output pins along with a power input.

Some useful shortcuts:

- Middle click to drag around the schematic

- Right click when holding a symbol to rotate

- When placing parts, press esc to return to the parts selection window. Press it again to exit part placement completely.

- Right click a wire/part to bring up more options such as deleting.

### Layout:

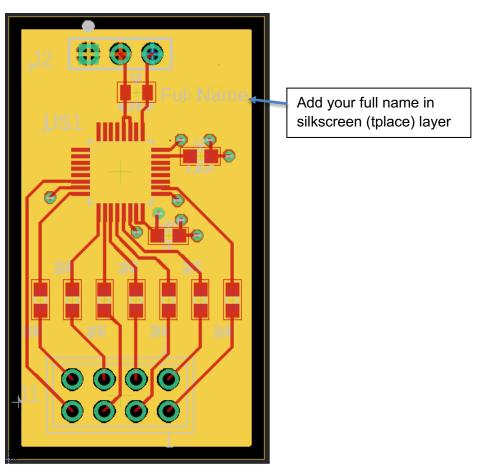

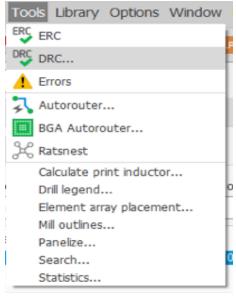

Next, you will you place and route the parts from your schematic onto the actual PCB layout as shown above. You must add your name on the Silkscreen layer as shown above. This will be a 4-layer board. You can set the board to 4 layers using the DRC window as shown below:

|    | Layers | Clearance | Distance | Sizes        | Annular Ring | Shapes      | Supply | Masks      | Misc |      |     |

|----|--------|-----------|----------|--------------|--------------|-------------|--------|------------|------|------|-----|

| 1  | _      |           | la       | Layer Pairs: |              |             |        | Via Pairs: |      |      |     |

| 2  |        |           |          | Layer        | Materia      | I Thickness |        | Туре       |      | From | То  |

|    |        |           | 1        |              | Copper       | 0.035       | imm    | Through    | 1    | 1    | 16  |

|    |        |           |          |              | Core         | 0.2m        | m      |            |      |      |     |

|    |        |           | 2        |              | Copper       | 0.035       | imm    |            |      |      |     |

|    |        |           |          |              | Core         | 1.5m        | m      |            |      |      |     |

|    |        |           | 1        | 5            | Copper       | 0.035       | imm    |            |      |      |     |

| 15 | ┥┝━━━  |           |          |              | Core         | 0.2m        | m      |            |      |      |     |

| 16 |        |           | 1        | 6            | Copper       | 0.035       | imm    |            |      |      |     |

|    |        |           |          |              |              |             |        |            |      |      |     |

|    |        |           | 4        | layers       | ¥            |             | - +    |            |      |      | • + |

|    |        |           |          |              | * *2*15*16)  | -           |        |            |      |      | . + |

Note: Please route traces with a 10mil width.

General tips and tricks for layout:

- Don't route directly under a chip unless you have to. You can route under in a different layer.

- If tying together multiple pins on a chip, bring the traces out rather than tying them directly together

- Make thermal pads slightly smaller

- Try to not make any signal wires travel a large distance or go through many vias

- 45 degree corners only

- Keep bypass capacitors close to the IC pins

- Ratsnest is a great tool for flooding planes

- Click on the + sign of the part to perform actions on it.

- Right click when routing to change the routing style. Leave it in the mode the outputs 45 degree angles.

- Modify the snapping of parts and routing using the grid menu. I recommend 10mil for the grid.

### Gerber Output:

Lastly, generate the gerber files in RS-274x format. To output the gerber, open up the cam processor and set the setting as shown below. Then process the job to output the gerber files.

| CAM Processor                                                       |                     |                       |                      |                      | -                 |           | $\times$ |  |

|---------------------------------------------------------------------|---------------------|-----------------------|----------------------|----------------------|-------------------|-----------|----------|--|

| SeeedFusion_4_layer.cam                                             | New<br>Oper         | Units:                | Metric               | *                    |                   |           |          |  |

| Drill                                                               | Rece                | nt CAM jobs 🕨 Silks   |                      | ÷.                   | 2                 |           |          |  |

| Drill Layer<br>Gerber                                               | Loca                | CAM jobs              |                      | Function: Other      | ~~~~ <del>~</del> |           |          |  |

| Mechanical                                                          | Tem                 | plates Fop            | Sikscreen            | Negative polarity    |                   |           |          |  |

| Bottom Paste                                                        | Third Party         |                       | AISLER >             |                      |                   |           |          |  |

| Top Paste                                                           |                     |                       | Beta Layout 🔹        |                      |                   |           |          |  |

| Bottom Solder Mask<br>Top Solder Mask                               |                     | # Layer               | OSH Park +           |                      |                   |           |          |  |

| Bottom Silkscreen                                                   | 21 tPlac∈           | Seeed Fusion +        | Seeed Fusion 2-Layer |                      |                   |           |          |  |

| Top Sikscreen                                                       |                     | 25 tName <del>s</del> |                      | Seeed Fusion 4-Layer | I                 |           |          |  |

| Bottom Copper                                                       |                     |                       | -                    | 52                   | _                 |           |          |  |

| Top Copper<br>Inner Layer 2                                         |                     |                       | · ·                  |                      |                   |           |          |  |

| Inner Layer 3                                                       |                     |                       | 1.14                 |                      |                   |           |          |  |

| Drawings                                                            |                     |                       |                      | 1.4                  |                   |           |          |  |

| Legacy                                                              |                     |                       |                      |                      |                   |           |          |  |

|                                                                     |                     |                       |                      | 2222222              |                   |           |          |  |

|                                                                     |                     |                       |                      | J1 4                 |                   |           |          |  |

|                                                                     |                     |                       |                      |                      |                   |           |          |  |

|                                                                     |                     |                       |                      | 1                    |                   |           |          |  |

|                                                                     |                     | 5                     |                      |                      |                   |           |          |  |

|                                                                     |                     | - •                   |                      | Board Sh             | ape               | Cuto      | outs     |  |

| + 1                                                                 | +                   | Output                |                      |                      |                   | _         |          |  |

| Seeed CAM file designed for versi                                   | ons 🔺               | Gerber filename:      | %N.GTO               |                      |                   | Export Fi | ile      |  |

| of Eagle prior to version 8.6. In                                   |                     |                       |                      | 21                   |                   |           |          |  |

| version 8.6, Gerber X2 format<br>compatibility was introduced which | Resolved file path: |                       |                      |                      |                   |           |          |  |

| is not currently supported by See                                   |                     |                       |                      |                      |                   |           |          |  |

| Fusion. Other minor adjustments<br>have also been made.             | ~                   | Advanced              |                      |                      |                   |           |          |  |

| Edit Description                                                    |                     |                       |                      |                      |                   |           |          |  |

| Select Board                                                        |                     |                       |                      | Pi                   | rocess Jo         | b Car     | ncel     |  |

|                                                                     |                     |                       |                      |                      |                   |           |          |  |

If you'd like to view your output files, you can upload the files to the following link as a zip: <u>http://www.gerber-viewer.com/</u>

Zip and submit the schematic, board layout and gerber files and you're done!