### **ECE594A Lecture Notes**

### **Track and Hold**

- 1. Sampling basics

- 2. Sample-hold/track-hold performance metrics

Acquisition time

Settling time

Droop rate

Pedestal error

Aperture uncertainty

- 3. Basic MOS switch sampler

- 4. Nonidealities

Input dependent resistance

Charge injection

Clock feedthrough

Hold feedthrough

Output voltage limitation

5. Signal to noise limitations

Quantization error

Aperture error

Thermal noise

Signal to distortion ratio

- 6. Methods for improving MOS samplers

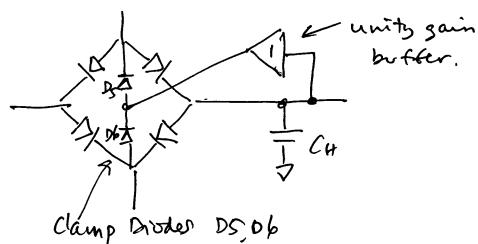

- 7. Diode bridge sampler

- 8. Emitter follower sampler

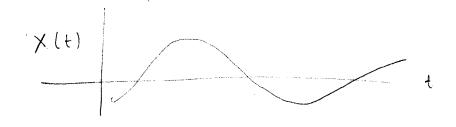

Sampling of Continuous Time Signals (Ideal)

$$y(kT_{5})$$

$$T_{5} \approx T_{5} \approx T_{5}$$

$$y(t) = \chi(t) \cdot \sum_{k=-\infty}^{\infty} \delta(t-kT_{5}) = \chi(kT_{5})$$

discrete samples at intervals kTs.

$$X(f) = \sum_{x(t)} e^{-j2\pi ft}$$

$$Y(S(t)) = 1$$

$$(convolution)$$

$$Y(f) = X(f) * \frac{1}{T_s} \sum_{n=-\infty}^{\infty} (f - \frac{n}{T_s})$$

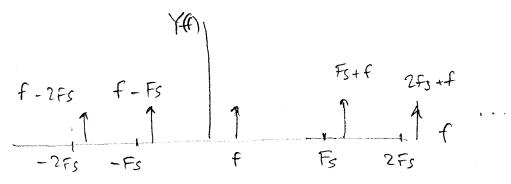

$$= \frac{1}{T_s} \sum_{n=-\infty}^{\infty} X(f - \frac{n}{T_s})$$

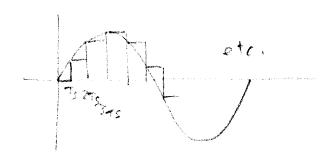

We see that the signal is replicated at intervals of n. to.

suppose x/t) = LOS 2019+

If we neglect phase and consider only positive freq.

we see that the signal is replicated (shifted) in frequency, This can lead to the problem of aliasing,

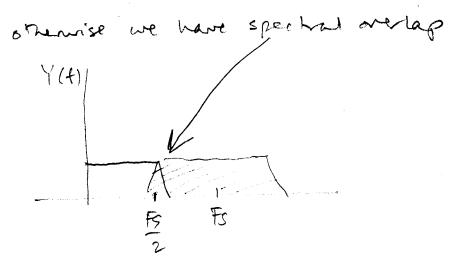

2f < Fs (Nygvist rule)

Also, we could not distinguish a signal at f. at f+nFs from a signal at f.

Same Sample values.

So, for Nyquist rate sampling, sampled signal must be band limited to below Fs.

1. LPF

2. Higher than Nyquist sampling rete

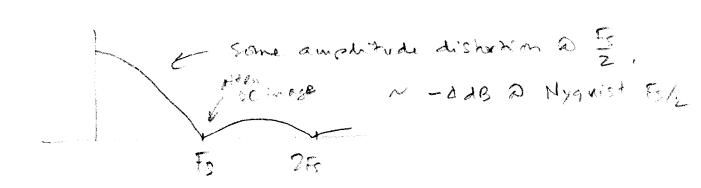

# Hold Function (zero order)

Since it is impractical to generate impulse trains, the sampled value is generally captured and held for  $E \leq Ts$ .

co, we have a rectangle function  $T(\frac{t}{T_3} - \frac{1}{2})$   $= u(t) - u(t - T_3)$   $\times (t) - (3)$

This has the effect of taking the periodic train of impulses and convolving with the rectangle.

$$y(t) = \left[ x(t) \sum_{k=-\infty}^{\infty} \varepsilon_{1} t - k \tau_{s} \right] * \prod \left( \frac{t}{\tau_{s}} - \frac{1}{s} \right)$$

so we multiply frequespenses to get spectrum of sample-hold.

$$Y(t) = Y(t) \cdot T\{T(\frac{t}{\tau_s} - \frac{1}{2})\}$$

$$= e^{-j\pi f T_s} \cdot \sin(\pi f T_s) \xrightarrow{\infty} X(t - \frac{n}{\tau_s})$$

$$= e^{1} \cdot T_s \cdot \sin(\pi f T_s) \xrightarrow{n=-\infty} X(t - \frac{n}{\tau_s})$$

can be corrected by equaliting inverse sinc filter it musseage I in case of DAC for example).

ADC Appent need correction—

samples the held signal— ideal case.

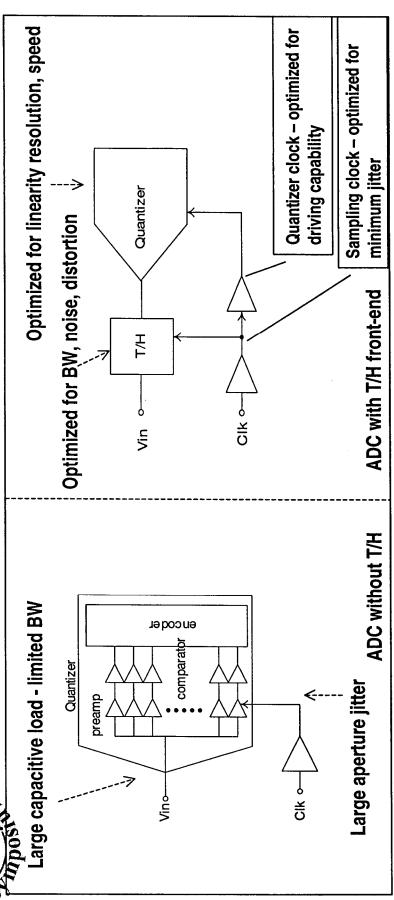

# Why Track and Hold?

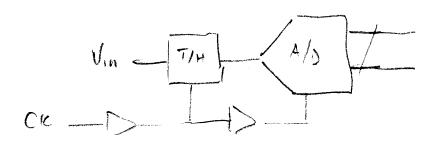

- T/H is essential for multi-stage ADC architecture

- Pipeline ADC

- Subranging ADC

- Folding converter

- Algorithmic converter

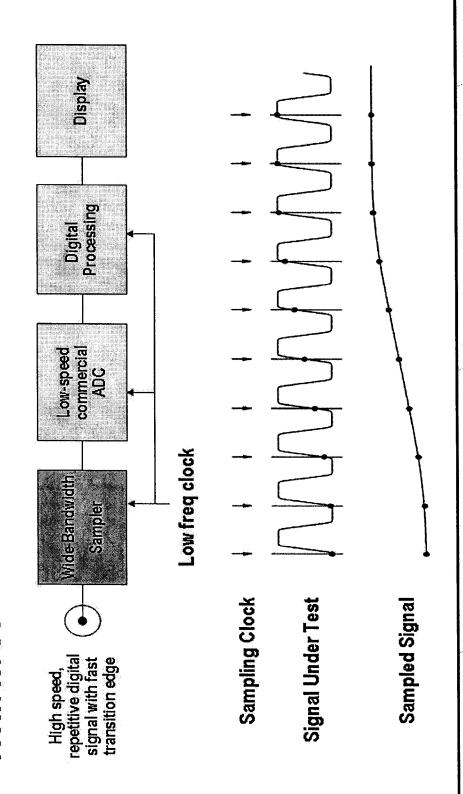

# Wide-band T/H in sub-sampling application

Used in ATE, Oscilloscope, Jitter Measurement, Signal Integrity Tester for OC

# T/H architectures

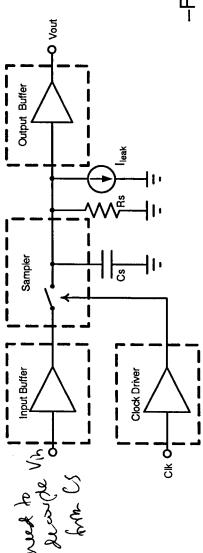

mposity Input buffer / Sampling switch / Hold capacitor / Clock driver / Output buffer

A/D can have

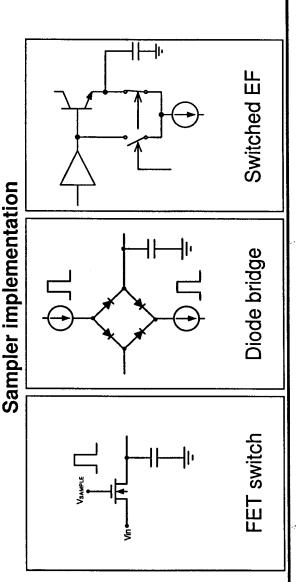

- –FET switch

- No static power

- Non-linear charge injection

- Limited bandwidth

- -Diode bridge

- Widest bandwidth

- -Switched emitter follower

- Good linearity, large dynamic range

Simple open long SH

include ox

By

Cu b

Held

coperator

at t=nTs, Ewitch closes.

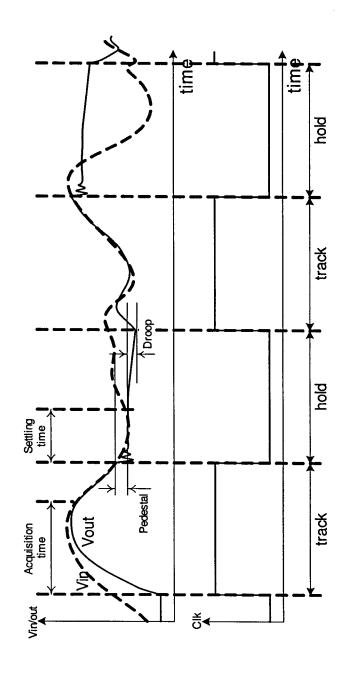

Acquisition time:

time to experience full crace transition and settle within an error band.

(full data pata)

Hold Setling Time.

Bz. time after hold command to settle within arrow band

DR. Maxingur - Min ingut

# T/H operation

- Performance requirement

- Large track mode bandwidth

- Small track mode distortion

- Low noise

- Small or linear pedestal error

- Small droop

- Fast recovery

Pedostal.

server when switch from sample to hold

Droop.

discharge of C4

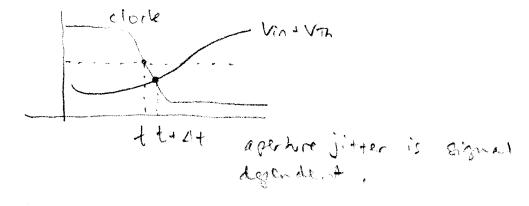

Aperture Jimer or Uncertaints

Let

$$Vin = A \sin \omega t$$

$$\frac{\partial Vin}{\partial t} = A \cos (\omega t)$$

$$\frac{\partial A + \partial A}{\partial t}$$

$$\frac{\partial A}{\partial t} = \frac{\partial A}{\partial t}$$

$$\frac{\partial A}{\partial t} = \frac{\partial A}{\partial t}$$

For N bit accuracy,

$$\left(\frac{1}{2}LSB\right)$$

$$\frac{\Delta A}{2A} \angle \frac{1}{2^{N}} \qquad \Delta t = \frac{2A}{2^{N} \cdot A\omega \cos \omega t}$$

So,  $\Delta t \angle \frac{2^{-N}}{\pi f_{in}} \cos(2\pi f_{in}t) = \frac{2^{-N}}{\pi f_{in}}$

(for greatest slope)

ex. 146, 500 MHZ

1t 4 40 fs

serious requirement for high speed samples, ADCS.

of course, placing T/H before A10 is helpful—

can be optimized for minimum aporture jither

and allows A15 to be optimized for accuracy

and a appeal

# MOS Switch

asymmetry requires harmonics

1+D

prelations:

1. Resistance toperds on Vas which depends on Vin.

Pyon would like lage with W to get more seed.

Eun V., tarq V

tarq. will depend on Vin

2. Charge injection.

ach = WL Cox (VOS- VTH)

when turn off device, this channel charge must seave through SID. This causes a gain error since Och degends on VGS.

Vou depends on body affect.

This can introduce nonlinear Och (Vin).

HD, 1100 is generated.

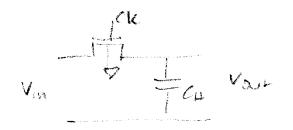

3. Clock Feelthough

everlap cap (ov charge sharing products offset error

4. Sampling instant depends on Vin.

Switch turns off when Ves- Van 60.

12vt., Ves depends on Vin.

need fast clock edge

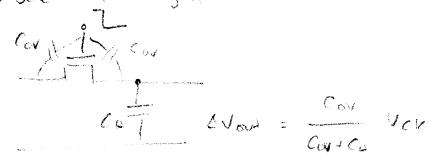

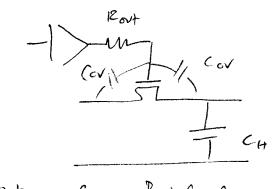

5. Hold feedtam

$$\frac{V_{\text{out}}}{V_{\text{in}}} = \frac{C_{\text{ov}}}{C_{\text{H}}} \frac{P_{\text{out}} C_{\text{ov}} s}{2 R_{\text{out}} C_{\text{ov}} s + 1}$$

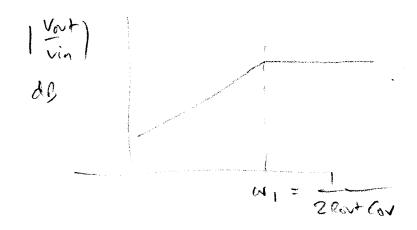

6. Reduced output range.

less resistance, variation. charge injection not helped: différent VGS - Vm Today (Lec 3)

Sig/Noise limiters.

Quantization error SNR ave to aperture - Sig. dependence SDR Themas Morse

Methods for improvement of samplers

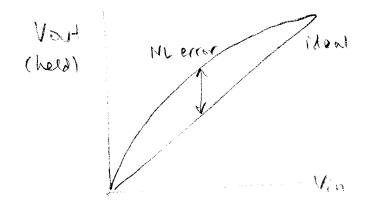

Gain -> straight line through center

$$\pm \frac{\Delta}{2} = \text{enorband}.$$

$$M = \# \text{bits}$$

Signal power:

$$P_S = \frac{A^2}{2} = \frac{(2^m - 1)^2}{2} = 2^{2m-3} \Delta^2$$

Quantitation Noise pener:

$$P_n = \frac{1}{\Delta} \int_{-4/2}^{+4/2} e^2 de = \frac{\Delta^2}{12}$$

SNR due to quantization noise:

$$SNR = \frac{Ps}{P_n} = \frac{2^{2m-3}\Delta^2}{\Delta^2/12} = \frac{3}{2} 2^{2m} = (6.62m + 1.76)d$$

was needed for high frequency TH to remain accumte to  $\pm \frac{1}{2} LSB$ .

another way to look at this is to consider the maximum signal-to-noise ratio that can be attained by a given aperture uncertainty z.

SNR = 20 log

$$\left(\frac{V_{FS}(Ims)}{Noise(vms)}\right)$$

$V_{FS}(vms) = \frac{V_{FS}}{2\sqrt{2}} \left(\frac{1}{full scale} / 2 \cdot \frac{1}{\sqrt{2}}\right)$

$N(vms) = \tau \cdot \left(\frac{d(V_{in})}{dt}\right)_{vms}$

$= \tau \cdot \sqrt{\frac{1}{T}} \int_{0}^{T} \left(\frac{dV_{in}}{dt}\right)^{2} dt = \frac{\sqrt{2}}{2} \pi V_{FS} F_{in}$

$SNR = 20 log \left(\frac{1}{2\pi F_{in} T}\right)$

$$8hits = > SNR = (6N + 1.76)dB$$

$= 50dB$

$= 50dB$

$= 500MHt \rightarrow T = 1.68pS$

## Themal Noise.

channel/smitch resistance

part of the speed-noise tradeoffs

(AS) in pass

'/pc

logf

Vi= Vn

Total nuise parer

$$N = \int_{0}^{\infty} |V_0|^2 df = \frac{kT}{C}$$

large c, low themal noise floor but lover speed.

# Signal-to-Distortion Ratio. (SDR)

Ref. Lim and Wooley, "A High Speed Sample and Hold Technique...," J. Solid State Cir., vol 26, 14, april 1991.

input dependent sampling creates harmonic distortion. In the appendix to the above Paper, the authors present some empirical results from Simulations:

$$V_{\text{OUT}} = A \sin[2\pi f_{\text{IN}}] \left[ t - \frac{A}{V_{\text{CL}}} \cdot t_{\text{TR}} \cdot \sin 2\pi f_{\text{t}} \right]$$

reconstructed signal (sine ware)

A = Signal amplitude

VCL = clock voltage amplitude

tre = clock transition time

SDR = 20 log

$$\left(\frac{\sqrt{c\kappa}}{t_{TR}}\right)\left(\frac{1}{Af_{IN}}\right) - 4$$

Clock

Slew

rate  $\left(\frac{Sig.}{slew}\right)$

SO SDR may be limited by input-dependent sampling

# Charge injection affect error.

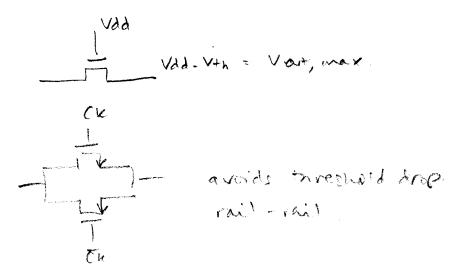

Charge Cancellation to w/2

of the office w/2

office of the office of t

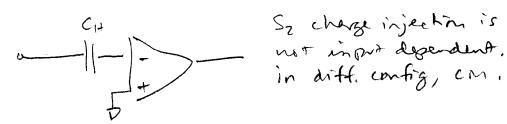

# Differential verion

charge injection shows up

Vint > Vint, so amount

a chase injection is

not equal.

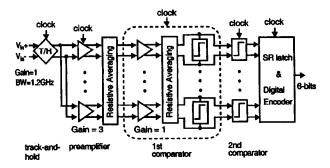

Fig. 2. Block diagram of 6-b flash A/D converter.

comparator. However, the preamplifiers in the array suffer from random offsets. Collective averaging of the preamplifier outputs across a properly designed resistor network lowers the impact of the offsets, improving accuracy of the threshold comparison without degrading bandwidth [13]. A comparator must quickly recover from large overdrive when the changing input voltage rapidly approaches the comparator's threshold from far away. To aid this, the gain of the comparator's input differential pair is about one, which widens its bandwidth. The resulting net amplification of 3 is not sufficient to overcome the dynamic random offsets in the regenerative latch for 6-b accuracy. Resistor averaging is also used within the comparators to lower the impact of offsets. Interpolation is not used in this work, because it degrades bandwidth [12], [13]. The second comparator array provides rail-to-rail logic swing for the digital back end consisting of the SR latch and ROM-based digital encoder.

### III. OFFSET AVERAGING

### A. Accuracy Improvement With Averaging Network

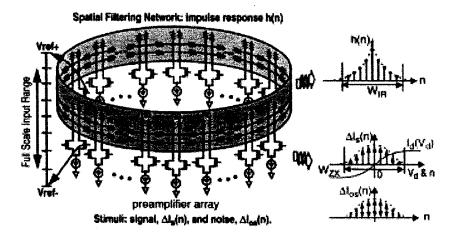

Fig. 3 shows a preamplifier array with averaging resistors R1 connecting adjacent output nodes. In this work, offset averaging is treated and optimized based on the concept of spatial filtering [13], [14]. The R0–R1 network forms a spatial filter with impulse response h(n)

$$h(n) = h(0) \cdot b^{|n|}, \qquad b = e^{-|\operatorname{acosh}(1+R1/2R0)|}$$

(1)

where n represents the index of differential pairs in the array. The ratio R1/R0 determines the width of the impulse response. An array of differential pairs injects two different types of stimuli currents in the averaging network. First, differential signal currents  $\Delta I_s(n)$  limited by the linear region of the differential pair enter the network. Second, "noise" currents  $\Delta I_{os}(n)$  due to transistor random mismatches also enter the averaging network. A well-designed averaging network should filter out the random currents, without losing valuable signal current, nor should the network lower bandwidth. Averaging is optimum when  $W_{ZX}$  (the number of differential pairs in the unclipped linear region of their characteristic) is greater than the impulse response width of the network  $W_{IR}$  [13].

Dummy preamplifiers are inserted to compare the input signals with thresholds beyond the actual full scale, so that the tails of the averaging network's impulse response remain undistorted at the ends of the full scale. A circular arrangement with suffi-

cient dummy preamplifiers maintains translational symmetry of the array across the input full scale.

### B. Speed Improvement With Averaging Network

It is by now well known that averaging improves accuracy. What is not as well appreciated, as explained below, is that averaging also improves speed.

The input random offset voltage is inversely proportional to the square root of the transistor gate area [15]. Therefore, preamplifier FET size may be related to the target ADC resolution as follows.

$$\sigma V_{os} \approx \frac{A}{\sqrt{(W \cdot L)_{\text{input}}}} \le \frac{1}{4} \cdot \text{LSB}.$$

(2)

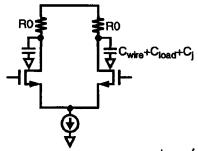

References [13], [14] show that the optimum averaging network lowers random offset by up to  $3\times$ , with a spatial impulse response  $W_{ZX}$  18 nodes wide. With this network connected to the outputs of a preamplifier array, a given accuracy is maintained with  $9\times$  smaller FETs than if no averaging were used. The bandwidth as set by the output pole of this differential pair, shown in Fig. 4, is

$$BW_{\text{single}} = \frac{1}{R0 \cdot (C_{\text{wire}} + C_{\text{load}} + C_j)}.$$

(3)

With averaging, the wiring and junction capacitance are  $9 \times$  lower due to transistor scaling  $(3 \times \text{less } gm)$ . For the same bias current, the load resistance R0 must be  $3 \times \text{larger}$  for equal voltage gain, which means that

$$BW_{\text{withavg}} = \frac{1}{3 \cdot R0 \cdot (C_{\text{wire}}/9 + C_{\text{load}} + C_j/9 + C_{\text{network}})}$$

(4)

where  $C_{\rm network}$  is the parasitic capacitance of the averaging network. Comparing the two terms from (3) and (4)

$$\frac{\mathrm{BW_{single}}}{\mathrm{BW_{withavg}}} = 3 \cdot \left[ 1 + \frac{C_{\mathrm{network}}}{C_{\mathrm{wire}} + C_{\mathrm{load}} + C_{j}} - \frac{8}{9} \right] \cdot \left( \frac{C_{\mathrm{wire}} + C_{j}}{C_{\mathrm{wire}} + C_{j} + C_{\mathrm{load}}} \right) \approx \frac{1}{3}. \quad (5)$$

The second term in (5) is much less than 1, while the third term is close to 1. Therefore, use of the averaging network raises preamplifier bandwidth by  $3\times$ .

### IV. CIRCUIT DESCRIPTIONS

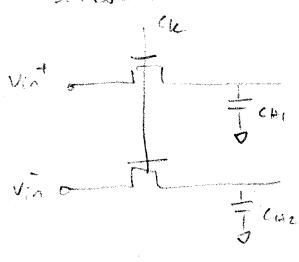

### A. Track-and-Hold

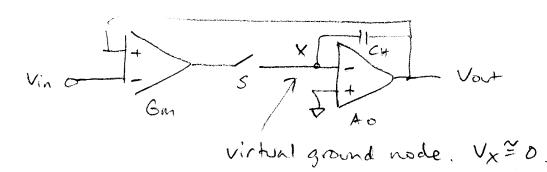

An input T/H improves the dynamic performance of an ADC. By holding the analog sample static during digitization, the T/H largely removes errors due to skews in clock delivery to a large number of comparators, limited input bandwidth prior to latch regeneration, signal-dependent dynamic nonlinearity, and aperture jitter [11]. The on-chip T/H circuit shown in Fig. 5 precedes the flash quantizer. This simple circuit, consisting of a passive nMOS switch connected to a sampling capacitor through a dummy switch [16], [17], offers just the required linearity. The dummy switch lowers the common-mode jump after the track-to-hold transition. The main sources of distortion

Fig. 3. Preamplifier array with resistor averaging network.

Fig. 4. Single differential amplifier.

Vin. FS = 1.6V

Vin. FS = 1.6V

Vin. clik

Vin. c

Fig. 5. On-chip track-and-hold.

are signal-dependent charge injection on switch opening, nonlinearity of the source follower, and dynamic current into the signal-dependent input capacitance of the quantizer.

FET charge injection and clock feedthrough cause distortion by adding/removing charge on the hold capacitor when the switch disconnects the signal source [18]. A dummy switch driven by the complement of the switch clock lowers these effects [19]. Because both the source and drain of the dummy switch are connected to the hold node, its W/L ratio is initially chosen as half the size of the switch, and then tuned through simulation. A low input common-mode voltage, 0.5 V, enables use of only nMOSFETs for the sampling and dummy switches. Unlike a complementary switch, nMOS (or pMOS)-only switches

effectively cancel charge feedthrough, even with process variations.

Sample jitter due to the input-dependent switch opening is another distortion source and is described by the following output equations with a differential sine input.

$$V_{\text{out}} = V_{\text{outp}} - V_{\text{outn}}$$

$$= 2 \cdot A \cdot \sin(2\pi f t) \cdot \cos\left(2\pi f \cdot \frac{A}{V_{\text{CL}}} \cdot t_{\text{TR}} \cdot \sin(2\pi f t)\right)$$

(6)

where  $V_{\rm CL}$  is the maximum clock voltage,  $t_{\rm TR}$  is the transition time of a clock edge, f is the input frequency, and A is the input amplitude [20]. For given  $V_{\rm CL}$  (3.3 V),  $t_{\rm TR}$  (0.15 ns), f (500 MHz), and A (0.4 V), the total harmonic distortion is -68 dB for the differential output, and -25 dB for the single-ended.

The low-input common-mode voltage of 0.5~V allows a larger gate overdrive to turn on the switch, which lowers track-mode distortion due to nonlinear channel resistance. The source is tied to the well in the pMOS source follower to eliminate nonlinear body effect. Simulations show that when acquiring samples of a 250-MHz full-scale sine wave at 1~Gsample/s, the T/H delivers samples to the quantizer input with third-harmonic distortion of about -60~dBc.

### B. Preamplifier

The preamplifier stage should be wideband and provide sufficient gain to overcome comparator offsets. It should also recover from large overdrive within one clock cycle. An open-loop low-gain-stage amplifier is gain-bandwidth limited, therefore unsuitable for use at high speeds because of poor overdrive recovery [6], [21]-[23].

The following analysis addresses the fundamental limitation of an open-loop single-pole amplifier stage in overdrive recovery and justifies quantitatively that an amplifier with a reset switch meets the speed requirement. Consider a simple one-stage single-pole amplifier, shown in Fig. 4. The preamplifier is completely unbalanced at t=0-. With a step input applied to

- · but doesn't holp charge injection since Vos-V+h isn't squal of 6.12 devices.

- · But, resistance voltation und vin is reduced.

- . Clock edge misalignment causes sampling instant shift that depends on Vin.

How are base errors addressed?

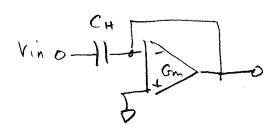

# 1. Closed Loop Architectures

· Feedback keeps Vout = Vin when S is closed.

not ingut dependent.

- · Holds Vous when open

- · Constant Vx on S means no Vin dependent charge injection or pedestal error.

offset is constant. No nonlinearity,

This can be modified to cancel offset (podestall) and chick feed through.

Common mode cancellations

Freden: stability us speed - tends to be slow.

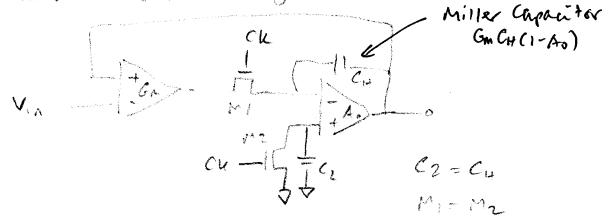

• GarCH (1-A0) forms dominant pole

con easily overcompensate.

o if undercongensate, her settling time is degraded

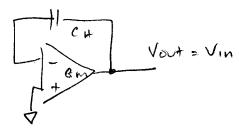

Pedestal error can also be reduced in an open loop architecture by using separate sample and hold capacitors. Faster architecture.

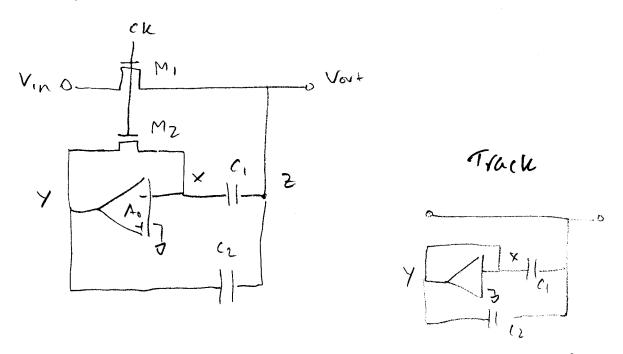

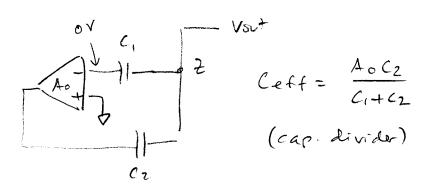

in acq. mode, M. and M2 are on.  $V_x = V_y^*$ , so  $C_1$  and  $C_2$  have the same charge,  $V_{in} = V_{DU}t$ .

Hold: M, M2 off. Node 7 sees Miller multiplied capacitance (2

Node X and y are at ground when enter hold, so nonlinear charge injection.

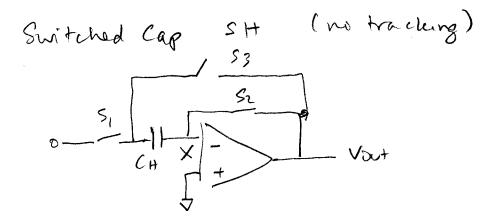

Sample: 5,, Sz on.  $V_X = 0 = Vout$

CH is charged to VIN

Itold: turn off Sz first, CH retains Vin

next turn off SI, and S3 on.

Si charge injection direct aftert charge on CH.

Diode Snitches  $T = V_T + V_{contact}$   $V_{in} = V_{out} + V_{out}$   $T = V_T + V_{contact}$   $T = V_T + V_T + V_{contact}$   $T = V_T + V_$

# Better inclementation

Volume + 05,06 prevents saturation of Q2.

Mid input range

both off in sample on in hold state.

Diode Bridge.

Saves of error.

- 1. Signal dependent bridge current.

- 3. input dependent pedestal offset

- 2, on-resistance varies with Vin

CH charges brough DZ. Decreases r D1, D4 conduct less. Increases r These changes must be small relative to on-resistance of switch.

$$V_{X} = V_{1n} + V_{0}$$

$$V_{Y} = V_{1n} - V_{0}$$

$$V_{X} = V_{01} - V_{0}$$

$$V_{Y} = V_{01} - V_{0}$$

$$V_{Y} = V_{01} + V_{0}$$

$$V_{Y} = V_{01} + V_{0}$$

$$V_{Y} = V_{01} + V_{0}$$

because junction capacitance of Dz, Da depends on voltage, pedestal has nonlinear tem. Compensate by tracking VBI with Vort.

4. Hold-mode feed man.

# An 8-Bit 2-Gsample/s Folding-Interpolating Analog-to-Digital Converter in SiGe Technology

Farhang Vessal, Student Member, IEEE, and C. Andre T. Salama, Fellow, IEEE

Abstract—This paper deals with the design and implementation of an 8-bit 2-Gsample/s folding-interpolating analog-to-digital converter (ADC) using a SiGe technology with a unity gain cutoff frequency  $f_T$  of 47 GHz. The high-speed high-resolution ADC has applications in direct IF sampling receivers for wideband communication systems. The converter occupies an area of 3.5 mm  $\times$  3.5 mm including pads and exhibits an effective resolution bandwidth of 700 MHz at a sampling rate of 2 Gsample/s. The maximum DNL and INL are 0.5 and 1 LSB, respectively. The ADC dissipates 3.5 W (including output buffers) from a 3.3-V power supply.

Index Terms—Analog-to-digital converter (ADC), folding-interpolating, heterojunction bipolar transistor (HBT).

### I. INTRODUCTION

NALOG-TO-DIGITAL converters (ADCs) are widely used in modern communication systems to interface analog waveforms with digital signal processing (DSP) circuitry. By moving the ADC closer to the system front-end, the majority of the processing can be performed in the digital domain. To take advantage of the increasing speed and sophistication of digital signal processing, the ADC must operate at high sampling rates and low voltages, and remain immune to a noisy digital environment. This brief describes the design and implementation of an 8-bit 2-Gsample/s ADC with an on-chip track-and-hold amplifier (THA) using a SiGe heterojunction bipolar transistor (HBT) technology with a  $f_T$  of 47 GHz. Compared to conventional bipolar junction transistors (BJTs), SiGe HBTs have improved high-frequency behavior and low base resistance.

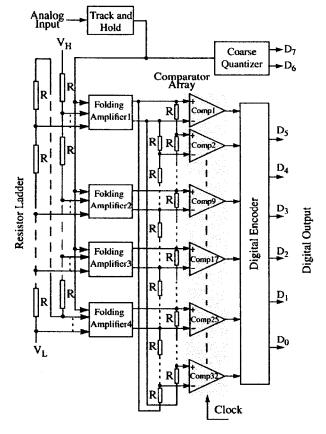

### II. BLOCK DIAGRAM

The block diagram of a folding-interpolating architecture is illustrated in Fig. 1. The output of the track-and-hold circuit is applied to the input of four folding amplifiers where it is compared to reference voltages generated by a resistor ladder. The output of the folding amplifiers is a set of phase-shifted sinusoid-like signals which are, in turn, applied to an array of comparators. The outputs of the comparators are the representation of the input signal in thermometer codes. These codes are eventually converted back to binary codes by a digital encoder to produce the six least significant bits (LSBs). The two most significant bits (MSBs) are produced by a coarse quantizer. The

Manuscript received December 2, 2002; revised August 19, 2003. This work was supported by NSERC, Micronet, Gennum, Nortel Networks, PMC Sierra and Zarlink.

The authors are with the Department of Electrical and Computer Engineering, University of Toronto, Toronto, ON M5S 3G4, Canada (e-mail: salama@vrg.utoronto.ca).

Digital Object Identifier 10.1109/JSSC.2003.820867

Fig. 1. Block diagram of the folding-interpolating ADC.

folding-interpolating architecture is very suitable for high-resolution converters that require a large analog bandwidth.

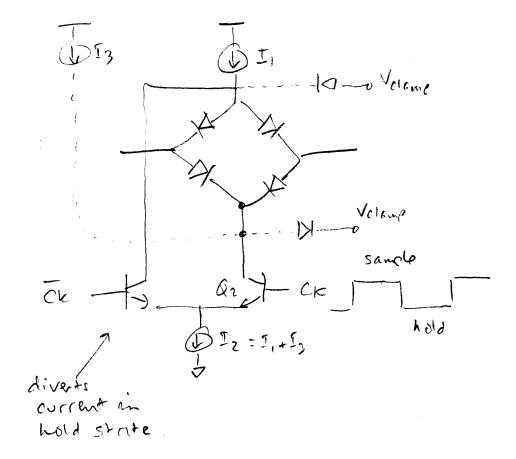

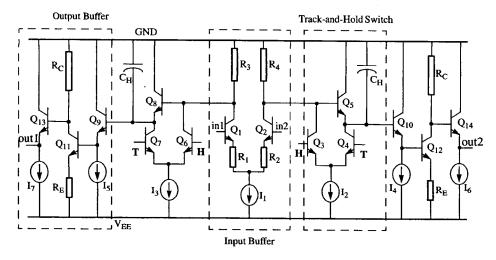

### A. Track-and-Hold Amplifier

The THA at the front-end of the converter performs the time sampling of the input signal. A simplified circuit diagram of the THA circuit is given in Fig. 2 [1], [2]. It consists of an input buffer, sampling switches, and output buffers. The differential input buffer consists of a differential pair  $Q_1$  and  $Q_2$  with degenerative feedback  $(R_1,R_2)$ , loaded with resistors  $R_3$  and  $R_4$ . The differential input signals are applied to the bases of the transistors  $Q_1$  and  $Q_2$ . The differential output of the input buffer go to the track-and-hold switches. Each track-and-hold switch consists of three transistors  $(Q_3,Q_4,Q_5)$ , a current source  $(I_2)$  and a holding capacitor  $(C_H)$ . There is a compromise between the droop rate and the bandwidth of the THA in choosing the proper value for  $C_H$ . Lowering the value of  $C_H$  increases the bandwidth but deteriorates the droop rate. In this work, a value

Fig. 2. THA circuit.

Fig. 3. (a) Folding amplifier circuit. (b) Comparator circuit.

of 0.9 pF was chosen for  $C_{\rm H}$  to get an analog bandwidth of at least 4 GHz and a droop rate of 10 mV/ns.

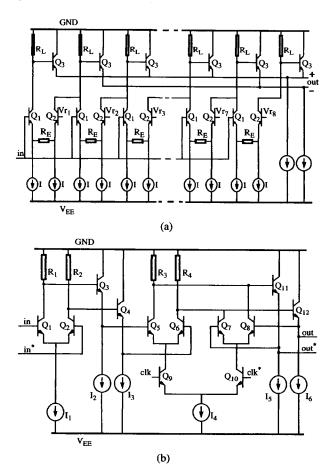

### B. Folding Amplifier

The topology of the folding amplifier used in this implementation is shown in Fig. 3(a). The basic function performed

by the folding amplifiers is the conversion of the increasing (or decreasing) input signal into a number of sinusoid-like output signals [1]. Each folding amplifier generates eight zero-crossings, equidistantly spaced over the input range. Four folding amplifiers are used in parallel, generating the required 32 zero-crossings. To ensure that the ADC achieves the required 8-bit resolution, accurate zero-crossing points must be generated by the folding circuits. In order to reduce the mismatch between Q1 and Q2 in each differential pair, these transistors should be large enough, but increasing the size of these transistors affects the loading capacitance of the previous stage (THA) in the system; therefore, a compromise must be considered in choosing the size of Q1 and Q2 during the design of this stage. In this design, the size of these transistors was chosen to be  $0.5 \times 5 \ \mu m^2$ . Biasing conditions are a tradeoff between bandwidth and power consumption. The bandwidth of the circuit is inversely proportional to the value of R<sub>I</sub>. A large R<sub>L</sub> leads to a serious analog bandwidth limitation. In addition, the shape of the sinusoid-like waveforms must exhibit high linearity around the zero-crossing points because linear interpolation between two adjacent folding signals is necessary. The interpolation is implemented using a resistive string because of its simplicity and power efficiency. In this design, differential interpolation is implemented by applying the differential outputs of the folding amplifiers to the differential resistive strings. This differential implementation improves the accuracy of the converter.

### C. Comparator

The comparators consist of a two-stage preamplifier  $(Q_1 - Q_4)$  and a latch  $(Q_5 - Q_{10})$ , as illustrated in Fig. 3(b). Such a comparator architecture reduces the kickback noise to an acceptably low level and provides a relatively high gain, which in turn lowers the offset contributed by the latch and improves the metastability behavior of the comparator. Transistors  $Q_5$  and  $Q_6$  form a tracking differential pair (track pair) that produces a differential voltage across resistors  $R_3$  and  $R_4$ . A second differential pair,  $Q_7$  and  $Q_8$  (latch pair), connected in a positive-feedback configuration, latches the differential signal. To reduce