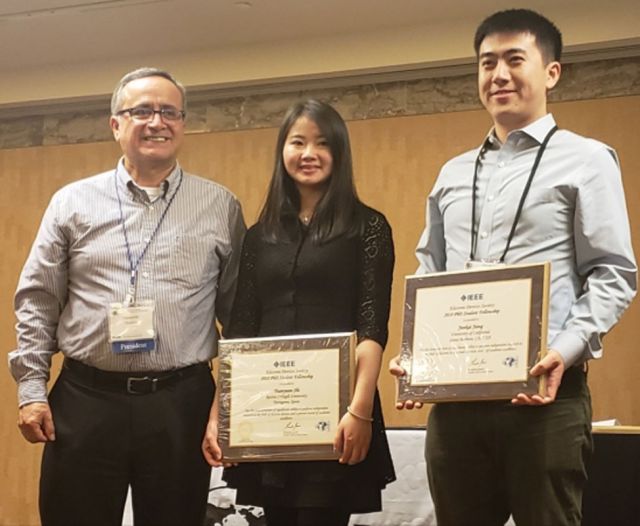

Jiang “Pushing Past Limits”

PhD student Junkai Jiang awarded student fellowship from the IEEE Electron Devices Society in the broad area of electron devices

The steady improvement of the performance and versatility of our electronic systems is due in large part to the scaling-down of transistors and interconnects that drive them. Components on the chips have been shrunk, stacked and more densely packed to add increased functionality without expanding the systems’ small footprints.

But the smaller, denser arrangements present their own set of challenges, and electronics engineers and designers everywhere are trying to find ways to overcome the resulting degradation in performance, reliability and energy efficiency – and doctoral student Junkai Jiang is one of those people.

Jiang’s work centers on interconnects — the conducting channels of electronic signal and power between and through components. Interconnects play a dominant role in determining the performance and power-dissipation of all integrated circuits, including state-of-the-art microprocessors. As the dimensions of on-chip components have scaled down and their number has increased, the conventional copper wire interconnects have also had to shrink, causing them to hit limits in terms of their ability to conduct signal and power rapidly, reliably and without interference. As a result, the systems may slow down, overheat and drain their batteries sooner than expected.

The answer to this problem could come in the form of graphene, a two-dimensional form of carbon with interesting and valuable electronic properties.

“My research is focused on designing and fabricating fast, energy-efficient and highly reliable on-chip interconnects and passives uniquely enabled by low-dimensional carbon nanomaterials such as graphene,” Jiang explained.

Graphene, with its atom-thick dimension and electronic conduction properties, has emerged as a viable replacement for copper wire interconnects primarily driven by his advisor, ECE Professor Kaustav Banerjee over the past decade. But its ability to revolutionize modern electronics is directly related to the ease of large-scale manufacture, which also is a thrust of Jiang’s research.

“Supported by this award, I have been working on integrating graphene in the high-volume-manufacturing friendly or ‘CMOS-compatible’ process and its application in demonstrating a multilayer VLSI (Very Large Scale Integrated Circuit) interconnect scheme to establish its feasibility for the semiconductor industry,” Jiang added.

“I offer sincere congratulations to Junkai Jiang for receiving this prestigious award, and to Professor Banerjee for the support that is indispensable to such achievement,” said Rod Alferness, dean of the UC Santa Barbara College of Engineering. “Given to only a single student in the Americas and only three in the world, this award is a major testament not only to Junkai, but also to the kind of students we attract at UCSB and the pioneering spirit they bring to tackling important problems.”

According to Professor Banerjee, “Junkai’s achievements in his research are certainly most deserving of this honor.” Jiang joined Banerjee’s Nanoelectronics Research Lab (NRL) in 2012 as a dual M.S./Ph.D. student after completing his bachelor of science degree in microelectronics at Peking University in China.

The UCSB Current – "Pushing Past Limits" (full article)